# The Pennsylvania State University

The Graduate School

College of Engineering

# STATE SPACE MODELING, ANALYSIS, AND SIMULATION OF IDEAL SWITCHED RLCM NETWORKS

A Thesis in

**Electrical Engineering**

by

Saleh Mahdi Albeaik

© 2014 Saleh Mahdi Albeaik

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science

May 2014

The thesis of Saleh Mahdi Albeaik was reviewed and approved\* by the following:

Jeffery S. Mayer Associate Professor of Electrical Engineering Thesis Advisor

John D. Mitchell Professor of Electrical Engineering

Kultegin Aydin Professor of Electrical Engineering Head of the Department of Electrical Engineering

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

The design process for power converters and electromechanical drives would be enhanced by the availability of modeling software that represents the fundamental nature of these systems, namely, switch-mode operation of the semiconductor devices. Established network simulation programs, such as SPICE and its many descendants, utilize a combination of companion models and modified nodal analysis (CM + MNA) that permits very simple implementations of algorithms for simulating the dc, ac, and transient response of most electrical networks. In the early days of computer modeling, the simplicity of these algorithms was critically important while the attention being given to networks with switch-mode operation was modest and focused on digital logic. Thus, SPICE (CM + MNA) became the de facto standard for network simulation. It can be used for transient simulation of power converters, but it is inherently slow and can provide little insight beyond the raw time-domain response of the converter. These limitations can be addressed by replacing CM + MNA with state space modeling (SSM). Ideal switches, the main subject of this thesis, impose computational difficulty to simulation software. The ideal behavior is extremely non-linear, potentially causing impulses to exist in the network. Moreover, to employ piecewise linear analysis techniques, switch conduction state dependencies must be resolved. The thesis offers a computationally efficient method to handle the presence of impulses as an alternative to more complex approaches presented in literature. Analyzing the presence and the effect of impulses efficiently makes resolving switch state dependencies using the common iterative search algorithm feasible.

Simulation software based on this thesis was designed and implemented. An overview of the software design is presented towards the end.

# **TABLE OF CONTENTS**

| List of Figuresv                                                                    |      |  |  |  |

|-------------------------------------------------------------------------------------|------|--|--|--|

| List of Tables                                                                      | viii |  |  |  |

| Chapter 1 Introduction                                                              | 1    |  |  |  |

| 1.1 Motivation                                                                      | 1    |  |  |  |

| 1.2 Problem Description                                                             |      |  |  |  |

| •                                                                                   |      |  |  |  |

| 1.3 Technical Challenges                                                            |      |  |  |  |

|                                                                                     |      |  |  |  |

| 1.3.2 Impulses Are Related to Device Level Behavior                                 |      |  |  |  |

| 1.3.3 Impulses in Switched RLCM Networks                                            |      |  |  |  |

| 1.4 Contributions                                                                   |      |  |  |  |

| 1.5 Thesis Organization                                                             | 10   |  |  |  |

| Chapter 2 Modeling                                                                  | 11   |  |  |  |

| 2.1 Network Modeling                                                                | 11   |  |  |  |

| 2.1.1 Device level                                                                  |      |  |  |  |

| 2.1.1 Device level                                                                  |      |  |  |  |

|                                                                                     |      |  |  |  |

| 2.2 Control System Modeling                                                         |      |  |  |  |

| 2.2.1 Device Level                                                                  |      |  |  |  |

| 2.2.2 System level                                                                  | 21   |  |  |  |

| Chapter 3 Analysis                                                                  | 22   |  |  |  |

| 3.1 Analysis of Switched Networks                                                   | 22   |  |  |  |

| 3.2 Incomplete State Space Model Analysis (Switches Modeled as SOC)                 |      |  |  |  |

| 3.3 Incomplete State Space Model Analysis (Switches Modeled as ZVIS)                |      |  |  |  |

| 3.4 Completing the State Space Model                                                |      |  |  |  |

| 3.5 Complete State Space Model (Switches Modeled as SFIS)                           |      |  |  |  |

| 3.6 Explicit State Re-initializing                                                  |      |  |  |  |

| 3.7 Network analysis in the presence of internally controlled switches and diodes   |      |  |  |  |

| 3.8 Design of the simulation algorithm                                              |      |  |  |  |

| Chapter 4 Software Design                                                           | 35   |  |  |  |

| 4.1 Switched RLCM Network Simulator                                                 | 25   |  |  |  |

| 4.1 Switched RECM Network Simulator  4.2 Use Case                                   |      |  |  |  |

|                                                                                     |      |  |  |  |

| 4.3 Program Architecture                                                            |      |  |  |  |

|                                                                                     |      |  |  |  |

| 4.3.2 Analysis Methods and Their Utility in The Context of Functional Decomposition |      |  |  |  |

| 4.3.3 Component Models                                                              |      |  |  |  |

| 4.3.4 Impulse support and the Signal Value object                                   |      |  |  |  |

| 4.4 Objects Interaction (Sequence Diagrams)                                         |      |  |  |  |

| 4.4.1 Compute Dynamic Response                                                      |      |  |  |  |

| 4.4.2 Initialize and Finalize Piecewise Linear Step:                                |      |  |  |  |

| 4.4.3 Refresh State Space Model                                                     |      |  |  |  |

| 5.1 Simulation Tests and Results                                                  | 62 |

|-----------------------------------------------------------------------------------|----|

| 5.2 Simple Networks                                                               |    |

| 5.3 Rectifier Network                                                             |    |

| 5.4 Buck Converter Networks                                                       |    |

| Chapter 6 Future Work                                                             | 78 |

| 6.1 Introduction                                                                  | 78 |

| 6.2 Motivation                                                                    | 78 |

| 6.3 Drawbacks                                                                     | 78 |

| 6.4 Modeling                                                                      |    |

| 6.4.1 Dependent Source Switch Model                                               |    |

| 6.4.2 Switched Network General State Space Model                                  | 80 |

| 6.5 Network Analysis                                                              |    |

| 6.6 Network Analysis in the Presence of Internally Controlled Switches and Diodes |    |

| 6.7 Equivalence between the General and the Complete State Space Models           | 88 |

| Chapter 7 Conclusion                                                              | 93 |

| References                                                                        | 94 |

| Appendix A Parameters for Test Cases                                              | 95 |

| Appendix B ISM and SCN Files for Test Cases                                       | 98 |

# LIST OF FIGURES

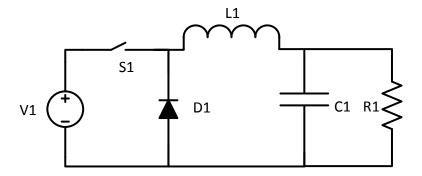

| Figure 1.1 Switched active RC network                                                                         | 5  |

|---------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2 The change of a switch state from OFF to ON corresponds to a voltage drop                          | 6  |

| Figure 1.3 The change of a switch state from ON to OFF corresponds to a current drop                          | 7  |

| Figure 1.4 Switched active RC network                                                                         | 7  |

| Figure 1.5 DC to DC buck converter                                                                            | 7  |

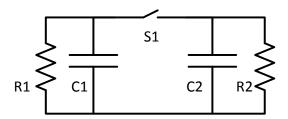

| Figure 1.6 Switched passive RC network                                                                        | 8  |

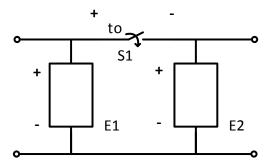

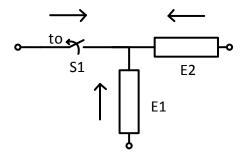

| Figure 3.1: KVL must be conserved for all time t: $v(E1, t) - v(E2, t) - v(S1, t) = 0$                        | 24 |

| Figure 3.2: KCL must be conserved for all time t: $i(E1, t) + i(E2, t) + i(S1, t) = 0$                        | 25 |

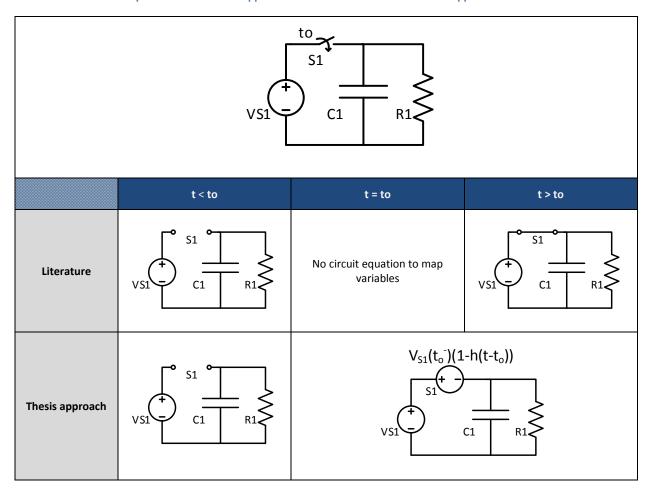

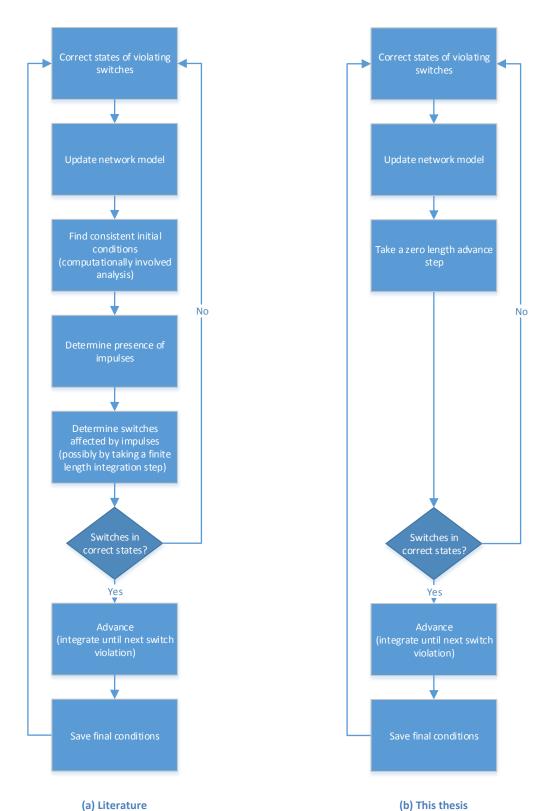

| Figure 3.3 Simulation algorithm commonly used in literature as compared to algorithm in thesis                |    |

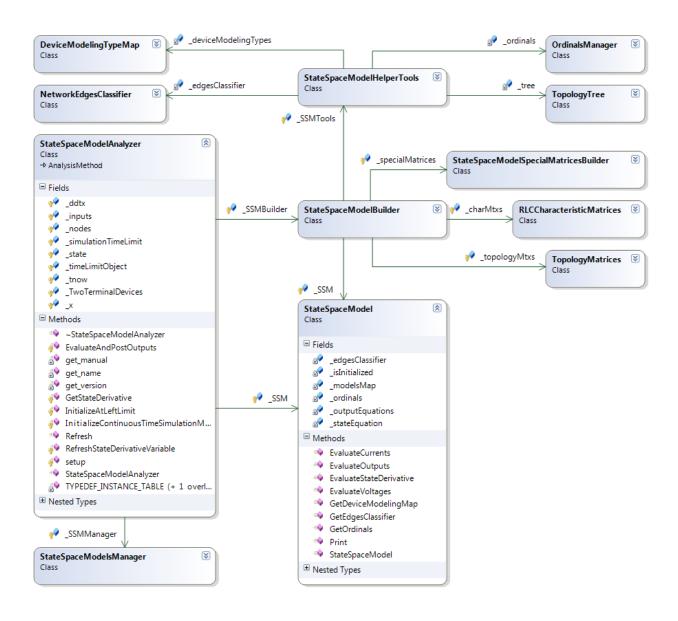

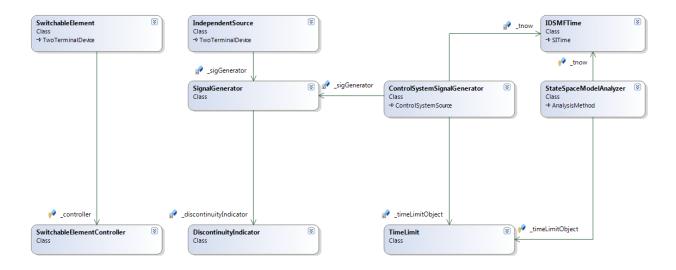

| Figure 4.1 Class diagram for State Space Analyzer and the classes it is composed of                           | 39 |

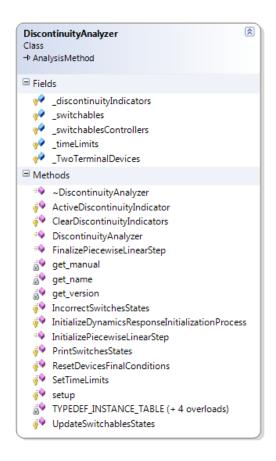

| Figure 4.2 Class diagram for Discontinuity Analyzer                                                           | 44 |

| Figure 4.3 Class diagram for classes the Discontinuity Analyzer interacts with                                | 44 |

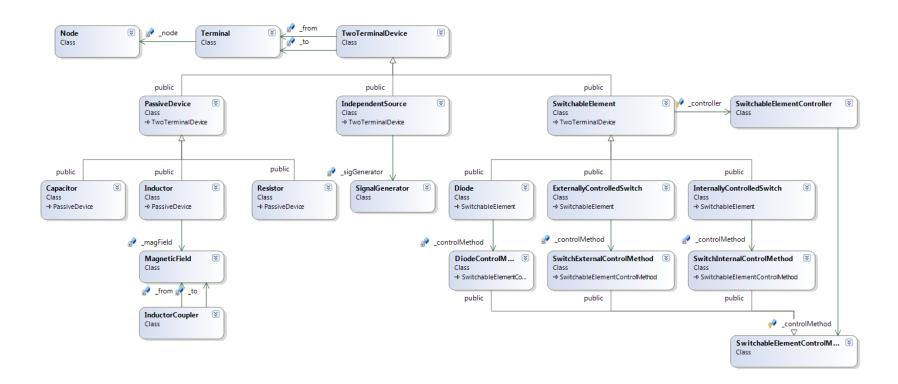

| Figure 4.4 Class diagram for electrical network component models                                              | 47 |

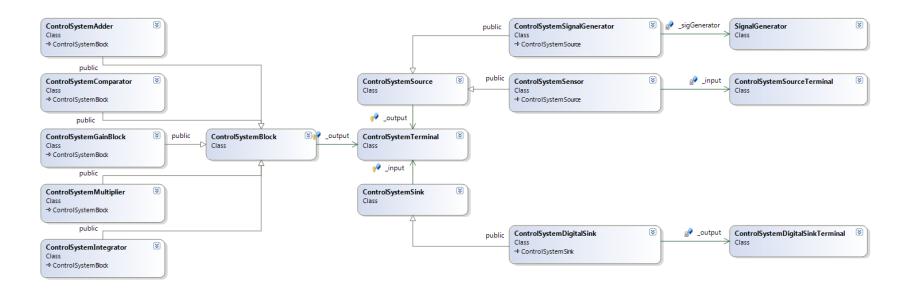

| Figure 4.5 Class diagram for control system component models                                                  | 53 |

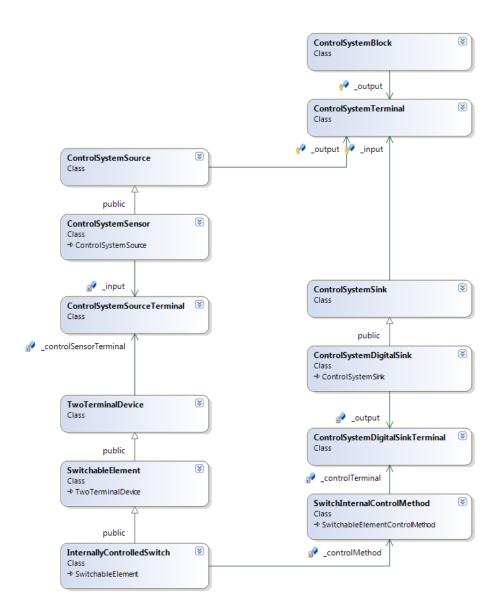

| Figure 4.6 Class diagram showing the interface between control system and electrical network component models |    |

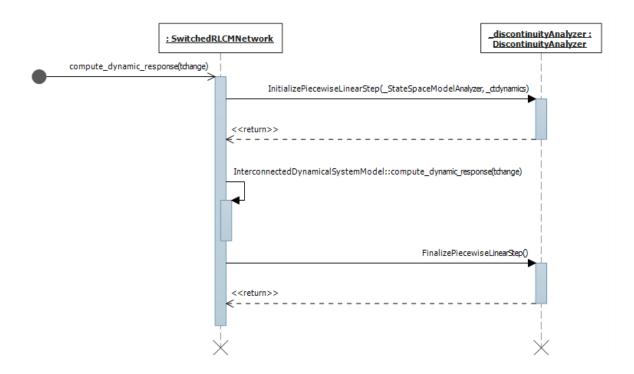

| Figure 4.7 Sequence diagram for Compute Dynamic Response                                                      | 57 |

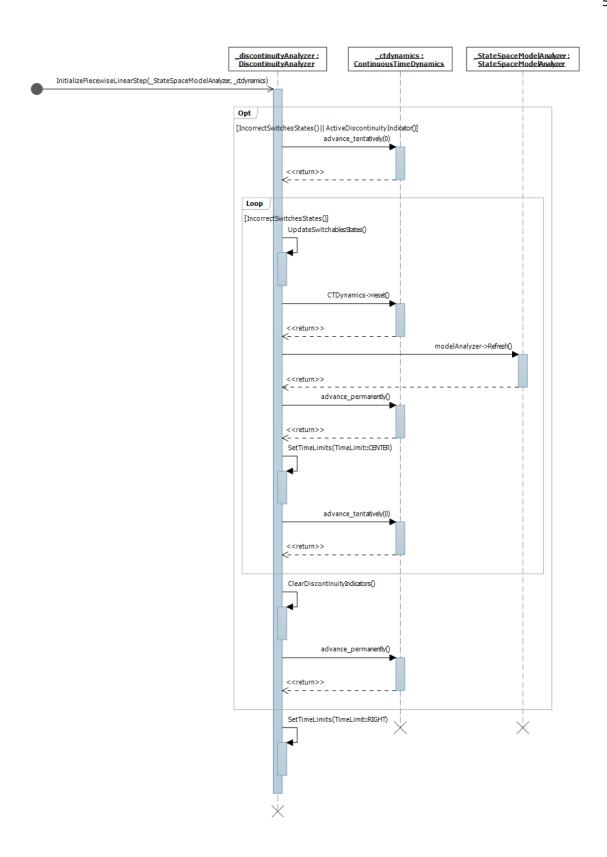

| Figure 4.8 Sequence diagram for Initialize Piecewise Linear Step                                              | 59 |

| Figure 4.9 Sequence diagram for Finalize Piecewise Linear Step                                                | 60 |

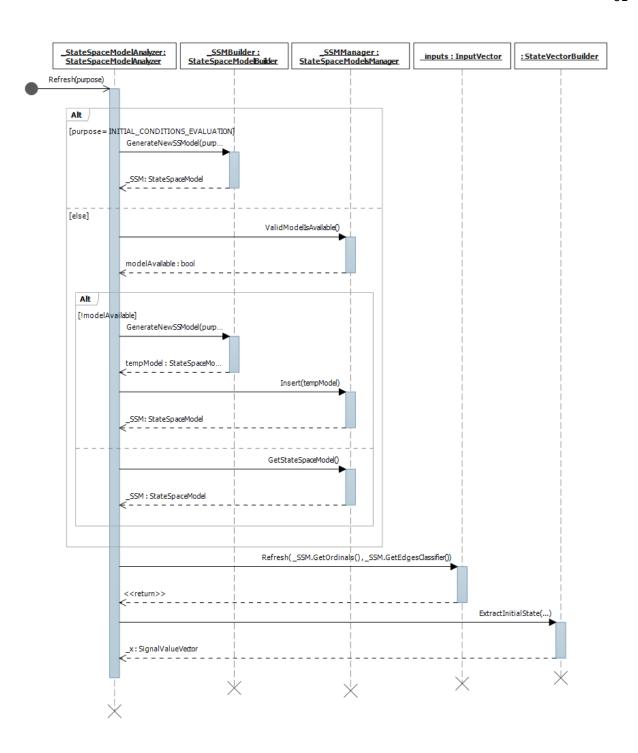

| Figure 4.10 Sequence diagram for state space model Refresh                                                    | 61 |

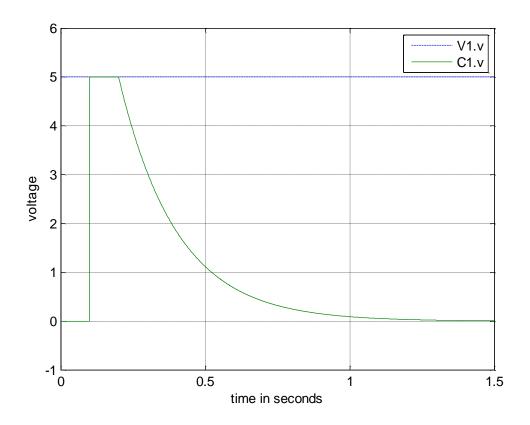

| Figure 5.1 Simulation results for network in Figure 1.1                                                       | 63 |

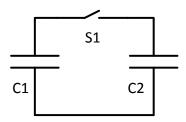

| Figure 5.2 Switched capacitor loop                                                                            | 64 |

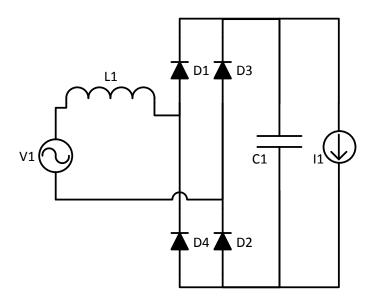

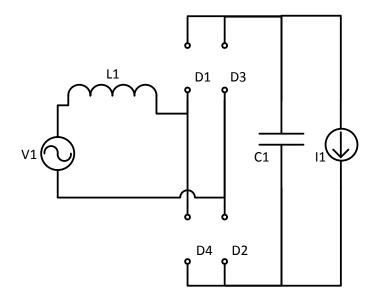

| Figure 5.3 Bridge rectifier network                                                                           | 65 |

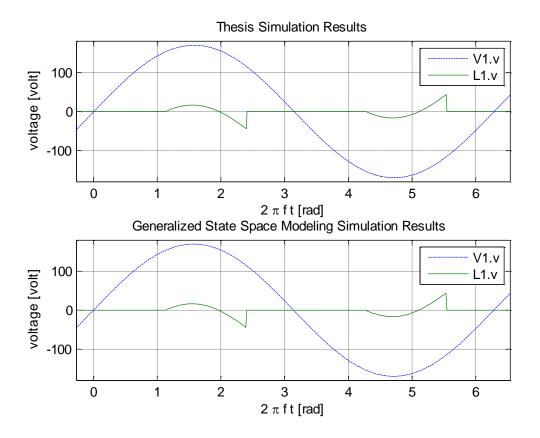

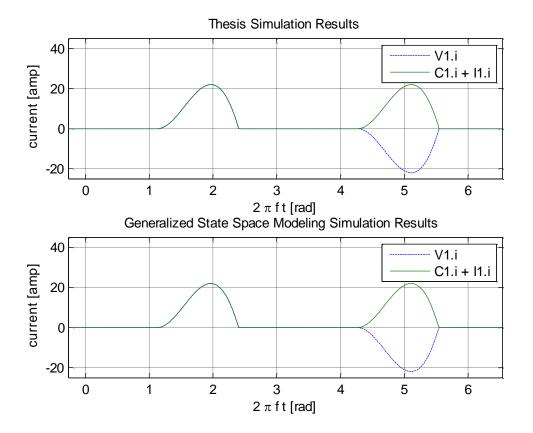

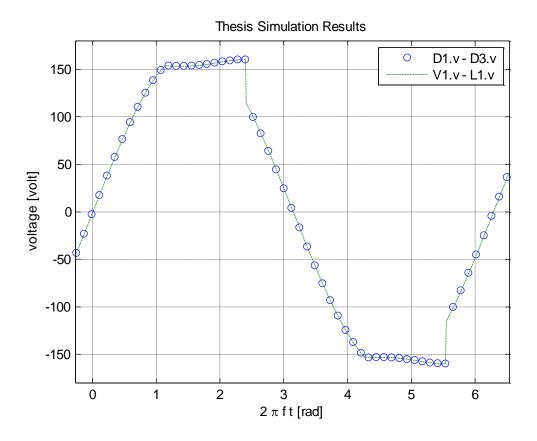

| Figure 5.4 Simulated AC side voltage values for network in Figure 5.3                    | 66 |

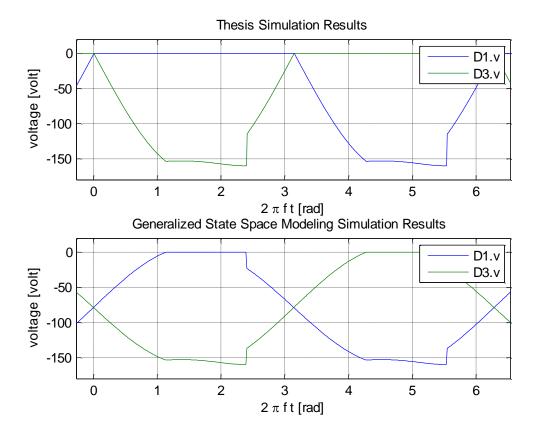

|------------------------------------------------------------------------------------------|----|

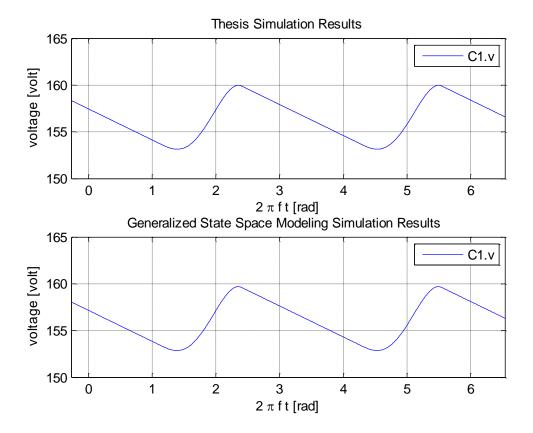

| Figure 5.5 Simulated DC side voltage values for network in Figure 5.3                    | 67 |

| Figure 5.6 Simulated currents of the network in Figure 5.3                               | 68 |

| Figure 5.7 Simulated diode voltages of the network in Figure 5.3                         | 69 |

| Figure 5.8 Bridge rectifier when all diodes are OFF                                      | 70 |

| Figure 5.9 Consistent loop voltages in any switch configuration                          | 70 |

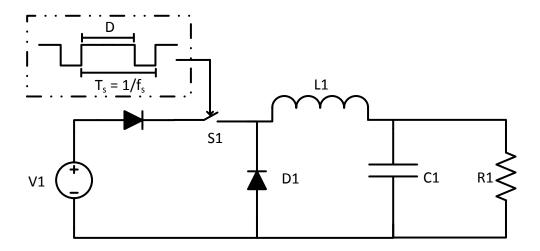

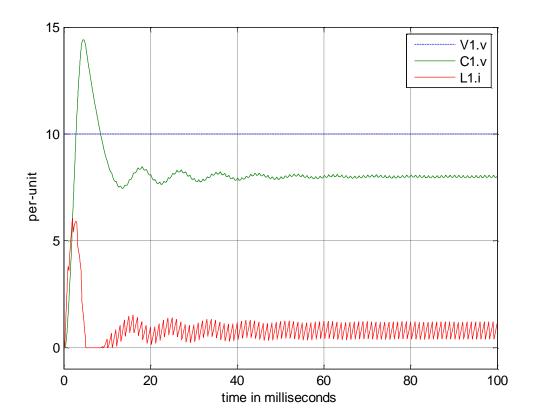

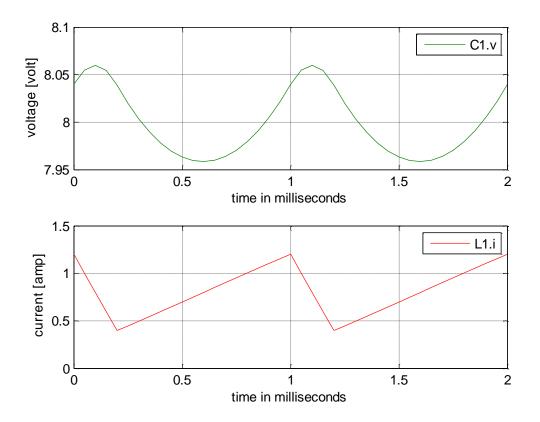

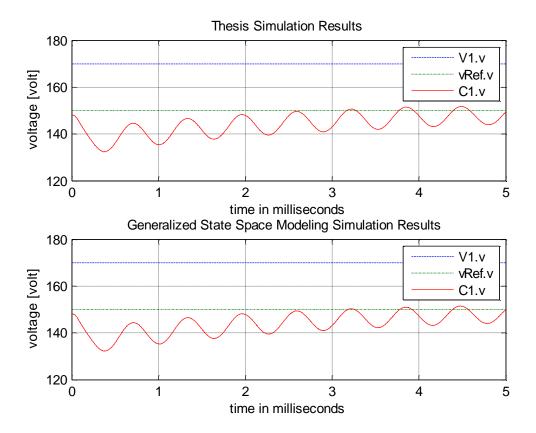

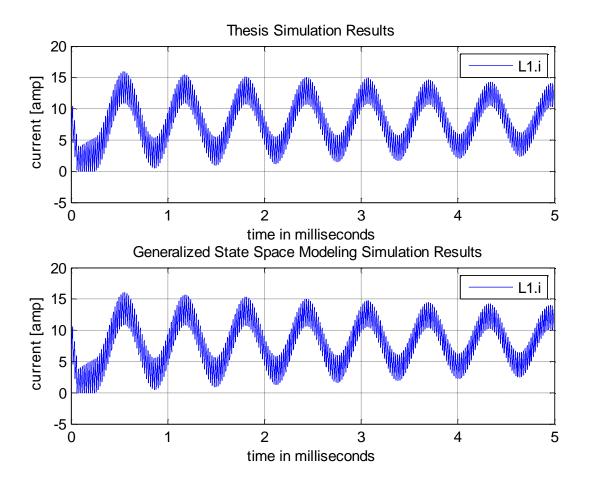

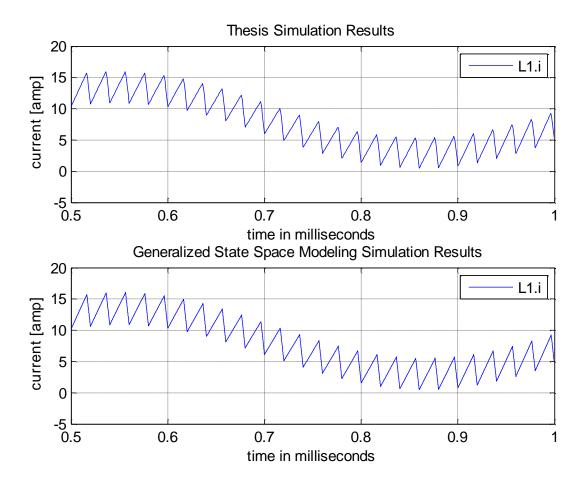

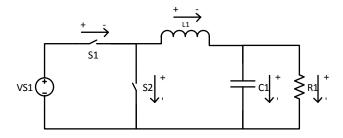

| Figure 5.10 Buck converter with constant switching frequency                             | 71 |

| Figure 5.11 Simulation results for network in Figure 5.10                                | 72 |

| Figure 5.12 Simulation results for network in Figure 5.10 during steady state operation. | 73 |

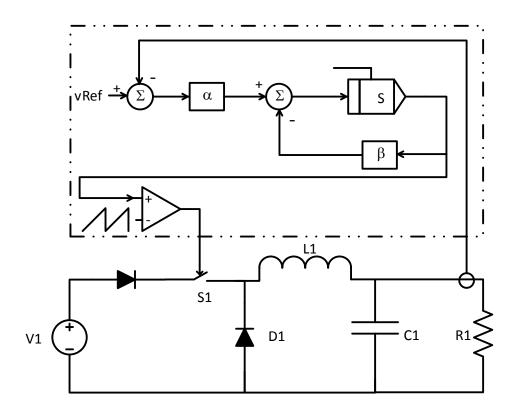

| Figure 5.13 Buck converter with closed loop switch control                               | 74 |

| Figure 5.14 Input and output voltages for network in Figure 5.13                         | 75 |

| Figure 5.15 Output current for network in Figure 5.13                                    | 76 |

| Figure 5.16 Output current for network in Figure 5.13 showing waveform details           | 77 |

| Figure 6.1 Buck converter with diode represented as a switch                             | 88 |

| Figure 6.2 Buck converter with the switch and diode represented as sources               | 90 |

# LIST OF TABLES

| Table 1.1 A comparison between the approach discussed in this thesis with the approach discussed in literature | 10 |

|----------------------------------------------------------------------------------------------------------------|----|

| Table 2.1 v-i and i-v characteristic of RLCM devices                                                           | 12 |

| Table 2.2 v-i and i-v characteristic of independent sources                                                    | 12 |

| Table 2.3 Ideal switch models                                                                                  | 13 |

| Table 2.4 Voltage and current characteristic of SFIS                                                           | 13 |

| Table 2.5 Summary of Switched Network Incomplete State Space Model                                             | 15 |

| Table 2.6 u variable as defined by SOC and ZVIS based state space models                                       | 15 |

| Table 2.7 Summary of Switched Network Complete State Space Model                                               | 17 |

| Table 2.8 Definition of dynamic function blocks                                                                | 19 |

| Table 2.9 Output characteristics for non-dynamic function blocks                                               | 20 |

| Table 2.10 Parameters and characteristics of signal sources                                                    | 20 |

| Table 2.11 Definition of signal sinks                                                                          | 21 |

| Table 3.1 Erroneous use of network model at turning ON switching instant with switches modeled as SOC          | 26 |

| Table 3.2 Erroneous use of network model at turning OFF switching instant with switches modeled as SOC         |    |

| Table 3.3 Complete ideal switch characteristic                                                                 | 27 |

| Table 5.1 Simulation results for network in Figure 5.2                                                         | 64 |

| Table 5.2 Theoretical results for network in Figure 5.10 during steady state operation                         | 73 |

| Table 6.1 Ideal switch model (extended)                                                                        | 79 |

| Table 6.2 Summary of the Switched Network General State Space Model                                            | 81 |

| Table 6.3 Discontinuities in Switched Network General State Space Model                                        | 82 |

| Table 6.4 Switch constraints and dependent source variable                                                     | 84 |

| Table 6.5 Dependent current source dependence expressions                                                      | 84 |

| Table 6.6 Expected characteristic for the network in Figure 1.1 given example scenario              | .85 |

|-----------------------------------------------------------------------------------------------------|-----|

| Table 6.7 General state space model as function of switch input                                     | .87 |

| Table 6.8 Voltages across and currents through each switch in each of the buck converter topologies | .89 |

# **Chapter 1 Introduction**

#### 1.1 Motivation

We are living in an era of ever faster and more sophisticated products and services. To design and build systems that meet the standards of this era, engineers usually must conduct complex analyses of system performance using mathematical models. Computer systems, both hardware and software, are among the technologies with the fastest development process and provide a basis for conducting analyses of many other systems. More pointedly, object-oriented programming languages and their associated design processes have emerged as key elements for creating engineering analysis and design tools that are critical to increasing engineering productivity.

Programs for simulating electronic circuits were among the limited set of applications developed during the first few generations of digital computer technology. The most successful of those programs was SPICE – Simulation Program with Integrated Circuit Emphasis – which went on to become a de facto standard in the integrated circuit industry and in electrical engineering more generally. The success of SPICE (including its descendants) was due in large part to the fact that the combination of so-called companion models and modified nodal analysis (CM+MNA) that it uses is highly adapted to simulating electrical networks. The simplicity of the CM+MNA was particularly valuable with early computers, and simulation, as opposed to other forms of analysis, was of paramount importance.

Having powerful programming languages and fast hardware readily available, it is useful to reconsider the modeling and simulation techniques that did not gain popularity in the earlier days. The objective of this research is to design and implement software to model and simulate switched RLCM networks using state space methods and ideal switch models, as these methods and models are more appropriate for the analysis of power converters.

## 1.2 **Problem Description**

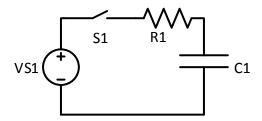

There are several practical methods for modeling and simulating so-called RLCM networks that are comprised of resistors, inductors, capacitors, and mutual inductance as well as independent sources. The addition of switches in an RLCM network, however, poses a significant challenge. In particular, SPICE and its many descendants utilize a combination of companion models and modified nodal analysis (CM+MNA) that can accommodate highly accurate behavioral modeling of diodes and transistors but does not recognize changes in network topology arising from the use of ideal switch models. When analyzing power converters at a system level; however, it is often desirable to model the switching devices as being ideal and to consider the sequence of topologies that the converter goes through. Thus, state space modeling (SSM) is a preferred alternative to CM + MNA.

In recent years, several SSM-based simulators have been proposed and implemented. However, many of these are limited to particular types of networks as the result of simplifying assumptions. These assumptions commonly fall under two main categories: (1) suitability of state space formulation to computer environments and (2) efficiency in handling the transitions between two consecutive topologies [1], [2], [3]. The first category of assumptions has led to simulators that are reliant on pregenerated state transition matrices to model the network. The second category of assumptions includes limiting the mutual behavior of switches to reduce the complexity of algorithms for determining transitions between topologies. Examples include relying on equivalent multi-terminal switches to hide dependencies, limiting the number of switches that may change state at any particular time instant, and assuming continuity of capacitor voltages and inductor currents.

This thesis project utilizes modern programming approaches and modern analysis methods to obviate the need for restrictive assumptions in state space modeling and simulation of switched RLCM networks.

The use of object oriented programming languages facilitates formulating state space models and handling changes in network topology. Each topology corresponds to a linear electrical network, which

can be solved using numerical integration methods. The generated solutions can be monitored automatically to detect conditions referring to change in the state of any of the switches. At this instant, the simulator evaluates the state of each switch in order to generate the new topology and the corresponding state space model. This approach eliminates the need for a prior knowledge of all possible state space models or state transition matrices. The automation of the process also reduces the complexity and the time associated with finding the proper next topology.

A software application for modeling and simulating switched networks has been designed and implemented. The use of ideal switch models in this application is of particular importance for simulating system level behavior of power converters. Moreover, the use of state space modeling methods allows the use of the application for purposes other than simulation. For example, studying stability of systems without the need to simulate the response of the network.

## 1.3 **Technical Challenges**

To simulate switched RLCM networks using state space modeling techniques, we must first address a number of challenges. Ideal switches have nonlinear i-v characteristics, which can disturb the network. The nonlinearity of ideal switches takes effect only at transition instants. This makes it possible to reduce the simulation problem to analyzing a sequence of linear RLCM networks. However, analyzing switch transition instants is challenging.

The first challenge to analyzing switch transition instants is identifying these instants. This challenge is specific for networks that have internally controlled switches. For numerical simulation applications, this challenge is commonly addressed using numerical binary search algorithms. The instants of switch transitions are identified in an iterative process attempting to specify the time instant at which a switch violates its conditions. The accuracy of identifying the time instant can be controlled by the number of iterations executed.

The instantaneous response of ideal switches can cause discontinuity in capacitor voltages or inductor currents. The new capacitor voltages and inductor currents must be calculated, which is the second challenge. This challenge is commonly called the re-initialization problem, or the problem of finding consistent initial conditions. In the literature, re-initialization has been addressed in multiple ways. A popular approach was proposed by [4] based on two-step integration algorithm. However, their approach requires special integration algorithms, which adds to the complexity of the solution. Another approach was proposed recently by [5] based on an energy jump rule. While that method is relatively easy to implement, finding the consistent initial conditions requires computing a Moore-Penrose pseudo inverse and finding the null space of a matrix. These two linear algebra operations are not the simplest to calculate, and are supported natively by only a limited number of programming languages. In particular, C++, which is the language used for this project, does not support it natively.

When a switch transitions, it is possible that it will trigger a sequence of other switch transitions throughout the network. Therefore, whenever the network has experienced a switch transition, a thorough analysis must be performed to identify the correct topology the network will enter after the initial event. A recent work by [6] addressed this challenge by constructing closed form solution. However, their approach assumes that capacitor voltages and inductor currents are continuous at the transition instant. An earlier work [4] used an iterative approach. The iterative approach traces impulses, while freezing time, to identify the sequence of switch transitions. However, that approach also requires performing some analysis to detect the presence of analytical impulses and to calculate their areas.

In this project we were interested in a general and automatic simulation process that does not require prior knowledge about the network dependencies nor user intervention. Some of the issues with the

approaches in literature will be addressed in this thesis before delving into the software design of the simulator.

#### 1.3.1 Transitions in Switch Conduction States

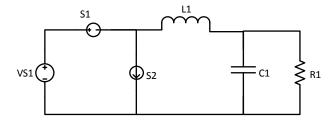

Transitions in the conduction state of an ideal switch (may) force instantaneous changes in the values of network variables. Network variables associated with storage elements are particularly sensitive to such changes due to the time derivatives in the i-v characteristics of the storage elements. This means that an abrupt change in the network initiated by a switch can introduce impulses in the network. To illustrate this process, consider the circuit shown in Figure 1.1. The switch S1 changes state from OFF to ON at  $t_o$ .

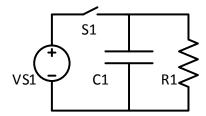

Figure 1.1 Switched active RC network

This forces the voltage between the switch terminals to zero instantaneously. The network voltages and currents must continue to satisfy KVL and KCL, but the capacitor is the only element in the loop (VS1, S1(ON), C1) whose voltage may change. Consequently, the capacitor voltage undergoes a step change with an associated current impulse ( $i_C = C \frac{d}{dt} v_c$ ).

The changes in network at a switch transition can be formalized as follows:

- A voltage or current changes instantaneously due to a trigger event. Trigger events considered in this work include switch transitions and discontinuities in independent sources.

- A switch transitions in one of two ways:

- Switch turning on

- The voltage change across the terminals of the switch steps to zero forcing an instantaneous change in voltage around the remainder of any loops that include the switch as in Figure 1.2.

- Switch turning OFF

- The current change through the switch steps to zero forcing an instantaneous change in the current through the remainder of any cut-sets that include the switch as in Figure 1.3.

- To maintain KVL and KCL, one of the following three conditions must occur in the affected loops or cut-sets:

- An element (or elements) simply absorbs the change without instigating changes in variables for any other element as in Figure 1.4.

- A switch transitions between ON/OFF states, possibly instigating even more switch transition events. An example of this scenario is the switching events in a buck converter, shown in Figure 1.5.

- A capacitor or inductor absorbs the change thereby creating a current or voltage impulse as in Figure 1.1.

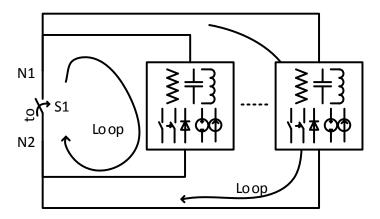

Figure 1.2 The change of a switch state from OFF to ON corresponds to a voltage drop

Figure 1.3 The change of a switch state from ON to OFF corresponds to a current drop

Figure 1.4 Switched active RC network

Figure 1.5 DC to DC buck converter

## 1.3.2 Impulses Are Related to Device Level Behavior

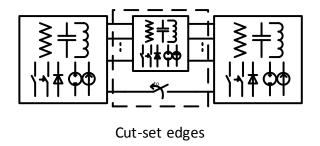

Consider the circuit shown in Figure 1.6. When S1 is OFF, the state space dimensionality is 2 with both capacitor voltages being state variables. However, when S2 is ON, the dimensionality is 1 and only one capacitor voltage can be a state. At a transition from the first case to the second, both capacitor voltages

will be discontinuous (assuming the voltages were not identical immediately preceding the switch transition), and a current impulse will flow through the capacitors and switch.

Figure 1.6 Switched passive RC network

This example illustrates the fact that in switched RLCM networks with finite inputs, impulses may arise due to a discontinuity in capacitor voltage or inductor current regardless of the status of the voltage or current as state variable (both before and after the transition). Therefore, when using state space models, it is important not to let the notion of state misguide us to wrong conclusions. In this chapter and in our simulation algorithm, we allow impulses to be legitimate signals and thus we establish independence between the notion of state and the possibility of discontinuity, and thus between the state and its impulsive derivative.

To summarize, independently of any other notions, at the device level, the following is always true:

- For any capacitor whose voltage  $v_C$  undergoes a step change, the current  $i_C = C \frac{d}{dt} v_C$  will be an impulse.

- For any inductor whose current  $i_L$  undergoes a step change, the voltage  $v_L = L \frac{d}{dt} i_L$  will be an impulse.

## 1.3.3 Impulses in Switched RLCM Networks

In switched network analysis, admission of impulses is critical for obtaining the correct response.

Impulses arise in the network as a result of interaction between the non-linear i-v characteristic of the ideal switch and the time derivatives in the i-v characteristics of storage elements. Such impulses allow one to model an instantaneous transfer of energy between storage elements. This transfer of energy is a

counterpart for the discontinuity in the corresponding variables. In this thesis, we allow impulses in the analysis, eliminating the assumption that the capacitor voltages and inductor currents are continuous, and eliminating the need to analyze discontinuities explicitly. We can characterize a discontinuity by addressing the relationship between the changes caused by switch transitions and the impulses that arise. The relationship can be embedded in the state space model for implicit handling of discontinuities, or a simple (compared to the methods presented in literature) explicit re-initialization equation can be derived.

In our simulation algorithm, similar to [4] method, we made use of another type of impulse, which appears in the analysis to help us find correct switching configuration. This type of impulse can help us find the simultaneous solution satisfying RLCM network variables and switch states. That is, some trigger switch transitions can cause disturbances in the network putting a storage element at a critical state. In this critical state, an impulse would normally arise; however, a change in an internally controlled switch state absorbs the disturbance. This type of impulses can be used to trace a sequence of switching events leading to a stable simultaneous solution.

## 1.4 Contributions

This thesis contributes the following:

- Re-initialization equations are proposed to be part of the ideal switch model and the

corresponding state space model thus simplifying the analysis of switched RLCM networks.

Unlike the approaches in literature, which consider the re-initialization as an independent step

(additional analysis at the instant of switching), the method in this thesis gives a complete

characterization of the switched RLCM network at the instant of switching based on the network

following the event as shown in Table 1.1.

- A model for ideal switches and a corresponding state space model is introduced as a possible future work to model switched RLCM using a single model.

- An object-oriented application program was designed and implemented to simulate switched RLCM networks using state space modeling and the theory discussed in this thesis.

Table 1.1 A comparison between the approach discussed in this thesis with the approach discussed in literature

## 1.5 **Thesis Organization**

In the following chapters of this thesis, the theory that is used to develop the simulation algorithm is discussed first followed by the developed software. In chapter 2, RLCM network modeling, and control system modeling are discussed. The chapter introduces device models, ideal switch models in particular, and system models. Chapter 3 discusses the analysis of the models introduced in chapter 2. It focuses on addressing the analysis challenges of switched RLCM networks. The design and implementation of the simulator are then discussed in chapter 4. In chapter 5, test cases and results are presented. Chapter 6 then introduces an interesting future work based on generalizing the discussion of chapter 2 and 3. Finally, the thesis is concluded in chapter 7.

# **Chapter 2 Modeling**

# 2.1 **Network Modeling**

Modeling is prerequisite to simulation, and the choice of model plays an important role in analysis and affects its complexity. In this project, state space models are used for system level modeling. State space models for switched RLCM networks are not unique. An important difference between state space models stems from the choice of device level models. In the following sections, various alternatives for device level models will be discussed. Afterwards, the state space models that we obtain based on these models will be discussed.

In this thesis, the terms "open interval" and "closed interval" will have the specific meanings defined here.

Open interval will refer to a time interval that is free of switch transitions and is open at the beginning and at the end. For such an interval, we assume that we have been given or have computed a consistent initial condition.

Closed interval will refer to a time interval that is free of switch transitions and is closed at the beginning. In this interval, we assume that the consistent conditions satisfying KVL and KCL are available.

We call such consistent conditions final conditions<sup>1</sup>.

#### 2.1.1 Device level

In this project, we are interested in modeling switches as ideal devices. Such models retain the essential characteristics of the devices but do not include features of secondary importance, such as parasitic effects or stochastic behavior. We focus on switched RLCM networks that are comprised of elements from three groups: RLCM elements, independent sources, and switching elements. There are

<sup>&</sup>lt;sup>1</sup> Consistent conditions associated with a closed interval are called final conditions because they are typically the output of the preceding open/closed interval.

conventional models for devices in the first two groups as summarized in Table 2.1 and Table 2.2.

However, many different models for switching elements have been proposed in the literature. While each of those models preserves the characteristics of an ideal switch, different models are defined in this chapter to simplify system level analysis in the next chapter.

Table 2.1 v-i and i-v characteristic of RLCM devices

| Device            | v-i characteristic                               | i-v characteristic                                                                |

|-------------------|--------------------------------------------------|-----------------------------------------------------------------------------------|

| Resistor          | v = R i                                          | $i = \frac{1}{R}v$                                                                |

| Conductor         | $v = \frac{1}{G} i$                              | i = G v                                                                           |

| Capacitor         | $v = v(t_0) + \frac{1}{C} \int_{t_0}^t i(s)  ds$ | $i = C \frac{d}{dt} v$                                                            |

| Inductor          | $v = L \frac{d}{dt}i$                            | $i = i(t_0) + \frac{1}{L} \int_{t_0}^t v(s)  ds$                                  |

| Mutual inductance | $ar{v} = ar{\overline{L}} rac{d}{dt} ar{v}$     | $\bar{\iota} = \bar{\iota}(t_0) + \bar{\bar{L}}^{-1} \int_{t_0}^t \bar{v}(s)  ds$ |

Table 2.2 v-i and i-v characteristic of independent sources

| Independent source type | v-i characteristic                                     | i-v characteristic                                                  |

|-------------------------|--------------------------------------------------------|---------------------------------------------------------------------|

| Voltage source          | v = specified input                                    | <pre>i = determined by KCL at a node to which it is connected</pre> |

| Current source          | v = determined by KVL of $a loops to which it belongs$ | i = specified input                                                 |

## Switching elements:

Switching elements are at the core of this research. These elements can be in one of two conduction states: conducting (ON) and non-conducting (OFF). The conduction state may be controlled internally or

externally. For example, a diode would be represented as an internally controlled switch. As another example, a MOSFET would be represented as an internally controlled switch, if the gating signal is derived from network variables, or as an externally controlled switch, if the gating signal is specified by the user.

Ideal switching elements have the following characteristic: i=0 or v=0. Some alternative models that have an equivalent characteristic are listed in Table 2.3.

Table 2.3 Ideal switch models

| Name                                       | ON-State Model             | OFF-State Model            |

|--------------------------------------------|----------------------------|----------------------------|

| Short-Open-Circuit<br>(SOC)                | Short circuit              | Open Circuit               |

| Zero-Valued Independent Source<br>(ZVIS)   | 0-V Voltage source         | 0-A Current source         |

| Step Function Independent Source<br>(SFIS) | Step to 0-V voltage source | Step to 0-A current source |

Each model from Table 2.3 brings advantages and disadvantages as we will see later. Conduction state is the only parameter of the first two models. They are very intuitive and the information already presented suffices. The third model depends on additional variables. Table 2.4 gives the details of the model, where h(.) represents the unit step function and  $t_o$  is the instant of switch transition.

Table 2.4 Voltage and current characteristic of SFIS

| variable | OFF-State Model                              | ON-State Model                               |

|----------|----------------------------------------------|----------------------------------------------|

| Voltage  | $v = v(t_o^-) \left( 1 - h(t - t_o) \right)$ | v = 0                                        |

| Current  | i = 0                                        | $i = i(t_o^-) \left( 1 - h(t - t_o) \right)$ |

The importance of this model stems from the fact that it is event dependent. The first two models in Table 2.3, model the ideal switch characteristic based on its conduction state only, independent of the switch condition at the transition instant. This model, on the other hand, includes a derivative at the transition instant to incorporate the switch condition into the model. The addition of the switch condition does not alter the characteristic in that i=0 or v=0 is maintained. However, the derivative of voltage or current may have a non-zero value at  $t_o$ ; thus the model includes additional information about the transition event.

#### 2.1.2 Network (system) level modeling

To simulate switched RLCM networks, we will be using state space models. The state space model description will vary slightly, yet in an important way, based on the choice of device models. More specifically, the choice of switch model, as will be presented in next chapter, affects the amount of information [about the switched network] the resulting state space model includes. In this section, the models will be introduced, and the analysis details will follow in the next chapter.

#### Switched Network Incomplete State Space Model<sup>2</sup>:

In this model, we represent switches as Short-or-Open-Circuits (SOC). This representation is the simplest, and its inclusion in the state space model derivation can be handled in the obvious way.

Comparing this state space model to the ones that will follow, this model is the simplest because switch variables do not appear in the model.

A single state space model is not sufficient to describe a switched RLCM network. Instead, a state space model is developed for each network configuration, where the configuration is identified by state of the switches. Each of these models is valid in an open interval between two switch transitions. This model requires that consistent initial conditions be provided at the beginning of each interval.

.

<sup>&</sup>lt;sup>2</sup> Incomplete State Space Model for short.

Table 2.5 summarizes this model for a given switch configuration,  $\pi$ .

**Table 2.5 Summary of Switched Network Incomplete State Space Model**

|                       | Summary                                 |                                                               |  |

|-----------------------|-----------------------------------------|---------------------------------------------------------------|--|

| E                     | State equation                          | $M_{\pi} \dot{x} = A_{\pi} x + B_{\pi} u + B_{\pi,1} \dot{u}$ |  |

| Equation form         | Output equation                         | $y = C_{\pi} x + D_{\pi} u + D_{\pi,1} \dot{u}$               |  |

|                       | x                                       | Vector of state variables                                     |  |

|                       | χ̈́                                     | Vector of first derivatives of state variables                |  |

| Variables             | и                                       | Vector of input variables                                     |  |

|                       | ù                                       | Vector of first derivatives of input variables                |  |

|                       | y                                       | Vector of outputs variables                                   |  |

| Validity interval     | π configuration                         |                                                               |  |

| ,                     |                                         | t0 t1                                                         |  |

| Validity requirements | Consistent $x(t_o^+)$ must be provided. |                                                               |  |

The incomplete model can also be obtained by modeling switches as Zero-Valued Independent Sources (ZVIS). The only difference between the ones based on SOC models, and the ones based on ZVIS is the definition of state space model variable u. This is summarized in Table 2.6.

Table 2.6 u variable as defined by SOC and ZVIS based state space models

| variable | SOC based                                      | ZVIS based                                                                                 |

|----------|------------------------------------------------|--------------------------------------------------------------------------------------------|

| u        | Input vector                                   | Input vector concatenated with zero entries for switches                                   |

| ù        | Vector of first derivatives of input variables | Vector of first derivatives of input variables concatenated with zero entries for switches |

## Switched Network Complete State Space Model<sup>3</sup>:

This state space model is based on representing the switches by Step Function Independent Source (SFIS) models. This state space model is a generalization of the incomplete state space model where switches are represented by (ZVIS) models. In this state space model, however, non-zero valued derivatives of switch variables are included in the  $\dot{u}$  variable. Including the derivatives extends the interval for which the model is valid to include the switching instant, which makes the validity requirement a trivial one. Table 2.7 summarizes this model for a given switch configuration,  $\pi$ .

<sup>3</sup> Complete State Space Model for short.

**Table 2.7 Summary of Switched Network Complete State Space Model**

|                       | Summary                                                          |                                                                                                            |  |

|-----------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| Equation form         | State equation                                                   | $M_{\pi} \dot{x} = A_{\pi} x + B_{\pi} u + B_{\pi,1} \dot{u}$                                              |  |

|                       | Output equation                                                  | $y = C_{\pi} x + D_{\pi} u + D_{\pi,1} \dot{u}$                                                            |  |

|                       | x                                                                | Vector of state variables                                                                                  |  |

|                       | χ̈́                                                              | Vector of first derivatives of state variables                                                             |  |

|                       | u                                                                | For independent sources, $u_i$ is input                                                                    |  |

|                       |                                                                  | Turning ON switches, $u_i = v(t_o^-) \left(1 - u(t - t_o)\right) = 0$                                      |  |

|                       |                                                                  | Turning OFF switches, $u_i = i(t_o^-) \left(1 - u(t - t_o)\right) = 0$                                     |  |

| Variables             | ù                                                                | For independent sources, $\dot{u}_i$ is first derivative of input                                          |  |

|                       |                                                                  | Turning ON switches,                                                                                       |  |

|                       |                                                                  | $\dot{u}_i = \frac{d}{dt} \Big( v(t_o^-) \left( 1 - u(t - t_o) \right) \Big) = -v(t_o^-)  \delta(t - t_o)$ |  |

|                       |                                                                  | Turning OFF switches,                                                                                      |  |

|                       |                                                                  | $\dot{u}_i = \frac{d}{dt} \Big( i(t_o^-) \left( 1 - u(t - t_o) \right) \Big) = -i(t_o^-)  \delta(t - t_o)$ |  |

|                       | у                                                                | Outputs vector                                                                                             |  |

|                       |                                                                  | π configuration                                                                                            |  |

| Validity interval     | ——{:::::::::::::::::::::::::::::::::::                           |                                                                                                            |  |

|                       | Consistent $x(t_o^-)$ must be provided                           |                                                                                                            |  |

| Validity requirements | For switches turning ON, consistent $v(t_o^-)$ must be provided  |                                                                                                            |  |

|                       | For switches turning OFF, consistent $i(t_o^-)$ must be provided |                                                                                                            |  |

Table 2.7 indicates that this model has more validity requirements than the earlier model. Note, however, that all the required variables are readily available in simulation applications. After discussing the analysis of these state space models in more details, a method to eliminate, or deduce, the consistent switch variable requirements will be presented for added generality.

#### State Space Model Formulation:

State space model formulation is an important aspect of the analysis. Because this thesis is aimed at developing a computer aided simulation application, the formulation algorithm must be well defined and suitable for computer environments. The method we chose is discussed in [7].

While the method presented only discusses the RLCM elements, we will also be adding switches.

Switches modeled as Short-or-Open Circuits are trivial to add. We include switches modeled as independent sources similar to actual independent sources. We can incorporate switches in the general formulation algorithm by using the following tree edge weighting strategy:

$$w(VS) < w(ON \ switch) < w(c) < w(R) < w(L) < w(OFF \ switch) < w(CS)$$

## 2.2 **Control System Modeling**

Control system model describes the switch state control of internally controlled switches. The control system, in our analysis and simulation, will be constructed such that it is an independent entity from the network model. While this choice might not be the most concise, it allows for generality which is one of the project requirements.

#### 2.2.1 Device Level

The control system consists of functional blocks, signal sources, and signal sinks. The functional blocks are defined by their inputs, [states,] outputs, and a function that operates on the inputs [and the states]. The signal sources and signal sinks, as their name suggest, source the control system with signals and sink signals by controlling switch states. All of the blocks operate in the ideal way such that the output is deterministic given the block definition.

#### **Functional Blocks:**

Functional blocks are divided into two categories; dynamic, and non-dynamic. The dynamic blocks depend on a state or states and present inputs. On the other hand, non-dynamic blocks depend on present inputs only.

## Dynamic Functional Blocks

From this category, we are interested in integrators only. Integrators are defined by a single input, a state, and output. This block is defined as in Table 2.8.

**Table 2.8 Definition of dynamic function blocks**

| Inputs                      | u                                   |  |

|-----------------------------|-------------------------------------|--|

| Outputs                     | y                                   |  |

| State                       | x                                   |  |

| Characteristic function     | $y = \int u(t) dt$                  |  |

| Numerical integration model | x(t+dt) = x(t) + u dt $y(t) = x(t)$ |  |

## Non-Dynamic Functional Blocks

This category consists of adders, comparators, gain blocks, and multipliers. The characteristic of each of these blocks is dependent on present input to the block only. Table 2.9 summarizes these blocks. In Table 2.9,  $u_i$  is the  $i^{th}$  input to the block, and y is its output.

Table 2.9 Output characteristics for non-dynamic function blocks

|             | Characteristic function                                                                                                              |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Adder       | $y = u_1 + u_2$                                                                                                                      |  |

| Comparator  | $y = \begin{cases} y_{true}, & u_1 > u_2 \\ y_{false}, & u_1 \leq u_2 \end{cases}$ Where $y_{true}$ , and $y_{false}$ are parameters |  |

| Gain block  | $y=g\ u_1$ Where $g$ is a parameter                                                                                                  |  |

| Multipliers | $y = u_1 u_2$                                                                                                                        |  |

## Signal Sources:

Signal sources blocks input signals to the control system. A subset of these blocks forms the input interface between the electrical network and the control system. Based on the input to these blocks, we define two categories: sensors, and signal generators. Signal generators are intended to be independent blocks generating signals directly to the control system. On the other hand, sensors are blocks attached to the electrical network to allow the transfer of signals to the control system. Table 2.10 summarizes the two signal source block types.

Table 2.10 Parameters and characteristics of signal sources

|                   | parameters                                              | Characteristic function                                                                                                |  |

|-------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Sensors           | The device to be considered, $\emph{d}$                 | $y = \begin{cases} v \text{ of device d,} & v \text{ sensor} \\ i \text{ of device d,} & i \text{ sensor} \end{cases}$ |  |

|                   | The variable to be measured, $i$ or $\emph{v}$          | y — \i of device d, i sensor                                                                                           |  |

| Signal Generators | Function F                                              | $y = F(\varphi)$                                                                                                       |  |

|                   | Parameter set $arphi$ independent to electrical network |                                                                                                                        |  |

#### Signal Sinks:

Signal sinks form the output interface between the control system and the electrical network. This set consists of digital sinks. The digital sinks are switch controllers. The state of switches a sink controls equals the binary bit-value of the input to the block as shown in Table 2.11.

**Table 2.11 Definition of signal sinks**

| Input            | u                                                                             |  |

|------------------|-------------------------------------------------------------------------------|--|

| Parameter        | Threshold                                                                     |  |

| Output           | $y = \begin{cases} ON, & u < threshold \\ OFF, & u \ge threshold \end{cases}$ |  |

| Switch interface | Switch state = y                                                              |  |

#### 2.2.2 System level

Unlike the system level model of the electrical network, this control model does not formulate a single system model. In the control system, we assume that the variables do not have circular dependences. This assumption makes it possible to find a sequence of function invocations, starting with system inputs (from signal sources) to system outputs (to signal sinks). To obtain the outputs of the system, we evaluate the characteristic function of each block on its inputs in the order specified by the generated function invocations sequence. The assumption that variables do not form circular dependency does limit the set of control systems that can be simulated. However, such systems are not within the scope of our interest.

# **Chapter 3** Analysis

## 3.1 Analysis of Switched Networks

In this chapter, the state space models presented in Chapter 2 will be discussed in more detail with a focus on switch transition instants. To study the state space models in isolation from the dependencies of the control variables of switches, networks with only externally controlled switches will be considered initially. Networks containing internally controlled switches will be considered later in the chapter.

# 3.2 Incomplete State Space Model Analysis (Switches Modeled as SOC)

In the analysis of networks containing ideal switches, the Short-Open Circuit model for switches is very common. While this model describes the network, given the states of ideal switches, in a very intuitive manner, handling switch transitions is complicated. Despite the fact that the model eliminates the switches nonlinearity in the open intervals where the switches states are constant, it does not properly address the correlation between network variables in successive time intervals. The inability of this model to describe the switching events necessitates an additional analysis to transfer final conditions to initial conditions. This additional analysis fills the gap between two successive time intervals described by two incomplete state space models.

This approach to analyzing a switched network ignores switch variables locally, in that each individual state space model is independent with respect to switch variables. This makes the task of transferring final conditions to initial conditions for storage element variables non-trivial. Considering the network model in any of the open intervals where switches are replaced with their Short-Open Circuit model, it is not obvious what changes initiated and caused step changes in the variables associated with the storage elements.

This problem has been addressed in the literature by developing explicit equations for transfer of conditions. [4] relies on a special two-step integration algorithm based on Laplace transform to perform the transfer. Their method, however, was designed to accompany nodal analysis and companion modeling techniques. A more recent work by [5] developed an explicit transfer of condition equations for state space models. Formulation of their equations, however, requires generating a Moore-Penrose pseudo inverse and finding the null space of a matrix for every topology of interest.

Finding consistent initial conditions after switch transitions is not sufficient for simulation. The combination of incomplete state space models and the re-initialization equations do not describe a switched RLCM network. Instead, they describe a sequence of linear RLCM networks. This is because, at the switch transition instant, the combination describes the step changes, if any, in energy storage element variables. The combination does not describe the remainder of the RLCM network. For this reason, at least one more analysis must be performed to identify the presence of impulses through or across switches. This task cannot be performed simply by substituting impulses for state variables in the equations that we already have. This is because the impulses, of capacitor currents and inductor voltages, we computed from the re-initialization equations are present at  $t_o$ , or equivalently during  $(t_o^-, t_o^+)$ . However, we do not have any equation that describes the switched RLCM network during  $(t_o^-, t_o^+)$ .

A section that will follow addresses the reason why the additional analyses are required. The problem is then tackled by extending the ideal switch characteristic leading to a more expressive switch model.

# 3.3 Incomplete State Space Model Analysis (Switches Modeled as ZVIS)

This model is tempting to use especially for computer-aided analysis algorithms as it is well known that a 0-V voltage source is equivalent to a short circuit, and a 0-A current source is equivalent to an open circuit. However, the network analysis using this model is prone to the same issues that arise when modeling switches as SOC.

# 3.4 Completing the State Space Model

Before delving into details, we will state explicitly why consistent final conditions are not necessarily consistent initial conditions. Consistent final conditions, by definition, combined with inputs and switch configuration before switch transitions, satisfy both KVL and KCL. However, after switch transitions, the change in network topology makes it possible that the zero-voltage or zero-current property around a loop or through a cut-set is violated by some of the final conditions. To account for this violation, the reinitialization equations, which give the consistent initial conditions, are used. Figure 3.1 and Figure 3.2 illustrates KVL and KCL during a switch transition.

Figure 3.1: KVL must be conserved for all time t: v(E1, t) - v(E2, t) - v(S1, t) = 0

Figure 3.2: KCL must be conserved for all time t: i(E1, t) + i(E2, t) + i(S1, t) = 0

The combination of incomplete state space models and the re-initialization equations are not sufficient to characterize the switched RLCM network. In this combination, other than the re-initialization equations, which map consistent final to initial conditions, the steps in capacitor voltages or inductor currents make no sense. Any attempt to reference these voltage or current steps outside the scope of the re-initialization equations leads to violation of the first derivative of KVL or the first derivative of KCL. Because state space models are constructed assuming KVL and KCL, the incomplete state space models are invalid outside the open interval. It is also why we must perform another independent analysis in order to find impulses around the switched RLCM network at the instant of switching. Table 3.1 and Table 3.2 illustrates the violation of the derivatives of KVL or KCL when erroneously attempting to use any of the incomplete state space at the instant of switching.

Table 3.1 Erroneous use of network model at turning ON switching instant with switches modeled as SOC

|                    | t < t0                                          | t > t0                  |  |

|--------------------|-------------------------------------------------|-------------------------|--|

| Equivalent network | + dv - + + + + + + E2                           | + + + E2 E2             |  |

| KVL                | No requirements                                 | v(E1, t) - v(E2, t) = 0 |  |

| Inconsistency      | d/dt[v(E1, t0) - v(E2, t0)} != 0                |                         |  |

| Correction         | $d/dt[v(E1, t0) - v(E2, t0)] != - dv \delta(0)$ |                         |  |

Table 3.2 Erroneous use of network model at turning OFF switching instant with switches modeled as SOC

|                    | t < t0                                                   | t > t0                  |

|--------------------|----------------------------------------------------------|-------------------------|

| Equivalent network | $ \begin{array}{c}                                     $ | E2<br>E1                |

| KVL                | i(E1, t) + i(E2, t) + i(S1, t) = 0                       | i(E1, t) + i(E2, t) = 0 |

| Inconsistency      | d/dt[i(E1, t0) + i(E2, t0)} != 0                         |                         |

| Correction         | $d/dt[i(E1, t0) + i(E2, t0)] = di \delta(0)$             |                         |

The switch model used to construct incomplete state space models misleads us to ignore the voltage derivative around, or the current derivative through a switch. Once this piece of information is recovered, we can easily verify that loop voltage derivative or the cut-set current derivative is equal zero at all times. And thus we can relate the non-zero derivative of storage element's variables with the non-zero derivative of switches variables. The switches force the voltage around themselves or the current

through them to zero. Using this property simplifies the analysis and extends the validity interval of our model. So, preserving the relevant derivatives, KVL and KCL can be maintained even during the instant of a switch transition. Thus the state space model after the transition can be made valid at the transition instant.

After addressing the importance of switch derivatives in the analysis, it is reasonable to generalize, or complete, the conventional switch characteristic from chapter 2. In the updated characteristic, we will include the switch derivative, which we require that the switch model satisfies. Table 3.3 summarizes the conventional and the complete switch characteristic.

Table 3.3 Complete ideal switch characteristic

|                             | ON-State                                        | OFF-state                                       |

|-----------------------------|-------------------------------------------------|-------------------------------------------------|

| Conventional characteristic | v = 0                                           | i = 0                                           |

| Complete characteristic     | $v=0$ and $rac{d}{dt}v=-v(t_o^-)\delta(t-t_o)$ | $i=0$ and $rac{d}{dt}i=-i(t_o^-)\delta(t-t_o)$ |

Completing the state space model, thus, means that the additional analysis methods are eliminated. The state space model itself can handle any discontinuities. A complete state space model describes the network at the instant of switching, or equivalently, the model contains the information necessary to transfer the final conditions into consistent initial conditions. Moreover, having a network and a corresponding state space model that is valid at the switch transition instant makes the task of finding impulses around the switched RLCM network trivial.

# 3.5 Complete State Space Model (Switches Modeled as SFIS)

In the complete state space model presented in Chapter 2, we use the SFIS switch model, which is consistent with the complete switch characteristic presented in Table 3.3. It preserves enough information to fill the gap between final and initial conditions, while maintaining the simplicity of an

incomplete state space model. The complete state space model specifies that given the switch configuration, we let ON switches be step-to-zero voltage sources, and OFF switches be step-to-zero current sources. The step size of each of the step sources is equal to the switch variable specified by the final conditions,  $v_{switch}(t_o^-)$  or  $i_{switch}(t_o^-)$ . In simulation applications, we normally know switch states at the least, in which case we can always evaluate the step size using the state space model prior to the switch transitions. If otherwise is the case, methods in a section that will follow address the problem.

Based on this method, switches are necessary to correctly redistribute energy in discontinuity conditions. Derivatives of switch variables take care of state re-initialization implicitly in this model. In some networks, it is possible that inconsistent conditions appear, usually defined by user, in loops or cut-sets that do not contain any switches. In this case, consistency is assumed, and one or more of the final conditions is neglected. Such circuits can be identified easily, and an equivalent circuit can be constructed to eliminate the limitation.

In the tree/co-tree representation of the network, a capacitor failing to be a branch or an inductor failing to be a link indicates dependence of the violating element on another that succeeded to be.

Therefore, if there exists a tree such that all voltage sources and all capacitors are branches, and all current sources and all inductors are links, irrespective of where switches go, then either all energy storing elements are independent or a switch exist in the same loop or cut-set. Such a test can be done by choosing the weight function for edges properly. Networks that fail this test, potentially, exhibit the problem described above. To solve the problem, an equivalent network must be constructed by adding ON switches in series with capacitors failing the test, and OFF switches in parallel with inductors failing the test.

## 3.6 Explicit State Re-initializing<sup>4</sup>

The complete state space model is capable of handling inconsistent initial condition, by relying on consistent final conditions only. However, it is common that we are given a network with final conditions not completely specified; switch states were not given. In this case, the method based on the complete state space model will experience difficulty because all the analyses discussed previously were based on the assumption that we started with given final conditions.

To handle this case, we have two choices, explicitly reinitialize energy storage variables and use the complete state space model starting with initial conditions, or find consistent switch states to complete specifying final conditions. Both approaches will be considered. A simple, as compared to the literature, explicit re-initialization equation will be derived first, followed by a method to find consistent switch states.

Given the state equation

$$M \frac{d}{dt}x = Ax + Bu + B_1 \frac{d}{dt}u$$

The equation above is the general form of a complete state space model. If switch states are not specified as part of the final conditions, then u and  $\dot{u}$  which depend on switch variables are unknowns. Thus the state equation is not completely specified. In the following analysis, we will attempt to derive explicit re-initialization equation independent of switch variables based on the state equation.

<sup>&</sup>lt;sup>4</sup> This section uses same matrix/vector naming notation from [7].

We can derive the re-initialization equation as follows:

$$x(t_o^+) = x(t_o^-) + \int_{t_o^-}^{t_o^+} \frac{d}{dt} x \, dt$$

$$x(t_o^+) = x(t_o^-) + \int_{t_o^-}^{t_o^+} M^{-1} \left( Ax + Bu + B_1 \frac{d}{dt} u \right) dt$$

$$x(t_o^+) = x(t_o^-) + M^{-1} B_1 \int_{t_o^-}^{t_o^+} \frac{d}{dt} u dt$$

The integral is non-zero only when the derivative is impulsive, and the equation becomes

$$x(t_0^+) = x(t_0^-) + M^{-1} B_1 (u(t_0^+) - u(t_0^-))$$

This equation appeared implicitly in the complete state space model, which allowed us to relate the final and the initial conditions. However, if the initial switch states at  $t_o^-$  are unknown, then so is  $u(t_o^-)$ . To work around this issue, notice the following set of equations. From the fundamental cut-set equations, we can derive the following equation:

$$\begin{bmatrix} F_{14}^t & 0 \\ 0 & F_{41} \end{bmatrix} u = \begin{bmatrix} F_{24}^t - I & 0 & 0 \\ 0 & 0 - I - F_{42} \end{bmatrix} \begin{pmatrix} v_c \\ i_l \end{pmatrix}$$

where  $u=\binom{v_{vs}}{i_{cs}}$  for all devices modeled as independent sources (including SFIS switches), and  $v_c$  and  $i_l$  are vectors of all capacitor voltages and all inductor currents respectively.

By inspecting the  $B_1$  matrix, we notice that  $\begin{bmatrix} F_{14}^t & 0 \\ 0 & F_{41} \end{bmatrix}$  is a right factor, thus let

$$K = \begin{bmatrix} F_{14}^t & 0 \\ 0 & F_{41} \end{bmatrix}$$

and let

$$B_1 = \hat{B}_1 K$$

Then we can rewrite our re-initialization equation as

$$x(t_o^+) = x(t_o^-) + M^{-1} \hat{B}_1 (Ku(t_o^+) - Ku(t_o^-))$$

by using the equation that links initial states with inputs, we obtain

$$x(t_o^+) = x(t_o^-) + M^{-1} \hat{B}_1 \left( Ku(t_o^+) - \begin{bmatrix} F_{24}^t - I & 0 & 0 \\ 0 & 0 - I - F_{42} \end{bmatrix} \begin{pmatrix} v_{vs}(t_o^-) \\ i_{cs}(t_o^-) \end{pmatrix} \right)$$

where  $u(t_o^+)$  is a vector of independent sources and zero entries for all switch variables.

This last equation allows us to reinitialize the state (find consistent initial conditions) given the incompletely specified final conditions and inputs. Notice that we are relying on the derivative of u for re-initialization. In other words, this formulation assumes that there exists a switch configuration such that all capacitor voltages and all inductor currents are states (independent)<sup>5</sup>. Otherwise the initial conditions of some elements will be ignored. This limitation can be eliminated using the same approach discussed in Section 3.5.

This last equation reveals an important fact about the necessity of knowing switch initial states at  $t_o^-$ . That is, since the equation does not depend on input values from  $t_o^-$  and thus does not depend on switch initial states, then we can opt to initialize our switches to any configuration such that at  $t_o^-$ , KVL, KCL, and energy storage element initial conditions are satisfied. This last statement can help us in cases where it is desired to have a fully specified final condition rather than attempting to find an explicit consistent initial condition. Also notice that because we will need the derivative of the switch variables,

<sup>&</sup>lt;sup>5</sup> This is an existence statement. It is not a requirement that the desired switch configuration satisfy this condition.

by same argument, we can simply solve for the voltages and currents of switches at  $t_o^-$  using any method we prefer, given we have chosen consistent switch states at  $t_o^-$ .

# 3.7 Network analysis in the presence of internally controlled switches and diodes

Internally controlled switch and diode variables are coupled with other network variables. Therefore, to include internally controlled switches in the network analysis, we must solve for all the variables of the switched network simultaneously. The simultaneous solution must consider the RLCM variables, KVL and KCL, switches control variables, and inputs. That is, it must find switch states, and accordingly switch voltages or currents, and properly deals with discontinuities in energy storage variables.

Attempts to find the simultaneous solution are rarely discussed in the literature. One interesting attempt was proposed by [6]. Their work assumes capacitor voltages and inductor currents are constant at the instant of switching. While the work is interesting, we desire to develop a simulator that is capable of analyzing any switched RLCM network without imposing any such constraints.

A consistent simultaneous solution can be found iteratively, without imposing continuity constraints on capacitor voltages and inductor currents. There are several valid iterative approaches, one of which is evaluating all possibilities to find the consistent ones (such as bond graph method). However, since the number of possibilities grows exponentially with the number of switches, this approach is not feasible. To overcome the exponential growth, we can iterate over topologies according to the intermediate analytical impulses in the network. That is, assume switch control is independent of network variables. Freeze time and final conditions, solve the network, and change switch states according to this new network solution. Keep iterating until all switches control variables are stable.

- 1. Freeze time at  $t_o$ , and freeze  $\binom{v_{vs}(t_0^-)}{i_{cs}(t_0^-)}$ , and  $u(t_0^-)$

- 2. Until switch states are stable

- a. Identify and update switches that must take a transition

- b. Use  $M_{\pi} \dot{x} = A_{\pi} x + B_{\pi} u + B_{\pi,1} \dot{u}$  and  $y = C_{\pi} x + D_{\pi} u + D_{\pi,1} \dot{u}$  of the new topology to evaluate switch control variables at  $t_0^+$ . In this step, use final conditions from step 1.

Step 2.b can be performed numerically as follows:

- 1. Numerically integrate x using  $M_{\pi} \dot{x} = A_{\pi} x + B_{\pi} u + B_{\pi,1} \dot{u}$  from  $t_0^-$  to  $t_0^+$ . The integration is equivalent to the explicit re-initialization:  $x(t_0^+) = x(t_0^-) + M^{-1} B_1(u(t_0^+) u(t_0^-))$ .

- 2. Evaluate variables of interest (needed for control) using  $y = C_{\pi} x(t_0^+) + D_{\pi} u(t_0^+) + D_{\pi,1} \dot{u}(t_0)$ .

The steps to evaluate control variables, given by the algorithm above, can be implemented to be automatic using the same infrastructure used to simulate the state space model in the open interval. However, because we are interested in a fixed time instant, we only make zero length integration steps. The implementation of this algorithm is simple.

## 3.8 **Design of the simulation algorithm**

Computer aided analysis and simulation require generalizable algorithms. Since we have a well-defined algorithm for constructing state space models, simulation based on the sequence of complete state space models methods is suitable. Each state space model is solved using numerical integration algorithms. At switch transition instants, the simultaneous solution for control equations and state space model equations is found iteratively, as in the earlier section. Figure 3.3 gives an overview of the simulation algorithm, and compares it with the common algorithm used in literature. Other than the computational simplicity of this method, this method abstracts the complexities of switch behavior during the search for correct switch states.

(a) Literature (b) This thesis

Figure 3.3 Simulation algorithm commonly used in literature as compared to algorithm in this thesis

# **Chapter 4 Software Design**

#### 4.1 Switched RLCM Network Simulator