# The Pennsylvania State University The Graduate School

#### A STUDY OF DRAM OPTIMIZATION TO BREAK THE MEMORY WALL

A Dissertation in Computer Science and Engineering by  ${\bf Tao~Zhang}$

© 2014 Tao Zhang

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

The dissertation of Tao Zhang was reviewed and approved\* by the following:

Yuan Xie

Professor of Department of Computer Science and Engineering Dissertation Advisor, Committee Chair

Mary Jane Irwin Professor of Department of Computer Science and Engineering Robert E. Noll Professor Evan Pugh Professor

Vijaykrishnan Narayanan Professor of Department of Computer Science and Engineering

Zhiwen Liu Associate Professor of Department of Electrical Engineering

Raj Acharya Professor of Department of Computer Science and Engineering Department Head

<sup>\*</sup>Signatures are on file in the Graduate School.

## **Abstract**

The well-known "Memory Wall" has been raised in 1990s. At that time, the researchers noticed the diverging exponential increase in the performance of processor and main memory and thus claimed that the main memory would eventually become the bottleneck of the entire computing system. Furthermore, benefiting from the semiconductor process scaling, the number of transistors in a single chip keeps growing up. As a result, microprocessor designs enter multi-/many-core era and the instruction level parallelism (ILP) and thread level parallelism (TLP) have been extensively exploited. The improved parallelism requires the memory to provide low latency, high bandwidth and low power consumption. Unfortunately, as the de facto main memory technology, the evolution of DRAM is relatively slow due to the poor scalability and the extremely high sensitivity of design cost (cost per bit). To this end, we are hitting the "Memory Wall".

To break the memory wall, enormous research work has been proposed to optimize the DRAM architecture so that a better trade-off among performance, power, and design overhead can be achieved. Some of the previous proposals, however, are difficult to be implemented because of either the unaffordable design overhead or the unacceptable performance degradation. Moreover, certain new issues have shown up along with the evolution of DRAM. For example, the performance impact of refresh cannot be ignored anymore as it can significantly degrade the DRAM performance. The power consumption of DRAM is also critical as up to 40% power is consumed by the DRAM modules, which are massively populated in the data centers. Therefore, in the DRAM realm it still needs lots of research efforts to make sure DRAM can win the war against the "Memory Wall". This is the motivation of this dissertation.

In this dissertation, the author proposes several novel DRAM architectures, which aims at a better trade-off among DRAM performance, power, and design overhead. Both traditional DRAM technologies and the emerging 3D-stacked DRAMs are covered in this work. To relieve the refresh penalty in the commodity DRAM, a concurrent refresh aware memory, CREAM, is proposed. CREAM allows refresh and memory access to be served in parallel. In addition, Half-DRAM is proposed to achieve power reduction and performance improvement simultaneously. In Half-DRAM, a bank is redesigned so that it is able to activate only half of a row to reduce the activation and precharge power. In this way, Half-DRAM can easily eliminate the power constraints and thus improve the performance. Meanwhile, two half-rows can be accessed in parallel to further improve the performance once the sub-array level parallelism is deployed. Furthermore, a new precharge policy, Lazy Precharge, is introduced to minimize the precharge overhead. By leveraging the Lazy Precharge, multiple activations can share a precharge so that the number of precharge can be reduced significantly. Furthermore, In addition to the traditional

2D DRAM, a novel 3D WideIO architecture is proposed to increase the DRAM parallelism. To take advantage of the increasing wiring resource in the vertical dimension, a bank is further split into multiple sub-banks. Each sub-bank can provide the full cacheline. Finally, a 3D SoC chip has been taped out to demonstrate the feasibility of 3D-stacked DRAM. In the chip, a 3D-stacked DRAM directly stacks on a two-layer logic chip. The experimental results show that the proposed optimizations can either effectively improve DRAM performance or significantly reduce DRAM power with negligible area overhead.

# **Table of Contents**

| List o                 | Figures                                                                | ix   |

|------------------------|------------------------------------------------------------------------|------|

| List o                 | Tables                                                                 | xiii |

| Ackno                  | rledgments                                                             | xiv  |

| Chapt                  | r 1                                                                    |      |

| $\mathbf{Int}$         | oduction                                                               | 1    |

| 1.1                    | The "Memory Wall"                                                      | 1    |

| 1.2                    | The Response From The Industry                                         | 2    |

| 1.3                    | The DRAM Hierarchy                                                     | 4    |

| 1.4                    | The Preliminary Of DRAM Commands                                       | 5    |

| 1.5                    | The Structure Of The Dissertation                                      | 7    |

| Chapt                  | r 2                                                                    |      |

| $\mathbf{C}\mathbf{R}$ | AM: The Relax Of Refresh Penalty                                       | 8    |

| 2.1                    | Background And Motivation                                              | 9    |

|                        | 2.1.1 Preliminary Of DRAM Refresh                                      | 9    |

|                        | 2.1.2 The Source Of Refresh Penalty                                    | 10   |

|                        | 2.1.3 Power Constraint—The Secondary Cause                             | 11   |

|                        | 2.1.4 The Ineffectiveness Of Existing Refresh Scheduling Methods       | 13   |

| 2.2                    | The Proposed Memory Architecture – CREAM                               | 14   |

|                        | 2.2.1 Sub-Array-Level Refresh (SALR): Reduction Of Refresh Conflicts   | 14   |

|                        | 2.2.2 Sub-Rank-Level Refresh (SRLR): Consideration Of Power Constraint | 15   |

|                        | 2.2.3 The Combination Of SALR And SRLR                                 | 16   |

|                        | 2.2.4 Refresh-Aware Optimization                                       | 17   |

|                        | 2.2.4.1 Sub-Array Round-Robin                                          | 17   |

|                        | 2.2.4.2 Dynamic Refresh Scheduling                                     | 17   |

| 2.3                    | The Design Of CREAM                                                    | 18   |

|                        | 2.3.1 Protocol Change For Dynamic Scheduling And PAAR                  | 18   |

|                        | 2.3.2 The Enabling Technology For SALR                                 | 19   |

|                        | 2.3.3 Design Overhead Analysis                                         | 20   |

|                        | 2.3.3.1 Overhead On DRAM Chip                                          | 20   |

|        | 2        | 2.3.3.2 Interface Protocol Change                   |

|--------|----------|-----------------------------------------------------|

| 2.4    | Evaluati | ion Results                                         |

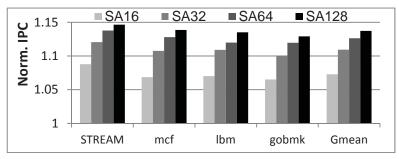

|        | 2.4.1 I  | Design Space Exploration                            |

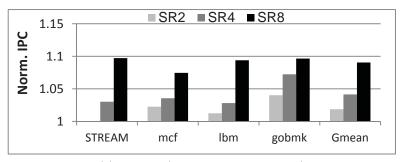

|        | 2.4.2 S  | Single-Core Simulation Results                      |

|        | 2        | 2.4.2.1 Proof Of Effectiveness Of SALR              |

|        | 2        | 2.4.2.2 Effectiveness Of Dynamic Refresh Scheduling |

|        | 2.4.3 S  | Sensitivity Study                                   |

|        |          | 2.4.3.1 Core Number And Memory Size                 |

|        | 2        | 2.4.3.2 Relax Of Power Constraint                   |

|        |          | 2.4.3.3 Address Mapping Policy                      |

|        |          | 2.4.3.4 Smaller Refresh Cycle                       |

| 2.5    |          | on                                                  |

| 2.0    |          | Integration Of Partial Array Self Refresh (PASR)    |

|        |          | Support For 3D-stacked DRAM                         |

|        |          | Fine Scalability For Future Refresh Technology      |

| 2.6    |          | Work                                                |

| 2.0    |          | Concurrent Refresh                                  |

|        |          | Refresh Deferring                                   |

|        |          | Refresh Reduction                                   |

|        |          | Refresh Prediction                                  |

| 2.7    |          | y                                                   |

| 2.1    | Summai   | y                                                   |

| Chapte | er 3     |                                                     |

| _      |          | I: The Rethinking Of Fine-grained Activation 30     |

| 3.1    |          | und And Motivation                                  |

|        |          | The DRAM Power Breakdown                            |

|        |          | Row Overfetching And N-bit Prefetching              |

|        |          | The Opportunity For Activation Power Reduction      |

|        |          | The Dilemma Of Fine-Grained Activation              |

| 3.2    |          | sign Of Half-DRAM                                   |

|        |          |                                                     |

|        |          | Half Active DRAM                                    |

|        |          | Half-Size Row Buffer: Challenge Or Opportunity      |

|        |          | Chance Of Improving Memory Parallelism              |

| 3.3    |          | Overhead Analysis                                   |

| 3.4    |          | ion Results                                         |

| 9      |          | Performance Analysis                                |

|        |          | Power Analysis                                      |

|        |          | The Effect Of The Relaxation of Power Constraint    |

|        |          | 3.4.3.1 Impact Of Four-Activation-Window Constraint |

|        | _        | 3.4.3.2 A Case Study Of Half-DRAM                   |

| 3.5    | _        | Work                                                |

| 3.6    |          | work                                                |

| Chapt                       | er 4                                                            |    |

|-----------------------------|-----------------------------------------------------------------|----|

| Laz                         | y Precharge: The Reduction Of Precharge Overhead                | 50 |

| 4.1                         | Background                                                      | 51 |

| 4.2                         | Design Of Lazy Precharge                                        | 52 |

|                             | 4.2.1 Overhead Of Precharge                                     | 52 |

|                             | 4.2.2 DRAM Chip Design                                          | 53 |

|                             | 4.2.3 DRAM Controller Design                                    | 54 |

| 4.3                         | Evaluation Results                                              | 56 |

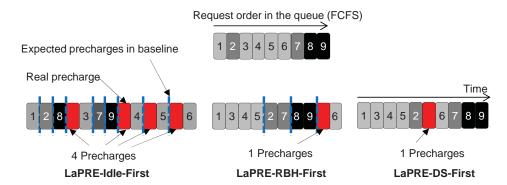

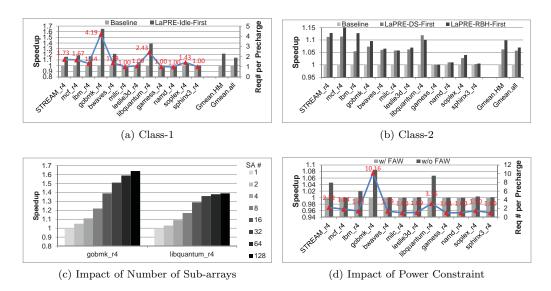

|                             | 4.3.1 Performance Analysis                                      | 57 |

|                             | 4.3.2 Sensitivity Study                                         | 58 |

|                             | 4.3.2.1 Impact Of Number Of Sub-arrays                          | 58 |

|                             | 4.3.2.2 Impact Of Power Constraint                              | 59 |

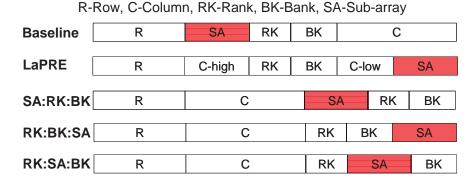

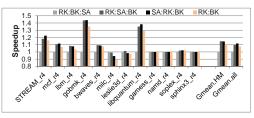

|                             | 4.3.2.3 Impact Of Address Mapping Scheme                        | 59 |

| 4.4                         | Related Work                                                    | 60 |

| 4.5                         | Summary                                                         | 61 |

|                             |                                                                 |    |

| Chapt                       |                                                                 |    |

|                             | -SWIFT: Enabling Sub-array Level Parallelism In 3D Wide-IO DRAM | 62 |

| 5.1                         | Background And Motivation                                       | 63 |

|                             | 5.1.1 The Limitations Of 2D DRAM                                | 64 |

|                             | 5.1.2 The Disadvantage Of Wide-IO                               | 64 |

|                             | 5.1.3 Rationale Of 3D-SWIFT                                     | 65 |

| 5.2                         | 3D-SWIFT-A Novel Wide-IO DRAM                                   | 66 |

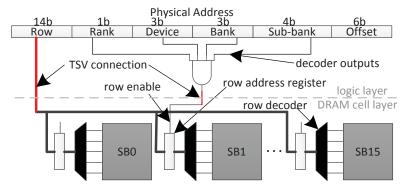

|                             | 5.2.1 Fine-Grained Memory Architecture                          | 67 |

|                             | 5.2.2 Adoption Of Close-Page Policy                             | 68 |

|                             | 5.2.3 Sub-bank Autonomy                                         | 69 |

|                             | 5.2.4 Packet-Based Interface Protocol                           | 69 |

|                             | 5.2.5 Hierarchical Bus                                          | 69 |

|                             | 5.2.6 Address Decoding                                          | 70 |

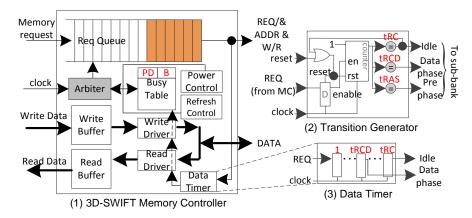

|                             | 5.2.7 The Design Of Memory Controller                           | 71 |

| 5.3                         | Design Overhead Analysis                                        | 72 |

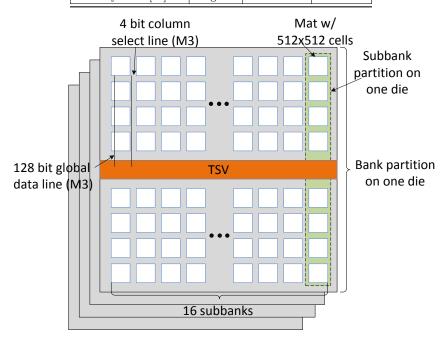

|                             | 5.3.1 Sub-bank DRAM Floorplan                                   | 72 |

|                             | 5.3.2 TSV Overhead                                              | 74 |

| 5.4                         | Experiment                                                      | 75 |

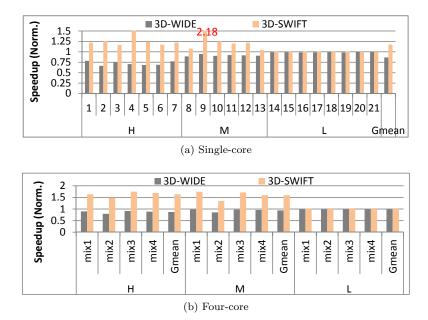

|                             | 5.4.1 Single-Core Simulation                                    | 75 |

|                             | 5.4.2 Four-Core Simulation                                      | 77 |

|                             | 5.4.3 Impact Of Power Constraint (tTAW)                         | 77 |

|                             | 5.4.4 Address Mapping                                           | 78 |

| 5.5                         | Related Work                                                    | 78 |

|                             | 5.5.1 Related Work in Conventional 2D DRAM Architecture         | 78 |

|                             | 5.5.2 Related Work in 3D DRAM Architecture                      | 79 |

| 5.6                         | Summary                                                         | 79 |

|                             |                                                                 |    |

| Chapt                       |                                                                 |    |

| $\operatorname{Th}\epsilon$ | e Prototype Chip Tapeout Of A 3D SoC With 3D-Stacked DRAM       | 80 |

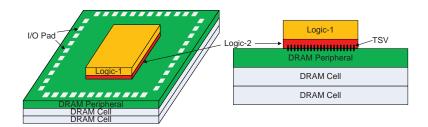

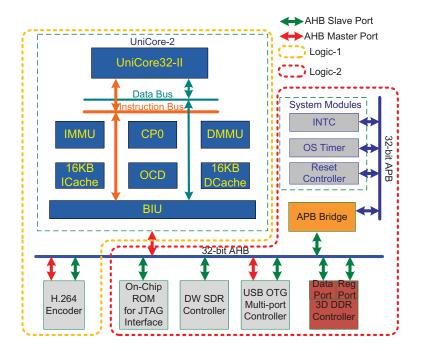

| 6.1                         | Chip Overview                                                   | 80 |

|                             | 6.1.1 The Architecture Of 3D SoC                                | 80 |

|                             | 6.1.2 The Use Of 3D-Stacked DRAM                                | 81 |

| 6.2     | $3D O_1$ | otimization                    | 82 |

|---------|----------|--------------------------------|----|

|         | 6.2.1    | Parallel Access Policy         | 82 |

|         | 6.2.2    | TSV Clustering                 | 83 |

| 6.3     | The F    | Proposed Design Flow           | 84 |

|         | 6.3.1    | Divide and Conquer Methodology | 84 |

|         |          | Front-End Design               |    |

|         | 6.3.3    | Back-End Design                | 85 |

|         | 6.3.4    | Power Delivery                 | 87 |

| 6.4     | Summ     | ary                            | 88 |

| Chapte  | er 7     |                                |    |

| Cor     | ıclusio  | n and Future Work              | 89 |

| Bibliog | graphy   |                                | 92 |

# **List of Figures**

| 1.1<br>1.2        | The performance divergence between processor and memory                                                                                                    | 2               |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|                   | generation of DDR $x$ family. LPDDR $x$ is introduced to reduce the power con-                                                                             |                 |

|                   | sumption. In addition, 3D-stacked DRAMs, including Wide-IO and HMC, are                                                                                    |                 |

|                   | invented to provide high bandwidth with low power consumption                                                                                              | 9               |

| 1.3               | DRAM hierarchy – a 2Gb-8bank×16 example                                                                                                                    | 4               |

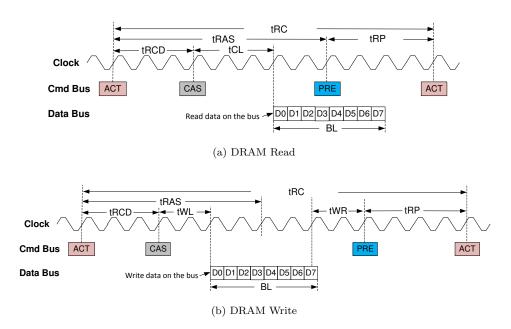

| 1.4               | DRAM commands for read and write transaction. Note that a write can lock a                                                                                 |                 |

|                   | bank for a longer time before the bank can be closed (precharged)                                                                                          | 6               |

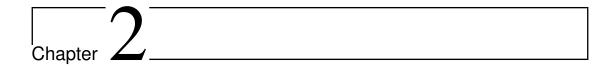

| 2.1               | Refresh basics. (a) Burst refresh; (b) Distributed refresh; (c) Refresh command                                                                            |                 |

|                   | and related timing constraints; (d) impact of power constraint on performance                                                                              | G               |

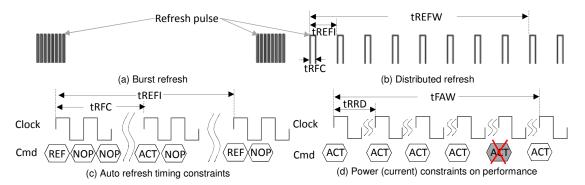

| 2.2               | The motivation experimental results. (a) performance gain without refresh as                                                                               |                 |

|                   | chip size ranges from 1Gb to 16Gb; (b) the ineffectiveness of fine-grained refresh                                                                         |                 |

|                   | in DDR4; both $\times 2$ and $\times 4$ modes are shown by the normalized IPC to the baseline                                                              |                 |

|                   | ×1 mode; (c) the ineffectiveness of ER; (d) cause of ER's failure                                                                                          | 12              |

| 2.3               | Enabler of concurrent refresh. Left: a refresh in a sub-array is a two-stage oper-                                                                         |                 |

|                   | ation. The row is firstly open to recharge the cell and then the row is closed by                                                                          |                 |

|                   | a precharge. Right: a refresh and an activation can be performed concurrently in                                                                           |                 |

|                   | any banks as long as no sub-array conflict occurs                                                                                                          | 15              |

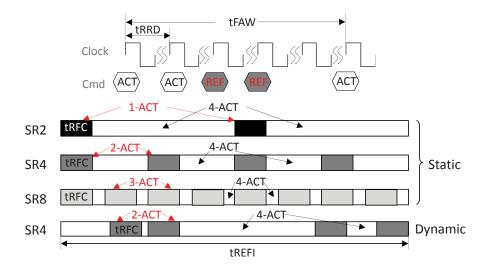

| 2.4               | The different capabilities of concurrency in SR2, SR4 and SR8 refresh. A refresh                                                                           |                 |

|                   | in SR4 occupies two slots in the four-activation window based on current con-                                                                              |                 |

|                   | sumption. As a result, only two ACTs are available during a refresh. Similarly,                                                                            | 1.5             |

| 0.5               | one and three ACTs are available in SR2 and SR8, respectively.                                                                                             | 17              |

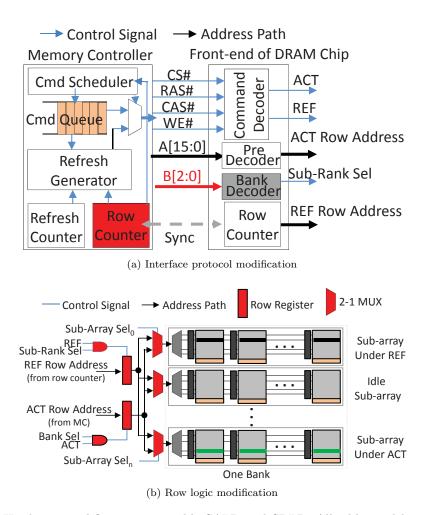

| 2.5               | Hardware modifications to enable SALR and SRLR. All additional logics are highlighted in red. (a) Quasi-ROR is employed to put sub-rank ID on BA[2:0]; (b) |                 |

|                   | Two registers are used to separate refresh row address and activation row address.                                                                         | 19              |

| 2.6               | Design space exploration for sub-rank and sub-array number                                                                                                 | 21              |

| $\frac{2.0}{2.7}$ | One-core simulation results with 4GB memory. All results are normalized to IR.                                                                             | $\frac{21}{22}$ |

| 2.8               | Refresh conflict number under SRLR-only and SR                                                                                                             | 24              |

| 2.9               | Four-core simulation with 8GB memory. All results are normalized to IR                                                                                     | 25              |

| 2.10              | · · · · · · · · · · · · · · · · · · ·                                                                                                                      | (               |

| 0                 | SR4(S); In (b) and (c), all results are normalized to No Refresh                                                                                           | 26              |

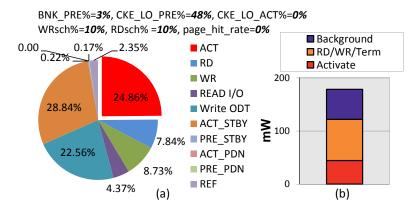

| 3 1               | Power breakdown of STREAM                                                                                                                                  | 39              |

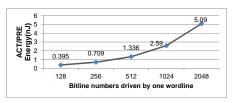

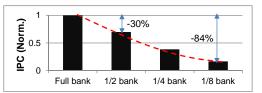

| 3.2               | Motivation study. (a) The activation/precharge energy proportionality to the number of bitlines based on CACTI-3DD [1]; (b) The Impact of reduced data bandwidth in prior work [2, 3]. These are simulation results of the STREAM                                                                                             |          |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

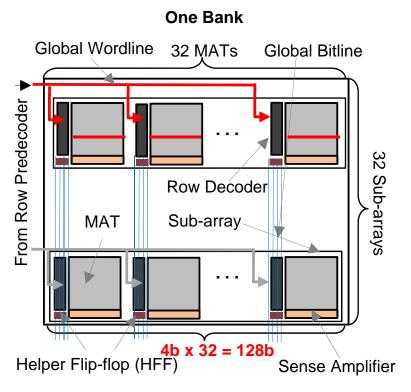

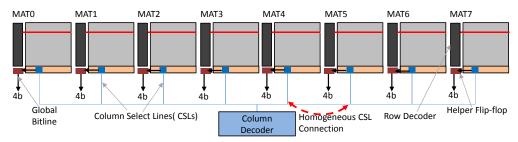

| 3.3               | benchmark, and are normalized to the speedup of the baseline full bank activation. Zoom-in view of the fine-grained structure inside one DRAM bank. The bank has 32 sub-arrays and each sub-array contains 32 MATs. Global bitlines are shared                                                                                | 33       |

|                   | by all sub-arrays. Every MAT can only provides 4b data to form 128b/bank data width                                                                                                                                                                                                                                           | 35       |

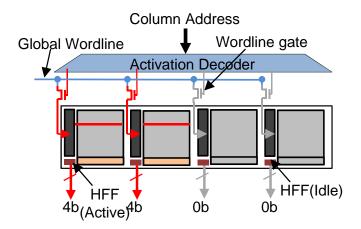

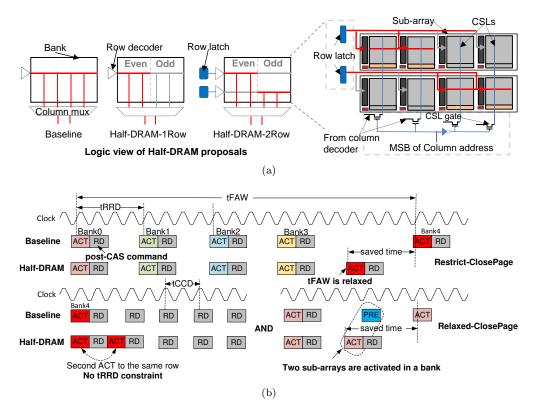

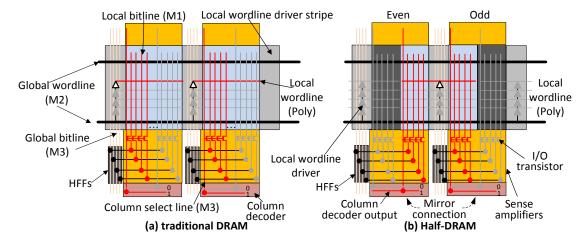

| 3.4               | Fine-grained activation in prior work [2, 3]. An activation decoder is introduced to control the number of active MATs. However, halving the active MATs also halves the data width and thus reduces bandwidth                                                                                                                | 36       |

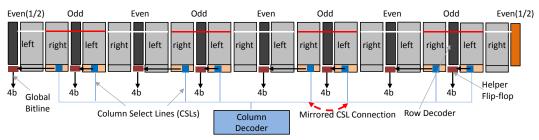

| 3.5               | The reorganization of sub-array in Half-DRAM. (a) Traditional sub-array. The one-to-one relationship exists between row decoder and HFF since the row decoder drives the entire wordline of one MAT; (b) A MAT is split into "left" and "right" block and they are driven by different row address decoders. The sub-array is |          |

| 3.6               | further divided into Odd and Even groups                                                                                                                                                                                                                                                                                      | 37       |

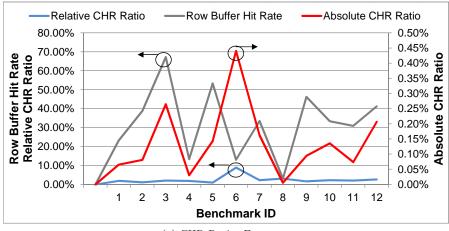

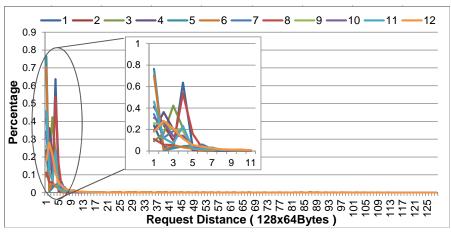

| 3.7               | indicates the great opportunity for Half-DRAM                                                                                                                                                                                                                                                                                 | 38       |

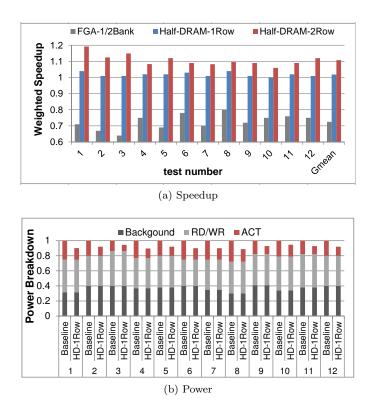

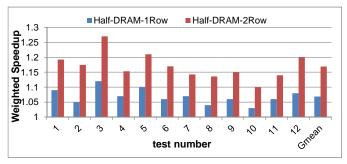

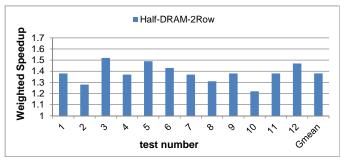

| 3.8               | tFAW as well as the integration of sub-array level parallelism [4] for performance improvement                                                                                                                                                                                                                                | 40       |

| 3.9               | in an Odd MAT                                                                                                                                                                                                                                                                                                                 | 42       |

| 3.10              | bank activation in prior work [2, 3]. The burst length of FGA-1/2Bank is 16 Simulation results of power constraint study. Restrict-ClosePage management policy is applied. (a) Weighted speedup by relaxing tFAW constraint; (b) Better performance improvement due to higher tFAW penalty in Wide-IO                         | 47       |

| 4.1               | The circuit operation of activation and precharge                                                                                                                                                                                                                                                                             | 52       |

| 4.2<br>4.3<br>4.4 | Timing diagram of the three different memory access schemes                                                                                                                                                                                                                                                                   | 53<br>56 |

| 4.5<br>4.6        | of Sub-arrays; (d) Impact of Power Constraint                                                                                                                                                                                                                                                                                 | 58<br>59 |

|                   | (f) Evidence of the importance of bank-level parallelism                                                                                                                                                                                                                                                                      | 60       |

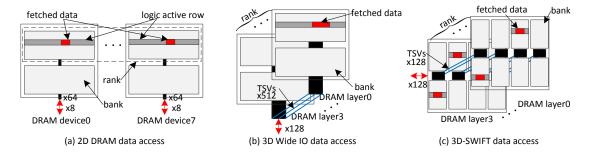

| 5.1  | Data access mechanisms in different memories. (a) DDR3: the data is distributed over all devices in a rank. Only a small fraction of row is fetched in each memory access; (b) Wide-IO: the data is placed in a large row and no individual device |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | exists. Still only a portion of data is fetched; (c) 3D-SWIFT: the width of fetched                                                                                                                                                                |    |

|      | data matches cacheline width. The rest of row is idle                                                                                                                                                                                              | 63 |

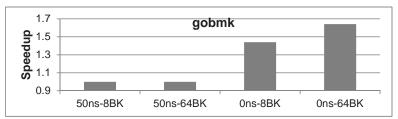

| 5.2  | The impact of power constraint on 3D DRAM. The simulation is done with 8/64                                                                                                                                                                        |    |

|      | banks(BK) and tTAW=50ns/0ns (see Section 5.4 for the details of simulation settings)                                                                                                                                                               | 65 |

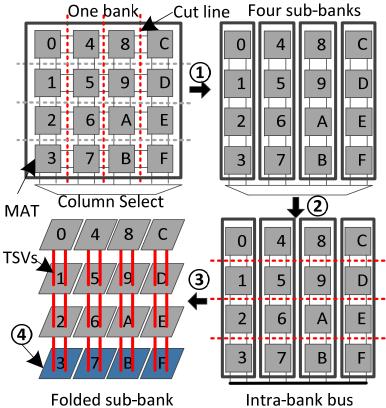

| 5.3  | The fundamental of 3D-SWIFT. Four optimizations are illustrated: 1) A bank is                                                                                                                                                                      |    |

| 0.0  | partitioned into four sub-banks; 2) The column multiplexing is replaced by intrabank bus; 3) A sub-bank is further folded into four layers; 4) A local MAT is                                                                                      |    |

|      | dedicated to store ECC code                                                                                                                                                                                                                        | 67 |

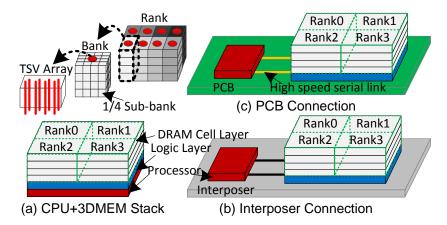

| 5.4  | 3D-SWIFT memory subsystem and possible applications. (a) 3D-SWIFT directly stacks on the top of CPU; (b) 3D-SWIFT is connected to CPU by interposer; (c)                                                                                           | 07 |

|      | 3D-SWIFT is placed on PCB with high speed links. Multiple 3D-SWIFTs can be                                                                                                                                                                         |    |

|      | populated to provide large memory capacity (not shown)                                                                                                                                                                                             | 68 |

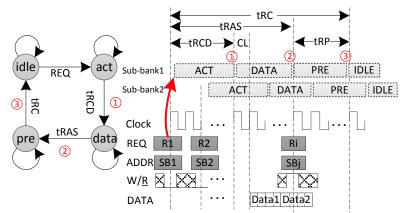

| 5.5  | Packet-based interface protocol. Memory controller only issues REQ to initiate a                                                                                                                                                                   |    |

|      | memory access. The sub-bank can complete the data transfer and precharge to                                                                                                                                                                        |    |

|      | close the row automatically.                                                                                                                                                                                                                       | 70 |

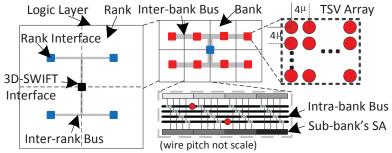

| 5.6  | Hierarchical I/O bus. The intra-bank bus, TSV array and inter-bank bus are                                                                                                                                                                         |    |

|      | 512-bit and inter-rank bus is 128-bit. Each rank interface has a data buffer for                                                                                                                                                                   |    |

|      | the 4-beat burst (not shown)                                                                                                                                                                                                                       | 70 |

| 5.7  | Address decoding and early sub-bank select. The full address is decoded by rank,                                                                                                                                                                   |    |

|      | device, bank, and sub-bank decoders and a "row enable" signal is asserted to latch<br>the row address. MC is responsible for the freedom of sub-bank conflict so that                                                                              |    |

|      | no second "row enable" is asserted to an active sub-bank                                                                                                                                                                                           | 71 |

| 5.8  | Memory controller design in 3D-SWIFT. (1) Memory controller; (2) Transition generator; (3) Data timer. The length of the counter and shifter are determined                                                                                        |    |

|      | by the cycle number of tRC                                                                                                                                                                                                                         | 71 |

| 5.9  | The Floorplan of 3D-SWIFT. A bank consists of 32 mats and each mat is 256Kb                                                                                                                                                                        |    |

|      | $(512\times512)$                                                                                                                                                                                                                                   | 73 |

| 5.10 | Performance results of single-core and 4-core simulation. All results are normal-                                                                                                                                                                  |    |

|      | ized to 2D DRAM design                                                                                                                                                                                                                             | 76 |

| 5.11 | Sensitivity Study. (a) Impact of tTAW; (b) Performance with different address                                                                                                                                                                      |    |

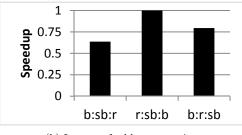

|      | mapping schemes. "r"-row, "b"-bank, "sb"-sub-bank                                                                                                                                                                                                  | 77 |

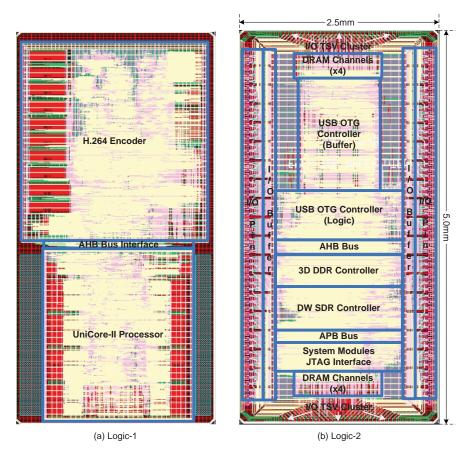

| 6.1  | 3D SoC with On-chip Memory. The 3D SoC consists of five dies: two logic dies                                                                                                                                                                       |    |

|      | and three DRAM dies. The two logic dies are stacked together via micro-bumps                                                                                                                                                                       |    |

|      | in a fashion of Face-to-Face (F2F). In addition, Logic-2 is thinned to expose TSV                                                                                                                                                                  |    |

|      | for the communication with the 3D DRAM. The 3D DRAM is composed of one                                                                                                                                                                             |    |

|      | peripheral die and two cell dies. It can provide eight independent channels while                                                                                                                                                                  |    |

|      | we use four of them in this work                                                                                                                                                                                                                   | 81 |

| 6.2  | Block View of 3D SoC. We reuse the SoC from Peking University, where it employs a UniCore RISC processor. The SoC is partitioned into two parts that are mapped to Logic 1 and Logic 2 respectively. Note that the 2D DRAM controller is placed    |    |

|      | to Logic-1 and Logic-2, respectively. Note that the 3D DRAM controller is placed on Logic-2 so that it is close to the 3D DRAM                                                                                                                     | 81 |

|      | on rogic-2 by man in is close to me or ritam                                                                                                                                                                                                       | OI |

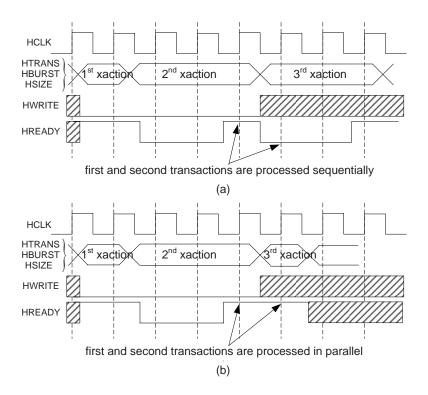

| 6.3 | Parallel Access Policy. a) the transaction in the conventional memory controller.                                                                            |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | The first and second transactions are processed sequentially, which cannot be                                                                                |     |

|     | hidden due to the lack of parallelism; b) the transaction in the proposed 3D                                                                                 |     |

|     | memory controller. The first and second transaction can be issued in parallel due                                                                            |     |

|     | to the increasing channels in 3D DRAM                                                                                                                        | 83  |

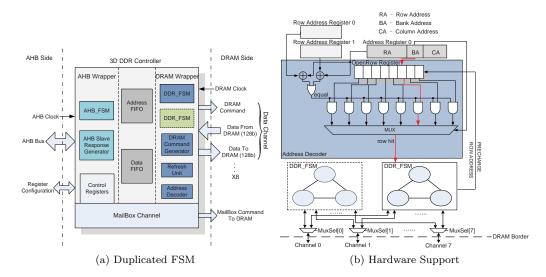

| 6.4 | Block Diagram of 3D DRAM Controller. a) two FSMs are deployed to improve the overall bandwidth. Asynchronous FIFOs are used to deal with the synchronization |     |

|     | between AHB clock domain and DRAM clock domain; b) The design detail of the                                                                                  |     |

|     | memory controller                                                                                                                                            | 84  |

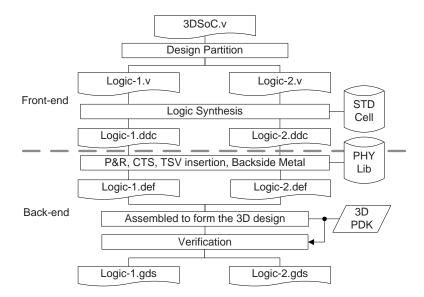

| 6.5 | 3D SoC Design Flow. The flow is divided into front-end and back-end. The                                                                                     |     |

|     | front-end flow mainly contains the design partition and logic synthesis. The back-                                                                           |     |

|     | end flow runs various design rule checking and TSV insertion. The merge of two                                                                               |     |

|     | netlists is also done in the back-end                                                                                                                        | 85  |

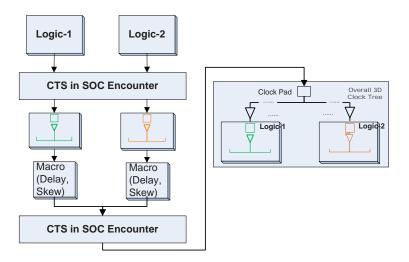

| 6.6 | An example of Divide and Conquer methodology. Firstly, CTS is conducted in                                                                                   |     |

|     | Logic-1 and Logic-2 separately. Then the overall clock tree is built once the two                                                                            | 0.0 |

|     | netlists are integrated                                                                                                                                      | 86  |

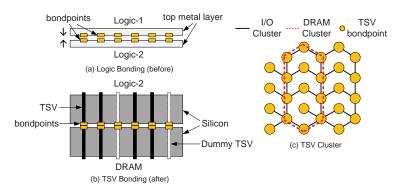

| 6.7 | 3D Bonding. a) logic bonding. Logic-1 and Logic-2 are bonded face-to-face.                                                                                   |     |

|     | The bond-point is predefined in the top metal layer of each die; b) Similar to                                                                               |     |

|     | logic bonding, the TSV is bonded in the back-side metal layer; c) multiple TSVs                                                                              |     |

|     | compose a TSV cluster to enhance the reliability and connectivity                                                                                            | 86  |

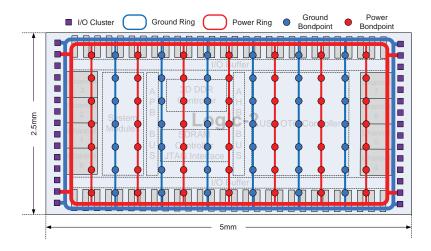

| 6.8 | Power Delivery Network on Logic-2. The power and ground ring are placed at the                                                                               |     |

|     | edge of the chip while they are placed alternatively in the middle to supply the                                                                             |     |

|     | power to the devices                                                                                                                                         | 87  |

| 6.9 | Layout of Two Logic Tiers. I/O TSVs are placed on the top and bottom edge of                                                                                 |     |

|     | Logic-2. In addition, the eight DRAM channels are divided into two groups and                                                                                |     |

|     | placed on the top and bottom as well.                                                                                                                        | 88  |

# **List of Tables**

| 2.1 | Refresh related parameters with various DRAM capacities (based on Micron |

|-----|--------------------------------------------------------------------------|

|     | DDR3-1333 data sheet)                                                    |

| 2.2 | Settings for fine-grained refresh in DDR4 [6]                            |

| 2.3 | Synthesis Result Comparison for a 2Gb DRAM Chip                          |

| 2.4 | Simulation Platform Configuration                                        |

| 2.5 | Benchmark Classification and Model Settings                              |

| 3.1 | DRAM Area and Power Breakdown by CACTI-3DD [1]                           |

| 3.2 | Power Parameters based on Micron Datasheet [7]                           |

| 3.3 | Simulation Platform Configuration                                        |

| 4.1 | Timing Parameters from Micron Data sheet [8]                             |

| 4.2 | New Timing Constraints on Activation                                     |

| 4.3 | Simulation Configuration                                                 |

| 5.1 | Hardware Implementation Summary                                          |

| 5.2 | Simulation Platform Configuration                                        |

| 5.3 | Benchmark Classification                                                 |

| 5.4 | DRAM Configurations                                                      |

| 6.1 | Parameters of 3D DRAM                                                    |

| 6.2 | TSV Parameters                                                           |

| 6.3 | System Design Summary                                                    |

# **Acknowledgments**

My sincerest gratitude is definitely to Dr. Yuan Xie, who is my research advisor in the past six years and is also my dissertation advisor. I would like to thank him to give me the chance to work in the great team with exciting research topics. In addition to his guidance, support, and encouragement in the research activities, he also helps me recognize my weaknesses and does his best to let me know how to be stronger. Moreover, he provides me enormous opportunities to meet and communicate with other leading researchers in the world. I can't imagine how I can graduate without his constant advising and guidance.

I also want to thank Dr. Mary Jane Irwin, Dr. Vijay Narayanan, and Dr. Zhiwen Liu. As the committee members, they give me constructive advices and helps throughout my research activities. Dr. Irwin teaches me how to design a partial product multiplier, which is finally implemented in a 3D chip. Dr. Vijay helps a lot on the 3D chip design. He even funds me a laptop that I use in the daily study. Dr. Zhiwen Liu shows me the possibility of silicon-compatible Y-shape optical splitter, which is also presented in one of my papers. It is my pleasure to work with them in my prior work. I am looking forward to the collaboration in my future research.

I would like to thank Dr. Xu Cheng, Dr. Dong Tong, Dr. Yi Feng, Dr. Kui Wang, and Dr. Junlin Lu from Peking University, Dr. Shau-Yin Tseng, Dr. Yi-Ta Wu from Industrial Technology Research Institute (Taiwan), Dr. Youn-Long Lin and Dr. Tingting Hwang from National Tsing Hua University, Dr. Eren Kursun from IBM Research, Dr. Jie Liu, Dr. Nissanka B. Priyantha and Dr. Aman Kansal from Microsoft Research, Dr. Heitor S. Ramos from Federal University of Alagoas, Dr. Ke Chen from Oracle Corporation, Dr. Frank Mueller and Dr. Paul D. Franzon from North Carolina State University, Dr. Jia Di from University of Arkansas. We have closely collaborated in various work and publications. I believe the great work relationship can continue in my new career.

Thanks a lot to the previous and present MDL members: Dr. Jin Ouyang, Cong Xu, Matthew Poremba, Jing Xie, Dr. Yibo Chen, Dr. Mike Debole, Qiaosha Zou, Dr. Lian Duan, Jishen Zhao, Hsiang-Yun Cheng, Dr. Xiangyu Dong, Dr. Xiaoxia Wu, Karthik Swaminathan, Dr. Yang Ding, Dr. Kevin Irick and Misun Park. In particular, I want to thank Dr. Guangyu Sun, who is one of my best friends and research partners for his help in my research and life. Also, I want to thank Dr. Raj Acharya (department head), Kathy Zimmerman, Cindy Milliron, Beth Kennedy, Annie Royer, and Karen Corl for their many helps on the administrative work. I am proud of working with them and I do remember it in my mind forever: WE ARE PENN STATE!

Finally, I give my deepest gratitude to my family. I know my parents always give silently but never ask for any return from me. I can feel their love forever. Also, I owe my wife Dan Zhu a lot because she does great sacrifice to support me.

# **Dedication**

This dissertation is dedicated to my parents and my wife for their endless love, support and encouragement throughout my life.

# Introduction

In this chapter, we first briefly review the "Memory Wall" as the motivation of the work shown in the following chapters. We then summarize the various DRAM types as the response from the industry to the "Memory Wall". Afterwards, we show the DRAM hierarchy in which all our optimization schemes occur in this work. Finally, we depict the basic DRAM commands, including Activate (ACT), Read, Write, Precharge (PRE) and Refresh (REF), along with the introduction of command timing analysis.

## 1.1 The "Memory Wall"

The term "Memory Wall" can be traced back to 1994, when Dr. Wulf and Dr. McKee firstly raised the word in their short paper [9]. Their concern is that the main memory will finally become the bottleneck of the whole computing system due to the diverging exponential increase in the performance of process and main memory. Equation 1.1 is given in the paper to explain the cause of memory wall, which calculates the overall access time for a memory request. As shown, the access time is determined by the performance of the processor  $(T_{core})^1$ , the performance of main memory  $(T_{mem})$  and the cache hit rate  $(P_{cache\_hit})$ . Given the modern processor has high cache hit rate (>90%), the performance of CPU dominates the overall access time as long as  $T_{mem}$  is comparable to  $T_{core}$ .

$$T_{total} = T_{core} \times P_{cache,hit} + T_{mem} \times (1 - P_{cache,hit}) [9]$$

(1.1)

Unfortunately, as the *de facto* main memory, DRAM technology turns out to be difficult to keep the pace with the processor scaling. By leveraging the "Moore's Law", processor performance can be doubled in every 18-24 months. Even though DRAM capacity can catch up the

<sup>&</sup>lt;sup>1</sup>The paper assumes the processor and cache have the same performance. Also, the authors consider a uniform cache access (UCA) architecture.

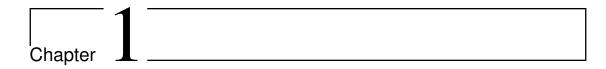

Figure 1.1: The performance divergence between processor and memory.

speed, DRAM performance can only be improved by 7% per year. Therefore, the performance gap between processor and memory increases exponentially, which is shown in Figure 1.1. As a consequence, the memory will eventually be dominant in the system performance and thus become the system bottleneck.

In fact, only the access latency is considered in the paper as the criteria of memory wall. In addition to the aforementioned latency issue, DRAM also needs to face the design challenges from the increasing bandwidth requirement, the reduction of power consumption, and the desire to further scale down the feature size. As a result, the memory wall is four-fold today: 1) Latency, 2) Bandwidth, 3) Power, and 4) Scalability. In this work, the first three issues are addressed with the corresponding optimization proposals. The goal is to make a better design trade-off among the latency, bandwidth and power. Furthermore, the design overhead is carefully analyzed to make sure the optimization schemes are practical.

## 1.2 The Response From The Industry

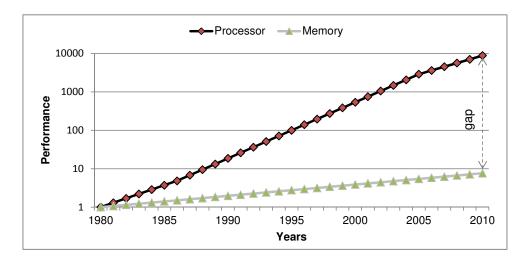

To win the war against "Memory Wall", the DRAM industry works hard to develop various DRAMs as the response to the increasing system requirements. Figure 1.2 illustrates the evolution of DRAM technologies. In particular, there are two DRAM families shown in the figure: DDRx and LPDDRx. Each family has advanced to the fourth generation (DDR4 [6] and LPDDR4 [10], respectively). DDRx is a high-performance DRAM that is usually used in PC, server and network processors. In contrast, LPDDRx is a low-power DRAM that is widely used in the mobile devices. Furthermore, some 3D-stacked DRAMs, such as Wide-IO [11], High Bandwidth Memory (HBM) [12] and Hybrid Memory Cube (HMC) [13], have been proposed in recent years. All these DRAMs are targeting at addressing one or multiple aforementioned challenges. The industry's solution can be summarized as follows.

Figure 1.2: The evolution of DRAM technology. The operating frequency doubles in each generation of DDRx family. LPDDRx is introduced to reduce the power consumption. In addition, 3D-stacked DRAMs, including Wide-IO and HMC, are invented to provide high bandwidth with low power consumption.

- Latency reduction. Micron has shipped Reduced-Latency DRAM (RLDRAM) [14], which has smaller access latency. Similarly, Fujitsu has invented Fast-Cycle DRAM (FCRAM) [15] to obtain less access latency. The access latency of these two memories is improved due to the smaller load on the wordline in a smaller bank. In addition, a higher voltage is usually applied on the wordline to speed up the row opening<sup>2</sup>.

- Bandwidth improvement. As the bandwidth is calculated as the product of data width and operating frequency (shown in Equation 1.2), DRAM vendors are striving to enhance both factors to improve the bandwidth. As shown in Figure 1.2, in each generation (from DDR [16] to DDR4), the data rate (2×frequency) is doubled to provide 2X bandwidth. HMC can even achieve up to 15Gbps data rate. On the other hand, Wide-IO and HBM have been proposed to increase the data width. Distinct from DDRx family in which the data is usually 64-bit wide, Wide-IO supports 512-bit data. HBM can even provide 1024-bit data via 8 channels.

$$\mathbf{B}_{DataBandwidth} = \mathbf{W}_{DataWidth} \times \mathbf{F}_{DataFrequency} \tag{1.2}$$

• Power reduction. The power reduction is achieved in two ways. First of all, the supply voltage drops in the DDRx family. As shown in Figure 1.2, the power supply that is 2.5V

<sup>&</sup>lt;sup>2</sup>Please see Section 1.3 for the definition of these terms

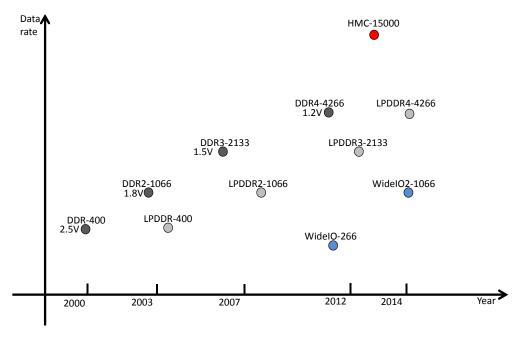

Figure 1.3: DRAM hierarchy – a 2Gb-8bank×16 example

in DDR shrinks to only 1.2V in DDR4. Both the dynamic and static power benefits from the supply voltage drop. Moreover, Low-power DDR DRAM (LPDDR) [17] (a.k.a. mobile DRAM) is introduced to further reduce the power. LPDDR has even smaller voltage than DDR. In LPDDR2 [18], the on-die termination (ODT) logic and delay-lock-loop (DLL) are removed to reduce the I/O and leakage power.

• Scalability. Taking advantage of semiconductor process scaling, DRAM process keeps scaling down accordingly. Recently, Samsung has announced to ship 20nm DDR3 soon [19]. 10nm DRAM is also on the roadmap and expected to be available in the near future. On the other hand, 3D ICs opens up another opportunity to sustain the scalability. By leveraging the Through-Silicon-Vias (TSVs), multiple DRAM dies can be stacked together and encapsulated in a single chip package. In this way, the 3D-stacked DRAM is able to increase the chip capacity, reduce the access latency and reduce power consumption at the same time.

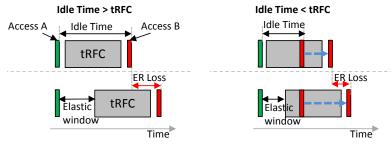

## 1.3 The DRAM Hierarchy

Without loss of generality, the DRAM memory structure has a pyramid-like hierarchy, which consists of rank, chip, bank, sub-array, MAT, and cell, as shown in Figure 1.3 (from top to bottom). A rank is composed of multiple memory chips (a.k.a. device) that operate in lock-step to feed the data bus. Inside one chip, several banks are employed as cell arrays and can

be accessed independently. Therefore, bank-level parallelism is extensively studied to improve memory performance.

In fact, a bank can be further divided into many sub-arrays. All sub-arrays share the output of global row address decoder so that only one sub-array is allowed to be active at any time. In one sub-array, there are many MATs and each of them has its own row decoder and sense amplifier array as the local row buffer. Typically, a MAT is sized of  $512 \times 512$  storage cells in row (wordline) and column (bitline) dimension. One storage cell is a Capacitor that is connected to an access Transistor (so-called 1T1C structure). According to the different voltage in the capacitor, the cell holds logic '1' ( $V_{dd}$ ) or '0' (0V). As the example shown in the figure, eight chips compose a rank to provide 64-bit data and each chip delivers 8-bit data (so-called  $\times 8$  chip). Every chip contains eight banks and each bank has 16K rows and 8K columns. Therefore, one bank has  $32 \ (= \frac{16,384}{512})$  sub-arrays and each sub-array consists of  $16 \ (= \frac{8,192}{512})$  MATs.

## 1.4 The Preliminary Of DRAM Commands

The commands a DRAM can accept can be classified into four types<sup>3</sup>: row activation ACT or RAS (Row Address Strobe), column read/write CAS (Column Address Strobe), precharge PRE, and refresh REF. Only CAS has data transfer between memory controller (MC) and memory modules while other three commands are only used for either access preparation (ACT and PRE) or data protection (REF). The purpose of the four commands is as follows.

- ACT: An activation is to open a row in a bank. It enables the row address decoder to assert a wordline. The data will then be sensed and locked in the sense amplifier.

- CAS: A column read/write is to fetch a data segment from the sense amplifier. It also accounts for the data traverse on the internal bus and read/write buffer.

- PRE: A precharge is to close a row in a bank. It resets the sense amplifier and bitline to the idle state for the next activation.

- REF: A refresh is to protect the data. It simply reads out and writes back the data. As a result, it can be treated as a pair of activation and precharge.

Figure 1.4a illustrates the command flow for a read transaction. The flow can be simplified as a loop of "ACT-CAS-PRE-ACT". First of all, the target bank should be activated by receiving an ACT command. After the RAS-to-CAS delay (tRCD), the data has been sensed in the sense amplifier so that a CAS can be issued to fetch the data. After the read latency (tCL), the data shows up on the data bus. As double data rate (DDR) is widely applied in commodity DRAM, the data is sampled by MC at both rising and falling clock edge. In DDR3, the data burst length (BL) is 8, which means DRAM spends 4 clocks to burst out the data.

<sup>&</sup>lt;sup>3</sup>In fact, more memory commands are available in JEDEC specification, such as implicit auto precharge, post-CAS, and commands for low-power mode. The ACT-CAS-PRE-ACT command order, however, is still applied. As a result, we only show these four basic commands in this work.

Figure 1.4: DRAM commands for read and write transaction. Note that a write can lock a bank for a longer time before the bank can be closed (precharged).

Note that the bank is unable to be closed immediately after CAS. Instead, the bank needs to spend time on restoring the data due to the destructive array access. The time period tRAS accounts for such constraint. Once the tRAS constraint is satisfied, a PRE can be issued to close the bank. As shown, there is also a minimum distance between the precharge and the next activation, which is denoted as tRP. As the bank is fully precharged, it can be reopened by the next activation. Therefore, the term *row cycle* tRC is the primary measurement of DRAM latency as it indicates how fast a bank can be reopened. As shown in Equation 1.3, the row cycle can be calculated as the sum of tRAS and tRP.

$$tRC_{read} = tRAS + tRP (1.3)$$

$$tRC_{write} = tRCD + tWL + BL/2 + tWR + tRP \tag{1.4}$$

The command flow for a write transaction is shown in Figure 1.4b. Distinct from read, write has a shorter write latency tWL (tWL <tCL). Moreover, since DRAM has to change the value of the storage cell, it needs to wait for the write recovery latency tWR before the bank can be closed. Note that the write recovery latency starts right after the completeness of data burst on the bus. Therefore, the row cycle of a write transaction is different from that of read transaction. As shown in Equation 1.4, it is the sum of tRCD, tWL, BL/2, tWR and tRP.

#### 1.5 The Structure Of The Dissertation

The rest of dissertation consists of six chapters. Chapter 2-Chapter 6 are the body of the dissertation. Chapter 7 concludes the dissertation with the summary of the proposals shown in this work and the discussion of future work. In general, the first five chapters follow the rule of "WWWH", which stands for "What is the problem", "Why the problem is important", "What is the proposed solution", and "How much improvement the solution can achieve". Correspondingly, each chapter has the dedicated introduction (W), background/motivation (W), the proposal and design overhead (W), and experimental results (H).

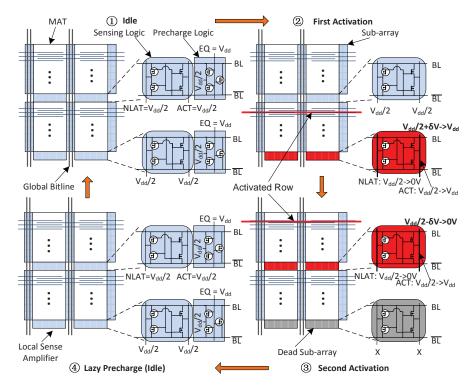

Chapter 2 shows the in-depth details of CREAM, which is a concurrent refresh aware DRAM architecture. Sub-rank and sub-array level refresh are proposed to isolate the refresh from normal memory access. In this way, it is unnecessary to lock the whole memory during a refresh. Chapter 3 presents the Half-DRAM, in which the DRAM is redesigned so that only a half of row is activated. As the active row size shrinks, Half-DRAM can effectively reduce the activation power. In addition, it can also achieve performance improvement once the sub-array level parallelism is employed. Chapter 4 targets at the reduction of the precharge overhead and thus proposes a novel precharge policy, which is noted as "Lazy Precharge". Distinct from prior studies, Lazy Precharge can effectively reduce the number of precharge in that it allows multiple activations to share a common (lazy) precharge.

Chapter 5 and chapter 6 focus on the optimization in 3D-stacked memory. In chapter 5, 3D-SWIFT is proposed in which a 3D Wide-IO memory [11] is further split into multiple sub-banks. Stemming from the improved wiring capability in the third dimension, each sub-bank can provide a full cacheline. As a result, 3D-SWIFT can significantly reduce the activation power and thus break the TAW (two activation window) constraint for performance improvement. Chapter 6 demonstrates the feasibility of 3D IC and the on-chip memory stacking technology. The design flow of a 3D SoC is depicted in this chapter. The front-end and bank-end flow are described separately. In addition, a custom memory controller is designed to interact with the 3D-stacked DRAM.

# CREAM: The Relax Of Refresh Penalty

In recent years, DRAM density has been improved dramatically as DRAM technology evolves along with CMOS process scaling. Recently, 16Gb DRAM chip was defined in DDR4 specification [6]. The increasing density, especially the increasing row number, introduces significant refresh penalty because more rows are required to be refreshed at a time. As a result, it takes longer time and more power to complete a refresh. The larger refresh penalty is no longer trivial as it can result in negative impact on memory performance and power. For example, significant performance degradation has been observed [20]. Consequently, the DRAM system should be carefully designed to mitigate the refresh penalty. In this work, we propose a Concurrent-REfresh-Aware Memory (CREAM) architecture that allows memory access and refresh to be executed concurrently under the pre-defined power constraint. The contributions of this work can be summarized as follows:

- Trade-off between power constraint and performance. The capability of concurrent refresh in today's commodity DRAM is limited due to power (current) constraint. To relax the constraint, sub-rank-level refresh (SRLR) is proposed so that fewer banks are refreshed simultaneously to reduce the refresh power consumption. The saved power can in turn be used for memory accesses to improve performance.

- Sub-array-level refresh. With SRLR alone, the whole sub-rank is still locked during a refresh. To further improve the performance, a novel sub-array-level refresh (SALR) is proposed to increase the probability of memory concurrency between normal access and refresh. To our best knowledge, this is the first work to deploy SALR for the reduction of refresh penalty.

- Concurrent refresh design. By combining SRLR and SALR, CREAM can issue a memory access even when a refresh operation is ongoing, which means that the access and

Figure 2.1: Refresh basics. (a) Burst refresh; (b) Distributed refresh; (c) Refresh command and related timing constraints; (d) impact of power constraint on performance.

refresh can be served in parallel. In this way, CREAM can effectively hide the refresh latency overhead and meanwhile improve the performance. Moreover, a quasi-ROR interface is designed to make CREAM compatible with JEDEC-DDR standard, with negligible hardware overhead.

Refresh-aware memory optimization. Two mechanisms, sub-array round-robin and dynamic refresh scheduling, are devised for further performance improvement. Sub-array round-robin evenly distributes the fine-grained refresh in a bank to avoid conflict between memory access and refresh. In addition, the concurrent refresh can be scheduled dynamically according to the status of a sub-rank.

## 2.1 Background And Motivation

In this section, we first briefly review the refresh overhead in the conventional DRAM architecture, and then discuss the ineffectiveness of existing solutions to mitigate the refresh overhead, which motivates this work to come up with a more effective approach to re-architect the DRAM structure.

#### 2.1.1 Preliminary Of DRAM Refresh

Due to the leakage current, the charge in each storage cell gradually dissipates and eventually the stored data can be lost as the state becomes unrecognizable. The lifetime of the data is noted as retention time. To prevent the data loss, refresh is required to recharge the storage cell within the retention time. In theory, a refresh scheme at any granularity is valid as long as the cell can be refreshed in time. The refresh in modern DRAM memory, however, is usually organized at rank level, which means all chips in the rank and all banks in the chip are refreshed in lockstep. No memory access is permitted to a rank when it undergoes a refresh. In other words, refresh and memory access are mutually exclusive to each other in the scale of rank.

Basically, two common refresh scheduling schemes have been developed to refresh the whole

memory system, which are shown in Figure 2.1. Burst Refresh requires the memory controller (MC) to send multiple successive refresh pulses in burst within a short period while Distributed Refresh mandates the MC to evenly send refresh pulses to DRAM chips periodically. Even though both methods can complete all refreshes before the data loss, burst refresh induces a relatively longer memory stall that degrades the performance. In addition, burst refresh consumes large power within a short time interval, which requires higher current density that is challenging for commodity DRAM. Therefore, distributed refresh is preferable for MC design due to the amortization of refresh overhead in terms of performance and power. In addition to these two schemes, there are two refresh modes in the commodity DRAM. Auto Refresh is one mode that MC initiates a refresh by sending a refresh command (REF) to DRAM chips. Alternatively, Self Refresh is employed as a low-power mode so that a DRAM chip can complete the refresh without the intervention from the MC. The refresh row address is generated by an internal row counter. Since only Auto Refresh is used during a memory access, we focus on this refresh mode in this work.

#### 2.1.2 The Source Of Refresh Penalty

The primary refresh penalty is the mutual exclusion between refresh and memory access due to the sharing of pre-decoded row address in a bank. As a result, one bank can only serve one out of four memory operations at a time: activation (RAS or ACT), precharge (PRE), read/write (CAS), and refresh (REF). Consequently, all memory operations can only be issued in sequence, which we call *intrabank-zero-parallelism*. The intrabank-zero-parallelism requires memory operations to wait if a refresh is being processed. Moreover, since all banks are refreshed simultaneously, refresh further suppresses bank-level parallelism, which we denote as *interbank-zero-parallelism*. The combined effect of intrabank- and interbank-zero-parallelism mandates all memory accesses to be delayed until the refresh completes. Considering the refresh should be taken periodically, an application may experience a long, periodic delay, which can incur significant performance degradation.

In JEDEC-DDR standard [6, 21], three timing parameters are used to define the refresh characteristics of a DRAM chip. These timing parameters are illustrated in Figure 2.1(b).

- **tREFW** is the refresh window that refers to the cell retention time.

- **tREFI** is the time interval of two REF commands. Since distributed refresh is applied, the value of tREFI is determined by tREFW and the refresh count in a tREFW.

- tRFC is the refresh latency of one REF command, which is also known as refresh cycle.

Table 2.1 shows the values of these three parameters as the chip capacity ranges from 1Gb to 16Gb<sup>1</sup>. According to the operating temperature, tREFW can be either 64ms (Temp≤85°C) or 32ms (85°C<Temp<95°C). From the table, the refresh count remains at 8,192 even though the

<sup>&</sup>lt;sup>1</sup>The values of 16Gb DRAM has not been defined in JEDEC DDR4 specification. The data listed in the table is based on our projection according to the trend from 1Gb to 8Gb.

| Capacity     | 1Gb     | 2Gb     | 4Gb     | 8Gb     | $16 \mathrm{Gb}$ |

|--------------|---------|---------|---------|---------|------------------|

| Row Num.     | 16K     | 32K     | 64K     | 128K    | 256K             |

| Refresh Num. | 8K      | 8K      | 8K      | 8K      | 8K               |

| Rows/REF     | 2       | 4       | 8       | 16      | 32               |

| tREFW(ms)    | 64/32   | 64/32   | 64/32   | 64/32   | 64/32            |

| tREFI(μs)    | 7.8/3.9 | 7.8/3.9 | 7.8/3.9 | 7.8/3.9 | 7.8/3.9          |

| tRFC(ns)     | 110     | 160     | 260     | 350     | 450              |

| tRFC/tREFI   | 1.41%   | 2.05%   | 3.34%   | 4.34%   | 5.77%            |

| thr C/theri  | 2.82%   | 4.11%   | 6.68%   | 8.68%   | 11.54%           |

| tRRD(ns)     | 6       | 6       | 6       | 6       | 6                |

| tFAW(ns)     | 30      | 30      | 30      | 30      | 30               |

| tRC(ns)      | 51      | 51      | 51      | 51      | 51               |

| IDD5B(mA)    | 165     | 111     | 148     | 230     | 260              |

| IDD0(mA)     | 65      | 41      | 47      | 85      | 95               |

Table 2.1: Refresh related parameters with various DRAM capacities (based on Micron DDR3-1333 data sheet)

memory capacity increases. Therefore, tREFI sustains at 7.8μs (3.9μs) regardless of the DRAM evolution.

K[7]

E[8]

G[22]

Version

$\overline{N/A}$

D[23]

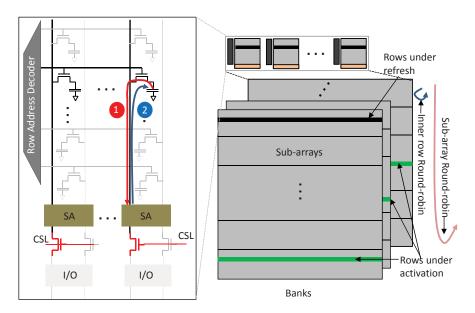

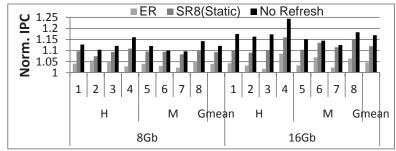

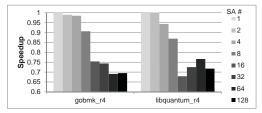

From Table 2.1, it is clear that the refresh cycle tRFC dramatically increases as the chip capacity keeps growing. Correspondingly, the refresh overhead that is defined as tRFC/tREFI becomes larger, which means the following memory accesses should wait for a longer time. The large performance degradation has been observed in [20] and we also see the similar result. Figure 2.2a illustrates the potential performance gain if there is no refresh in DRAM. The average speedup for all benchmarks and memory-intensive benchmarks is 6.3% and 11.2% with 3.9µs refresh rate, respectively. An interesting observation from Figure 2.2a is that some benchmarks, such as gobmk and libquantum, have larger performance drop (15.7% and 14.3%) than the maximum refresh overhead (11.54%), which indicates the refresh generates accumulative effect on an application and therefore aggravates the performance degradation.

#### 2.1.3 Power Constraint-The Secondary Cause

In addition to the aforementioned refresh penalty caused by intrabank- and interbank-zero-parallelism, power (current) constraint is the secondary factor that necessitates the mutual exclusion between refresh and memory access. Even though the refresh power constraint is not detailed in JEDEC standard and DRAM vendors' data sheet, we leverage the well-known power constraint on activation to help the explanation.

To ensure that the peak current consumption does not exceed the pre-defined threshold, a DRAM chip prohibits very frequent activations. Correspondingly, two timing parameters are used to limit the ACT frequency. tRRD is known as activation-to-activation delay, which determines the minimum interval between two successive ACTs. Moreover, the four-activation window constraint tFAW only allows four ACTs to be issued in any tFAW cycles. Once the MC issues an ACT to open a row, the next ACT can only be issued after tRRD cycles. Since tFAW is usually greater than

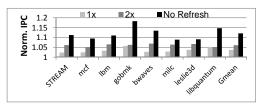

(a) Performance gain when no refresh is applied

- (b) Ineffectiveness of fine-grained refresh defined in DDR4  $\left[ 6\right]$

- (c) In effectiveness of elastic refresh in  $\left[20\right]$

(d) The cause of ER's failure

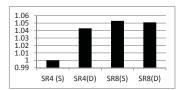

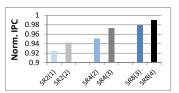

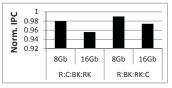

Figure 2.2: The motivation experimental results. (a) performance gain without refresh as chip size ranges from 1Gb to 16Gb; (b) the ineffectiveness of fine-grained refresh in DDR4; both  $\times 2$  and  $\times 4$  modes are shown by the normalized IPC to the baseline  $\times 1$  mode; (c) the ineffectiveness of ER; (d) cause of ER's failure.

the sum of four tRRDs (see Table 2.1), the fifth ACT (highlighted in gray) can only be issued after tFAW cycles even if it satisfies tRRD constraint. Therefore, tFAW constrains the performance in a DRAM system that the *close-page* row buffer management policy is applied [24]. As CREAM aims at the server memory that close-page policy is commonly deployed, tFAW effectively limits CREAM's performance as well.

Since a refresh can be simply considered as a pair of activation and precharge (see Section 2.2), it should abide with the same power constraints too. From Table 2.1, a refresh consumes about 3X currents (IDD5B) than an activation (IDD0), which means it almost reaches the peak current. As a result, no activation can be issued during a refresh.

Table 2.2: Settings for fine-grained refresh in DDR4 [6]

|           | $1 \times$ | $2\times$ | $4\times$ | 8×     |

|-----------|------------|-----------|-----------|--------|

| tRFC(ns)  | 350        | 260       | 160       | 75     |

| tREFI(µs) | 3.9        | 1.95      | 0.975     | 0.4875 |

## 2.1.4 The Ineffectiveness Of Existing Refresh Scheduling Methods

To mitigate the refresh penalty, the new DDR4 standard [6] proposes a fine-grained refresh scheme, in which refresh frequency can be two  $(2 \times \text{mode})$  or four times  $(4 \times \text{mode})$  higher than the original refresh rate  $(1 \times \text{mode})$ . Since more refreshes are involved, fewer rows need to be refreshed during a single refresh. In this way, the fine-grained refresh can reduce tRFC so that the waiting memory accesses can be served earlier to improve performance. Table 2.2 lists the timing changes when fine-grained refresh is applied<sup>2</sup>. We implement this fine-grained refresh in DRAMSim2 [26] and select some memory-intensive benchmarks from SPEC2006 suite to evaluate its effectiveness (see Section 2.4 for the detail of simulation platform). As shown in Figure 2.2b, on average  $2 \times$  and  $4 \times$  mode can only achieve 3.9% and 6.4% performance gain, respectively, which is consistent with JEDEC report [25]. Therefore, the proposed refresh scheme is ineffective to eliminate the refresh penalty, still leaving a big performance gap to be filled.

The main problem of such fine-grained refresh is that it only reduces the waiting time caused by intrabank- and interbank-zero-parallelism rather than eliminate either of them. As a result, all banks are still locked during the refresh even though the refresh cycle becomes smaller. Moreover, the higher refresh rate adversely affects the performance as well. Compared to the  $1\times$  mode where an application only needs to wait for one tRFC, the application running with the fine-grained refresh scheme can experience multiple refreshes in the same tREFI. The accumulative refresh penalty, which is calculated as  $N_{stall} \times tRFC_{2\times}$  ( $tRFC_{4\times}$ ) where  $N_{stall}$  is the maximum stall number, could be larger than the single refresh cycle  $tRFC_{1\times}$  and thus even induce performance degradation in  $8\times$  mode as shown in [25].

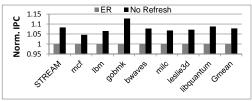

Another famous refresh scheduling policy has been proposed in [20], which is called elastic refresh (ER). ER leverages the 8-tREFI refresh scheduling flexibility defined in DDR standard to hide the refresh penalty. Different from prior work that defers a refresh until the memory is idle (DUE) [27], ER leaves an extra elastic window and expects that there are incoming memory accesses in the window. If so, ER further defers the refresh until either no access comes up during the window or it has deferred eight refreshes and thus hits the 9-tREFI refresh limitation. As the window width is critical to ER's performance, ER has capability to adjust the window width in-the-flight based on the average idle time and the number of deferred refreshes. We also implement this approach to measure the performance improvement. Figure 2.2c illustrates the results. Unfortunately, no result can be comparable to the ideal case where no refresh is applied. On average, there is 7.8% performance gap between ER and the ideal case. In particular, the potential improvement room can be as much as 12.1% (gobmk). Similar to the aforementioned fine-grained refresh, ER also renders the ineffectiveness to eliminate the refresh penalty.

$<sup>^28\</sup>times$  mode is mentioned in [25] but not defined in [6].