The Pennsylvania State University

The Graduate School

Department of Computer Science and Engineering

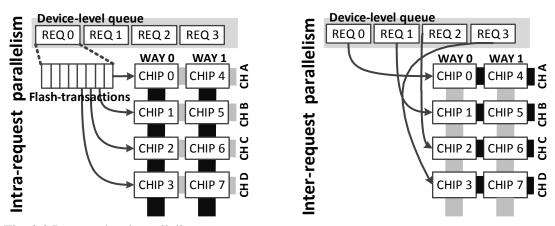

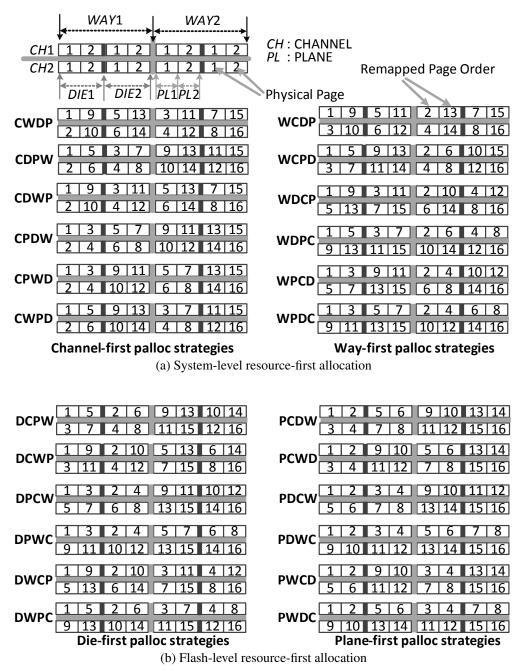

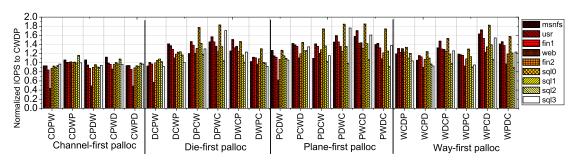

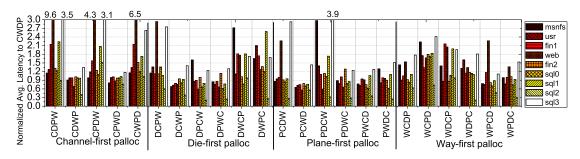

# DESIGN OF A SMART NON-VOLATILE MEMORY CONTROLLER: ARCHITECTURE MODELING, SYSTEMS ANALYSIS, PARALLEL I/O PROCESSING AND SCHEDULING ALGORITHMS

A Dissertation in

Computer Science and Engineering

by

Myoungsoo Jung

© 2013 Myoungsoo Jung

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2013

The dissertation of Myoungsoo Jung was reviewed and approved<sup>1</sup> by the following:

Mahmut T. Kandemir Professor of Computer Science and Engineering Dissertation Adviser Chair of Committee

Padma Raghavan Professor of Computer Science and Engineering

Chita R. Das Professor of Computer Science and Engineering

Long-Qing Chen Professor of Material Science and Engineering

Raj Acharya Head of the Department of Computer Science and Engineering

<sup>&</sup>lt;sup>1</sup>Signatures are on file in the Graduate School.

#### Abstract

State-of-the-art Solid State Disks (SSDs) and Non-Volatile Memory (NVM) systems have undergone severe technology shift and architectural changes in the last couple of years, and, in parallel, SSD internal architecture has dramatically changed; modern SSDs now employ multiple internal resources such as NVM chips and I/O buses in an attempt to achieve high internal parallelism in processing I/O requests. In addition, to reduce intrinsic NVM system management overheads, SSD firmware employs advanced memory control strategies such as finer-granular address mapping algorithms and concurrency methods. As a result of complex interactions among these different mechanisms, modern SSDs can be plagued by enormous performance variations depending on whether the underlying architectural complexities and NVM management overheads can be hidden or not.

Designing a smart NVM controller is key hiding the architectural complexities and reducing the internal firmware overheads. To this end, we first model a multi-plane and multi-die NVM architecture, which is highly reconfigurable and aware of intrinsic latency variation imposed by diverse state-of-the-art NVM systems. This NVM model has been implemented as a high fidelity open-source simulator, capable of capturing cycle-level interactions between the many components in an SSD, which can be used for various high-level and low-level NVM performance analyses. Based on this architecture model, we then explore twenty four different concurrency methods implemented in NVM controllers, geared toward exploiting both systemlevel and NVM-level parallelism. Further, we quantitatively analyze the challenges, faced by PCI Express-based (PCIe) SSDs in getting NVM closer to CPU and question popular assumptions and expectations regarding storage-class SSDs through an extensive experimental analysis.

Next, we present and discuss the significance of read performance degradations and write performance variations by performing comprehensive empirical experiments using a diverse set of commercial SSDs and propose two novel schedulers in order to address these read/write performance challenges that modern SSDs face: 1) Physical Address Queuing (PAQ) scheduler and 2) NVM garbage collection scheduling algorithm. PAQ is a novel I/O request scheduling method that avoids resource contention resultant from shared SSD resources. Our proposed PAQ significantly improves read performance by exposing the physical addresses of requests to the scheduler and selecting groups of operations that can be simultaneously executed without major resource conflict. In comparison, the novel garbage collection scheduler is an approach that removes garbage collection overheads of underlying flash firmware and provides stable write performance in SSDs during the I/O congestion periods. Our proposed garbage collection scheduler tries to secure free blocks and remove on-demand garbage collections from the critical path in advance or delay them to future idle periods, so that users do not experience garbage-collectioninduced latencies during the I/O-intensive periods. Overall, this thesis (1) presents a simulation infrastructure to conduct SSD/NVM research, (2) characterizes both system-level and devicelevel challenges faced by state-of-the-art SSDs, (3) presents a set of novel storage optimizations including various concurrency methods and scheduling algorithms design, and (4) points out future research directions.

## **Table of Contents**

| List of Tabl | les                                                             | ix |

|--------------|-----------------------------------------------------------------|----|

| List of Figu | ires                                                            | X  |

| Acknowled    | gments                                                          | xv |

| Chapter 1.   | Introduction                                                    | 1  |

| Chapter 2.   | NAND Flash Memory System Modeling and Simulation                | 6  |

| 2.1          | Introduction                                                    | 6  |

| 2.2          | NAND Flash Microarchitecture                                    | 11 |

| 2.3          | NAND Flash Operations                                           | 13 |

|              | 2.3.1 Cache Mode Operation                                      | 14 |

|              | 2.3.2 Internal Data Move Mode Operation                         | 14 |

|              | 2.3.3 Multi-plane Mode Operation                                | 15 |

|              | 2.3.4 Interleaved Die Mode Operation                            | 15 |

| 2.4          | Intrinsic Latency Variation of NAND Flash                       | 18 |

| 2.5          | Related Work                                                    | 19 |

| 2.6          | High Level View Of NANDFlashSim                                 | 22 |

|              | 2.6.1 Software Architecture                                     | 22 |

|              | 2.6.2 Clock Domains and Lifetime of Transaction                 | 23 |

| 2.7          | Implementation Details                                          | 25 |

|              | 2.7.1 NAND Command Set Architecture                             | 25 |

|              | 2.7.2 Awareness of Latency Variation                            | 26 |

|              | 2.7.3 Enforcing Reliability Parameters                          | 28 |

| 2.8          | Evaluation                                                      | 28 |

|              | 2.8.1 Validation of NANDFlashSim                                | 31 |

|              | 2.8.2 Individual Cycle Analysis                                 | 34 |

|              | 2.8.3 Performance and Power Consumption Comparison: Page Migra- |    |

|              | tion Test                                                       | 37 |

|              | 2.8.4 Breakdown of Read and Write Cycles                        | 39 |

|              | 2.8.5 Performance on Multi-plane and Multi-die Architectures    | 39 |

|              | 2.8.6 Performance Sensitivity to Page Size                      | 45 |

|              | 2.8.7 Resource Contention                                       | 45 |

|              | 2.8.8 Scheduling Strategy                                       | 46 |

| 2.9          | Simulation Speed and Download                                   | 46 |

| 2.10         | ) Conclusion                                                    | 46 |

| Chapter 3. | Page Allocation Strategies for Parallelizing Data Accesses                                |

|------------|-------------------------------------------------------------------------------------------|

| 3.1        | Introduction                                                                              |

| 3.2        | SSD Internals and Parallelisms                                                            |

| 3.3        | Page Allocation Strategies                                                                |

| 3.4        | Experimental Methodology                                                                  |

| 3.5        | Results                                                                                   |

|            | 3.5.1 Finding Overall Optimal Palloc scheme                                               |

|            | 3.5.2 Parallelism Interference                                                            |

|            | 3.5.3 Resource Utilization                                                                |

|            | 3.5.4 Optimization Potential for Parallelism                                              |

|            | 3.5.5 Discussion                                                                          |

| 3.6        | Conclusion                                                                                |

|            |                                                                                           |

| Chapter 4. | Challenges in Getting Flash Drives Closer to CPU                                          |

| 4.1        | Introduction                                                                              |

| 4.2        | Bringing SSDs Closer to CPU 70                                                            |

|            | 4.2.1 PCIe Architecture                                                                   |

|            | 4.2.2 Flash Software Stack                                                                |

| 4.3        | Experimental Setup                                                                        |

| 4.4        | Challenges in Resource Management                                                         |

|            | 4.4.1 Memory Usage                                                                        |

|            | 4.4.2 CPU Usage                                                                           |

|            | 4.4.3 Challenges in System Performance                                                    |

| 4.5        | System Implication                                                                        |

| Charter 5  | Deviciting Widely Held CCD Expectations and Dethicking Contam Land                        |

| Chapter 5. | Revisiting Widely Held SSD Expectations and Rethinking System Level Implications       86 |

| 5.1        | Introduction                                                                              |

| 5.1        |                                                                                           |

|            | e                                                                                         |

|            | 8                                                                                         |

|            | 5.1.3 Reconsidering Write Performance                                                     |

| 5.0        | 5.1.4 OS Support                                                                          |

| 5.2        | Preliminaries                                                                             |

|            | 5.2.1 SSD and NAND Flash Internals                                                        |

|            | 5.2.2 Flash Firmware                                                                      |

|            | 5.2.3 Reliability Challenges on Reads                                                     |

|            | 5.2.4 Storage Interfaces, TRIM and SMART                                                  |

| 5.3        | Evaluation Setup    95                                                                    |

| 5.4        | Testing Expectations on Reads    98                                                       |

|            | 5.4.1 Are SSDs good for applications that exhibit mostly random reads? . 98               |

|            | 5.4.2 Can we achieve sustained read performance with sequential accesses? 101             |

|            | 5.4.3 What is the relationship between read performance and previous                      |

|            | writes accesses?                                                                          |

|            | 5.4.4 Do program/erase (PE) cycles of SSDs increase during read only                      |

|            | operations?                                                                               |

vi

|            | 5.4.5 Is there any performance impact of the reliability management on  |     |

|------------|-------------------------------------------------------------------------|-----|

|            | reads?                                                                  | 108 |

| 5.5        | Testing Expectations on Writes                                          | 110 |

|            | 5.5.1 How much impact does the worst-case latency have on modern SSDs?  | 111 |

|            | 5.5.2 What is the correlation between the worst-case latency and system |     |

|            | throughput?                                                             | 112 |

|            | 5.5.3 Could DRAM buffer help the firmware to reduce garbage collection  |     |

|            | overheads?                                                              | 114 |

| 5.6        | Testing Expectations on Advanced Schemes                                | 117 |

|            | 5.6.1 Can TRIM command reduce GC overheads?                             | 117 |

|            | 5.6.2 Does a TRIM command incur any overheads?                          | 119 |

| 5.7        | Rethinking SSD Systems                                                  | 123 |

|            | 5.7.1 Reads                                                             | 125 |

|            | 5.7.2 Writes                                                            | 126 |

|            | 5.7.3 Advanced Schemes                                                  | 127 |

| 5.8        | Related Work                                                            | 127 |

| 5.9        | Conclusion                                                              | 128 |

|            |                                                                         |     |

| Chapter 6. | Memory Request Scheduling: Improving Parallelism in Solid State Drives  | 130 |

| 6.1        | Introduction                                                            | 130 |

|            | 6.1.1 Contributions                                                     | 132 |

| 6.2        | Background                                                              | 134 |

|            | 6.2.1 High-Level Architecture of SSD                                    | 134 |

|            | 6.2.2 Multi-Plane Mode Operation                                        | 136 |

| 6.3        | Random Write vs. Random Read Performance                                | 137 |

| 6.4        | Physically Addressed Queuing                                            | 141 |

|            | 6.4.1 QBM Migration                                                     | 141 |

|            | 6.4.2 Conflict Classification                                           | 142 |

|            | 6.4.3 Clump Composition                                                 | 144 |

|            | 6.4.4 Plane Packing                                                     | 147 |

|            | 6.4.5 Implementation of PAQ Scheduling                                  | 148 |

| 6.5        | Experimental Setup                                                      | 152 |

|            | 6.5.1 NAND Flash SSD Simulator                                          | 152 |

|            | 6.5.2 SSD Configuration and Schedulers Tested                           | 152 |

|            | 6.5.3 Traces                                                            | 153 |

| 6.6        | Experimental Results                                                    | 155 |

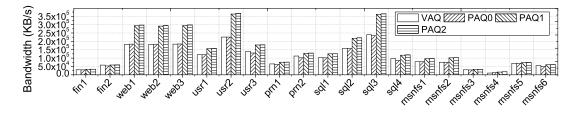

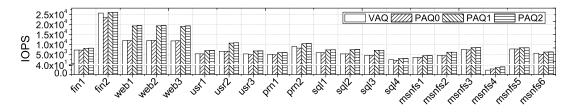

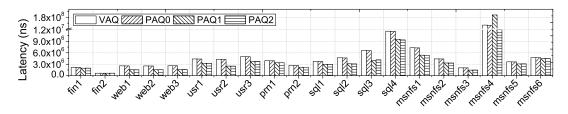

|            | 6.6.1 Aggregate Performance: Bandwidth, IOPs, and Latency               | 156 |

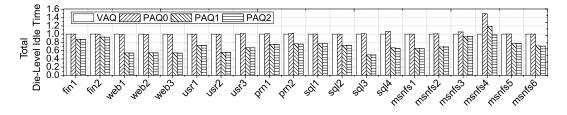

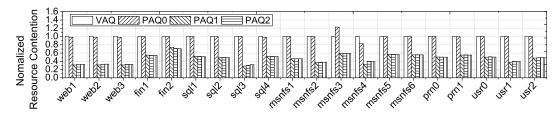

|            | 6.6.2 Quantifying Parallelism: Idle Time and Contention                 | 159 |

|            | 6.6.3 Overheads of PAQ                                                  | 160 |

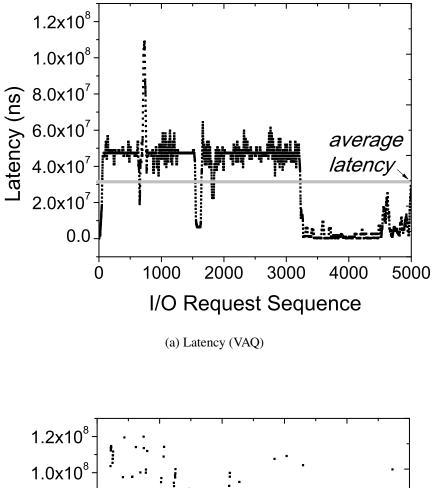

|            | 6.6.4 Time Series: In-Depth Analysis of a Database Trace                | 160 |

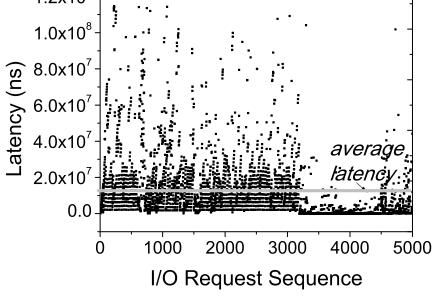

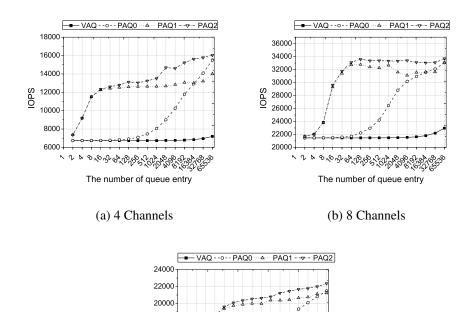

|            | 6.6.5 Sensitivity Analysis                                              | 161 |

| 6.7        | Related Work                                                            | 162 |

| 6.8        | Conclusion                                                              | 167 |

| 0.0        |                                                                         | /   |

| Chapter 7. | Garbage Collection Scheduling                               | 169 |

|------------|-------------------------------------------------------------|-----|

| 7.1        | Introduction                                                | 169 |

| 7.2        | Background and Related work                                 | 173 |

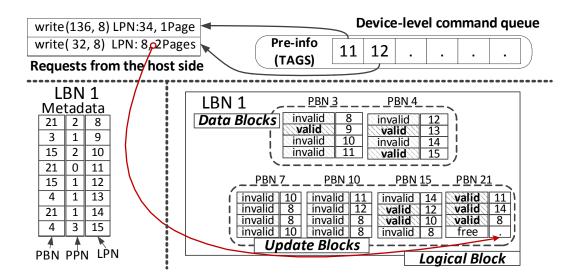

|            | 7.2.1 Flash Translation Layer                               | 173 |

|            | 7.2.2 Garbage Collection                                    | 174 |

| 7.3        | Impact of Garbage Collection in Commercial SSDs             | 175 |

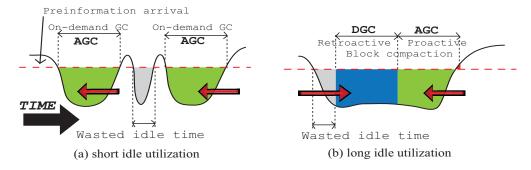

| 7.4        | High Level View of GC Scheduling                            | 177 |

|            | 7.4.1 Idle Period Classification                            | 177 |

|            | 7.4.2 Shifting Garbage Collection Overheads to Idle Periods | 180 |

| 7.5        | Implementation of our GC strategies                         | 181 |

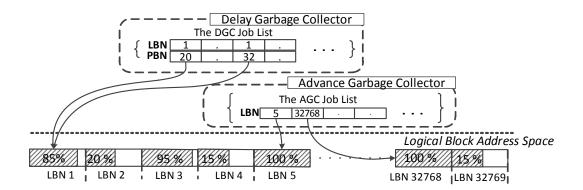

|            | 7.5.1 Details of Advanced GC Strategy (AGC)                 | 181 |

|            | 7.5.1.1 Look-ahead Garbage Collection                       | 181 |

|            | 7.5.1.2 Proactive Block Compaction                          | 184 |

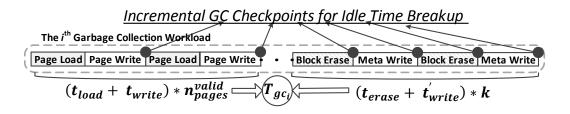

|            | 7.5.1.3 Incremental Garbage Collection                      | 185 |

|            | 7.5.2 Details of Delayed GC Strategy (DGC)                  | 186 |

|            | 7.5.2.1 Update Block Replacement                            | 186 |

|            | 7.5.2.2 Retroactive Block Compaction                        | 189 |

|            | 7.5.3 Putting the Two Schemes Together                      | 190 |

| 7.6        | Experimental Evaluation                                     | 190 |

|            | 7.6.1 Performance Comparison                                | 194 |

|            | 7.6.2 Worst Case Response Time                              | 196 |

|            | 7.6.3 Excess Waiting Time                                   | 198 |

|            | 7.6.4 Performance Compariosn of 3SSDs-RAID                  | 200 |

|            | 7.6.5 Side-Effects of AGC and DGC                           | 200 |

| 7.7        | Conclusions                                                 | 202 |

| Chapter 8. | Future Work                                                 | 203 |

| 8.1        | Near Term Future Research Directions                        | 203 |

|            | 8.1.1 QoS-aware and GC-aware Host Interface Scheduler       | 203 |

|            | 8.1.2 Out-of-Order Non-Volatile Memory Execution            | 203 |

|            | 8.1.3 NVM Power Modeling                                    | 204 |

|            | 8.1.4 High-speed Non-Volatile Memory Interface              | 205 |

| 8.2        | Long Term Future Research Directions                        | 205 |

|            | 8.2.1 SSD Redesign                                          | 205 |

|            | 8.2.2 Exposing NVM to Computational Resources               | 206 |

|            | 8.2.3 On-Chip NVM Systems                                   | 206 |

| References |                                                             | 207 |

viii

## List of Tables

|     | NAND Flash Device Characterization          Workloads Characterization                                                               |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Important characteristics of our traces.                                                                                             | 58  |

| 4.1 | Important characteristics of the tested PCIe SSDs                                                                                    | 73  |

| 5.1 | Device characteristics of SSDs used in our study.                                                                                    | 96  |

| 6.1 | Trace decomposition into the number of writes and reads, and the percentage of random-reads and random-writes issued.                | 153 |

| 7.1 | Important characteristics of our traces. The last column gives % of I/O requests containing sufficiently long idle (> 1 sec) periods | 192 |

## List of Figures

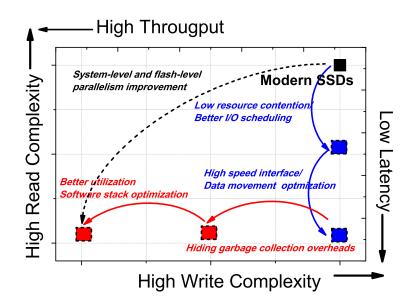

| 1.1        | Design and optimization goal of a smart NVM controller. Modern SSDs can be<br>plagued by enormous performance variations depending on whether underlying<br>architectural complexities and NVM firmware overheads can be hidden or not.<br>Designing a smart NVM controller is key hiding the architectural complexities<br>and reducing the internal firmware overheads.     | 2        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

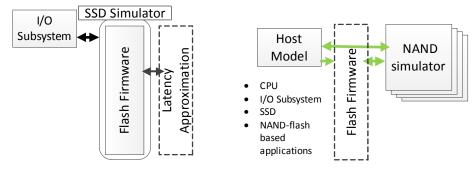

| 2.1        | Concept of a $\mu$ arch-level NAND flash simulation model (NANDFlashSim).<br>While existing SSD simulators are highly coupled to flash firmware emulation<br>with simplified latency model, NANDFlashSim simulates NAND flash mem-<br>ory system itself with independently synchronous clock domains and detailed<br>NAND operation timing models aware of latency variation. | 7        |

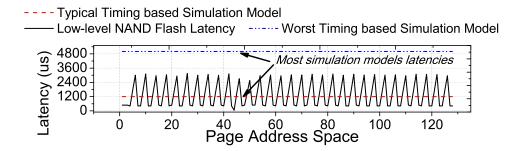

| 2.2        | Intrinsic Latency Variation Example.                                                                                                                                                                                                                                                                                                                                          | 9        |

| 2.3<br>2.4 | NAND flash memory system internals                                                                                                                                                                                                                                                                                                                                            | 12<br>16 |

| 2.5        | NAND flash memory cell organization. MLC NAND flash memory has multi-<br>ple states in a cell, which causes intrinsic latency variation [65].                                                                                                                                                                                                                                 | 19       |

| 2.6        | NANDFlashSim architecture. NANDFlashSim is a reconfigurable $\mu$ -level multiplane and multi-die architecture. The number of registers, blocks, planes and dies can be reorganized, and each entity has independent synchronized clock                                                                                                                                       | 21       |

| 2.7        | domain                                                                                                                                                                                                                                                                                                                                                                        | 21<br>24 |

| 2.8        | State machine for multiple NAND stages. Each state is identified by different type of stages and states of the machine are transited by different type of NAND commands. Since each die has their own state machine, NANDFlashSim pro-                                                                                                                                        |          |

| 2.9        | vides an independent clock cycle domain per die                                                                                                                                                                                                                                                                                                                               | 25       |

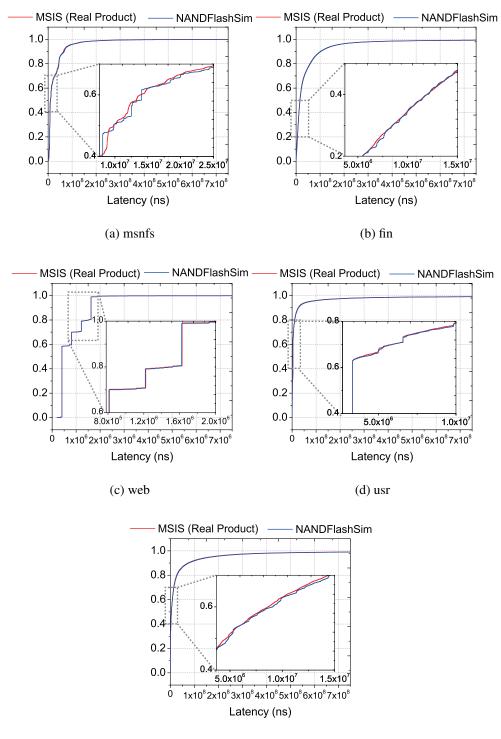

| 2.10       | Sim validation                                                                                                                                                                                                                                                                                                                                                                | 29       |

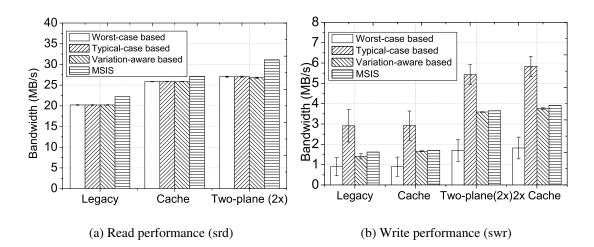

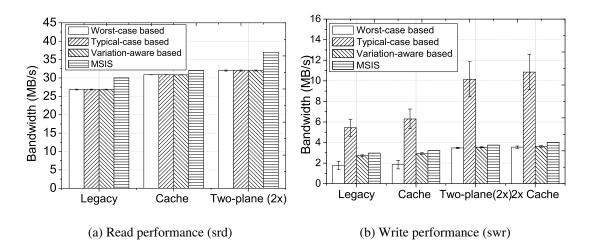

| 2.11       | Sim are mostly overlapped with real NAND flash product latencies Performance comparison on SDP. Typical-case/worst-case time parameter based                                                                                                                                                                                                                                  | 30       |

| 2.12       | latency models show unreasonable performance gap from real product ones<br>Performance comparison on DDP. While typical-based latency model show<br>more discrepant performance than that of multi-plane tests, the variation-aware                                                                                                                                           | 33       |

|            | NANDFlashSim provides performances close to the real product ones                                                                                                                                                                                                                                                                                                             | 34       |

| d  |

|----|

| st |

| 35 |

| le |

| d  |

| is |

| 36 |

| 1- |

| ie |

| g  |

| 38 |

| e  |

| 40 |

| st |

| 40 |

| te |

| ie |

| 41 |

| /r |

| ie |

| nt |

| 42 |

| n  |

| ie |

| 43 |

| e- |

| С  |

| re |

| 43 |

| ed |

| 44 |

| nt |

| ie |

| 44 |

| 8- |

|    |

| 53 |

| 55 |

| e- |

|    |

| e- |

| 57 |

| 60 |

| 60 |

| e  |

xi

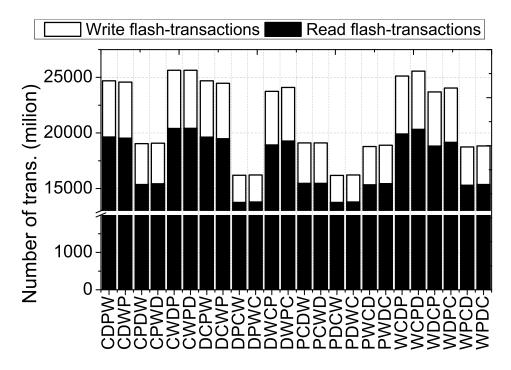

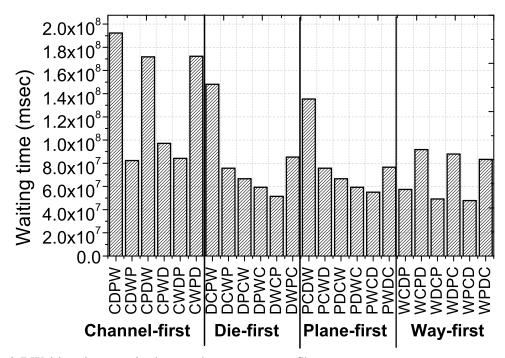

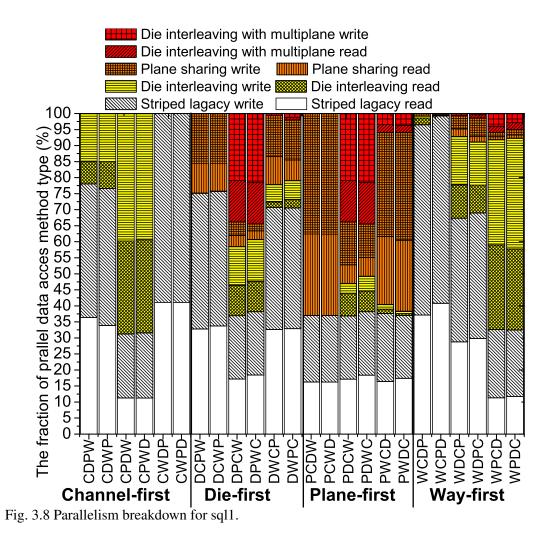

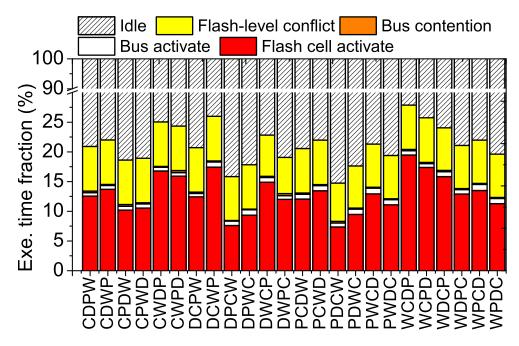

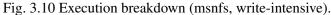

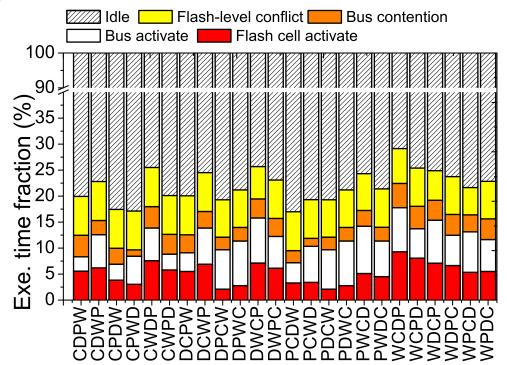

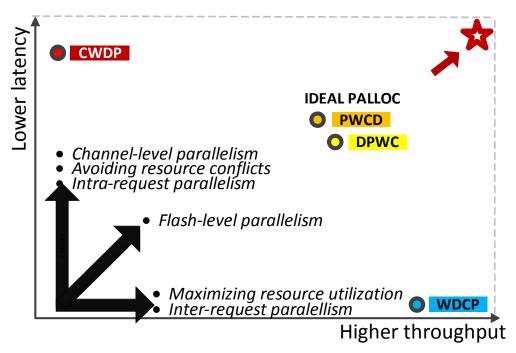

| 3.11                               | Parallelism breakdown for sql1.       .         Average channel utilization.       .         Execution breakdown (msnfs, write-intensive).       .         Execution breakdown (web, read-intensive).       .                                             | 62<br>62<br>63<br>63 |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

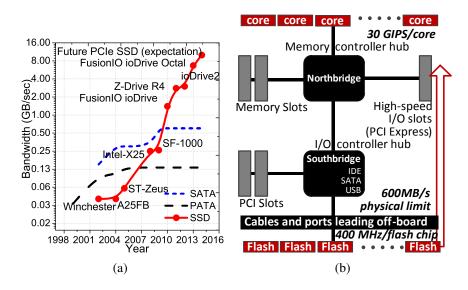

| <ul><li>3.12</li><li>4.1</li></ul> | Performance map with optimizations points                                                                                                                                                                                                                 | 64<br>68             |

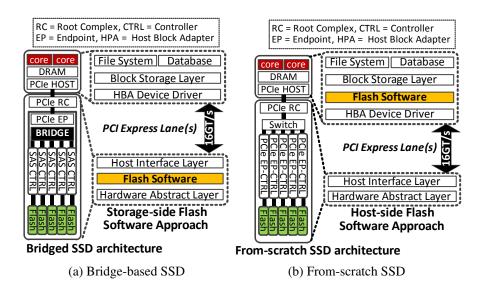

| 4.2                                | storage integration into a place closer to CPU (b)                                                                                                                                                                                                        | 71                   |

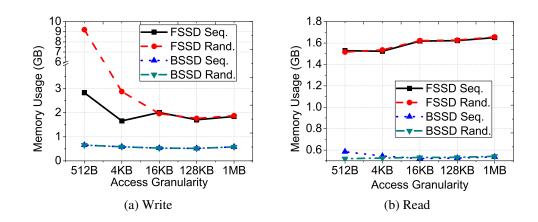

| 4.3<br>4.4                         | Memory usage                                                                                                                                                                                                                                              | 76<br>77             |

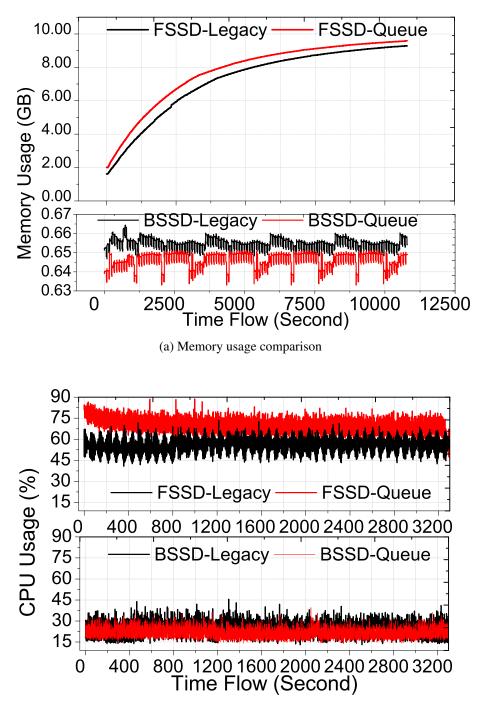

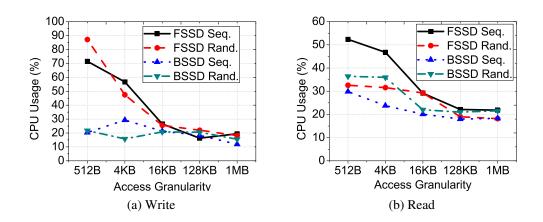

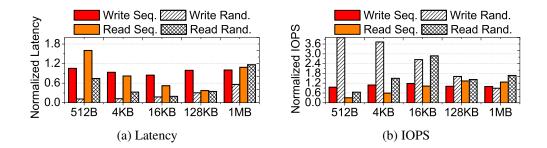

| 4.5<br>4.6                         | CPU usage                                                                                                                                                                                                                                                 | 78                   |

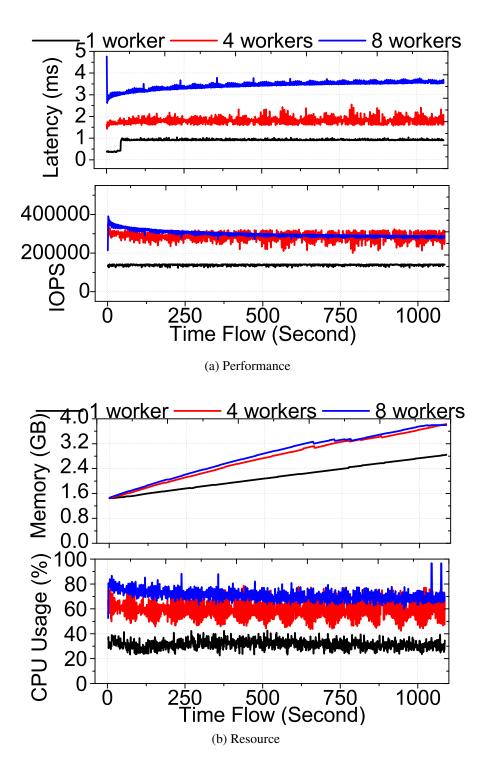

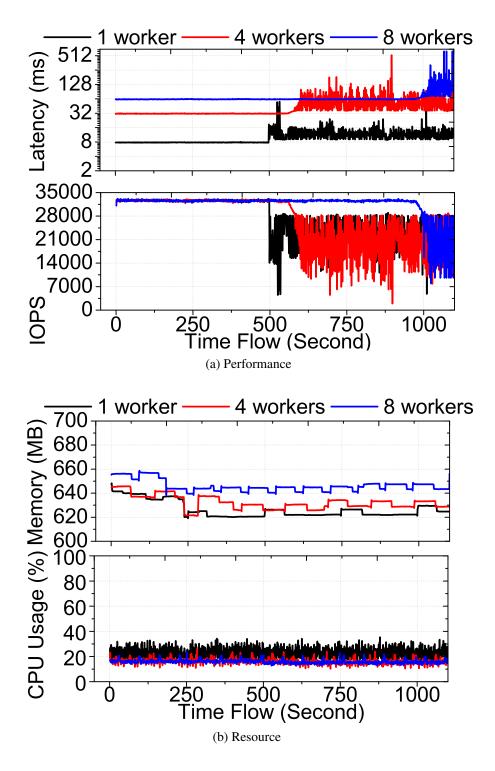

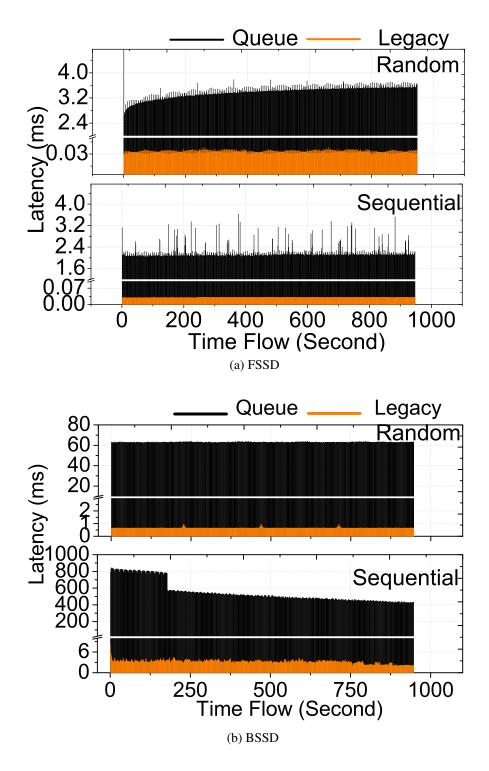

| 4.7<br>4.8<br>4.9                  | of BSSD values are normalized to corresponding values of FSSD FSSD performance characteristics on the multi-core environment BSSD performance characteristics on the multi-core environment Queueing latency comparison observed by FSSD (a) and BSSD (b) | 79<br>81<br>82<br>83 |

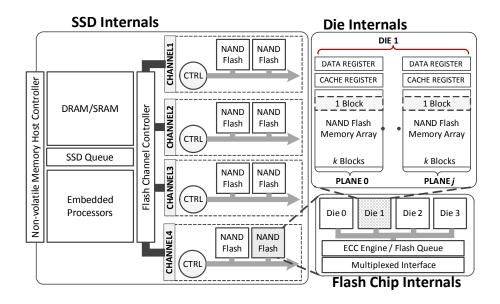

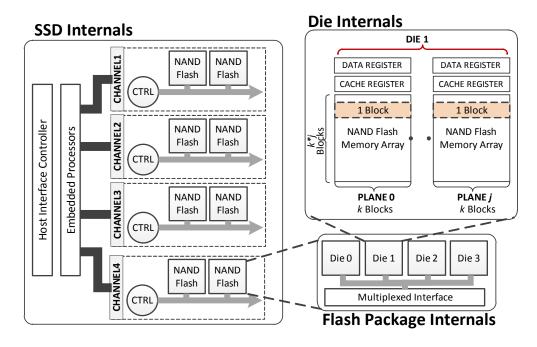

| 5.1                                | Modern SSD internal architecture. Note that an I/O request can be simultane-<br>ously served by many internal resources, which is one of the important charac-                                                                                            |                      |

| 5.2                                | teristics of SSDs                                                                                                                                                                                                                                         | 92                   |

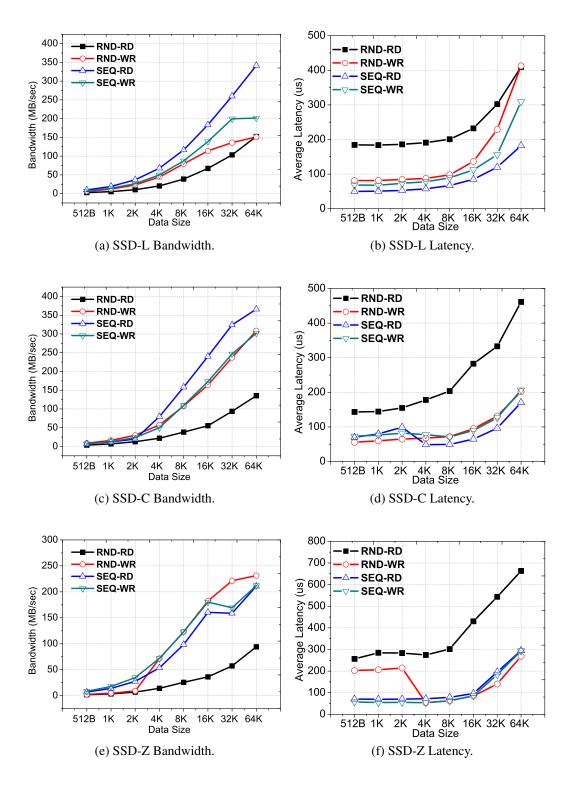

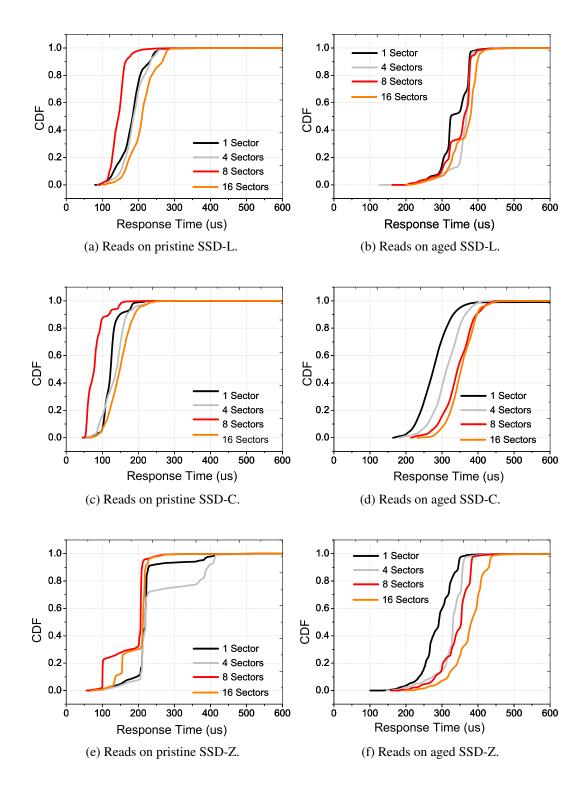

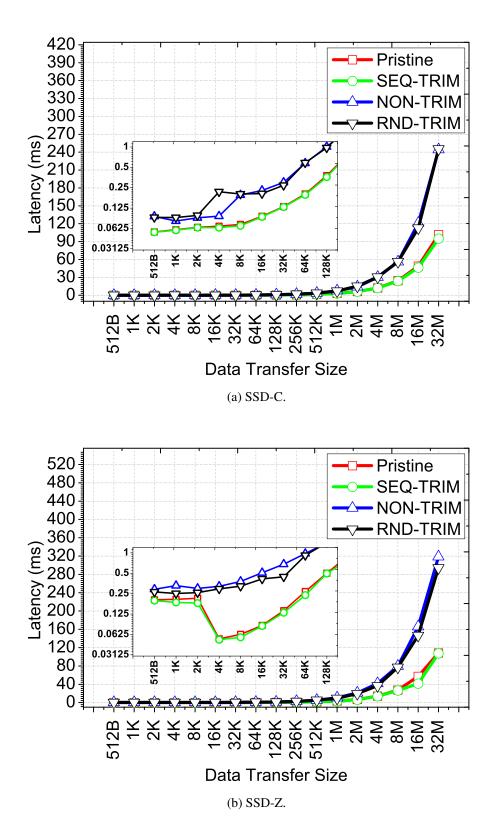

| 5.3                                | read and write                                                                                                                                                                                                                                            | 99                   |

| 5.4                                | pattern to the entire storage space of SSDs). Note that all the curves presented<br>in the CDFs are shifted from left to right as SSDs get older                                                                                                          | 102                  |

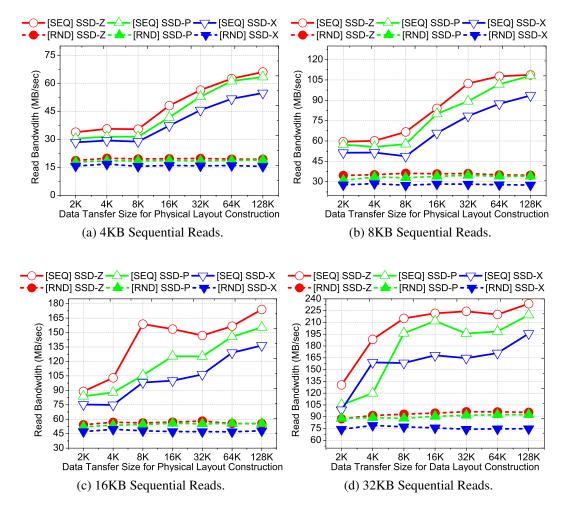

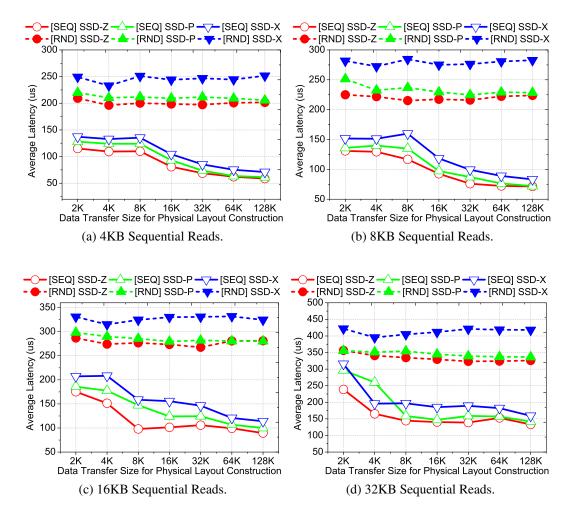

|                                    | quential writes and random writes, used for the physical data ( <i>PDT</i> ) layout construction. Observe that throughput significantly varies based on the physical data layout, constructed by previous writes, even under same read request            |                      |

| 5.5                                | patterns                                                                                                                                                                                                                                                  | 104                  |

|                                    | with SEQ-PDT is shorter than the improvement with RND-PDT that has many resource conflicts potential.                                                                                                                                                     | 106                  |

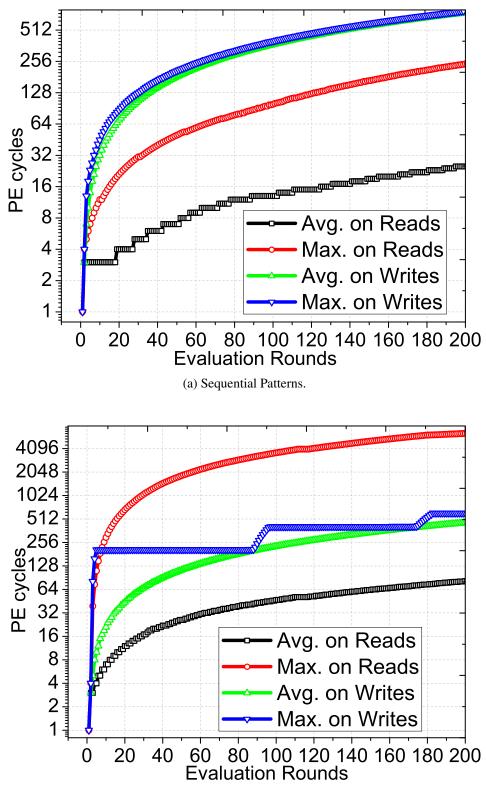

| 5.6                                | PE-cycle comparison between reads and writes. Note that PE cycles increase<br>under read-only workloads. Further, with random accesses, the maximum PE                                                                                                    |                      |

|                                    | cycles on reads are 12 times greater than that on writes.                                                                                                                                                                                                 | 109                  |

xii

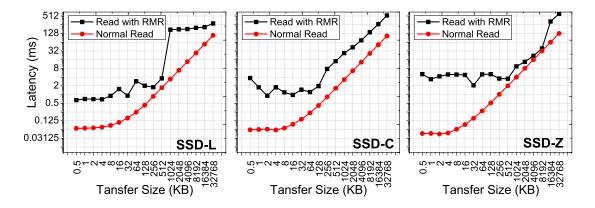

| 5.7          | Latency comparison between reads with reliability management (RMR) and ordinary reads (i.e., reads without RMR). When RMR is employed, the latency |     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|              | is at least 5 times higher than the latency of reads without RMR                                                                                   | 110 |

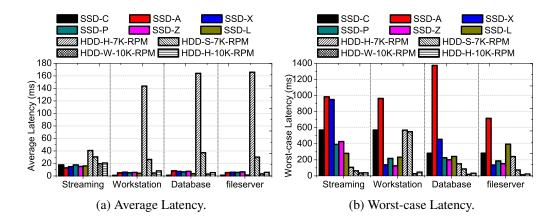

| 5.8          | SSD and HDD latency comparison. While SSDs overall outperform HDDs, the                                                                            | 110 |

| 5.0          | worst-case latencies of SSDs are much higher than the worst-case latencies of                                                                      |     |

|              | 6                                                                                                                                                  | 111 |

| 5.9          | HDDs                                                                                                                                               | 111 |

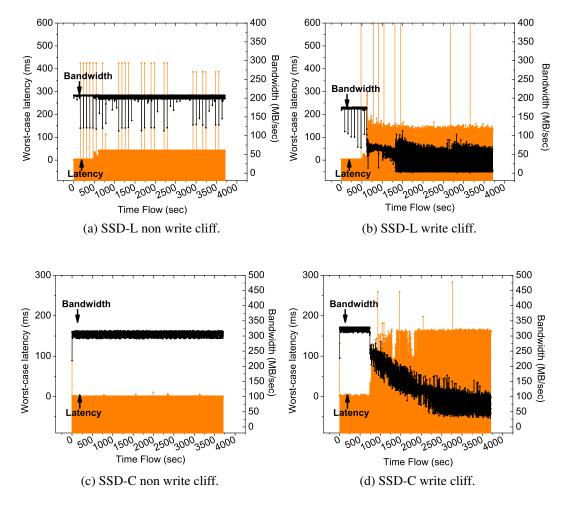

| 5.9          | Impact of write cliff. Initially, SSDs provide reasonable performance even                                                                         |     |

|              | though GCs are invoked. However, once write cliff begins, the performance                                                                          | 110 |

| 5 10         | significantly degrades and is not recovered later.                                                                                                 | 113 |

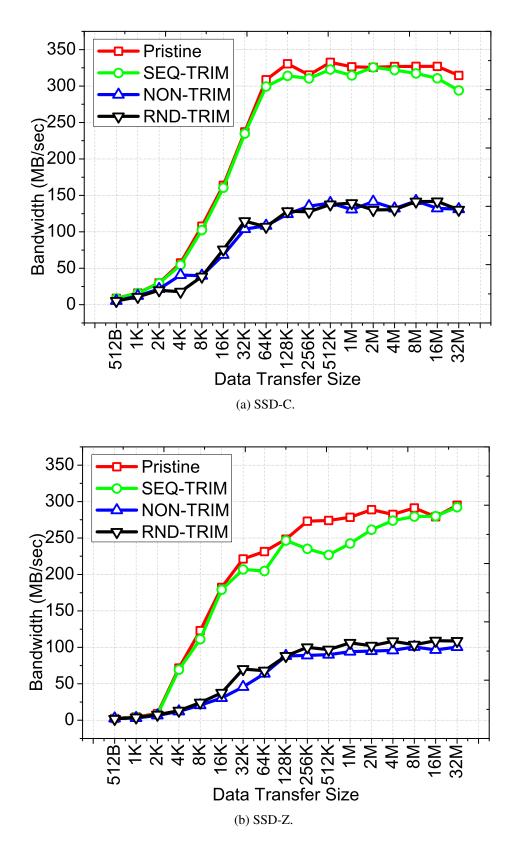

| 5.10         | Worst-case latency correlation between the DRAM buffer cache and GC. The                                                                           |     |

|              | DRAM buffer provides excellent latency, but after the write cliff, it makes la-                                                                    | 117 |

| <b>7</b> 1 1 | tencies even worse.                                                                                                                                | 115 |

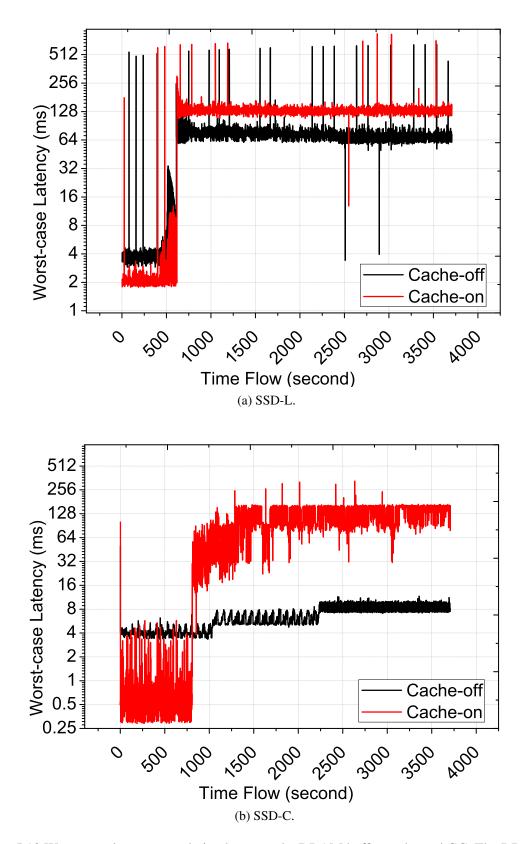

| 5.11         | Bandwidth impact of TRIM. While SEQ-TRIM (the order of target addresses                                                                            |     |

|              | is ascending) can effectively remove GCs, RND-TRIM (the order of targets is                                                                        | 110 |

|              | random) has no impact on GC overheads.                                                                                                             | 116 |

| 5.12         | Latency impact with TRIM. Similar to bandwidth impact, there is no latency                                                                         |     |

|              | gain with RND-TRIMS.                                                                                                                               | 118 |

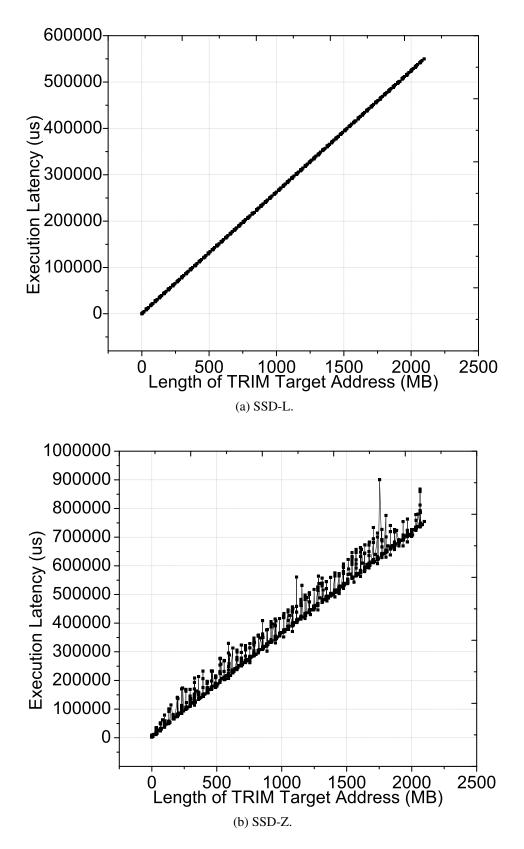

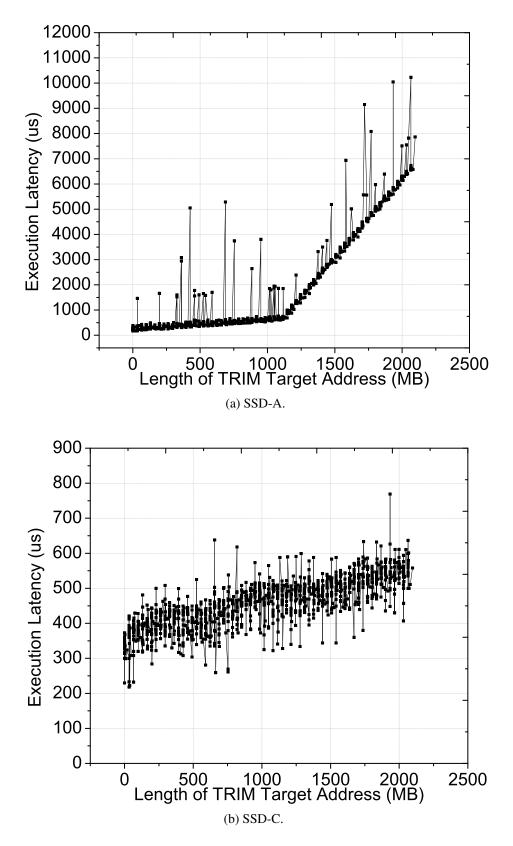

| 5.13         | E-TRIM overheads. Since E-TRIM performs block erasure on demand and do                                                                             |     |

|              | not return control to the storage system, the host can be disabled until the TRIM                                                                  |     |

|              | process finishes.                                                                                                                                  | 120 |

| 5.14         | I-TRIM overheads. I-TRIM is more efficient in controlling the TRIM com-                                                                            |     |

|              | mands, but the latency overheads are still about 6 $\sim$ 153 times worse than a                                                                   |     |

|              | 4KB write-latency.                                                                                                                                 | 121 |

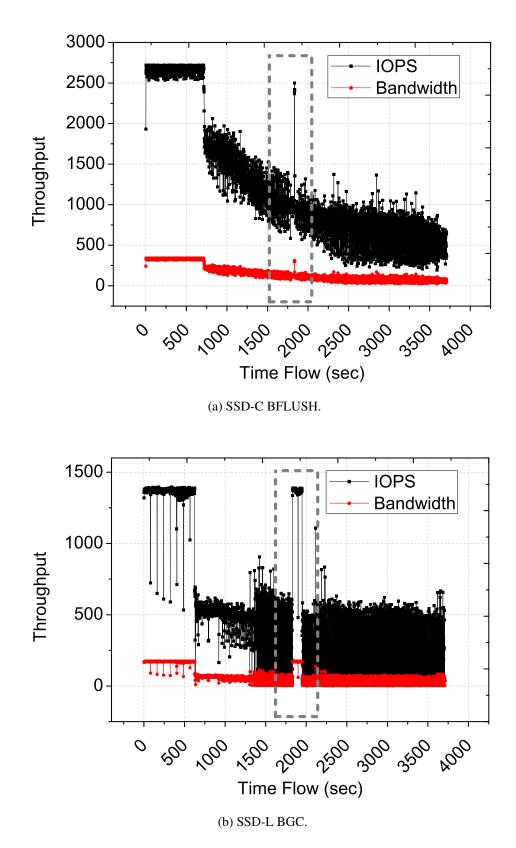

| 5.15         | Performance sustainability of the background tasks. Even though BFLUSH and                                                                         |     |

|              | BGC almost recover the performance on write cliff, they sustain the recovered                                                                      |     |

|              | performance for very short time (just a few seconds)                                                                                               | 124 |

| 6.1          | Physical internal architecture of SSD.                                                                                                             | 133 |

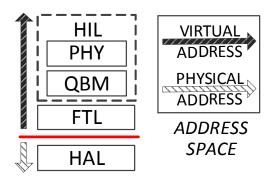

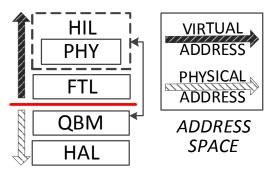

| 6.2          | Software stack of an SSD.                                                                                                                          | 135 |

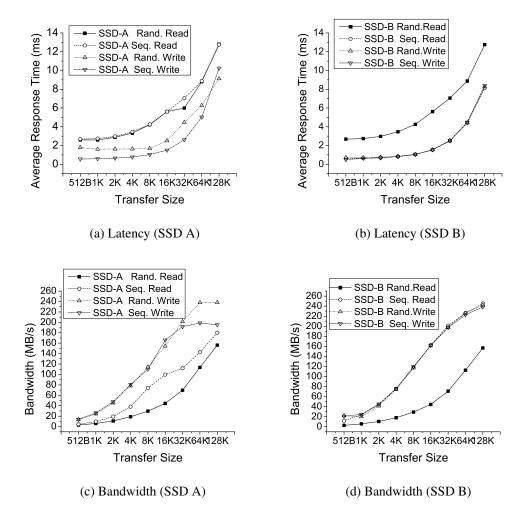

| 6.3          | Average response times and bandwidth results as transfer sizes varies under two                                                                    |     |

|              | commercial SSDs.                                                                                                                                   | 139 |

| 6.4          | Firmware layers within a solid state disk.                                                                                                         | 142 |

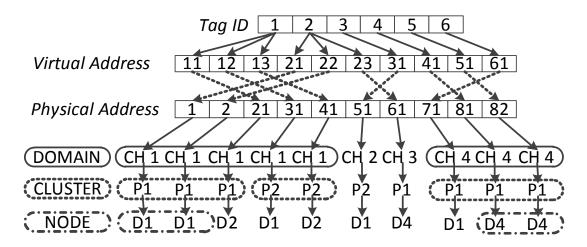

| 6.5          | An example that shows PAQ conflict classification. CH, P and D denote chan-                                                                        |     |

|              | nel, package, and die, respectively.                                                                                                               | 143 |

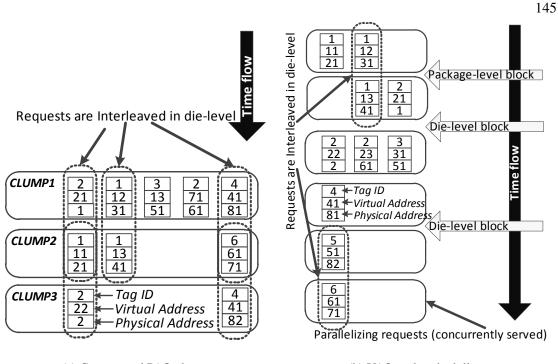

| 6.6          | An example that shows PAQ conflict classification and the associated clumps.                                                                       | 145 |

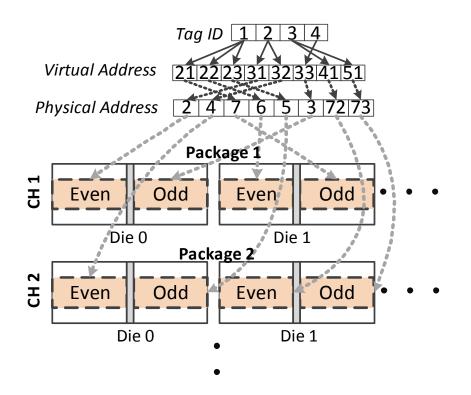

| 6.7          | Plane packing in PAQ.                                                                                                                              | 148 |

| 6.8          | Average bandwidth comparison between VAQ and PAQ.                                                                                                  | 154 |

| 6.9          | Average I/Os per second (IOPS) comparison between VAQ and PAQ.                                                                                     | 154 |

| 6.10         |                                                                                                                                                    | 154 |

|              | Idle times for VAQ and PAQ.                                                                                                                        | 154 |

|              | Normalized total contention time comparison between VAQ and PAQ                                                                                    | 154 |

|              | All latencies incurred for requests from trace sql3 for VAQ and PAQ. Note that                                                                     |     |

| -            | average latencies are shown using a horizontal line in each case.                                                                                  | 157 |

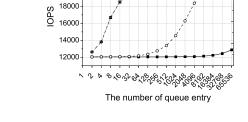

| 6.14         | IOPs sensitivity to varying queue and channel sizes.                                                                                               | 158 |

|              | Waiting time sensitivity to varying queue and channel sizes.                                                                                       | 163 |

|              |                                                                                                                                                    |     |

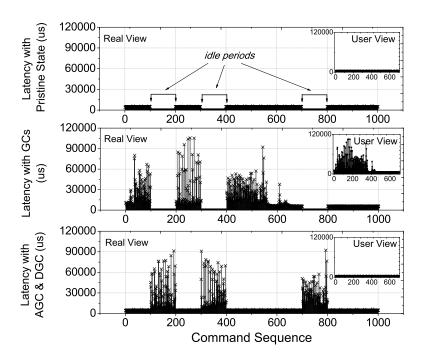

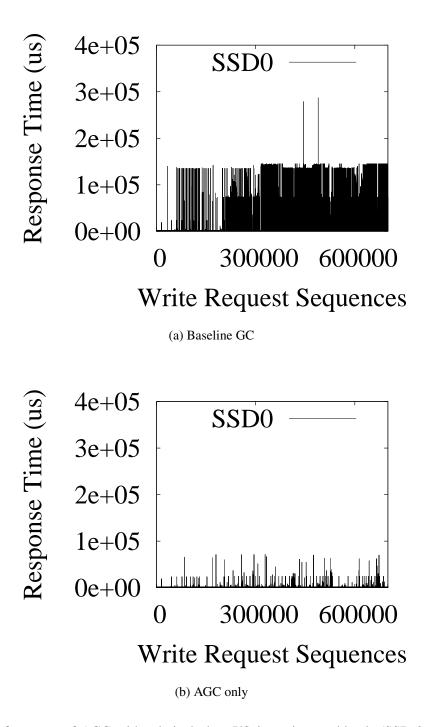

| 7.1         | Overview and comparison of SSD latencies with/without our proposed GC strategies (AGC and DGC), tested by random write pattern with 2048KB re- |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|             | quest size. Note that AGC and DGC shift GC overheads to idle periods (as                                                                       |     |

|             | shown in the real view), thereby providing stable I/O performance like a pris-                                                                 |     |

|             | tine state (as shown in the user view).                                                                                                        | 172 |

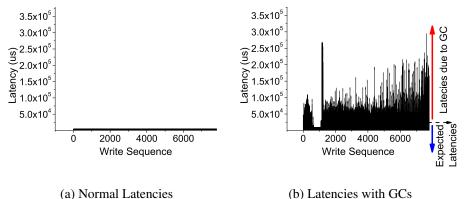

| 7.2         | Latency comparison for a random write access pattern with 1MB request size                                                                     | 1/4 |

| 7.2         | using a real MLC-based SSD.                                                                                                                    | 176 |

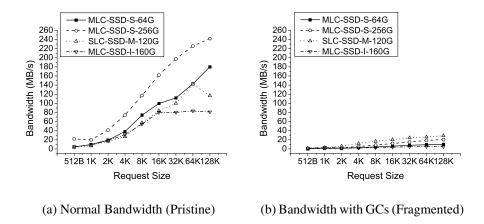

| 7.3         | System throughput for four state-of-the-art SSDs (different vendors and NAND                                                                   |     |

|             | types). Note that all SSDs tested suffer from significant performance degrada-                                                                 |     |

|             | tion once garbage collections begin.                                                                                                           | 177 |

| 7.4         | A high-level view of our proposed GC strategy and idle time utilization                                                                        | 179 |

| 7.5         | An example of the look-ahead GC with a hybrid mapping scheme. By inquiring                                                                     |     |

|             | the mapping information, our AGC scheme figures out that the GC for LBN 1                                                                      |     |

|             | will be invoked soon.                                                                                                                          | 183 |

| 7.6         | Job lists for AGC and DGC.                                                                                                                     | 184 |

| 7.7         | Checkpointing for incremental GC. At each checkpoint, by checking the device-                                                                  |     |

|             | level queue, the garbage collector can decide whether it can perform further                                                                   |     |

|             | collections or not                                                                                                                             | 185 |

| 7.8         | Performance of AGC with relatively low I/O intensive workloads (SSD 0 of                                                                       |     |

|             | 6SSDs-RAID)                                                                                                                                    | 193 |

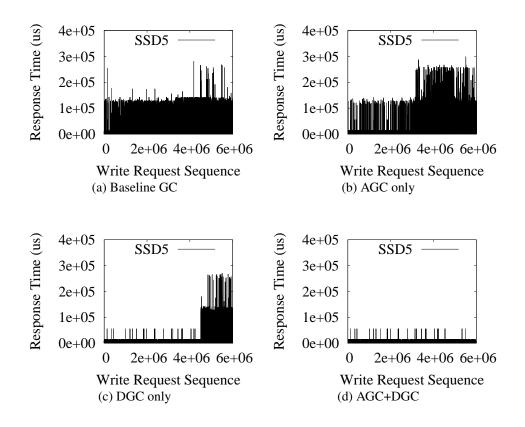

| 7.9         | Performance comparison of different garbage collection strategies (SSD5 of                                                                     |     |

|             | 6SSDs-RAID with high I/O intensive workloads)                                                                                                  | 195 |

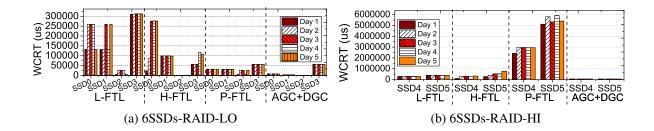

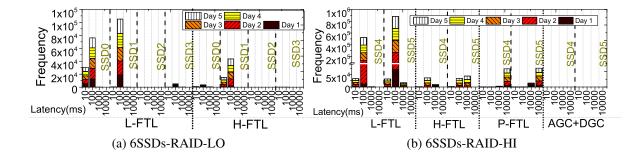

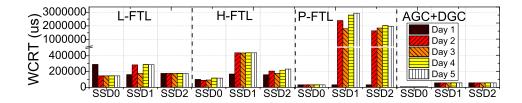

| 7.10        | Worst-case response time (WCRT) analysis for 6SSDs-RAID. (a) With low                                                                          |     |

|             | I/O intensive workloads, P-FTL and AGC+DGC show deterministic behaviors                                                                        |     |

|             | while the performances of L-FTL and H-FTL fluctuate over time. (b) With                                                                        |     |

|             | high I/O intensive workloads, P-FTL experiences very high WCRT, whereas                                                                        |     |

|             | AGC+DGC continues to provide stable I/O performance                                                                                            | 196 |

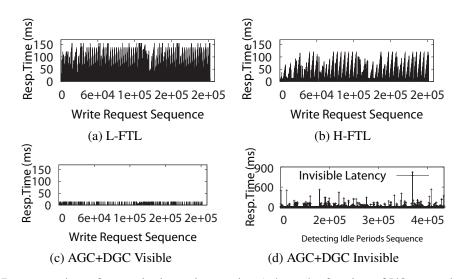

| 7.11        | Response times for a write intensive section (where the fraction of I/O execu-                                                                 |     |

|             | tions with no idle time is account for about 90%). While H-FTL removes about                                                                   |     |

|             | 40% of the GC related overheads, AGC+DGC hides all on-demand GC latencies.                                                                     | 197 |

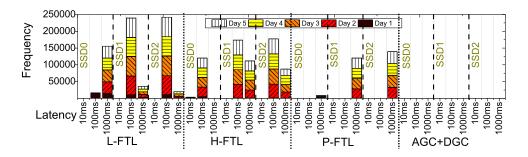

| 7.12        | Excess waiting time (EWT). The x-axis represents the upper bound on EWT.                                                                       |     |

|             | (a) L-FTL and H-FTL experience I/O blocking problem stemming from GCs                                                                          |     |

|             | while P-FTL and AGC+DGC have no such problem. (b) With heavy writes,                                                                           |     |

|             | even though P-FTL results in fewer GC invocations, its GC latencies are much                                                                   | 100 |

| <b>7</b> 10 | longer than others                                                                                                                             | 199 |

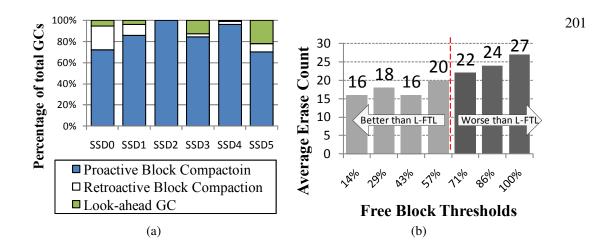

|             | Worst-case response time (WCRT) analysis for the 3SSDs-RAID.                                                                                   | 199 |

|             | Excess waiting time (EWT) analysis for the 3SSDs-RAID.                                                                                         | 199 |

| 1.15        | (a) Garbage collection type breakdown of total collection. (b) Block erase im-                                                                 | 201 |

|             | pact by free block threshold.                                                                                                                  | 201 |

#### Acknowledgments

Chapters 1 and 5, in part, are a reprint of the introduction as it appears in "Revisiting Widely-held Expectations of SSD and Rethinking Implications for Systems," Myoungsoo Jung and Mahmut Kandemir, in Proceedings of the ACM international Conference on Measurements and Modeling of Computer Systems (SIGMETRICS), 2013. The dissertation author was the primary investigator and the first author of this paper.

Chapters 1 and 2, in part, are a reprint of the material as it appears in "NANDFlashSim: Intrinsic Latency Variation Aware NAND Flash Memory System Modeling and Simulation at Microarchitecture level," Myoungsoo Jung, Ellis Herbert Wilson III, David Donofrio, John Shalf and Mahmut Kandemir, in Proceedings of the 28th IEEE Conference on Massive Data Storage (MSST), 2012. The dissertation author was the primary investigator and the first author of this paper.

Chapters 1, 2, and 3, in part, are a reprint of the material as it appears in "An Evaluation of Different Page Allocation Strategies on High-Speed SSDs," Myoungsoo Jung and Mahmut Kandemir, in Proceedings of the 4th USENIX Workshop on Hot Topics in Storage and File Systems (HotStorage), 2012. The dissertation author was the primary investigator and the first author of this paper.

Chapters 1, and 4, in part, are a reprint of the material as it appears in "Challenges in Getting Flash Drives Closer to CPU," Myoungsoo Jung and Mahmut Kandemir, in Proceedings of the 5th USENIX Workshop on Hot Topics in Storage and File Systems (HotStorage), 2013. The dissertation author was the primary investigator and the first author of this paper. Chapters 1, 2, and 6, in part, are a reprint of the material as it appears in "Physically Addressed Queueing (PAQ): Improving Parallelism in Solid State Disks," Myoungsoo Jung, Ellis Herbert Wilson III and Mahmut Kandemir, in Proceedings of the 39th International Symposium on Computer Architecture (ISCA), 2012. The dissertation author was the primary investigator and the first author of this paper.

Chapters 1, and 7, in part, are a reprint of the material as it appears in "Taking Garbage Collection Overheads off the Critical Path in SSDs," Myoungsoo Jung, Ramya Prabhakar and Mahmut Kandemir, in Proceedings of the 13th ACM/IFIP/USENIX 13th International Conference on Middleware (Middleware), 2012. The dissertation author was the primary investigator and the first author of this paper.

#### Chapter 1

#### Introduction

Non-Volatile Memory (NVM) based Solid State Disks (SSDs) have recently become immensely popular and been employed in different types of environments ranging from embedded systems to personal computers to high performance computing (HPC) systems. Moreover, various memory and storage systems have been proposed to take advantage of the performance benefits of SSDs over conventional block devices. For example, to reap up the benefits of high bandwidth on writes, prior HPC studies consider SSDs as a burst buffer [68], which can absorb heavy write traffic caused by check-pointing [83]. There also exist many applications developed under the expectation that NVM is biased toward reads in terms of performance and reliability. Enterprise servers, for example, consider employing SSDs for applications that exhibit many random reads [69, 92, 95] or use them as read caches [54, 7, 61, 82], sitting between main memory and hard disk drive (HDD). Similarly, SSDs are also introduced as a main memory replacement, memory extension, and a part of existing virtual memory systems [24, 23, 25, 92].

While many SSD applications and usage scenarios have been proposed and developed by prior research, modern SSDs and MVM systems have undergone severe technology shift and architectural changes. For instance, NAND flash cells have shrunk from 5x *n*m to 2x *n*m in the past four years, and now fewer electrons are stored per floating gate. These cell-level characteristics make NAND flash devices less reliable and introduce extra operations (e.g., multistep I/O, verification, error correction processes) to successfully complete I/O requests, which in turn imposes longer latencies. State-of-the-art NAND flash packaging technologies employ an increased number of planes and dies within a single flash chip, a command queue, ECC engines, and faster data movement interfaces [17, 81]. In parallel, SSD internal architecture has dramatically changed; modern SSDs now employ multiple internal resources such as flash chips, I/O buses, and cores in an attempt to achieve high internal parallelism. In addition, to reduce garbage collection overheads, NVM firmware employs advanced strategies such as finergranular address mapping algorithm. As a result of complex interactions among these different mechanisms, modern SSDs can be plagued by enormous performance variations depending on whether underlying architectural complexities and NVM firmware overheads can be hidden or not.

Fig. 1.1 Design and optimization goal of a smart NVM controller. Modern SSDs can be plagued by enormous performance variations depending on whether underlying architectural complexities and NVM firmware overheads can be hidden or not. Designing a smart NVM controller is key hiding the architectural complexities and reducing the internal firmware overheads.

As shown in Figure 1.1, designing a smart NVM controller is key to hiding the architectural complexities and reducing the internal firmware overheads; hiding complexity of writes, such as garbage collection overheads and low resource utilization, is crucial for achieving higher throughputs, and alleviating complexity on reads such data movement overheads and resource contention is key to offering lower latencies of modern SSDs. To this end, we first model a multi-plane and multi-die NVM architecture, which is highly reconfigurable and aware of intrinsic latency variation imposed by various state-of-the-art NVM systems. This NVM model has been implemented as a high fidelity open-source simulator, capable of capturing cycle-level interactions between the many components in an SSD, which can be used for various NVM performance analyses. Based on this architecture model, we then explore twenty four different concurrency methods implemented in NVM controllers, geared toward exploiting both systemlevel and NVM-level parallelism with a variety of design parameters. Further, we quantitatively analyze the challenges faced by PCI Express-based (PCIe) SSDs in getting NVM closer to CPU, conduct a comprehensive data analysis and uncover critical storage-class SSD/flash characteristics, which are not reported, to the best of our knowledge, in the literature so far, and are opposite to the widely held expectations on SSDs.

In this dissertation, we also perform a comprehensive set of experiments using diverse commercial SSDs (e.g., drawn from different SSD makers, NVM types, SSD internal architectures) and analyze them in an attempt to show practical significance of read performance degradations and write performance variations. Specifically, in cases where read access patterns are mainly random, the read performance can be worse than that of writes due to architectural complexities; internal resource conflicts and contentions occur among multiple incoming I/O requests, which can in turn introduce long system-level I/O pending times. In contrast, write

performance significantly varies based on patterns exhibited by garbage collections, which are an essential device-level activity, performed by an NVM firmware module in SSDs. The biggest challenge with existing garbage collectors is that their worst-case latency can be  $64 \sim 128$  times higher than that of normal write operations. Our experiments show that garbage collectors introduce numerous blocking I/Os, and once a garbage collection operation begins, the response time of write operations on SSD increases substantially. Further, garbage collection overheads significantly reduce available bandwidth in most recent commercial SSDs.

To address these challenges behind reads and writes that state-of-the-art SSDs face, we propose two different types of schedulers, which can be implemented in NVM controllers: (1) Physical Address Queuing (PAQ) scheduler (tacking the read performance degradation issue) and (2) NVM garbage collection scheduling algorithm (geared toward addressing the write performance variation issue). Specifically, PAQ is a novel I/O request scheduler that avoids resource contention resulting from shared SSD resources. Our proposed PAO dramatically improves read performance by exposing the physical addresses of requests to the SSD controllers/schedulers and selecting groups of I/O operations that can be simultaneously executed without major resource conflict. In parallel, our proposed NVM garbage collection scheduler that removes garbage collection overhead and provides stable I/O performance in SSDs during the I/O congestion periods. Our proposed garbage collection scheduler consists of two garbage collection strategies, namely, Advanced Garbage Collection (AGC) and Delayed Garbage Collection (DGC). AGC tries to secure free blocks and removes on-demand garbage collections from the critical path in advance, so that users do not experience garbage-collection-induced latencies during the I/O-intensive periods, whereas DGC handles the collections that AGC could not handle, by delaying them to future idle periods. While the PAQ scheduler mainly targets to improve read performance by avoiding resource conflicts, this garbage collection scheduler alleviates the write amplification factors posed by modern SSDs, thereby improving write performances and making them stable.

The rest of this dissertation proposal is organized as follows. In Chapter 2, we model a modern multi-die and multi-plane NAND flash architecture at a cycle-level. In Chapter 3, we study twenty four concurrency methods to understand details of internal parallelism. In Chapter 4, we quantitatively characterize the challenges faced by PCI Express-based (PCIe) SSDs in getting NVM closer to CPU, and in Chapter 5, we question popular assumptions and expectations regarding storage-class SSDs through an extensive experimental analysis. We then analyze the performance degradation in reads using different experiments and propose a novel I/O request scheduling strategy (PAQ) with the goal of removing this performance degradation in Chapter6. In addition, we show the significance of garbage collection overheads in modern SSDs and propose a garbage collection scheduler in order to make garbage collection overheads invisible to users by exploiting device-level idleness in Chapter 7. We finalize by discussing potential near-term and long-term future directions.

#### Chapter 2

#### NAND Flash Memory System Modeling and Simulation

#### 2.1 Introduction

While processors have enjoyed doubled performance every 18 months, and main memory performance increases roughly 7% in the same time frame, non-volatile storage media has been stuck at a standstill for nearly a decade [86]. Many efforts have been made to remedy such a great gap, and NAND flash has positioned itself at the forefront of such efforts. Since NAND flash is hundreds to thousands of times faster than conventional storage media and has a small form factor, it has been employed in the construction of devices such as Solid State Disks (SSD), Compact Flash, and Flash Cards. NAND flash density is increasing by two to four times every two years [66], which is in turn decreasing its cost and enabling wide-spread deployment in arenas as diverse as embedded systems and high-performance computing. In addition, by introducing multiple planes and dies, the NAND flash memory is expected to continue in this trend as it experiences the same ease of scaling multiprocessors currently enjoy. As a result of such proliferation, performance, energy consumption, and reliability of NAND flash memory are becoming increasingly important [100]. Further, this proliferation also results in a diversification of target system configurations, such as additional Flash Translation Layer (FTL) logic positioned atop flash, which is often tailored to the demands of various NAND-flash based applications. However, because NAND flash is very sensitive to a large number of parameters, and some latency parameters fluctuate between best-case and worst-case [27], deciding on an optimal NAND

flash memory system's configuration is non-trivial. Furthermore, NAND flash memory can have many different parameters depending on what memory system types are employed (e.g., single level cells (SLC), multi level cells (MLC), diverse node technologies (fabrication processes), page sizes, register management policy, memory density, and pin configurations). Consequently, this large parameter space and sensitivity of NAND flash to such parameters results in memory systems exhibiting significantly different behaviors.

(a) Existing SSD simulations

(b) The proposed NAND simulation

Fig. 2.1 Concept of a  $\mu$ arch-level NAND flash simulation model (NANDFlashSim). While existing SSD simulators are highly coupled to flash firmware emulation with simplified latency model, NANDFlashSim simulates NAND flash memory system itself with independently synchronous clock domains and detailed NAND operation timing models aware of latency variation.

Unfortunately, a comparison between different types of NAND flash memory systems becomes even harder when multi-die and multi-plane architectures are considered [22]. In these architectures, scheduling methods and arbitration [85] among multiple dies and planes are important factors in determining I/O performance [22]. However, incorporation of these methods and arbiters results in a greatly increased complexity of flash firmware and controllers. Even though simulation-based prior research [32, 60, 70, 1] reveals performance tradeoffs in an application level, the main focus of such studies has been on SSD rather than the NAND flash memory system itself; this difference is pictorially shown in Figure 2.1(a). Such simulations make several assumptions that ignore, to varying extents, the fluctuating timing behaviors of the diverse I/O operations supported by state-of-the-art NAND flash memory. These assumptions range from extremely widespread, where the SSD is modelled as having constant time and energy per I/O request, to more confined but still overly simplified, where dies and planes are modelled but the interactions between various NAND commands and components are still represented with *constants*. This implies that the existing simulation models used in those prior studies are strongly coupled to particular flash firmware and policies – performing the exact same study using slightly different firmware or policy-set has the potential to result in wildly different performances and conclusions. Using such imprecise timing models of NAND flash and NAND operations, hardware and system designers may overlook opportunities to improve memory system performance. Furthermore, as shown in Figure 2.2, since such prior studies are oblivious of *intrinsic latency variation* of NAND flash, they are not be able to properly model diverse node technologies. Also, simplified latency models ignore the substantial contributions of the flash firmware to memory system performance. This may result in these designers overlooking research potential regarding new algorithms in/on NAND flash memory systems, such as those involved in internal parallelism handling, wear-leveling, garbage collection, the flash translation layer, flash-aware file systems, flash controllers, and so on.

To address heretofore mentioned drawbacks, the introduction of a microarchitecture ( $\mu$ arch) level NAND flash memory system simulation model that is decoupled from specific flash firmware and supports detailed NAND operations with cycle-accuracy is required. This

Fig. 2.2 Intrinsic Latency Variation Example.

low-level simulation model can enable research on the NAND flash memory system itself as well as many NAND flash-based devices, as illustrated in Figure 2.1(b). Specifically, in this Chapter, we propose *NANDFlashSim*; a latency variation-aware, detailed and highly reconfigurable  $\mu$ arch-level NAND flash memory system based on multi-die and multi-plane architectures. To the best of our knowledge, NANDFlashSim is the first simulation model to target the NAND flash memory system itself at  $\mu$ arch-level, and the first model to provide sixteen latency variation-aware NAND flash operations with NAND command set architecture.

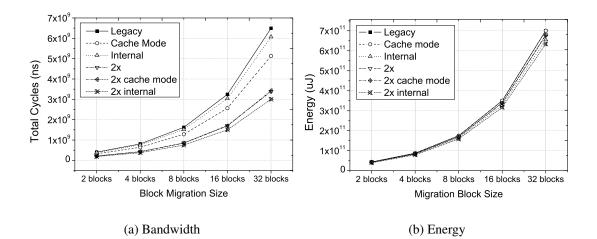

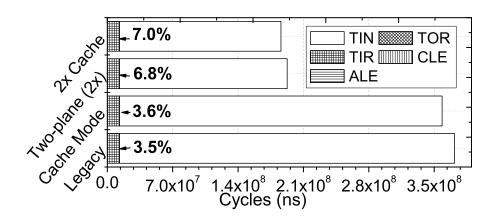

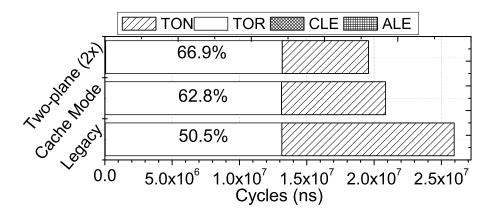

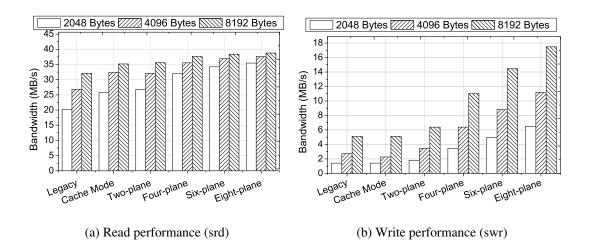

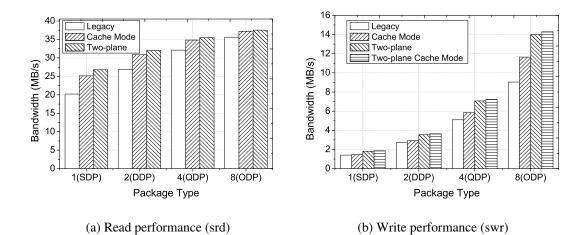

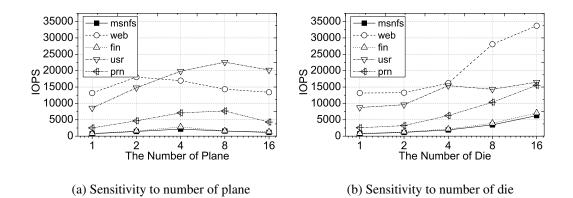

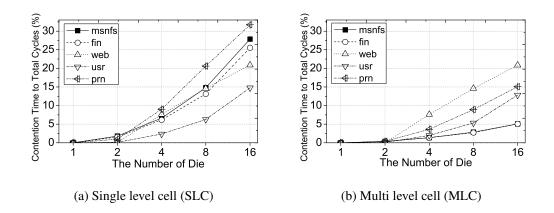

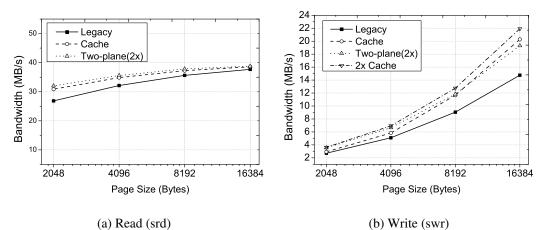

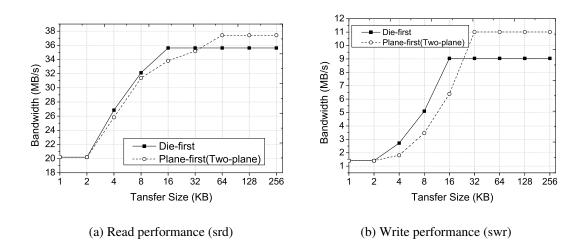

From our comprehensive experiments using NANDFlashSim, we found that 1) most read cases were unable to leverage the highly-parallel internal architecture of NAND flash regardless of the NAND flash operation mode. Specifically, the read throughputs improvements between quad dies and octal dies, between four-plane and eight-plane, and between 4KB and 8KB page size are 10.9%, 10.8%, and 10.9%, respectively, while the write throughputs are improved by 91.2% on average. 2) the main contributor of performance bottleneck is I/O bus activity, not NAND flash activity itself. 50.5% cycles of total I/O execution cycles are consumed by operations related to such I/O bus activity. The bottleneck is more problematic when *advance NAND flash commands* (e.g., cache and multi-plane mode) are applied. 3) MLC NAND flash provides lower I/O bus resource contention than SLC NAND flash, but such resource contention

becomes a serious problem as the number of dies increases, and 4) preference of employing many dies rather than employing many planes provides average 54.5% better performance in terms of throughput in disk-friendly workloads [88]. This Chapter makes the following main **contributions**:

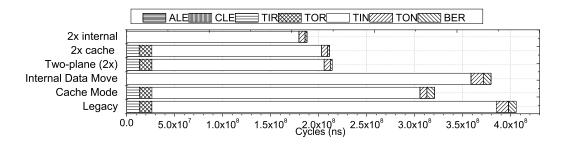

• Detailed Timing Model: NANDFlashSim presents a  $\mu$ arch-level flash simulation model for many NAND flash-based applications. The memory system, controller and NAND flash memory cells have independent synchronous clock domains. In addition, by employing multi-stage operations and command chains for each die, NANDFlashSim provides a set of timing details for a large array of NAND flash operation modes including: legacy mode, cache mode, internal data move mode, multi-plane mode, multi-plane cache mode, interleaved-die mode, interleaved-die cache mode, interleaved-die multi-plane mode, and interleaved-die multiplane cache mode. These detailed NAND operation modes and their associated timings expose performance optimization points to NAND flash-based application designers and developers.

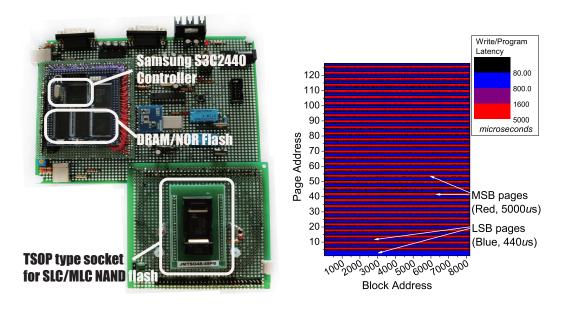

• Intrinsic Latency Variation-Aware Simulation Model: NAND flash memory, especially MLC, suffers from intrinsic performance variations when accessing a block. In our observations, write latency of [75] and [34] varies between  $250\mu$ s to  $2,200\mu$ s and  $440\mu$ s to  $5,000\mu$ s, respectively (maximum latencies are  $8.8 \sim 11.3$  times higher than minimum latencies). Therefore, NANDFlashSim, a cycle-accurate simulation model, is designed to be performance variation-aware and employs different page offsets in a physical block. To collect statistics related to the performance variation and validate our simulation model accuracy, we prototype a NAND flash hardware platform, called Memory Statistic Information System (MSIS). We present a comprehensive evaluation considering different types of NAND flash and NAND operation on both NANDFlashSim and MSIS. • *Reconfigurable Micoarchitecture:* NANDFlashSim supports highly reconfigurable architectures in terms of multiple dies and planes. This architecture allows a researcher to explore true internal parallelism in such an architecture by exposing the intrinsic latency variations in NAND flash. In contrast to prior simulation models, NANDFlashSim removes the dependency on a particular flash firmware, which enables memory system designers and architects to develop and optimize diverse algorithms targeting NAND flash such as buffer replacement algorithms, wear-leveling algorithms, flash file systems, flash translation layers, and I/O schedulers.

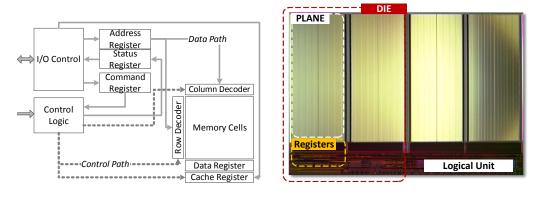

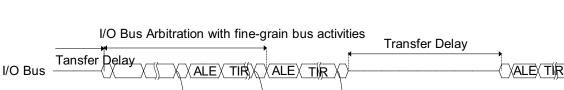

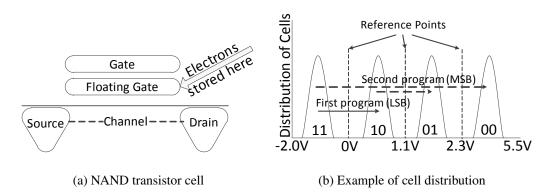

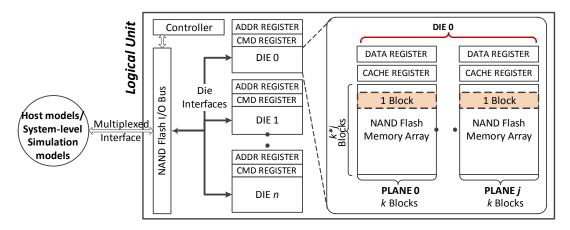

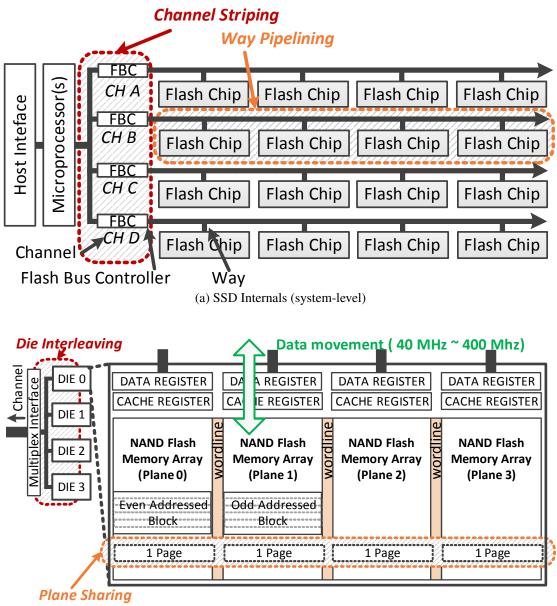

#### 2.2 NAND Flash Microarchitecture

Figure 2.3(a) illustrates the NAND flash microarchitecture [75], and Figure 2.3(b) depicts the physical NAND memory cell microphotograph [94]. Energy consumption and interface complexity are important factors in NAND flash memory system design. Therefore, interfaces for data, commands, and addresses are multiplexed onto the same I/O bus, which helps to reduce pin counts, interface complexity, and energy consumption [75]. Because of this, a host model must first inform the NAND flash package that it wishes to use the I/O bus through control logic before acquiring it. This information is provided via control signals like *command latch enable* (CLE) and *address latch enable* (ALE). Similarly, NAND commands are responsible for signalling usage of the I/O bus in addition to classifying following NAND operation types.

• *Page/Block.* A page is a set of NAND memory cells, and a block is a set of pages (typically 32~256 pages). A physical NAND block makes up a plane.

• *Register*. Registers are adopted to provide collection and buffering for delayed writeback of small writes and to fill the performance gap between the NAND flash interface and flash memory cells. Supporting multiple registers is a common trend to boost NAND flash memory performance. NAND flash is typically composed of a set of cache and data registers.

• Plane. A plane is the smallest unit that serves an I/O request in a parallel fashion. In

practice, physical planes share one or more word-lines for accessing NAND flash cells, which enables the memory system to serve multiple I/O requests simultaneously [65].

• *Die.* A die contains an even number of planes and constitutes a NAND flash package.

Depending on how many dies are placed into a package, a NAND flash memory is classified as a single die package (SDP), dual die package (DDP), quad die package (QDP), or octal die package (ODP).

• *Logical Unit.* A logical unit consists of multiple dies, and is the minimum unit that can independently execute commands and report its status. Multiple dies in a logical unit are interlaced by a chip enable (CE) pin, leading to a reduction in I/O bus complexity and total pin counts.

(a) NAND flash microarchitecture

Fig. 2.3 NAND flash memory system internals.

Since the number of dies sharing the I/O bus and CE pins is determined at packaging time, different numbers of logical units are used in DDP, QDP and ODP. Although state-of-theart NAND flash provides at most four planes [94] and eight dies, our proposed simulation model can be configured to simulate a much larger number of planes and dies in a logical unit.

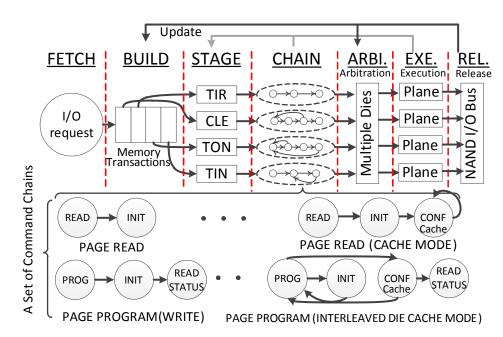

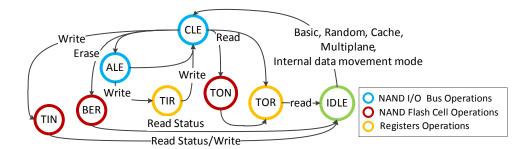

#### 2.3 NAND Flash Operations

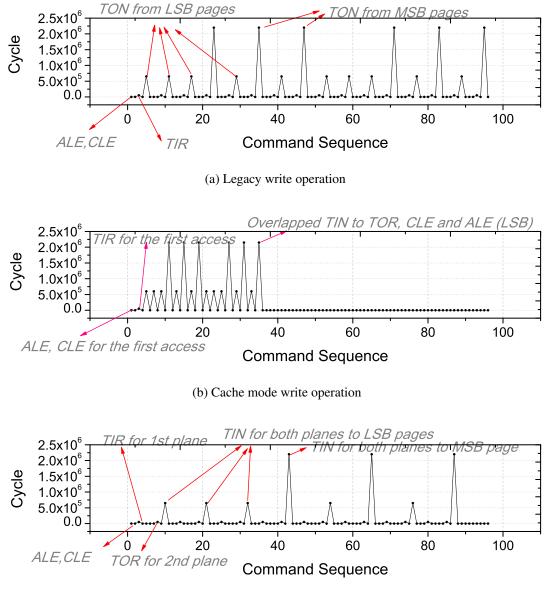

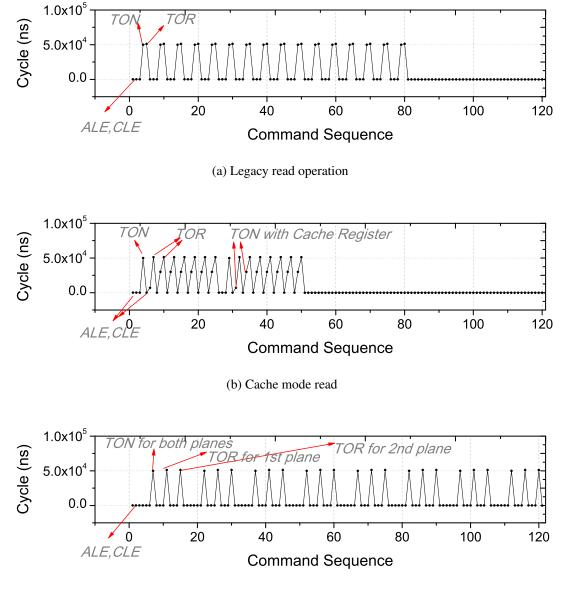

Legacy NAND operations can be classified into three types: read, write (also referred to as program), and *erase*. While reads and writes operate at a *page* granularity, erase operation executes on an entire block. To operate NAND flash memory, the first task is to load a command into the command register by raising the CLE signal, which informs what operation will be executed. After that, a start address for the operations is loaded into an internal address register by raising the ALE signal. Once the address is loaded, the NAND operation can be issued by loading the initiate command. Each of the NAND operations has different timings for data movement. For reads, a page of data is loaded from specific NAND memory cells into the data register. This data movement stage is called *transfer-out of NAND memory cells* (TON). Then, data are sequentially output from the register, byte by byte, which is a process termed *transfer*out of register (TOR). In the case of a write operation, after the address is loaded, the data can be stored in the data register. This data movement stage, called *transfer-in of register* (TIR), should be processed before loading the initiate NAND command. Following TIR, the NAND flash memory system starts to write data from the register to NAND memory cells, called transfer-in of NAND cell (TIN) stage. In addition to these basic operations, state-of-the-art NAND flash memories support more complex operations to improve system performance [22]. Below, we explain different I/O modes, which are used in concert with these legacy commands.

#### 2.3.1 Cache Mode Operation

In *cache mode* operation, data are first transferred to a cache register and then copied to a data register. After that the NAND flash memory system enters the TIN stage. In the meantime, the memory system is available again for TIR stage operations using the cache register because only the data register and memory cells are involved in writing. This cache mode operation overlaps the process of putting data into register and that of writing data into the NAND memory cells, thereby hiding the TIR time. Just like writes, read operations can also take advantage of the cache register. However, in our observations, cache mode operations demonstrate slightly different performances between reads and writes. This is due to the latency-dominating NAND operation differing between, which will be further discussed in Section 2.8.

#### 2.3.2 Internal Data Move Mode Operation

Flash applications may need to copy data from a source page to a destination page on the same NAND flash memory. Since data movement from one location to another within flash memory requires external memory space and cycles, a data copy is suprisingly expensive and time consuming. To reduce the time required to copy data, state-of-the-art NAND flash memory support *internal data move* operations. In these operations, a host is not involved in managing the data copy process. Instead, the host only has to load the source and destination address for copying data into the address registers, and commit the internal data move mode NAND command. Then, the NAND flash memory reads data from the source using the data register and directly writes it to its destination, without any data transfer involving the host model. That is, in internal data movement operation mode, data in one page of NAND memory destined for another page can be copied without any external memory cycles. This specialized operation alleviates the overheads of data copying, which notably results in greatly enhanced garbage collection performance [11], a critical task of flash firmware.

#### 2.3.3 Multi-plane Mode Operation

*Multi-plane mode* operations serve I/O requests using several planes at a time that are connected by word-line(s). Specifically, these operations can enhance performance up to *n* times, where *n* is the number of planes in a word-line. However, the multi-plane architecture carries with it limitations for addressing planes. Specifically, in multi-plane mode operations, I/O requests should indicate the same page offset in a block, same die address, and should have different plane addresses [75, 80]. These constraints are collectively referred to as the *plane addressing rule*. Therefore, performance enhancement using a multi-plane architecture may be limited based on user access patterns (we will discuss this issue in Section 2.8.5). Regulating plane addressing rules is required to obtain realistic performance with the multi-plane mode of operation. Using such rules, NANDFlashSim provides an accurate implementation of multi-plane mode operations, which may be used in any combination with other NAND flash operations.

#### 2.3.4 Interleaved Die Mode Operation

State-of-the-art flash memory share between one and four I/O buses among multiple dies in order to reduce the number of pins. While sharing the I/O bus reduces energy consumption and complexity, I/O bandwidth of the system also reduces. This is because all NAND operations except those related to NAND memory cells (e.g., TON, TIN) should acquire permission to use the I/O bus before they start executing. Thus, efficient bus arbitration and NAND command

Timings are simplified with the assumption that such timings are perfectly overlapped

TIN (MSB, 2200 microsec)

TIN (MSB, 2200 microsec)

Transfer Delay

TIN (LSB, 250 microsec)

XALE X TIR X TIN

DIE 0

DIE 1

DIE 2

Time line ALE TIR ALE TIR

(a) A typical-case timing parameter based simulation model

(b) Latency-aware NANDFlashSim

TIN

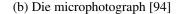

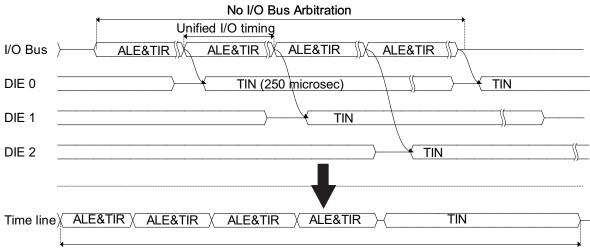

Fig. 2.4 A timing diagram of interleaved die with four legacy writes. While an existing simulation model simplifies bus activities and assumes that latencies are perfectly overlapped and interleaved with constant time, NANDFlashSim employs fine-grain bus activities and is aware of intrinsic latency variations.

XALEXTIRX

scheduling policies are critical determinants of memory system performance. *Interleaved die mode* operations provide a way to share the I/O bus and take advantage of internal parallelism by interleaving NAND operations among multiple dies. Unlike multi-plane mode operations, interleaved-die mode operations have no addressing restrictions.

It should be noted that all NAND operations discussed above can be used in any combination with interleaved-die operations. For example, a host model can issue an interleaved-die multi-plane mode operation, which stripes a set of multi-plane mode operations across multiple dies. Similarly, interleaved-die multi-plane cache mode operations are possible, which are operations that have the properties of operating in cache mode, being striped over multiple dies and being applied to multiple planes. A simplified and approximated latency circulation model with constant times is unable to capture the behavior of and interactions between these different types of operations. Furthermore, intrinsic latency variations exhibited by the NAND flash make it difficult for a latency model with constant time to mimic elaborate bus arbitration or scheduling NAND commands.

Consider the comparison, shown in Figure 2.4, between the existing simulation model (with constant time) and variation-aware NANDFlashSim. In the figure, four I/O requests are striped over three dies with interleaved-die legacy write mode. Existing simulation models will calculate the latency under the assumption that *timings are perfectly overlapped and interleaved*. Let  $t_{io}$  denote execution time for I/O activities, and  $t_{prog}$  denote programing (write) time. Suppose that  $n_{io}$  denotes the number of the write requests, and  $t_{resp\_legacy}^{interleaved}$  denotes the response time for  $n_{io}$  requests, In existing simulation models,  $t_{resp\_legacy}^{interleaved}$  is simply calculated by  $n_{io} * t_{io} + t_{prog}$  as shown in the time line of Figure 2.4(a). However, in practice,  $t_{resp\_legacy}^{interleaved}$  varies significantly based on system configurations. This is because  $t_{prog}$  fluctuates based on the access address and the

transfer delay time is also varied by the service order. In contrast, NANDFlashSim is aware of latency variation and provides a method for scheduling NAND commands and activities with fine granularity.

#### 2.4 Intrinsic Latency Variation of NAND Flash