# The Pennsylvania State University

#### The Graduate School

# Graduate Program in Materials Science and Engineering

# CHARACTERIZATION OF LASER FIRED CONTACTS, LASER DOPED EMITTERS, AND FIXED CHARGE PASSIVATION FOR IMPROVED SILICON SOLAR CELLS

A Thesis in

Materials Science and Engineering

by

Brittany Lynn Hedrick

© 2011 Brittany Lynn Hedrick

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science

August 2011

The thesis of Brittany Lynn Hedrick was reviewed and approved\* by the following:

Suzanne E. Mohney Professor of Materials Science and Engineering Thesis Co-advisor

Joseph R. Flemish Professor of Materials Science and Engineering Thesis Co-advisor

S. Ashok Professor of Engineering Science

T. DebRoy Professor of Materials Science and Engineering

Joan M. Redwing

Professor of Materials Science and Engineering

Chair, Intercollege Materials Science and Engineering Graduate Degree Program

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

With the introduction of laser processing into silicon solar cell manufacturing, characterization and understanding of laser-material interactions and laser fired device performance is critical. To assess laser doping of the front-side emitters and laser firing of the rear-side contacts of silicon solar cells, several experiments were carried out to create and characterize laser fired contacts (LFCs) and laser doped emitters (LDEs). Additionally, an investigation of fixed charge layers for increased surface passivation performance was performed.

A cross-sectioning and selective plating method was developed to characterize the molten region of LFCs created with varying laser firing conditions. Delineation of the geometry and penetration depth of an LFC, within the silicon, was possible with this method, and the oncemolten, laser fired region was measured to depths of tens of microns in the silicon substrate. Investigation of surface topography, diameter, and electrical performance of LFCs was carried out in previous work by Brennan DeCesar, and is briefly reviewed herein. Simulations of LFCs were performed by modeling devices of different diameter and doping densities to replicate trends in experimental resistance data, and to identify the concentration of Al in the fired contact region. Resistances simulated for LFCs modeled with doping densities above 1x10<sup>18</sup>/cm<sup>3</sup> matched best with experimental data, and the resistance of the contacts is dominated by spreading resistance from the heavily doped region (formed through laser firing) into the rest of the wafer.

Laser doped emitters were also fabricated and characterized through electrical characterization and cross-sectioning and junction delineation techniques. Doping of the emitters using phosphorus-doped amorphous silicon films, incorporated in the passivation layers, was found to be promising. Depths of LDEs within the silicon were much shallower than those of LFCs, due to the shorter pulse duration used in laser processing (µs rather than ms).

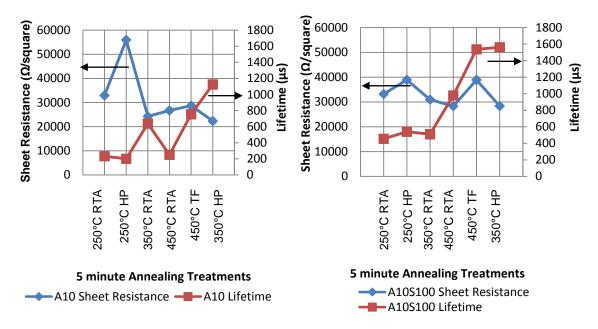

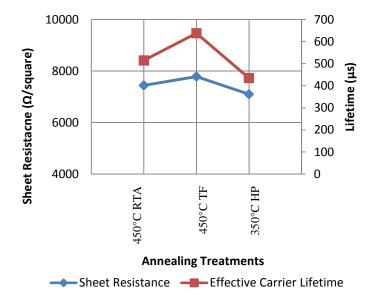

Passivation of silicon through the introduction of negative fixed charge was investigated using alumina (Al<sub>2</sub>O<sub>3</sub>) and hafnia (HfO<sub>2</sub>) films deposited by atomic layer deposition (ALD). Layered structures with SiO<sub>x</sub> capping films deposited by plasma enhanced chemical vapor deposition (PECVD) were also investigated. Passivation quality was characterized by measuring effective carrier lifetime using microwave photoconductive decay. The longest lifetimes achieved were over 1.5 ms, measured on a sample passivated with 10 nm Al<sub>2</sub>O<sub>3</sub> and 100 nm SiO<sub>x</sub> after a 5 min 350°C anneal. Fixed charge density was calculated through flat band voltage shifts in C-V measurements made using a mercury probe. Both the Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> samples exhibited negative fixed charge densities. Samples passivated with thin Al<sub>2</sub>O<sub>3</sub> layers were found to have the largest negative fixed charge densities, up to 1x10<sup>13</sup>/cm<sup>2</sup>. Additionally, the creation of an inversion layer due to fixed charge in passivation films deposited on high resistivity silicon substrates was investigated using contactless conductivity measurements and changes in sheet resistance. The presence of an inversion layer was detected by a decrease in sheet resistance and correlated to an increase in effective carrier lifetime for those samples annealed for 5 min at 450°C in a tube furnace, 450°C in a RTA, and 350°C on a hot plate.

# **TABLE OF CONTENTS**

| List of Figures                                      | vii |

|------------------------------------------------------|-----|

| List of Tables                                       | xi  |

| Glossary of Terms                                    | xii |

| Acknowledgements                                     | XV  |

| Chapter 1 Introduction                               | 1   |

| Device Components                                    | 1   |

| Selective Emitters                                   | 3   |

| Rear-Side Contacts                                   | 5   |

| Surface Passivation                                  | 6   |

| Solar Cell Design Improvements and Modern Structures | 8   |

| Solar Cell Structure and Laser Firing                |     |

| Motivation                                           |     |

| Experiments and Goals                                |     |

| Chapter 2 Laser Fired Contacts                       | 16  |

| Literature Review                                    |     |

| LFC Simulation and Cross-sectioning Goals            |     |

| Cross-sectioning and Junction Delineation            |     |

| Sample Fabrication                                   |     |

| Processing Procedures                                |     |

| Results and Discussion                               |     |

| LFC Simulation                                       |     |

| Device Modeling and Simulation                       |     |

| Simulation Results                                   | 27  |

| Chapter 3 Laser Doped Emitters                       | 30  |

| Literature Review                                    | 30  |

| LDE Experiments                                      |     |

| Background                                           |     |

| Characterization                                     |     |

| I-V Measurements                                     |     |

| Antimony Doped Samples                               |     |

| Phosphorus Doped Samples                             |     |

| Curve Comparison                                     |     |

| Metallization                                        |     |

| Cross-sectioning and Junction Delineation            |     |

| Results and Discussion                               | 79  |

| Chapter 4 Passivation                                                                                                              | 83  |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Literature Review                                                                                                                  | 83  |

| Passivation Experiments                                                                                                            | 88  |

| Film Thickness Experiment: Al <sub>2</sub> O <sub>3</sub> and HfO <sub>2</sub> Layers                                              | 90  |

| Lifetime Measurements                                                                                                              |     |

| C-V Measurements                                                                                                                   | 95  |

| Results and Discussion                                                                                                             | 103 |

| Multi-Layer Passivation Experiment: Al <sub>2</sub> O <sub>3</sub> /SiO <sub>x</sub> and HfO <sub>2</sub> /SiO <sub>x</sub> Layers | 104 |

| Lifetime Measurements                                                                                                              |     |

| C-V Measurements                                                                                                                   | 107 |

| Results and Discussion                                                                                                             | 108 |

| Inversion Layer Experiment: Al <sub>2</sub> O <sub>3</sub> and Al <sub>2</sub> O <sub>3</sub> /SiO <sub>x</sub> Layers             | 110 |

| Lifetime Measurements                                                                                                              |     |

| C-V Measurements                                                                                                                   | 115 |

| Sheet Resistance Results                                                                                                           | 123 |

| Results and Discussion                                                                                                             | 127 |

| Chapter 5 Conclusions and Future Work                                                                                              | 130 |

| Conclusions                                                                                                                        | 130 |

| Future Work                                                                                                                        | 133 |

| Bibliography                                                                                                                       | 135 |

| Appendix A                                                                                                                         | 142 |

| Effective Carrier Lifetime Measurements                                                                                            | 142 |

| Appendix B                                                                                                                         | 153 |

| C-V Measurements on n-Type Wafers                                                                                                  | 153 |

| Appendix C                                                                                                                         | 157 |

| C-V Measurements from the Inversion Layer Experiment                                                                               | 157 |

# LIST OF FIGURES

| Figure 1-1: Schematic of a standard solar cell adapted from (2).                                                                                                                                             | 2  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2: Passivated emitter and rear locally diffused cell (PERL) adapted from (2)                                                                                                                        | 9  |

| Figure 1-3: Front surface field, interdigitated back contact, back junction cell (FSF-IBC) adapted from (2)                                                                                                  | 10 |

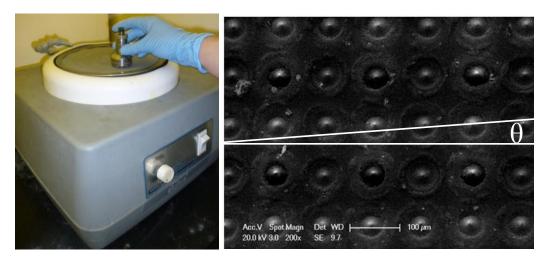

| Figure 2-1: Dense array and sample preparation for polishing                                                                                                                                                 | 21 |

| Figure 2-2: Polishing wheel and angle at which the sample is polished                                                                                                                                        | 21 |

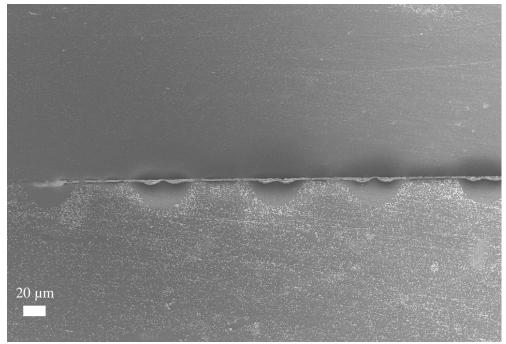

| Figure 2-3: Successful cross-section of a row of LFCs and junction delineation between the p-type melt regions and the n-type substrate, sample passivated with a-Si:H/SiO <sub>x</sub>                      | 23 |

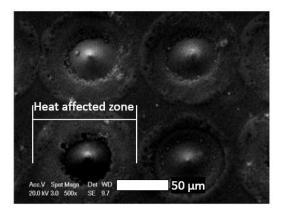

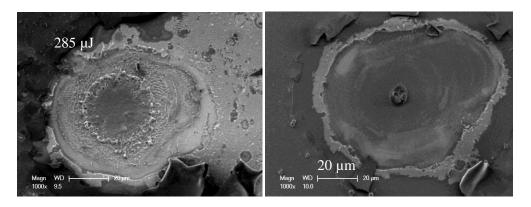

| Figure 2-4: Sample fired at 45 W and 4 ms showing typical morphology of LFCs fired with the IPG 1070 nm single mode fiber laser                                                                              | 25 |

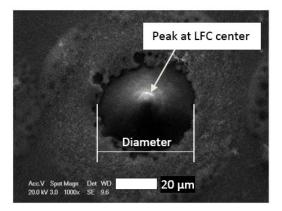

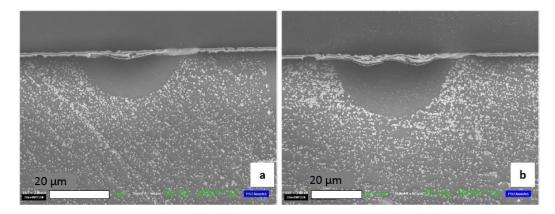

| Figure 2-5: Cross-sections after junction delineation of an LFC (a) fired at 22 W and 19 ms, passivated with a-Si:H, and an LFC in image (b) fired at 45 W and 4 ms, passivated with a-Si:H/SiO <sub>x</sub> | 25 |

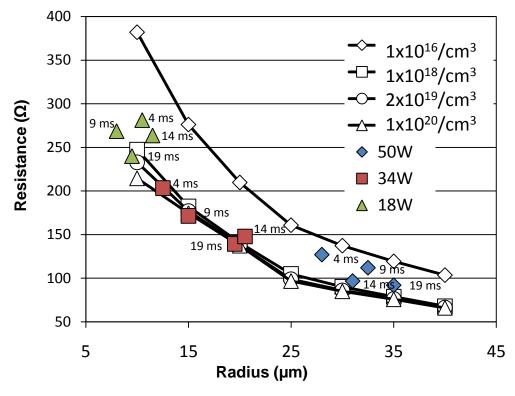

| Figure 2-6: Simulated resistance values and experimental resistance values for LFCs                                                                                                                          | 28 |

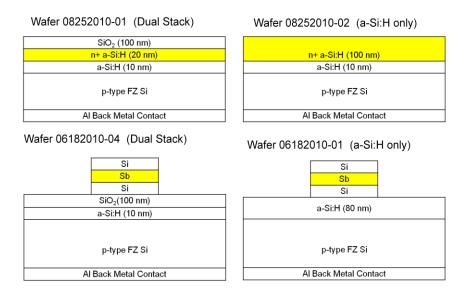

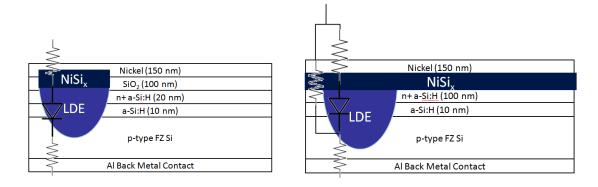

| Figure 3-1: Passivation and dopant structures.                                                                                                                                                               | 38 |

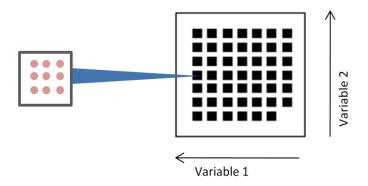

| Figure 3-2: Image of a LDE array sample.                                                                                                                                                                     | 39 |

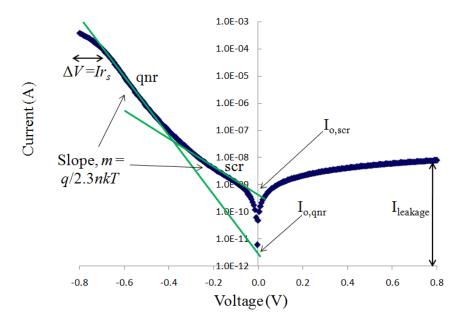

| Figure 3-3: I-V curve for a diode with series resistance, schematic after (50).                                                                                                                              | 42 |

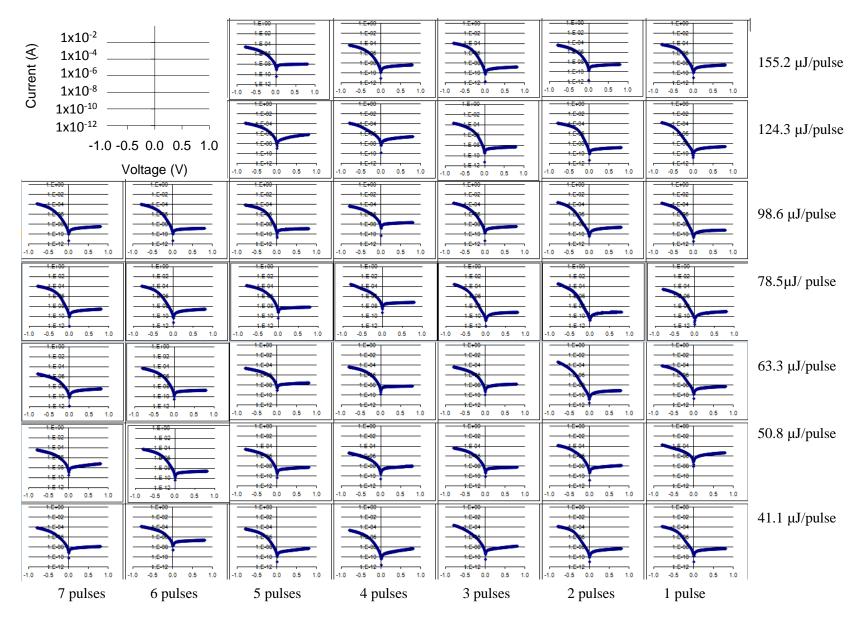

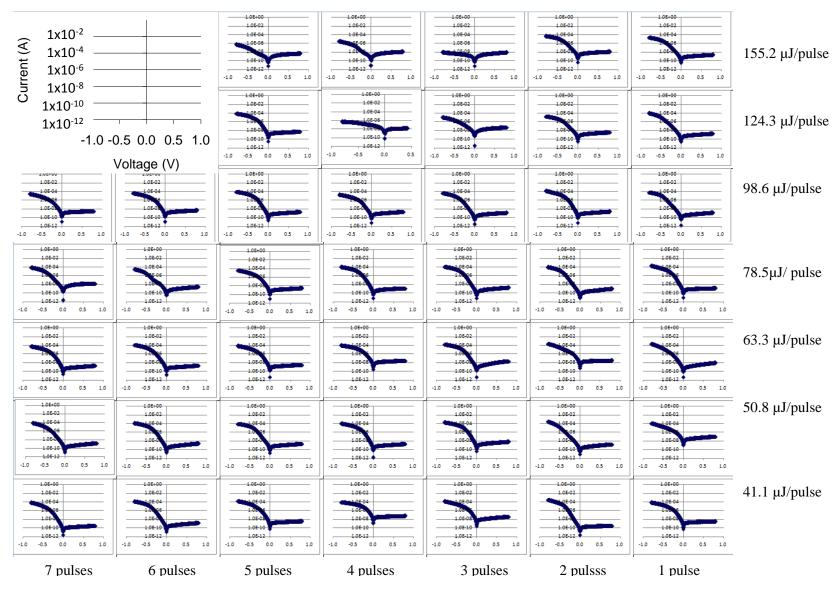

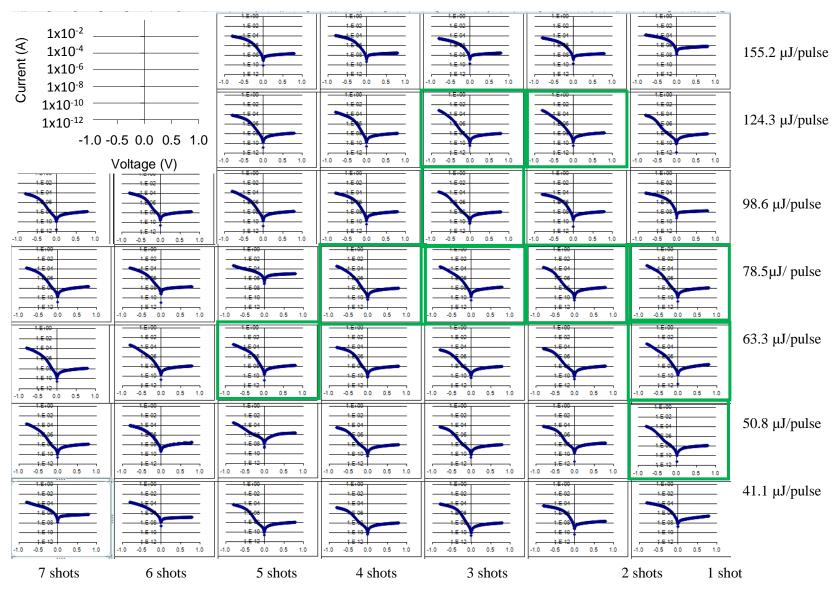

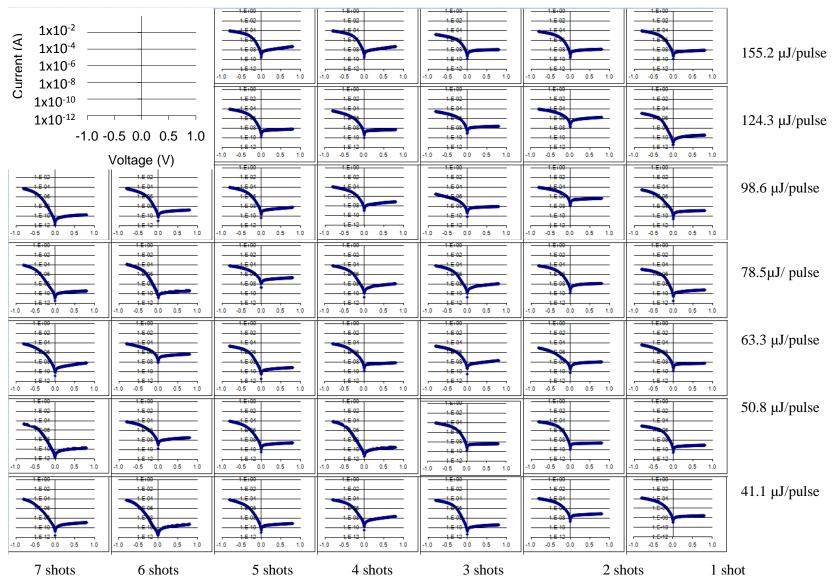

| Figure 3-4: I-V curves for LDEs on a-Si:H passivated Sb sample, 355 nm laser                                                                                                                                 | 45 |

| Figure 3-5: I-V curves for LDEs on a-Si:H/SiO <sub>x</sub> passivated Sb sample, 355 nm laser                                                                                                                | 46 |

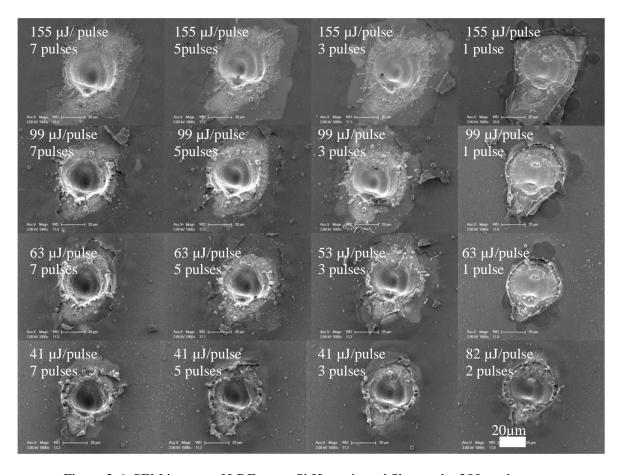

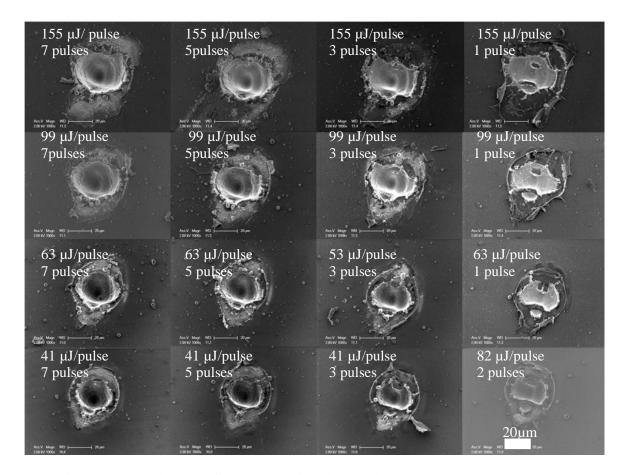

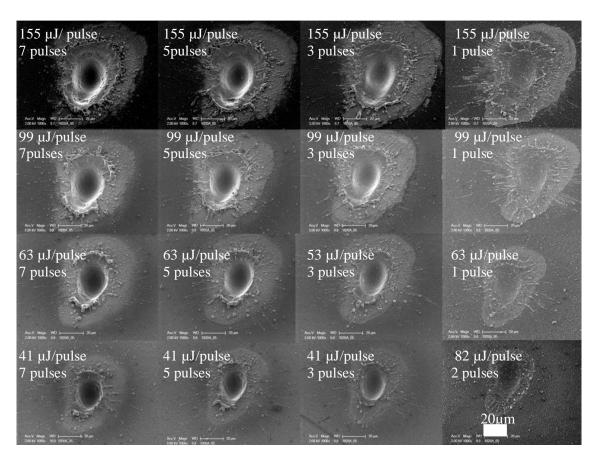

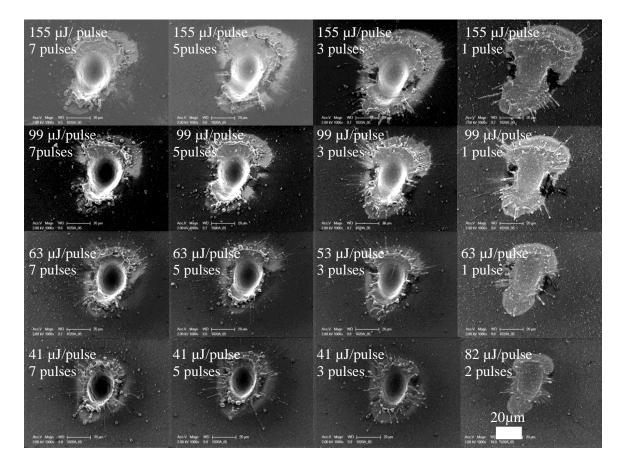

| Figure 3-6: SEM images of LDEs on a-Si:H passivated Sb sample, 355 nm laser                                                                                                                                  | 47 |

| Figure 3-7: SEM images of LDEs on a-Si:H/SiO <sub>x</sub> passivated Sb sample, 355 nm laser                                                                                                                 | 48 |

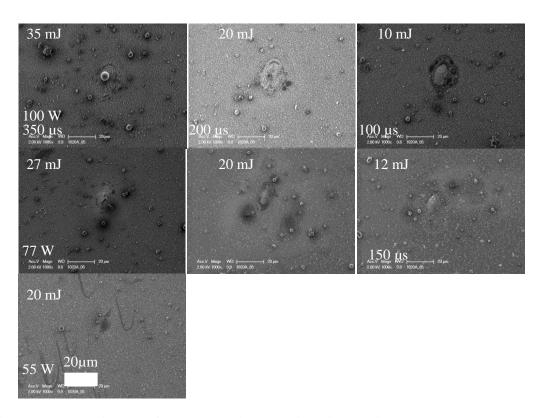

| Figure 3-8: SEM images of LDEs on a-Si:H passivated Sb sample, 1070 nm laser. The 20 nm scale marker applies to all micrographs not otherwise labeled                                                        | 49 |

| Figure 3-9: SEM images of LDEs on a-Si:H/SiO <sub>x</sub> passivated Sb sample, 1070 nm laser.  The 20 nm scale marker applies to all micrographs not otherwise labeled                                      | 49 |

| Figure 3-10: SEM images of processed spots on Sb doped (left) a-Si:H passivated sample and (right) a-Si:H/SiO <sub>x</sub> passivated sample, 1064 nm laser                                                  | 51 |

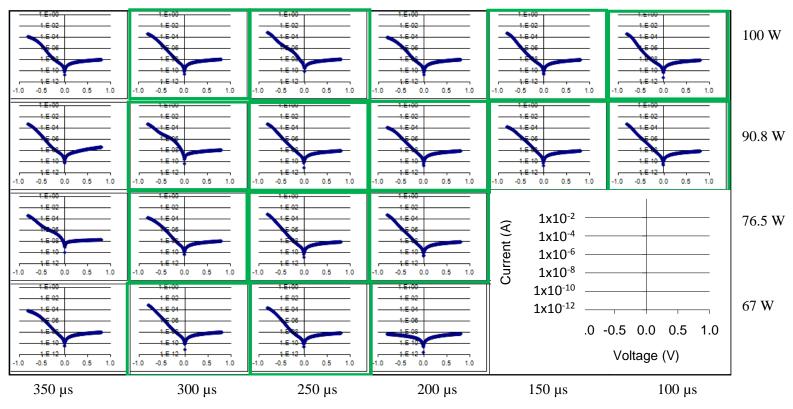

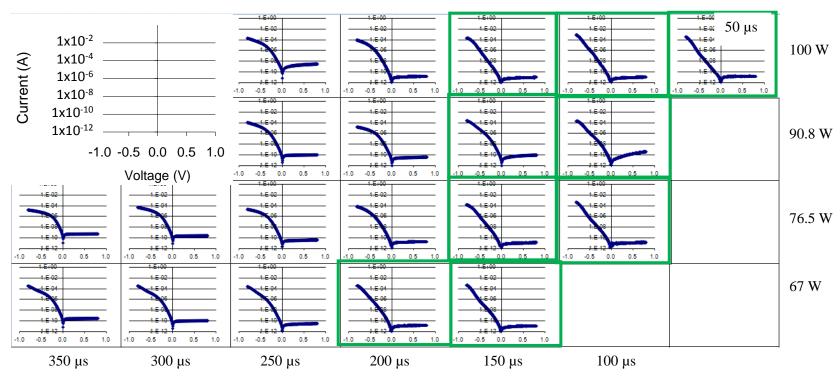

| Figure 3-11: I-V curves for LDEs on a-Si:H/n+ a-Si:H passivated sample, 355 nm laser5                           | 3 |

|-----------------------------------------------------------------------------------------------------------------|---|

| Figure 3-12: SEM images of LDEs on a-Si:H/n+a-Si:H passivated sample, 355 nm laser5                             | 4 |

| Figure 3-13: I-V curves for LDEs on a-Si:H/SiO <sub>x</sub> passivated sample, 355 nm laser5                    | 6 |

| Figure 3-14: SEM images of LDEs on a-Si:H/n+a-Si:H/SiO <sub>x</sub> passivated sample, 355 nm laser             | 7 |

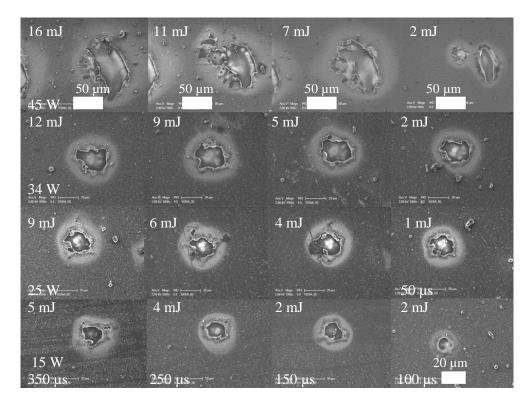

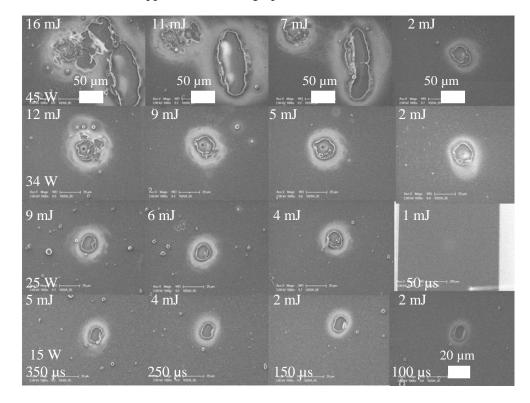

| Figure 3-15: I-V curves for LDEs on a-Si:H/n+a-Si:H passivated sample, 1070 nm laser5                           | 9 |

| Figure 3-16: SEM images of LDEs on a-Si:H/n+a-Si:H passivated sample, 1070 nm laser                             | 0 |

| Figure 3-17: I-V curves for LDEs on a-Si:H/n+a-Si:H/SiO <sub>x</sub> passivated sample, 1070 nm laser           | 2 |

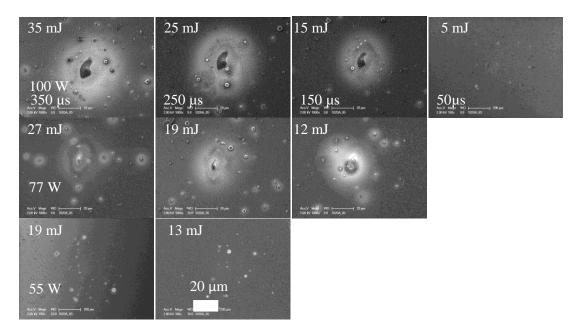

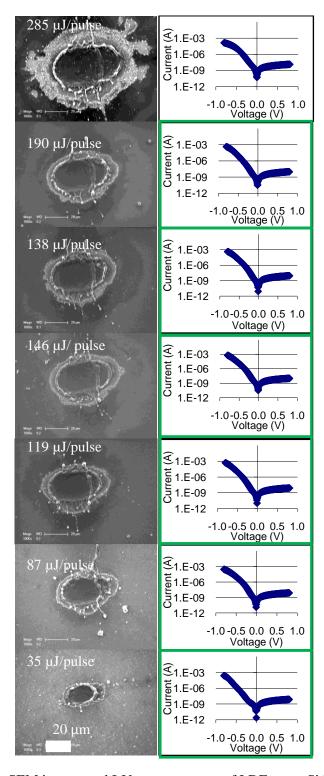

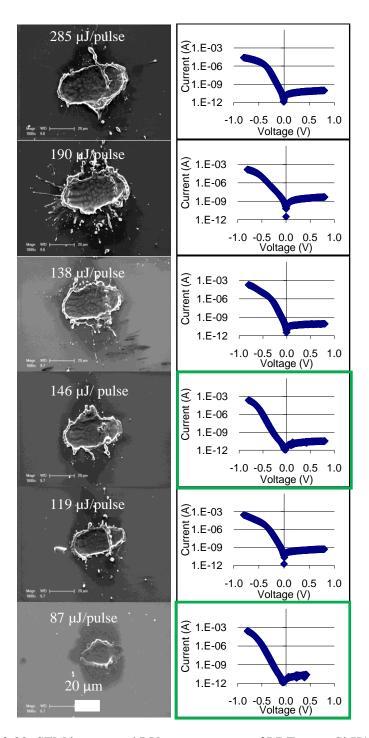

| Figure 3-18: SEM images of LDEs on a-Si:H/n+a-Si:H/SiO <sub>x</sub> passivated sample, 1070 nm laser            | 3 |

| Figure 3-19: SEM images and I-V measurements of LDEs on a-Si:H/n+ a-Si:H sample,  1064 nm laser6                | 5 |

| Figure 3-20: SEM images and I-V measurements of LDEs on a-Si:H/n+ a-Si:H/SiO <sub>x</sub> sample, 1064 nm laser | 7 |

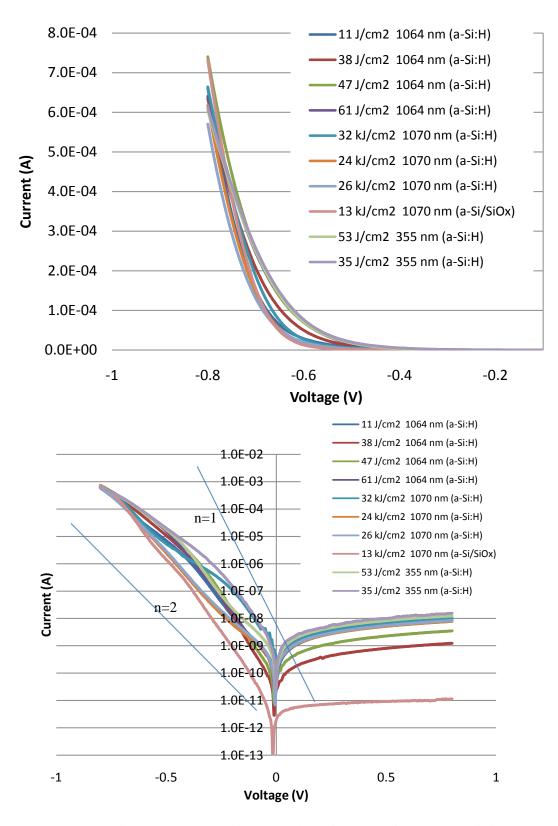

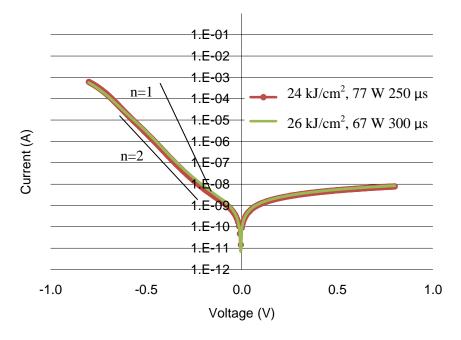

| Figure 3-21: I-V and log(I)-V plots of the best diode characteristics                                           | 0 |

| Figure 3-22: Curves for similar LDEs                                                                            | 2 |

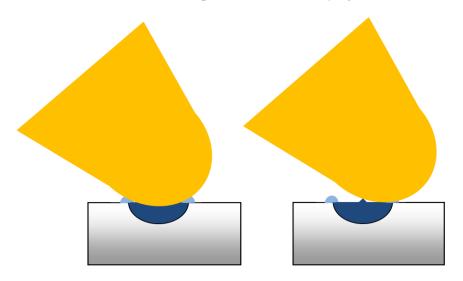

| Figure 3-23: Possible locations of probe tip contacting the LDE when taking I-V measurements                    | 4 |

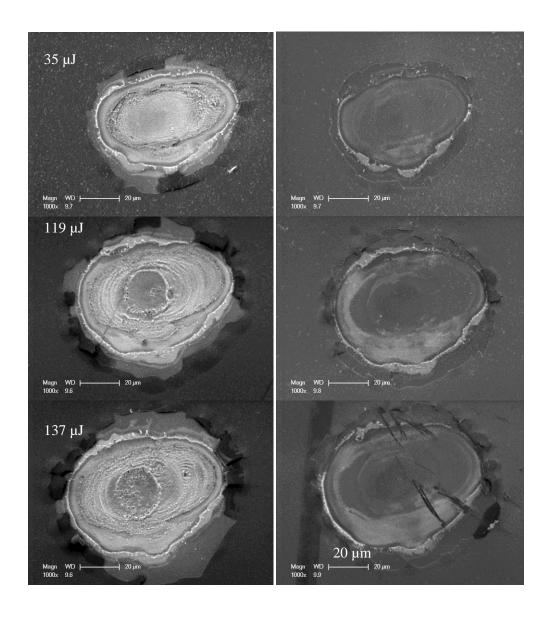

| Figure 3-24: Importance of a SiO <sub>x</sub> barrier layer for selective metallization of LDEs                 | 4 |

| Figure 3-25: Tensile stresses evidenced in Ni films by peeling                                                  | 6 |

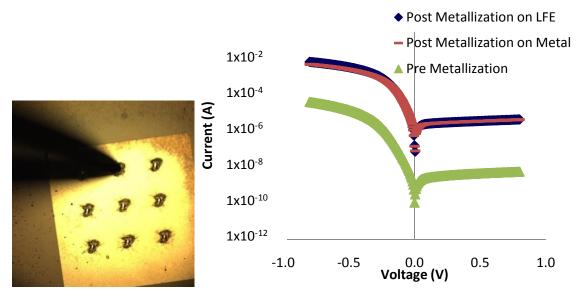

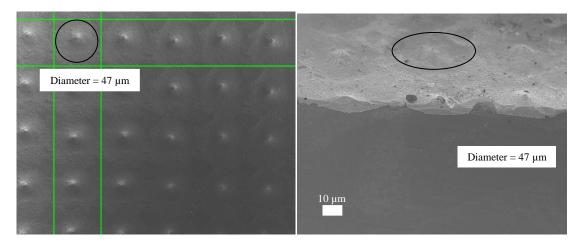

| Figure 3-26: Pre and post metallization I-V measurements on a pad fired with the 355 nm laser (155 μJ)          | 7 |

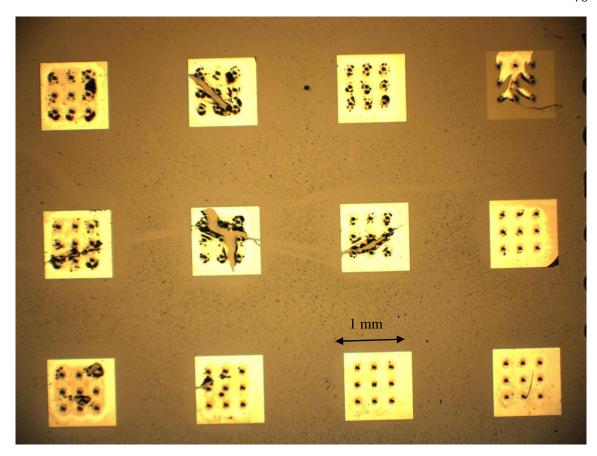

| Figure 3-27: Dense array of LDEs fired at 100W and 100 µs on a-Si:H/n+ a-Si:H sample using a 1070 nm laser      | 8 |

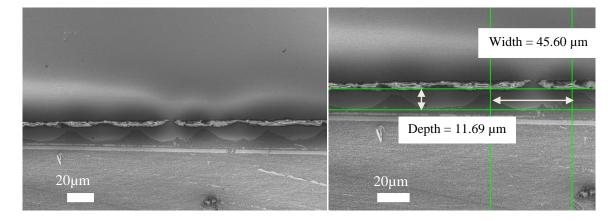

| Figure 3-28: Cross-section of LDEs processed with a 1070 nm laser at 100 W and 100 μs7                          | 8 |

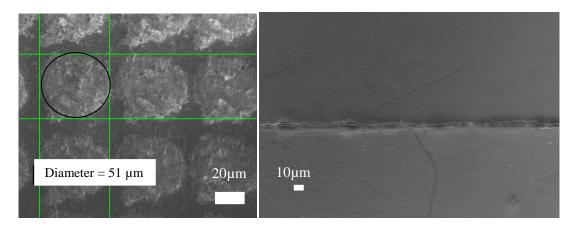

| Figure 3-29: Cross-sectioned LDE sample fired with 1 pulse at 124.3 µJ/pulse with the 355 nm laser              | 9 |

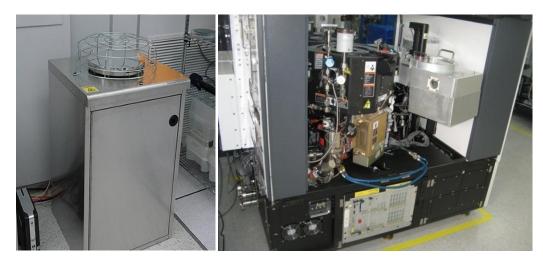

| Figure 4-1: Cambridge Savannah <sup>TM</sup> 200 ALD system and the AMAT P-5000 cluster tool8                   | 9 |

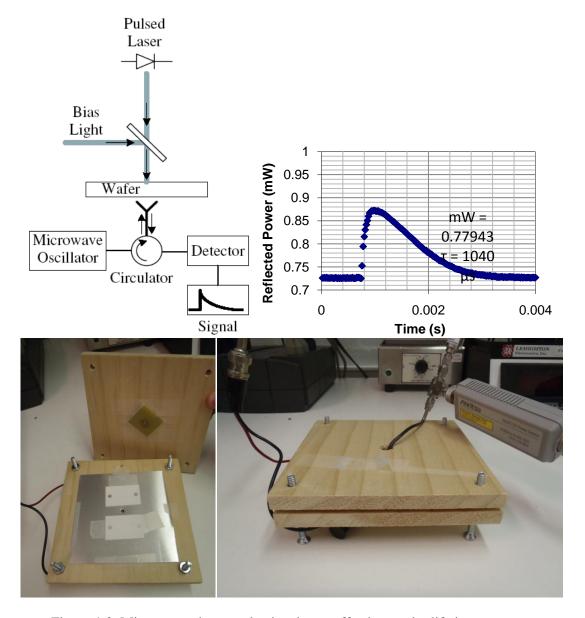

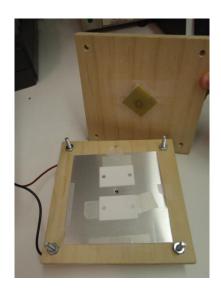

| Figure 4-2: Barnstead Thermolyne hot plate and Temptronic ThermoChuck vacuum chuck.                                                                       | 91  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

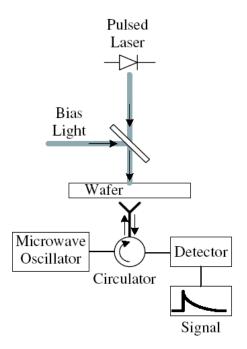

| Figure 4-3: Microwave photoconductive decay, effective carrier lifetime measurement set up (50)                                                           | 93  |

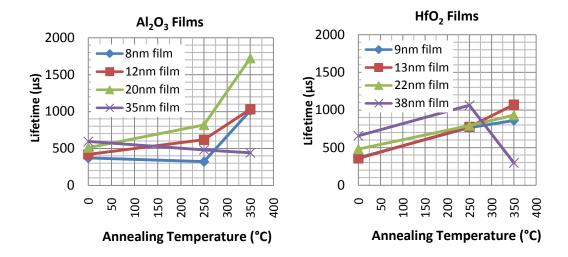

| Figure 4-4: Effective carrier lifetime and annealing temperature.                                                                                         | 95  |

| Figure 4-5: Agilent4284A LCR meter Leighton 2017B mercury probe                                                                                           | 95  |

| Figure 4-6: Shift in V <sub>FB</sub> due to the metal-semiconductor work function difference and fixed charge in the film.                                | 96  |

| Figure 4-7: C-V measurement hysteresis.                                                                                                                   | 98  |

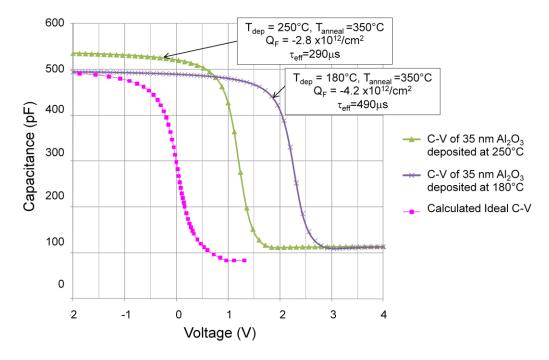

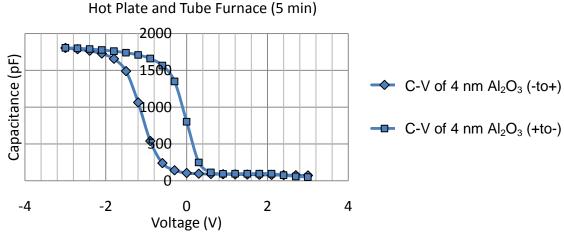

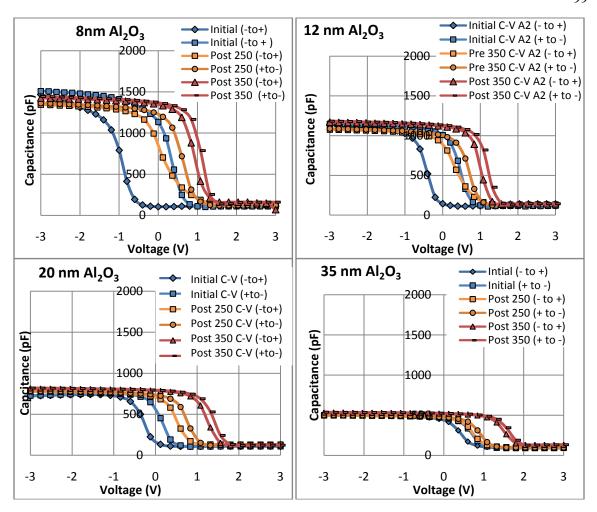

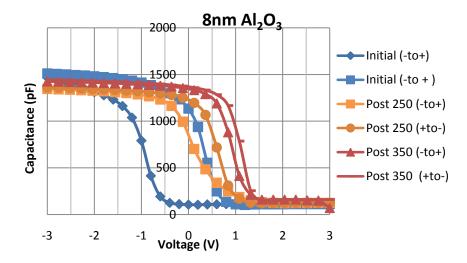

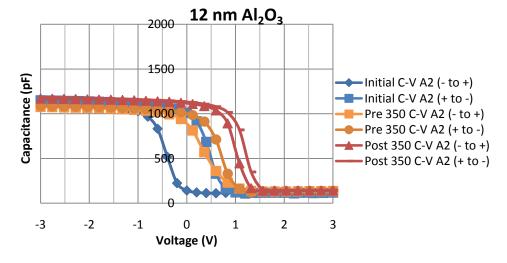

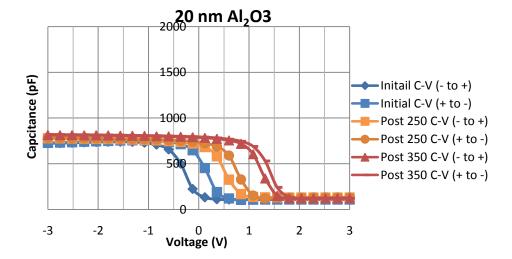

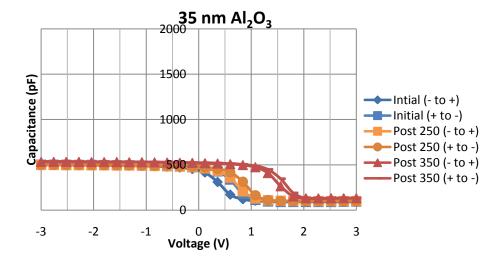

| Figure 4-8: C-V curves for the Al <sub>2</sub> O <sub>3</sub> passivated samples.                                                                         | 99  |

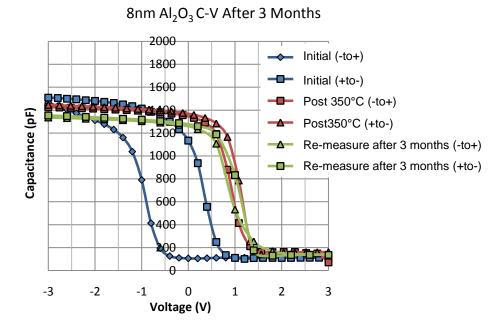

| Figure 4-9: C-V curves of the 8 nm Al <sub>2</sub> O <sub>3</sub> passivated sample after the 350°C anneal and three months later.                        | 101 |

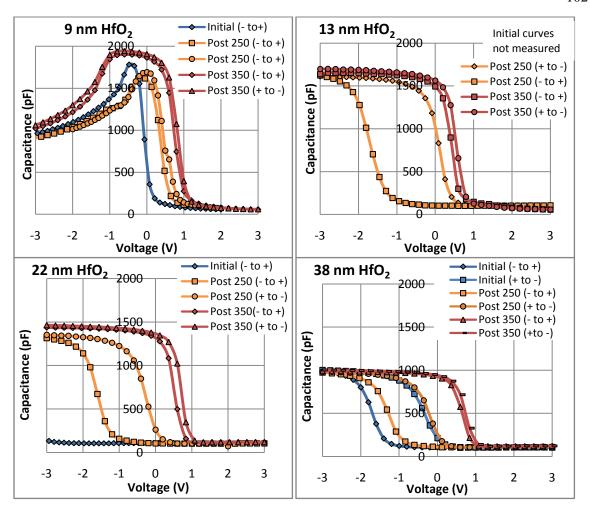

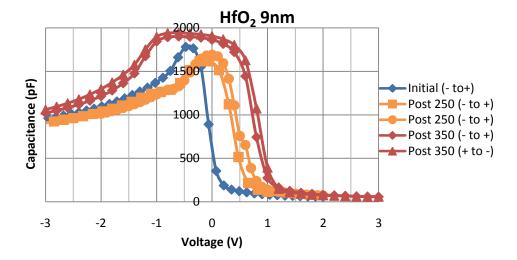

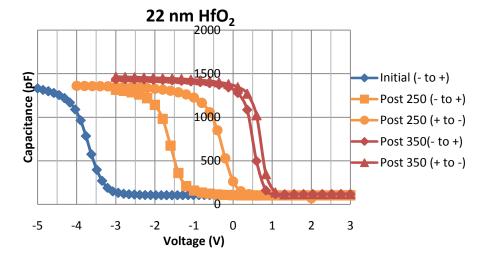

| Figure 4-10: C-V curves for the HfO <sub>2</sub> passivated samples.                                                                                      | 102 |

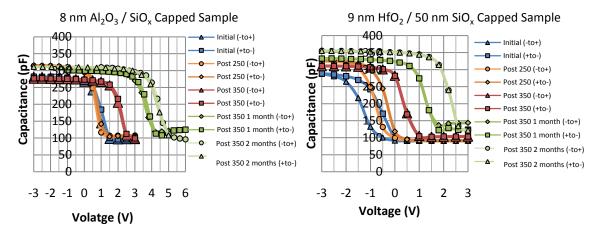

| Figure 4-11: C-V curves for 8 nm Al <sub>2</sub> O <sub>3</sub> and 9 nm HfO <sub>2</sub> samples capped with 50 nm SiO <sub>x</sub> .                    | 106 |

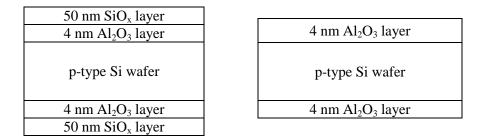

| Figure 4-12: Cross sectional diagram of the passivation layer stack up.                                                                                   | 106 |

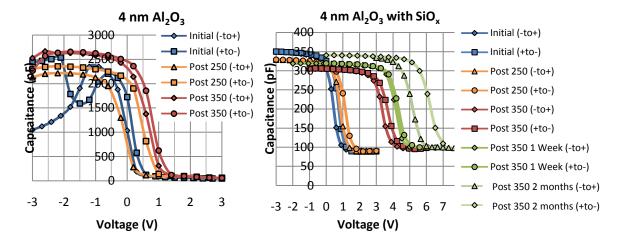

| Figure 4-13: C-V measurements for 4 nm Al <sub>2</sub> O <sub>3</sub> and 4 nm Al <sub>2</sub> O <sub>3</sub> /50 nm SiO <sub>x</sub> passivated samples. | 108 |

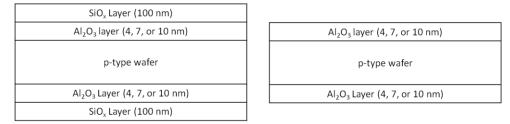

| Figure 4-14: Passivation layers on different substrates for lifetime and C-V measurements and sheet resistance measurements.                              | 110 |

| Figure 4-15: Stack passivation layer sample                                                                                                               | 111 |

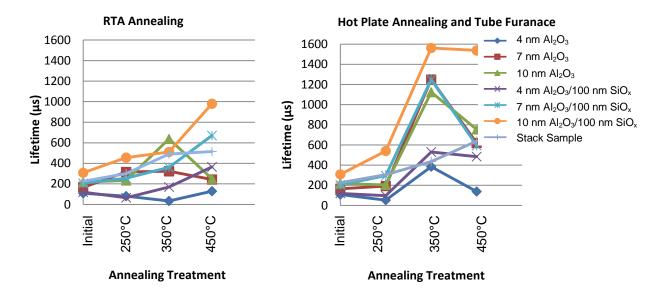

| Figure 4-16: Effective carrier lifetime vs. annealing treatment: (a) RTA annealing (b) hot plate annealing.                                               | 114 |

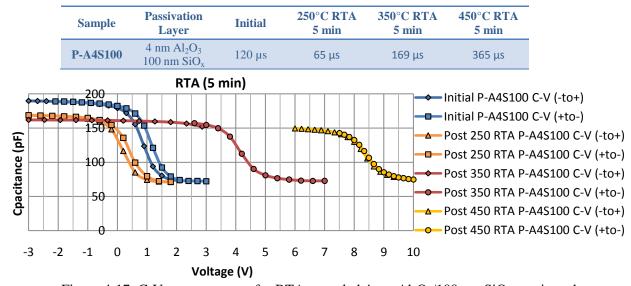

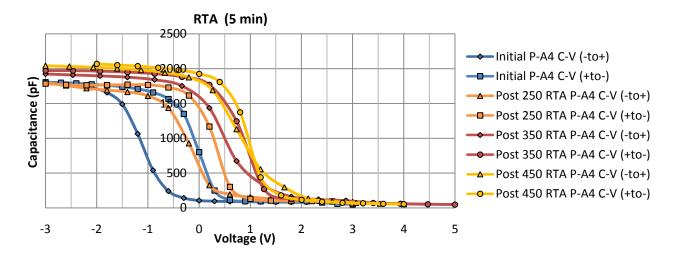

| Figure 4-17: C-V measurements for RTA annealed 4 nm Al <sub>2</sub> O <sub>3</sub> /100 nm SiO <sub>x</sub> passivated samples.                           | 116 |

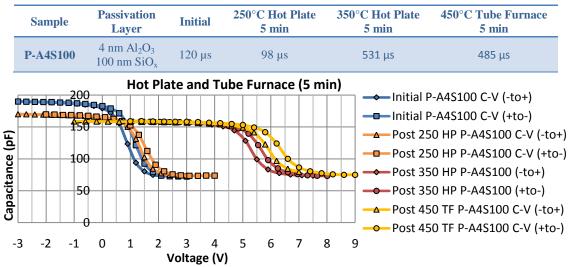

| Figure 4-18: C-V measurements for the HP and TF annealed 4 nm $Al_2O_3/100$ nm $SiO_x$ samples.                                                           | 117 |

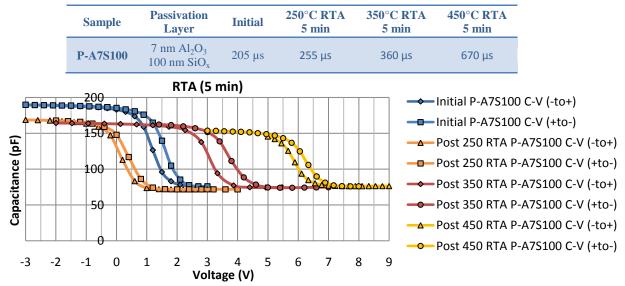

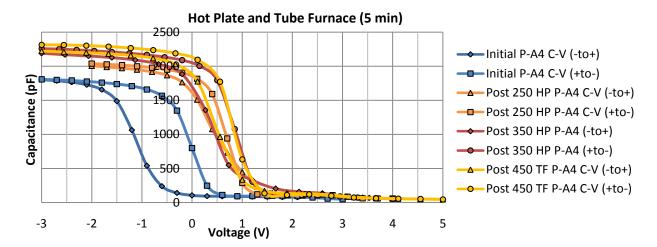

| Figure 4-19: C-V measurements of the RTA annealed 7 nm $Al_2O_3/100$ nm $SiO_x$ samples                                                                   | 118 |

| Figure 4-20: C-V measurements for HP and TF annealed 7 nm $Al_2O_3/100$ nm $SiO_x$ samples.                                                               | 119 |

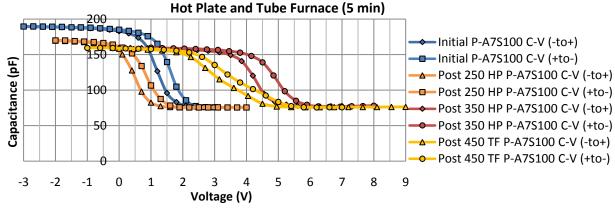

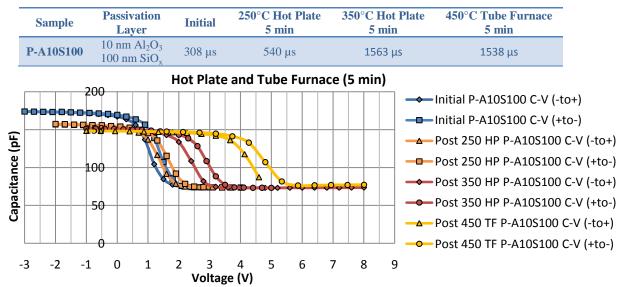

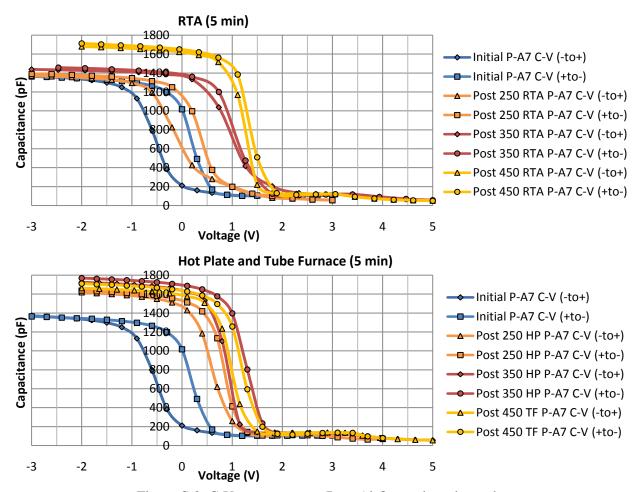

| Figure 4-21: C-V measurements for RTA annealed 10 nm Al <sub>2</sub> O <sub>3</sub> /100 nm SiO <sub>x</sub> samples                                      | 119 |

| Figure 4-22: C-V measurement for HP and TF annealed 10 nm Al <sub>2</sub> O <sub>3</sub> /100 nm SiO <sub>x</sub> samples                                                                                                              | 120  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

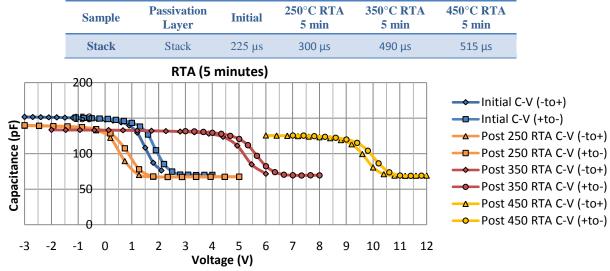

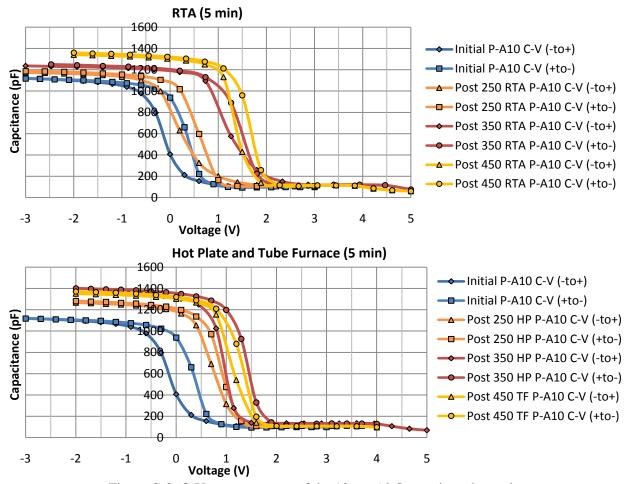

| Figure 4-23: C-V measurements for RTA annealed 4 nm Al <sub>2</sub> O <sub>3</sub> /4 nm SiO <sub>x</sub> /7 nm Al <sub>2</sub> O <sub>3</sub> /50 nm SiO <sub>x</sub> samples                                                         | 121  |

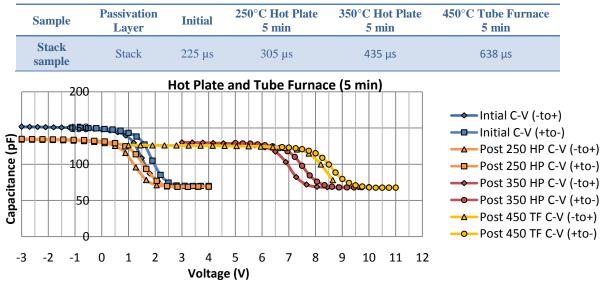

| Figure 4-24: C-V measurements for HP and TF annealed 4 nm Al <sub>2</sub> O <sub>3</sub> /4 nm SiO <sub>x</sub> /7 nm Al <sub>2</sub> O <sub>3</sub> /50 nm SiO <sub>x</sub> samples                                                   | 122  |

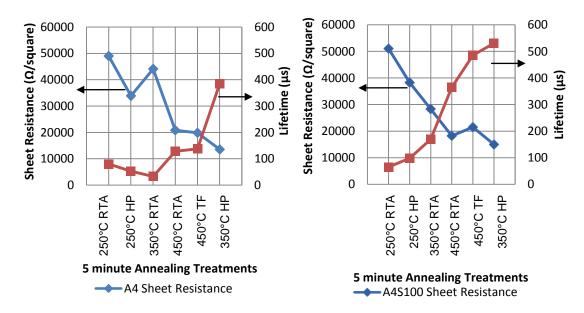

| Figure 4-25: Sheet resistance and effective carrier lifetime vs. annealing treatments for 4 nm Al <sub>2</sub> O <sub>3</sub> passivated sample and 4 nm Al <sub>2</sub> O <sub>3</sub> / 100 nm SiO <sub>x</sub> passivated samples   | 124  |

| Figure 4-26: Sheet resistance and effective carrier lifetime vs. annealing treatments for 7 nm Al <sub>2</sub> O <sub>3</sub> passivated sample and 7 nm Al <sub>2</sub> O <sub>3</sub> / 100 nm SiO <sub>x</sub> passivated samples   | 125  |

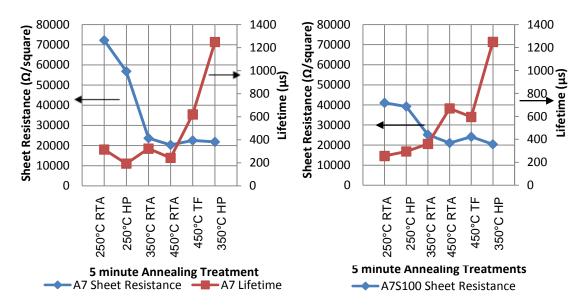

| Figure 4-27: Sheet resistance and effective carrier lifetime vs. annealing treatments for 10 nm Al <sub>2</sub> O <sub>3</sub> passivated sample and 10 nm Al <sub>2</sub> O <sub>3</sub> / 100 nm SiO <sub>x</sub> passivated samples | 126  |

| Figure 4-28: Sheet resistance and effective carrier lifetime vs. annealing treatments for samples passivated with the stack structure.                                                                                                 | 127  |

| Figure B-1: C-V measurements of the 8 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                              | 153  |

| Figure B-2: C-V measurements of the 12 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                             | 153  |

| Figure B-3: C-V measurements of the 20 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                             | 154  |

| Figure B-4: C-V measurements of the 35 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                             | 154  |

| Figure B-5: C-V measurements of the 9 nm HfO <sub>2</sub> passivated sample                                                                                                                                                            | 155  |

| Figure B-6: C-V measurements of the 13 nm HfO <sub>2</sub> passivated sample                                                                                                                                                           | 155  |

| Figure B-7: C-V measurements of the 22 nm HfO <sub>2</sub> passivated sample                                                                                                                                                           | 156  |

| Figure C-1: C-V measurements of the 4 nm Al <sub>2</sub> O <sub>3</sub> passivated samples                                                                                                                                             | 158  |

| Figure C-2: C-V measurements 7 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                                     | 159  |

| Figure C-3: C-V measurements of the 10 nm Al <sub>2</sub> O <sub>3</sub> passivated sample                                                                                                                                             | .160 |

# LIST OF TABLES

| Table 2-1: Dimensions of cross-sectioned profiles within the substrate                                |

|-------------------------------------------------------------------------------------------------------|

| Table 3-1: Sample processing conditions                                                               |

| Table 3-2: LDE parameters plotted in Figure 3-2169                                                    |

| Table 4-1: Al <sub>2</sub> O <sub>3</sub> deposition details90                                        |

| Table 4-2: HfO <sub>2</sub> deposition details90                                                      |

| Table 4-3: Effective carrier lifetime for Al <sub>2</sub> O <sub>3</sub> passivated samples94         |

| Table 4-4: Effective carrier lifetime for HfO <sub>2</sub> passivated samples                         |

| Table 4-5: Fixed charge density in Al <sub>2</sub> O <sub>3</sub> passivation films                   |

| Table 4-6: Fixed charge density in HfO <sub>2</sub> passivation films                                 |

| Table 4-7: Lifetime of thin film ALD samples capped with SiO <sub>x</sub>                             |

| Table 4-8: Lifetime of the 4 nm $Al_2O_3$ and 4 nm $Al_2O_3/50$ nm $SiO_x$ passivated samples 107     |

| Table 4-9: Fixed charge density values for the SiO <sub>x</sub> capped samples                        |

| Table 4-10: Annealing conditions studied                                                              |

| Table 4-11: Effective carrier lifetime measurements for samples across different annealing treatments |

| Table 4-12: Maximum fixed charge densities                                                            |

#### **GLOSSARY OF TERMS**

AC – alternating current

Al(CH<sub>3</sub>)<sub>3</sub> – trimethylaluminum, precursor for alumina ALD growth

Al<sub>2</sub>O<sub>3</sub> – aluminum oxide or alumina

ALD – atomic layer deposition

ARC – anti-reflection coating, for reduced reflection at a solar cell's surface

a-Si:H – amorphous silicon, hydrogenated

$a-Si_{1-x}C_x$  – amorphous silicon carbide

a-SiC<sub>x</sub> – amorphous silicon carbide

a-SiN<sub>x</sub>:H-amorphous silicon nitride, hydrogenated

BOE - buffered oxide etch, consisting of hydrofluoric acid and ammonium fluoride and DI water

BSF – back surface field created at the rear side of a cell due to Al metallization

$C_{ox}$  – capacitance of an oxide

C-V measurement – capacitance-voltage measurement

CVD – chemical vapor deposition

CZ – Czochralski, silicon growth technique

DI water – de-ionized water

e-beam deposition – electron-beam deposition

EBIC – electron beam induced current

FESEM – field emission scanning electron microscopy

FF - fill factor

FSF-IBC – front surface field interdigitated back contact back junction cell

FZ – float zone, silicon growth technique

H<sub>2</sub> – hydrogen gas

H<sub>2</sub>O - water

HfO<sub>2</sub> –hafnium oxide or hafnia

HIT cell – Sanyo's high efficiency cell, the "heterojunction with intrinsic thin layer" device

HP – hot plate, used for annealing

$I_{\rm o}$  – saturation current, a measure of recombination in the scr

I-V measurement – current-voltage measurement

$J_{sc}$  - short circuit current

LBIC – light beam induced current measurement

LCP – laser chemical processing

LCR meter – impedance, capacitance, resistance meter

LDEs – laser doped emitters

LFCs – laser fired contacts

LGBC – laser grooved buried contacts

LIMPID – laser induced melting of a pre-deposited impurity doping

L-SNMS – laser secondary neutral mass spectroscopy

m – slope of the qnr and scr regions on a log(I)-V plot

n+ a-Si:H – phosphorus doped a-Si:H

$N_2$  – nitrogen gas

N<sub>2</sub>O – nitrous oxide gas

Nd:YAG laser – neodymium-doped yttrium aluminium garnet laser

Nd:YVO<sub>4</sub> laser – neodymium-doped yttrium orthovanadate laser

PECVD – plasma enhanced chemical vapor deposition

PERC – passivated emitter and rear cell

PERL – passivated emitter and rear locally diffused cell

PERT – passivated emitter rear totally diffused cell

PH<sub>3</sub> – phosphine gas

$Q_f$  – fixed charge density

qnr – quasi neutral region, the p and n-type regions of a diode, away from the junction

$r_{\rm s}$  – series resistance

RTA – rapid thermal anneal or annealing furnace

scr – space charge region, the region of band bending in a diode

SEM – scanning electron microscopy

SiH<sub>4</sub> – silane gas

SIMS – secondary ion mass spectroscopy

SiN<sub>x</sub> – silcon nitride deposited by PECVD

SiO<sub>2</sub> – silicon dioxide, thermally grown silicon oxide

SiO<sub>x</sub> – silicon oxide as deposited by PECVD

SOD – spin on dopant

SRV – surface recombination velocity

TCAD - technology computer-aided design

TEM – transmission electron microscopy

TF- tube furnace, used for annealing

UV LED – ultraviolet light emitting diode

V<sub>FB</sub> – flat band voltage, the voltage at the transistion point between accumulation and depletion

V<sub>oc</sub> – open circuit voltage

μ-PCD – microwave photoconductive decay

$\varphi_{\rm MS}$  – metal-semiconductor work function difference

$\eta$  – conversion efficiency

#### **ACKNOWLEDGEMENTS**

First, I would like to thank Dave Carlson, Lian Zhou, and the other scientists of BP Solar for their guidance and support of this research. Second, I would like to acknowledge the students with whom I worked on this research project: Brennan DeCesar, for his initial work with LFCs, and Jillian Woolridge, for her continued work on LDEs. Third, I would like to thank my advisors: Suzanne Mohney, for her guidance and expertise, Joe Flemish, for his guidance in the design of experiments and help in the fab, and Ted Reutzel, for his challenging questions and attention to detail. Fourth, I would like to thank all the students in Suzanne's lab group, for their friendship, insight, and support. Finally, I would like to thank all of my friends and family, for their love and encouragement; most of all my parents and my fiancé Wesley. Hebrews 12:1-3.

# Chapter 1

# Introduction

## **Device Components**

Developed in 1954 by researchers at Bell Telephone, the first solar cell for commercial use was fabricated with an efficiency of 6% (1). The cell was based on a diffused p-n junction, fabricated in silicon, that successfully separated charge carriers generated by the absorption of solar radiation (1) (2). From that structure the basic solar cell design was born. In its simplest form a solar cell is intended to maximize the conversion of incident solar energy into electrical energy (2), and to do so any design requires three necessary components: a semiconducting substrate, a p-n junction, and metal/semiconductor contacts. The band gap in a semiconductor allows for certain wavelengths of electromagnetic radiation to be absorbed; those materials used in solar cells are selected to absorb wavelengths corresponding to the solar spectrum. The substrate comprises the active regions of the solar cell where photon absorption takes place and electron and hole charge carriers are generated (3). A homogeneous or heterogeneous p-n junction, or "charge separation engine", is required so that photogenerated charge carriers can be separated for current collection. Homogeneous junctions are formed in silicon by doping a region of the bulk n-type (p-type) substrate to be p-type (n-type). Heterogeneous junctions are formed by growing or depositing a different semiconductor material of a different dopant type and bandgap on top of silicon (3) (4). The space charge region (SCR) that forms in the p-n junction serves to separate electrons and holes absorbed in the bulk of the material, making them available for collection (3) (4). The metal/semiconductor contacts of the cell serve to collect the separated photogenerated carriers from the device, and maintain current flow to the external load on the

cell. These three components, or variations of them, will be found in any solar cell structure.

Working together they allow the device to operate.

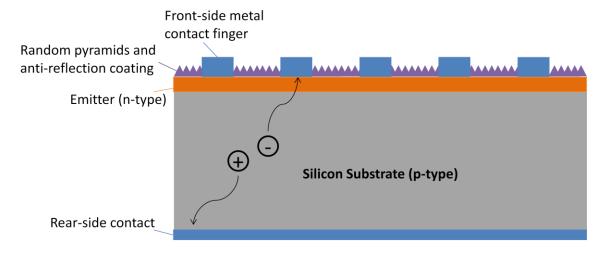

The basic structure of a bulk silicon solar cell is pictured in Figure 1-1. It features a base layer of silicon for light absorption, a rear-side, full area contact for carrier collection, and a front-side emitter region contacted by thin metal finger contacts, to allow incident light into the cell and create a front contact. The front surface the metal grid (as opposed to a full area, blanket metal contact) is necessary to reduce shading and limit optical losses, but it still provides adequate contact area to minimize resistive losses (5). The junction is present on the front surface of the cell in order to more efficiently collect the large number of carriers that are photogenerated where light is first incident on the cell. Surface treatments, such as texturing and the application of an anti-reflection coating, improve light trapping and decrease reflection of impinging radiation. Surface treatments are just one means of engineering to improve device efficiency.

Figure 1-1: Schematic of a standard solar cell adapted from (2).

The cell in Figure 1-1 utilizes a p-type silicon wafer as the base material, and an n-type doped emitter region. Cells can also be manufactured on n-type wafers with p-type doped emitters. The quality of the cell and its performance is dependent upon the doping of the base

layer along with structural and process variables including front contact spacing, minority carrier lifetime, and surface recombination velocities of the front and rear-side contacts and surfaces (2).

Intrinsic performance of a solar cell hinges on material quality. Values inherent to the material such as carrier mobility and carrier lifetime will govern the maximum efficiency that a solar cell can achieve. A perfect single crystal would yield the best performance, but in the interest of cost savings, aspects of cell design are sometimes cleverly engineered and manufactured in order to obtain as much performance as possible out of less expensive, lower quality materials. Innovative engineering will be required to obtain (1) effective charge separation at the emitter (p-n junctions), (2) efficient carrier collection at the contacts, and (3) excellent front and rear surface passivation.

#### **Selective Emitters**

In a solar cell, light is absorbed in the bulk material and electron and hole charge carriers are generated. Separation of those photogenerated charges takes place in the space charge region of a p-n junction, built into the solar cell at the interface of the emitter layer and the bulk substrate. Nomenclature surrounding solar cells typically terms the "emitter" as the layer deposited on the substrate to form the junction, but sometimes refers to emitter characteristics in reference to the performance of the p-n junction (6). In the experimental section, use of the term "emitter" will refer to the doped region on the front side of a cell and the p-n junction thus created. A good quality emitter-base junction essentially acts as a diode, allowing current flow in one direction and separating carriers out of the cell for collection. Emitter junctions need to be rectifying, with little series resistance, low saturation current, and minimal leakage current. To form the front side emitter in a solar cell, a homogenous or heterogeneous p-n junction can be created. A homogeneous junction is formed by heavily doping the front surface of a p-type (n-

type) cell to be n-type (p-type). A heterogeneous junction is formed by depositing a p-type (n-type) layer of another semiconducting material onto an n-type (p-type) substrate material (3) (4). In conventional solar cell designs the emitter region is heavily doped over the entire front surface (7) (8). Doping is performed through high temperature furnace diffusion to drive an n-type dopant, such as phosphorus (p-type dopant, i.e., boron), present in a phosphorus containing environment or a phosphosilicate glass, into the p-type (n-type) substrate material (7) (8). The high temperature drive-in step is necessary for doping to occur, but can have undesirable effects on yield due to wafer warping and fracture that can occur (8). Furnace diffusion results in uniform doping across the entire front surface, with no selectivity between the active regions of the material and the regions to be metallized (7). The heavy doping in the active window region decreases the short wavelength response of the cell and leads to a reduction in cell efficiency (7) (9).

Continued efforts to manufacture high-efficiency cells necessitated a switch to selective emitters, which feature heavily doped contact areas underneath the metallized region and a light doping in the window regions (active regions) between front metal fingers (9) (10). Heavy doping under metal contacts ensures ohmic contact formation and reduced contact resistance, and light doping of the active regions of a cell reduces recombination and improves spectral response (11). Selective emitters are formed through either photolithographic patterning and an "etch back" process, or screen printing and patterning of a dopant paste or metallization paste with the dopant mixed in (10). The heavily doped regions under the metallization have to be carefully patterned for alignment of the metal fingers that are subsequently patterned over the doped region using screen printing, or in high-efficiency cells photolithographic patterning and electron-beam or physical vapor deposition.

#### **Rear-Side Contacts**

Photogenerated majority carriers are collected out of the cell at the rear-side contacts. The contacts need to be low resistance and ohmic to ensure that carriers are collected and to avoid degradation of cell efficiency. Higher resistance contacts hinder the travel of holes (for a p-type cell) through the contact and increase resistive loss. Rear-side contacts can be formed over the full area of the rear or in local areas, depending on the cell structure. Screen printing of the rear side contact is commonly performed due to its low cost (12). Using an aluminum paste, full area contacts are printed and then fired to drive out organics and solvents in the paste. Finally the contact is further annealed to ensure contact of the Al metal with the silicon substrate (7) (12). The aluminum layer aids in the reduction of recombination at the rear surface by generation of a back surface field (BSF), which inhibits the movement of minority carriers to the rear-side surface. The presence of Al, a p-type dopant in Si, generates a p-p+ junction at the rear, from which the localized electric field results (7) (13). While screen printing is inexpensive and repeatable it is undesirable to expose the device to the high temperature firing step required to cure the paste and anneal the contacts. The performance of passivation layers degrades with high temperature firing, and as wafers in production become thinner, the contact printing process and extreme heat treatment required for screen printing can cause wafer warping and breakage (8). In high-efficiency solar cells local rear-side Al contacts are made by photolithographic definition. The contacts must be spaced a certain distance apart in a large array; contact spacing depends on the carrier mobility in the substrate and their diffusion lengths. Contact regions are photolithographically defined and etched through the rear passivation layer, making openings for local metal contact to the active region of the device (12). A blanket layer of aluminum is typically used as the contact metal, deposited through e-beam deposition, thermal evaporation, or sputtering.

#### **Surface Passivation**

Surface passivation is critical to solar cell performance because it is at the surface where photo-generated carriers can be most readily lost through recombination (9) (14) (15). In the bulk, electrons and holes exist for a characteristic time before they recombine; referred to as the bulk lifetime, the value is much longer than the near-surface lifetime of the carriers. At the termination of the crystalline silicon lattice, bulk properties of silicon no longer apply and the order and predictability of the lattice is abruptly truncated, leaving dangling bonds, surface states, and numerous defects, which have a large impact on cell efficiency and device performance due to carrier recombination. A large fraction of the photogenerated carriers are generated in the near-surface region as light impinges on the cell, but when electron and hole pairs are generated in the bulk of the cell they must travel to the device contacts to be collected (9). Once in the vicinity of the contacts at the cell surface the carriers have an increased chance of recombination. Electrons and holes are attracted to defect induced traps and surface states instead of the contacts if surface passivation is not in place to mitigate the defects.

Passivation and annealing are crucial to reducing carrier recombination and prolonging carrier lifetime. By tying up dangling bonds and reducing the number of defects, device efficiency is increased and carrier collection improved. The passivation layers used must be robust under constant light exposure in outdoor environments, and transparent (on the front side of the cell), to allow light penetration into the cell without absorbing much of the solar spectrum (15). Many materials can be used along with different deposition methods and subsequent heat treatments for passivation. In many solar cells, amorphous silicon (a-Si:H) layers or silicon oxide (SiO<sub>x</sub>) layers are used for passivation (14). Amorphous silicon layers can degrade over time, with light exposure and heating, due to the breakdown of the silicon-hydrogen in the film (15). The deterioration happens over the course of tens of years, but once it occurs the passivation qualities

of the film are lost. Amorphous silicon is deposited using plasma enhanced chemical vapor deposition (PECVD). Silicon oxide doubles as an anti-reflection coating (ARC) and a passivation layer. As an ARC it provides enhanced light trapping and light absorption. Silicon dioxide (SiO<sub>2</sub>) can be grown through thermal oxidation, or SiO<sub>x</sub> can be deposited using PECVD. Dual layers of a-Si:H and SiO<sub>x</sub> can be used to maximize the benefits of each material and prolong the longevity of the passivation quality. Silicon nitride (SiN<sub>x</sub>) is another common material used to provide surface passivation (14). Similar to SiO<sub>x</sub>, SiN<sub>x</sub> acts as an ARC, and is deposited through PECVD. Recently amorphous silicon carbide (a-SiC<sub>x</sub>) has been found to provide suitable passivation of silicon by researchers at Fraunhofer ISE (14) (16) (17).

Fixed charge passivation relies on charge in the deposited passivation layer to repel carriers from the surface, in addition to passivation through satisfying dangling bonds and surface states. The main mechanism for passivation is that of field effect passivation; by shielding carriers from the surface, they are never near enough to surface defects to have the opportunity to recombine (15) (18). Negative fixed charge in the passivation film is critical for providing passivation of the surface. Alumina (Al<sub>2</sub>O<sub>3</sub>) has been reported to have large densities of fixed charge (15) (18), and several groups have demonstrated its use in high-efficiency solar cells. Atomic layer deposition (ALD) and plasma assisted ALD or chemical vapor deposition (CVD) are useful in deposition of Al<sub>2</sub>O<sub>3</sub> passivation layers (15) (19) (20). Film thickness, passivation layer structure, and annealing treatments are important variables in optimizing passivation for increasing carrier lifetime at the surface. Fixed charge passivation potentially could replace conventional passivation materials if proven robust and capable of reducing carrier recombination.

#### **Solar Cell Design Improvements and Modern Structures**

In recent years there has been a push to thinner solar cells not only as a result of materials cost, but also due to the performance limitations associated with thicker base materials. If the base layer is excessively thick the photogenerated carriers have more opportunities to recombine within the material before they can be collected at a contact (2). Subsequent generations of solar cells, building upon the bulk crystalline cell, feature device designs and manufacturing techniques to improve performance and cost savings. Thinning the silicon used in the cell is one method to cut costs, but advancements in cell design typically require more expensive manufacturing processes, which are justified only by device performance improvements or cost savings elsewhere (5). To achieve higher conversion efficiencies and reduce manufacturing costs is a challenging combination but ultimately what manufacturers must do.

Recently, structures including the "heterojunction with intrinsic thin layer" (HIT) cell by Sanyo, and rear surface point-contact cells by SunPower, have been commercially manufactured. Sanyo and SunPower have demonstrated cells in production that achieve efficiencies upwards of 20%, with the HIT cell (23%) and rear point contact cell (22.7%), respectively (16) (21). Two additional cell structures that have the potential to defray manufacturing costs and improve device performance are the passivated emitter and rear cell (PERC) and the front surface field interdigitated back contact, back junction cell (FSF-IBC) (14) (22). Coupled with laser manufacturing, the PERC and FSF-IBC structures could lead to significant advancements in cell performance and efficiency (23) (24).

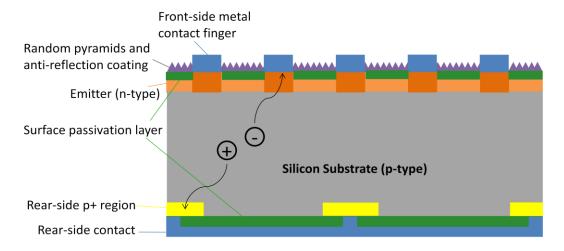

The PERC family of cells has achieved some of the highest efficiencies reported. As early as 1990 they were demonstrated with an energy conversion efficiency of 23.1% (25). Shown in Figure 1-2, the passivated emitter and rear locally diffused (PERL) cell features passivation at both the front and rear surfaces along with rear-side diffused p+ regions that serve

to reduce recombination losses at the contacts (2). PERL cells and passivated emitter rear totally diffused (PERT) cells have been demonstrated by researchers at the University of New South Wales with efficiencies of more than 24% (25). Both are types of PERC cells, featuring localized rear contacts made through the passivating dielectrics.

Figure 1-2: Passivated emitter and rear locally diffused cell (PERL) adapted from (2).

Creating a heavily doping the region under the contacts makes collection of majority carriers more efficient by the formation of a p-p+ junction and a local back surface field (13). In a PERC cell, the local rear-side contacts can be formed through laser firing, creating highly doped regions like those in a PERL cell, resulting in a BSF due to incorporation of Al into the laser fired contact. Laser firing of PERC cells reduces manufacturing steps and makes them more manufacturable while maintaining high efficiency. The Fraunhofer Institute for Solar Energy Systems has demonstrated PERC cells achieving efficiencies from 20.2 to 22.4% (16) (24) (26).

To reduce costs lower quality multi-crystalline silicon is often substituted for single crystalline silicon. The mc-Si has shorter minority carrier diffusion lengths and shorter carrier lifetimes, which limit the distance that the photogenerated carriers can travel to reach a contact. The lower quality material dictates the use of a front-side emitter and contact grid to ensure carriers can be collected at the front surface, in the vicinity where they are generated (5).

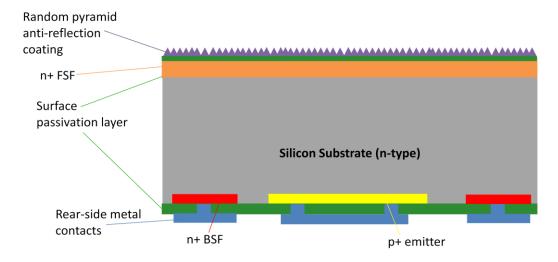

Unfortunately, the use of front side metal fingers causes shading loss of the active silicon, reducing the area available for photon absorption, leading to a reduction in cell efficiency. An innovative cell design to completely prevent shading loss is the front surface field, interdigitated back contact, back junction cell (FSF-IBC) shown in Figure 1-3. Interdigitating both contacts for collection of electrons and holes (shown as the n+ BSF and the p+emitter) on the rear-side of the cell leaves no metallization in the front side to shadow the active region of the cell (5).

Figure 1-3: Front surface field, interdigitated back contact, back junction cell (FSF-IBC) adapted from (2).

An n-type substrate is used due to the higher carrier mobilities it features. Higher quality substrates must be used in IBC cells because carriers generated at the front surface must travel from the front surface to the collecting contacts and emitters at the rear-side of the cell (9); therefore, it is critical that minority carrier lifetime and bulk diffusion lengths are very long.

As cells become thinner, the quality of the substrate plays an increased role in performance. Since the active region is thinner, the use of a high quality substrate is critical to maintaining device performance (9). Additionally, with the removal of the bulk thickness, carrier collection at the rear of the cell becomes more prevalent, making the FSF-IBC design more attractive (5).

With increased carrier collection at the rear side, cell performance can be severely limited if recombination at the rear surface and contacts occurs. Passivation at the front and rear surfaces become increasingly important in thinner cells, as well as FSF-IBC cells. In a FSF-IBC cell, excellent surface passivation is important in order to prevent carrier recombination at the front side surface since there are no contacts present to collect them (9). Passivation of the rear surface is important as well since the presence of both contacts means a large concentration of electrons and holes will be in the same area. Recombination at the contacts and front surface must be combatted using field effects (high doping density to create BSFs) and chemical passivation layers (5).

#### **Solar Cell Structure and Laser Firing**

The introduction of laser processing to photovoltaic manufacturing has the potential to be very advantageous for solar cell manufacturability. Laser firing makes possible the formation of front and rear-side contacts in a few steps, rather than the numerous photolithography, development, etching, and metallization steps or the high temperature screen printing steps previously required (24). The formation of front and rear-side contacts through laser firing is one potential method of reducing manufacturing cost while maintaining device performance and improving processing throughput; however, careful control of laser processing conditions must be implemented to ensure that device performance is maintained. It is imperative to understand how lasers processing can be used beneficially for improvement of device performance and implementation in manufacturing.

Laser fired contacts (LFCs) rely on a laser to selectively heat and melt regions of the rear Al contact layer through the rear-side passivation layers to create a localized rear-side contact into the underlying silicon substrate. In a PERC type cell this process creates contacts along with a localized back surface field (BSFs) created by the incorporation of Al into the molten silicon and subsequent solidification. The BSF positively impacts the recombination dynamics at the rearside contact given that the LFC does not introduce excessive damage to the region around it (16). The primary concern with replacing rear-side solar cell contacts with LFCs is that structural damage can occur due to the large amount of energy imparted by the laser to a very small volume over an exceedingly short time. Excessive laser energy can result in damage to the surrounding substrate and passivation layers, making careful selection of laser processing parameters critical. Conditions for forming LFCs must be only energetic enough to melt and mix the aluminum and silicon in the locally fired contact region; ablation, drilling, or a large heat affected zone are undesirable (27). With careful selection and control of the laser processing parameters, LFCs can be implemented into solar cells structures and can improve cell performance and manufacturing throughput.

The doping of locally diffused front side emitters is also possible with the proper implementation of laser firing. So-called laser doped emitters (LDEs) can be fabricated by selectively firing the laser in regions to be metallized. By firing through a dopant layer, a high concentration of the dopant is incorporated into the molten silicon substrate at points selectively melted with a laser (10). Using a laser to dope the emitter has the potential to degrade device performance if the laser processing parameters are excessively energetic. Excessive laser energy can induce defects into the crystalline structure that can act as recombination centers and reduce the number of carriers available for collection (28). In particular, series resistance, saturation current, and leakage current may be affected, and if any one of these parameters is increased, it detracts from the emitter's performance. The diode ideality factor also suffers with increased recombination; therefore, it is critical to perform laser doping with mild processing conditions that do not damage the silicon, but are energetic enough only for adequate doping of the contact, through the passivation layers.

The passivated emitter and rear cell (PERC) and front surface field interdigitated-back contact (FSF-IBC) cell are particularly well suited for the implementation of laser firing in solar manufacturing. In PERC cells, laser firing has been used to fire rear-side ohmic contacts though passivation layers, incorporating Al into the melted laser fired region of the silicon, forming cells with efficiencies greater than 20% (16) (24) (26). With improved understanding of laser-material interactions and LFE and LDE performance, a fully laser processed cell could be commercially manufactured in the near future.

#### **Motivation**

For solar energy to achieve grid parity, methods to increasing cell efficiency and manufacturability, while minimizing cost, need to be developed. Combining innovative cell structures, like the PERC and FSF-IBC, with advanced processing methods, like laser processing, is one strategy that holds promise in improving solar cell's manufacturability. Laser processing of rear-side contacts and front-side doped emitters, along with the introduction of new passivation techniques, can greatly improve performance of both PERC and FSF-IBC cells, providing efficiency enhancement and eliminating the traditional processing steps for patterning or screen printing emitters and contacts. Using the appropriate processing conditions, laser firing the rear-side contacts and laser doping the front-side emitters of crystalline silicon PERC solar cells could be adapted to a low-cost, high-volume manufacturing scenario.

## **Experiments and Goals**

In order to evaluate the feasibility of laser firing a solar cell and to assess the quality of the resulting contacts and emitters, several experiments have been performed. LFCs were fabricated and characterized through cross-sectioning, junction delineation, and simulations of resistance measurements. Two lasers, a ytterbium-doped 1070 nm single mode fiber laser and a Nd:YVO<sub>4</sub> 355 nm frequency tripled Q-switched laser, were utilized to evaluate laser processing parameters. Evaluation of contact geometry within the silicon was carried out using a newly developed technique of cross-sectioning and junction delineation of laser doped features. Device simulations were also performed to estimate the dopant density of the LFCs and to fit experimental current-voltage (I-V) data.

Laser doped emitters were fabricated and evaluated through I-V measurements, cross-sectioning, and junction delineation. Line emitters are generally studied in the literature, but herein we study individual spot emitters. Fabrication of the LDEs was performed with three different lasers; a ytterbium-doped 1070 nm single mode fiber laser, a Nd:YVO<sub>4</sub> 355 nm frequency tripled solid state Q-switched laser, and a Nd:YAG 1064 nm Q-Switched laser. Diode characteristics were evaluated for each LDE by comparing diode ideality factors, saturation currents, and leakage currents. Cross-sectioning and junction delineation were performed to determine emitter depth and width within the substrate.

In passivation layer experiments, alumina (Al<sub>2</sub>O<sub>3</sub>) and hafnia (HfO<sub>2</sub>) films prepared by atomic layer deposited (ALD) were investigated as a means of providing fixed charge passivation. Films of varying thickness, and multi-layer structures incorporating plasma-enhanced chemical vapor deposited (PECVD) silicon oxide (SiO<sub>x</sub>), were studied with different annealing treatments. Each passivation structure given a different annealing treatment was evaluated through measurement of effective carrier lifetime, calculated fixed charge densities, and sheet resistance changes in special high resistivity wafers, indicating the presence of an inversion layer. Microwave photoconductive decay was used to measure effective carrier lifetime, capacitance-voltage (C-V) measurements were used to calculate fixed charge densities, and a contactless conductivity probe was used to measure sheet resistance.

In evaluating these devices and passivation layers, the goal was to identify a means to fabricate a fully laser processed, high efficiency cell. Each structure is critical to the device performance and by optimizing each—the contacts, emitters, and passivation—a high efficiency cell may be manufactured affordably through laser processing.

# Chapter 2

# **Laser Fired Contacts**

#### **Literature Review**

Laser processing has made possible the formation of rear-side ohmic contacts without the use of multi-step photolithography patterning processes previously used in high efficiency solar cells. Instead of opening the rear side dielectric passivation through patterning and etching, and then metalizing the rear contacts, a laser can be used to fire through both the metal and dielectric passivation layers to incorporate the metal into the silicon substrate. Laser fired contacts (LFCs) are also suitable for replacing rear-side contact patterning by screen printing, which requires deposition of a metal paste and a high temperature firing step to create the contact. The elimination of extra processing steps and high temperature steps, along with the potential for compatibility in high efficiency device production has made research in laser processing widely popular. The ability to create laser fired contacts (LFCs) and apply them to solar cell devices has been demonstrated by many research groups (24) (26) (29) (30) (31). The best efficiencies reported have been greater than 18%, with the highest reported being 21.3% and recently 22.4% (14) (16) (24). Devices performance is evaluated by examining solar cell characteristics, including open circuit voltage, Voc, short circuit current, Jsc, fill factor, FF, and conversion efficiency, n. However, deeper understanding of the contacts themselves requires further characterization, and groups have used several techniques to do so. The work of Zastrow et al. (23) involved secondary ion mass spectroscopy (SIMS) and transmission electron microscopy (TEM) characterization. LFCs were fired with a pulsed Nd:YAG laser and had diameters between 80 and 100  $\mu$ m. The group found concentrations of Al on the order of ~10<sup>19</sup>cm<sup>-3</sup> at the center of

the LFC, which was incorporated within the contact to a depth of 1 µm (23). Grohe et al. (22) performed laser secondary neutral mass spectroscopy (L-SNMS) as well as electron beam induced current (EBIC) measurements on LFCs fired with a Q-switched Nd:YAG laser. The EBIC and L-SNMS measurements indicated that Al was incorporated with Si in the center region of each contact (22). Additional EBIC measurements on the cross-section of a cleaved LFC confirmed incorporation of the Al within the contact to a depth of ~1µm (22). Kray and Glunz investigated the morphology of LFCs and reported the effects of contact pitch on surface recombination velocity (SRV) analytically and experimentally (32). Surface recombination velocity was determined based on bulk carrier lifetime and near surface carrier lifetime. Light beam induced current (LBIC) measurements, scanning electron microscopy (SEM) images, and EBIC measurements were taken on LFCs to determine the presence of Al in the inner region and measure contact diameter. When performing SEM/EBIC scans on a cross-sectioned LFC fired on n-type silicon, they found Al present within the volume of their contacts as well (32). They report a SRV of 35 cm/s with a contact pitch of 1000µm (32). All these techniques are useful for tracing the presence of Al incorporated into the contacts and prove the ability to create LFCs; however, little has been disseminated with regards to the appropriate laser processing conditions to use.

A majority of the LFCs examined in previous work were fired with 1064 nm lasers with nanosecond pulse durations; in research carried out by past students on this project, an investigation to identify processing conditions for 1070 nm and 355 nm lasers was performed (27). Through evaluation of contact resistance, SEM observations, and post-processing effective carrier lifetime measurements, processing conditions of LFCs fabricated with a gated pulse ytterbium-doped 1070 nm single mode fiber laser and with a Nd:YVO<sub>4</sub> 355 nm frequency tripled Q-switched solid-state laser were evaluated for use in manufacturing. Samples investigated were passivated with either 10 nm of amorphous silicon (a-Si:H) and 100 nm of silicon oxide (SiO<sub>x</sub>)

deposited by plasma-enhanced chemical vapor deposition (PECVD), or 80 nm of a-Si:H deposited by PECVD and metallized with a 0.5 µm Al layer deposited on both sides using electron-beam (e-beam) deposition (27). All wafers used for resistance experiments and surface morphology studies were ~275 µm thick (100) p-type float zone (FZ) silicon wafers with a resistivity between 1-5 Ω-cm. LFCs fabricated with each laser were evaluated using SEM imaging to assess visible changes to the contact morphology as a function of laser processing parameters. For the 1070 nm laser, using high power (> 45 W) and long pulse durations (> 14 ms) resulted in large diameter contacts (> 50 μm), and at the largest powers and pulse durations (50 W, 19 ms) degradation of the surrounding area occurred due to a large heat affected zone (27). When low power and short pulse durations were used (< 30 W, and 14 ms), the contacts were much smaller in diameter (< 20 µm) and damage to the surrounding substrate was minimal (27). For the 355 nm laser, using high energies (> 50 µJ) and multiple pulses per shot (> 1 pulse) created large contacts and ablated a significant amount of material to the point of laser drilling. Those contacts fired at lower energies (< 50 µJ) and single pulses did not penetrate the substrate deeply but still exhibited ablation (27). Following SEM investigation resistance measurements were taken on LFCs fired with each laser to understand the effect of laser processing conditions on the electrical performance. Resistances measured on LFCs fired with the IPG 1070 nm single mode fiber laser correlated inversely with size. The resistance decreased with increased LFC diameter, implying that processing with larger powers and longer pulse duration led to larger contacts with smaller resistances. For the AVIA 355 nm laser, no trends or correlations between resistance and processing conditions were apparent. It was concluded that further investigation of less energetic pulses would be needed to further evaluate the usefulness of the AVIA 355 nm solid state Q-switched laser in LFC manufacturing. Carrier lifetime mapping provided insight into the consequences of laser firing on the effective carrier lifetime. It was demonstrated that appropriate laser firing conditions (30 W and 6.5 ms, 30 W and 21.5 ms, and

50 W and 4 ms) could be selected to avoid significant degradation of the effective carrier lifetime (27). The lifetime in regions surrounding LFCs processed with the IPG 1070 nm did not degrade after laser processing, but lifetime in regions surrounding LFCs fired with the AVIA 355nm laser did. A 10 min 275°C anneal was required post processing to re-measure lifetime.

Having gained an understanding of laser processing conditions useful for LFC creation in this previous work, additional experimentation was needed to understand the laser-material interaction. The work herein sought to study the effects of laser processing conditions on Al incorporation and concentration in the contact, and the resulting geometry of the contact within the silicon substrate.

#### LFC Simulation and Cross-sectioning Goals

Based on the experiments performed by DeCesar (27), additional experiments were performed along with simulations, to understand LFC geometry and doping. Cross-sectioning and junction delineation were performed to investigate contact depth within the silicon. A technique was developed to delineate the geometry of the melt region. Simulations using Sentaurus (33) device simulator were carried out to estimate the doping density of the laser fired contacts and fit the experimental trend of reduced contact resistance with increased LFC diameter. LFCs were modeled and resistance measurements were simulated in an attempt to match experimental resistance measurements taken by DeCesar.

## **Cross-sectioning and Junction Delineation**

# **Sample Fabrication**

In order to create a p-n junction upon laser firing a p-type Al contact, samples for cross-sectioning and junction delineation were fabricated on ~500  $\mu$ m thick (100) n-type Czochralski-grown (CZ) silicon wafers with a resistivity of 0.5-1  $\Omega$ -cm. The n-type samples were passivated with either 80 nm of PECVD grown a-Si:H or 10 nm of PECVD grown a-Si:H and 100 nm of PECVD grown SiO<sub>x</sub>, and metallized with 0.5  $\mu$ m of Al deposited on both sides by e-beam deposition.

The same ytterbium-doped 1070 nm continuous wave, gated pulse, single mode fiber laser used in previous work was used in fabrication of samples that were cross-sectioned. The 355 nm laser was not investigated due to the poor results previously seen in LFC resistance measurements. Dense arrays of LFCs were fired to increase the likelihood of cross-sectioning multiple contacts on a single sample. Center to center spacing of the LFCs in the array was equal to approximately twice their measured diameter.

#### **Processing Procedures**

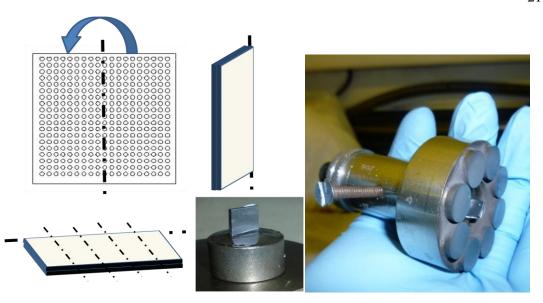

Following laser processing, samples were sectioned using a diamond saw for precise control of sample size and orientation. A piece of the sectioned array was super-glued on its face to another silicon piece to protect the edges to be polished from rounding off. The glued sample was mounted onto a polishing stub. The procedure is detailed in Figure 2-1.

Figure 2-1: Dense array and sample preparation for polishing.

By polishing the sample with increasingly finer grits of silicon carbide polishing disks, the sample was gradually ground down and scratches in the surface were polished out. The disks were mounted on a rotating polishing wheel, seen in Figure 2-2, and a steady stream of water was run across them while they spun. Polishing the samples with the LFC array at a slight angle, indicated in Figure 2-2 by  $\theta$ , increased the likelihood of cross-sectioning more than one LFC.

Figure 2-2: Polishing wheel and angle at which the sample is polished.

Throughout the grinding process, the surface was examined under a light microscope to assess the location of the cross-section within the LFC array. The approximate middle of an LFC, where the laser should have melted the silicon to a maximum depth, was reached when the characteristic peaks, at the center of an LFC on the surface, were apparent in cross-section. Once a successful cross-section was made, a final polishing pad was used, and afterwards the sample was rinsed in a de-ionized (DI) water bath and dried with N<sub>2</sub> gas.

Techni Gold 25, an electroless plating solution made by Technic, Inc., was used to delineate the p-n junction of the LFCs in a manner similar to that reported for delineating p-n junctions in silicon nanowires (34). Aluminum is a p-type dopant that has solubility on the order of 10<sup>19</sup> cm<sup>-3</sup> in silicon (35) (36). On an n-type wafer the incorporation of Al forms a p-n junction at each laser fired contact, making selective plating possible. Eichfeld et al. successfully demonstrate the selectivity of Technic Gold 25 on very small geometries, delineating n-type sections of 1.4 μm to 0.12 μm lengths on alternating n- and p-type segments of silicon nanowires only 150 nm in diameter (34). Under illumination, gold in the solution selectively plates on the n-type region of the silicon. The n-type region acts as a cathode, due to electrons generated, and the p-type region functions as an anode, remaining free of nucleated gold, due to holes generated.

Cross-sectioned samples were immersed in the plating solution and illuminated with a 50 W halogen lamp for 6 to 8 min at room temperature. Once removed from the solution, the samples were rinsed with DI water and dried with nitrogen gas. Imaging the samples in the field emission scanning electron microscope (FESEM) clearly showed the p-type regions created from laser firing, and provided evidence of the presence and incorporation of Al within the laser fired region, seen in Figure 2-3.

Figure 2-3: Successful cross-section of a row of LFCs and junction delineation between the p-type melt regions and the n-type substrate, sample passivated with a-Si:H/SiO<sub>x</sub>.

### **Results and Discussion**

Four different samples were cross-sectioned and plated after being processed with the IPG 1070 nm laser. Shown in Table 2-1, two sets of processing conditions were fired onto each type of passivated substrate. The processing conditions, 45 W and 4 ms along with 22 W and 19 ms, were selected to compare the dimensions of the resulting LFCs on each passivation structure. At the higher 45 W power there was not a significant difference in the dimensions of LFCs fired on either substrate, indicating that the structure of the passivation layers did not impact LFC formation. At the lower 22 W power, the LFC fired on the a-Si:H passivation structure is slightly larger than the LFC fired on the a-Si:H/SiO<sub>x</sub> layer. The difference is slight, but indicates that the presence of the SiO<sub>x</sub> layer may impact LFC formation at lower powers.

Table 2-1: Dimensions of cross-sectioned profiles within the substrate.

| Sample | Passivation             | Power | Duration | LFC Width | LFC Depth |

|--------|-------------------------|-------|----------|-----------|-----------|

| n-type | a-Si:H                  | 5 W   | 4 ms     | 57 μm     | 25 μm     |

| n-type | a-Si:H/SiO <sub>2</sub> | 45 W  | 4 ms     | 60 μm     | 28 μm     |

| n-type | a-Si:H                  | 22 W  | 19 ms    | 45 μm     | 21 μm     |

| n-type | a-Si:H/SiO <sub>2</sub> | 22 W  | 19 ms    | 42 μm     | 16 μm     |

Samples with the 45 W pulse had much larger melt regions than those fired with 22 W, which would be expected. Both sets of processing conditions adequately incorporated aluminum in silicon as evidenced by successful plating of samples. If Al had not been incorporated, there would not have been a noticeable contrast in the plating between n- and p-type regions. It is surmised that the geometry of the p-type region represents the once-molten solidified region, and originates from the melting and mixing of aluminum and silicon during the laser pulse. Solid state diffusion would be negligible given the length of the pulse durations. Aluminum was incorporated within the silicon to depths from 16 to 28  $\mu$ m, which was much deeper than previously reported (22) (23). Any effect a depletion region may have had on the dimensions has been neglected. Based on the assumed doping concentrations of  $1x10^{16}/cm^3$  for phosphorus in the n-type substrate (from  $\rho = 0.5$ -1  $\Omega$ -cm) and  $2x10^{19}/cm^3$  for Al in the p-type once-molten region (taken from (35)), the depletion width would be less than 0.4  $\mu$ m wide.

The characteristic morphology of LFCs fired with the 1070 nm single mode fiber laser exhibited a peak in the center of a recessed area. LFCs fired at 4 ms and 45 W are seen in Figure 2-4. The figure shows the diameter of the molten region, the diameter of the heat affected zone, and the center peak of the once-molten region. The diameter of the LFC, measured as the visible width of the molten region, is approximately 45 µm.

Figure 2-4: Sample fired at 45 W and 4 ms showing typical morphology of LFCs fired with the IPG 1070 nm single mode fiber laser.

As seen in cross-sectioning, the width of the once molten region is somewhat wider than what is visible at the surface. Figure 2-5 shows the extent of the p-type region for different laser parameters on each type of sample. Both were fired using the IPG 1070 nm single mode fiber laser. The LFC in image (a) was fired at 22 W and 19 ms on an n-type wafer passivated with a-Si:H. The LFC in image (b) fired at 45 W and 4 ms on an n-type wafer passivated with the a-Si:H/SiO<sub>x</sub> dual stack. In image (b), the characteristic peak seen in the top view of the LFCs in Figure 2-4 is evident in the cross-section.

Figure 2-5: Cross-sections after junction delineation of an LFC (a) fired at 22 W and 19 ms, passivated with a-Si:H, and an LFC in image (b) fired at 45 W and 4 ms, passivated with a-Si:H/SiO<sub>x</sub>.

### **LFC Simulation**

# **Device Modeling and Simulation**

To further understand the effects of laser processing parameters on the contact resistance and to determine if experimental measurements could be predicted, LFC simulations were performed using SENTAURUS TCAD by Synopsys, Inc. (33) with the assistance of Brian Downey.

Based on the results of cross-sectioning, the LFC device was modeled as a doped hemispherical region embedded at the surface of a silicon substrate. The model was created based on sample geometry, with a wafer thickness of  $275\mu m$  and length and width of  $700~\mu m$  on a side. Taking advantage of symmetry, current transport in only one quarter of the contact was simulated, and the total resistance of each LFC was found by dividing the simulated resistance by 4.

In order to simulate the boron doped substrate used in experiments, which was measured to have a resistivity of approximately  $2~\Omega$ -cm, the modeled substrate was doped p-type with a boron acceptor concentration of  $7x10^{15}$  cm<sup>-3</sup>. Simulations were performed using different doping densities for the contact region to best match the actual doping density of the contact by comparing simulations to experimental measurements. Many papers report aluminum concentrations in silicon similar to the solid solubility limit of  $2x10^{19}$ /cm<sup>3</sup>, as given by Trumbore in 1960 for a film grown at  $800^{\circ}$ C (35) (36). However, solubilities from  $3x10^{19}$  up to  $10^{20}$ /cm<sup>3</sup> have been suggested for films deposited and annealed at temperatures from  $400\text{-}500^{\circ}$ C (37) (38) (39). Doping densities up to  $1x10^{20}$ /cm<sup>3</sup> were modeled to compare with the experimental data.

The device was simulated by applying a dc bias to the top surface area of the LFC region from 0 to 2 V with the entire back side of the substrate at ground. The metal/semiconductor

contact resistance was neglected in the simulation due to the assumption that Al metal contacts a highly doped p+ region leading to a low specific contact resistance. Those reported in the literature justify this assumption. Hara et al. reported a contact resistivity of  $4x10^{-6}\Omega$ -cm<sup>2</sup> for an Al sintered contact at 450°C on p+ silicon with a surface dopant concentration of  $1x10^{19}$  cm<sup>-3</sup> (40). Furthermore, Schwartz reported a contact resistivity of  $3.6x10^{-6}\Omega$ -cm<sup>2</sup> for laser annealed Al contacts to poly-Si (41). A contact resistivity of  $4x10^{-6}\Omega$ -cm<sup>2</sup> corresponds to a contact resistance of  $0.2~\Omega$  for a  $25\mu$ m radius contact. Such a resistance is much less than the total resistance measured (~100  $\Omega$ ) and can be neglected. The generated I-V plot produced from the simulation was used to determine the total resistance of each different diameter contact.