# The Pennsylvania State University

# The Graduate School

# Graduate Program in Materials Science and Engineering

# SYNTHESIS AND CHARACTERIZATION OF SILICON NANOWIRE ARRAYS FOR PHOTOVOLTAIC APPLICATIONS

A Dissertation in

Materials Science and Engineering

by

Sarah M. Eichfeld

© 2009 Sarah M. Eichfeld

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2009

The dissertation of Sarah M. Eichfeld was reviewed and approved\* by the following:

Joan M. Redwing Professor of Materials Science and Engineering Chair, Intercollege Materials Science and Engineering Graduate Degree Program Dissertation Advisor Chair of Committee

Thomas E. Mallouk DuPont Professor of Materials Chemistry and Physics

Suzanne E. Mohney Professor of Materials Science and Engineering

Christopher L. Muhlstein Associate Professor of Materials Science and Engineering Corning Faculty Fellow

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

Due to rising energy costs and the growing demand for renewable energy, silicon nanowire arrays have become of interest for solar cells. Radial p-n junction silicon nanowire arrays allow for the decoupling of the directions of light absorption and carrier collection, which allows for the possibility of increased efficiencies. Prior device modeling studies have demonstrated that increased carrier collection can be obtained in radial p-n junction nanowires when the wire radius is approximately equal to the minority carrier diffusion length in the material. Consequently, radial p-n junction silicon nanowires are anticipated to enable increased efficiency in solar cells fabricated with less pure and therefore potentially lower cost silicon. Fabrication of these structures on low cost substrates such as glass would then enable a further cost reduction. The overall objective of this thesis was the development of processes for the fabrication of radial p-n silicon nanowires (SiNWs) using bottom-up nanowire growth techniques on silicon and glass substrates.

Vapor-liquid-solid (VLS) growth was carried out on Si(111) substrates using  $SiCl_4$  as the silicon precursor. Growth conditions including temperature,  $P_{SiCl4}$ ,  $P_{H2}$ , and position were investigated to determine the optimum growth conditions for epitaxially oriented silicon nanowire arrays. The experiments revealed that the growth rate of the silicon nanowires exhibits a maximum as a function of  $P_{SiCl4}$  and  $P_{H2}$ . Gas phase equilibrium calculations were used in conjunction with a mass transport model to explain the experimental data. The modeling results demonstrate a similar maximum in the mass of solid silicon predicted to form as a function of  $P_{SiCl4}$  and  $P_{H2}$ , which results from a change in the gas phase concentration of  $SiH_xCl_y$  and  $SiCl_x$

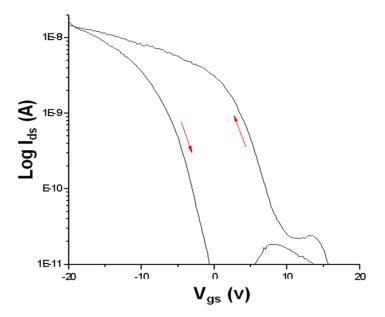

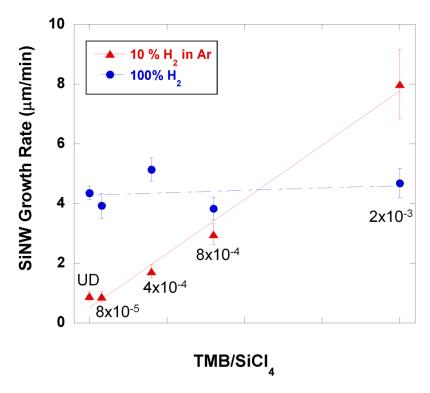

species. This results in a shift in the process from growth to etching with increasing  $P_{SiCl4}$ . In general, for the atmospheric pressure conditions employed in this study, growth at higher temperatures >1000°C and higher SiCl<sub>4</sub> concentrations gave the best results. TEM analysis of silicon nanowires grown at different SiCl<sub>4</sub> concentrations revealed no distinct differences in the structural properties of the SiNWs. Doping of the SiNWs using trimethylboron (TMB) was also examined. Gated I-V measurements demonstrated that the SiNWs exhibited p-type behavior. Wires doped with a TMB/SiCl<sub>4</sub> ratio of 0.1 had a resistivity in the range of  $10^{-3}$   $\Omega$ -cm. However, wires with a TMB/SiCl<sub>4</sub> ratio of  $2x10^{-3}$  exhibited a resistivity of  $10^{3}$   $\Omega$ -cm.

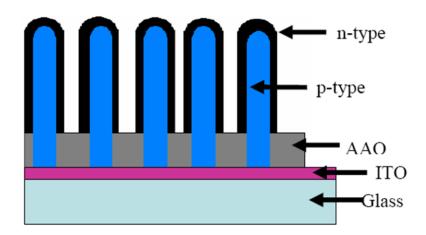

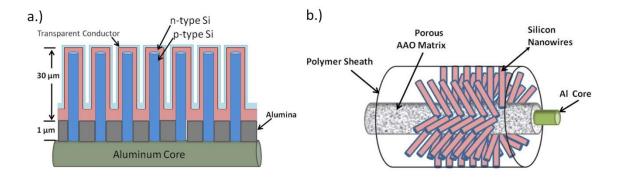

The growth of silicon nanowire arrays on anodized alumina (AAO)-coated glass substrates was also investigated. Glass will not hold up to the high temperatures required for Si nanowire growth with SiCl<sub>4</sub> so SiH<sub>4</sub> was used as the Si precursor instead. Initial studies were carried out to measure the resistivity of p-type and n-type silicon nanowires grown in freestanding AAO membranes. A series of nanowire samples were grown in which the doping and the nanowire length inside the membrane were varied. Circular metal contacts were deposited on the top surface of the membranes and the resistance of the nanowire arrays was measured. The measured resistance versus nanowire length was plotted and the nanowire resistivity was extracted from the slope. The resistivity of the silicon nanowires grown in the AAO membranes was then compared to the resistivity of silicon nanowires grown on Si and measured using single wire four-point measurements. It was determined that the undoped silicon nanowires grown in AAO have a lower resistivity compared to nanowires grown on Si substrates. This indicates the presence of an unintentional acceptor. The resistivity of the silicon nanowires was found to change as the dopant/SiH<sub>4</sub> ratio was varied during growth. The growth and doping conditions developed from this study were then used to fabricate p-type SiNW arrays on the AAO coated glass substrates.

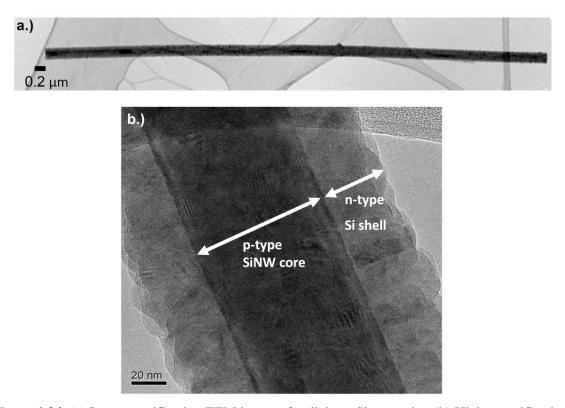

The final investigation in this thesis focused on the development of a process for radial coating of an n-type Si layer on the p-type Si nanowires. While prior studies demonstrated the fabrication of polycrystalline n-type Si shell layers on Si nanowires, an epitaxial n-type Si shell layer is ultimately of interest to obtain a high quality p-n interface. Initial n-type Si thin film deposition studies were carried out on sapphire substrates using SiH<sub>4</sub> as the silicon precursor to investigate the effect of growth conditions on thickness uniformity, growth rate and doping level. High growth temperatures (>900°C) are generally desired for achieving epitaxial growth; however, gas phase depletion of the SiH<sub>4</sub> source along the length of the reactor resulted in poor thickness uniformity. To improve the uniformity, the substrate was shifted closer to the gas inlet at higher temperatures (950°C) and the total flow of gas through the reactor was increased to 200 sccm. A series of n-type doping experiments were also carried out. Hall measurements indicated n-type behavior and four-point measurements yielded a change in resistivity based on the PH<sub>3</sub>/SiH<sub>4</sub> ratio. Pre-coating sample preparation was determined to be important for achieving a high quality Si shell layer. Since Au can diffuse down the sides of the nanowire during sample cooldown after growth, the Au tips were etched away prior to shell layer deposition. The effect of deposition temperature on the structural properties of the shell layer deposited on the VLS grown SiNWs was investigated. TEM revealed that the n-type Si shells were polycrystalline at low temperatures (650°C) but were single crystal at 950°C. SiNW samples grown on glass were also coated; however, due to the temperature constraints, the maximum temperature used was 650°C and therefore the n-type Si shells were polycrystalline.

SiNW arrays grown using SiCl<sub>4</sub> on Si(111) substrates were grown with a high degree of orientation and average growth rates of 3-4 µm/min at temperatures of 1050°C. Modeling results indicated the nanowire growth was limited by mass transport. SiNW arrays were also grown using SiH<sub>4</sub> on AAO coated glass. Epitaxial n-type Si regrowth was demonstrated on SiNW arrays

grown on Si(111) with SiCl<sub>4</sub>. The n-type Si deposition was carried out using SiH<sub>4</sub> at 950°C and a total pressure of 3 Torr. SiNWs grown on AAO coated glass substrates were also radially coated with n-type Si; however, due to temperature limitations the shell was polycrystalline. Future work on this project could include a study on the doping of SiNWs grown using SiCl<sub>4</sub>. Device measurements using the radial p-n junction SiNW arrays fabricated could also be carried out. Finally, a study on the effects of sample preparation, nanowire, and n-type shell doping could be correlated to the device measurements.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                        | X                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                         | xvii                             |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                       | xviii                            |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                 | 1                                |

| 1.1 Motivation 1.2 Silicon Photovoltaics 1.2.1 Silicon Nanowire Solar Cell 1.2.2 Fabrication of Silicon Nanowire Solar Cell 1.3 Focus of this Study 1.4 References                                                                                                                                                                                                                     | 3<br>8<br>11                     |

| Chapter 2 Literature Review                                                                                                                                                                                                                                                                                                                                                            | 20                               |

| 2.1 Introduction  2.2 CVD Growth of Silicon  2.2.1 Silicon Thin Film Growth using SiCl <sub>4</sub> 2.2.2 Silicon Thin Film Growth with SiH <sub>4</sub> 2.3 Silicon Nanowire Growth  2.3.1 Vapor-Liquid-Solid Mechanism  2.3.2 SiNW Growth using SiCl <sub>4</sub> 2.3.3 Growth Mechanism Diameter Dependence  2.3.4 SiNW Growth using SiH <sub>4</sub> 2.3.5 In-Situ Doping of SiNWs | 20<br>21<br>27<br>29<br>30<br>33 |

| Chapter 3 Experimental Methodology                                                                                                                                                                                                                                                                                                                                                     | 46                               |

| 3.1 Introduction 3.2 Substrate Preparation 3.2.1 Electrodeposition of Au in AAO Membranes 3.2.2 Silicon Wafer Preparation 3.3 Si CVD Growth                                                                                                                                                                                                                                            | 46<br>47<br>50                   |

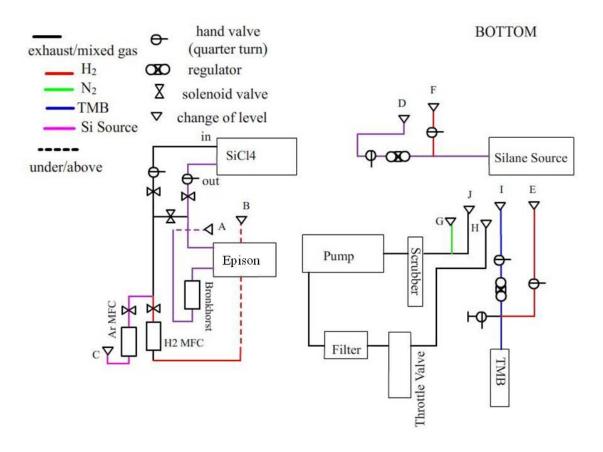

| 3.3.1 Atmospheric Pressure Chemical Vapor Deposition (APCVD)  3.3.1.1 Gas Manifold  3.3.1.2 Si Precursor Delivery System  3.3.1.3 Reactor  3.3.1.4 System Exhaust                                                                                                                                                                                                                      | 52<br>55<br>59                   |

| 3.3.2 Low Pressure Chemical Vapor Deposition (LPCVD)                                                                                                                                                                                                                                                                                                                                   | 63<br>63<br>63                   |

| 3.3.4 Nanowire Growth Process                                                                                                                                                                                                                                                                                                                                                          | 65<br>67                         |

| 3.5 References                                                                                       | 69  |

|------------------------------------------------------------------------------------------------------|-----|

| Chapter 4 Synthesis and Characterization of SiNW Arrays using SiCl <sub>4</sub>                      | 70  |

| 4.1 Introduction                                                                                     | 70  |

| 4.2 Experimental Details                                                                             |     |

| 4.2.1 Silicon Nanowire Growth on Si(111)                                                             |     |

| 4.2.2 Thermodynamic Modeling                                                                         |     |

| 4.2.3 p-type Doping and Electrical Characterization                                                  | 76  |

| 4.3 Results and Discussion                                                                           | 78  |

| 4.3.1 Temperature Dependence                                                                         | 78  |

| 4.3.1.1 Orientation                                                                                  | 79  |

| 4.3.1.2 Growth Rate                                                                                  |     |

| 4.3.2 Silicon Tetrachloride Partial Pressure                                                         |     |

| 4.3.3 Gas Phase Equilibrium Calculations                                                             |     |

| 4.3.4 Carrier Gas Composition                                                                        |     |

| 4.3.5 Growth Rate versus Diameter Dependence                                                         |     |

| 4.3.6 Effect of Inlet Distance and Residence Time                                                    |     |

| 4.4 Structural Properties                                                                            | 101 |

| 4.5 p-type Doping of SiNWs                                                                           |     |

| 4.6 Conclusions                                                                                      |     |

| 4.7 References                                                                                       | 112 |

| Chapter 5 Growth and Electrical Properties of Template Grown Silicon Nanowire Arra  5.1 Introduction |     |

| 5.2 Experimental Details                                                                             | 116 |

| 5.2.1 Free Standing AAO Membranes                                                                    |     |

| 5.2.2 AAO Membranes on Glass                                                                         |     |

| 5.2.3 AAO Aluminum Thread                                                                            |     |

| 5.3 Results                                                                                          | 120 |

| 5.3.1 Electrical Characterization of SiNWs Grown in Free-Standing AAO Membranes                      | 120 |

| 5.3.1.1 Sample Fabrication                                                                           | 121 |

| 5.3.1.2 Electrical Properties                                                                        | 124 |

| 5.3.2 Nanowire Growth on Templated Glass                                                             | 132 |

| 5.3.3 Nanowire Array Growth on Templated Wires                                                       | 135 |

| 5.4 Conclusions                                                                                      | 139 |

| 5.5 References                                                                                       | 140 |

| Chapter 6 Epitaxial Regrowth of n-type Si                                                            | 141 |

| 6.1 Introduction                                                                                     | 141 |

| 6.2 Silicon Substrates                                                                               |     |

| 6.2.1 Sample Types                                                                                   |     |

| 6.2.2 Sample Preparation                                                                             |     |

| 6.2.3 n-type Si Thin Film Development                                                                |     |

| 6.2.3.1 n-type Si Deposition                                                                         |     |

| 6.2.3.2 Sample Characterization                                                                      | 153 |

| 6.2.3.3 Effect of Growth Conditions          | 154 |

|----------------------------------------------|-----|

| 6.2.4 Epitaxial n-type Si Regrowth           | 164 |

| 6.3 n-type Si Deposition on Glass Substrates | 173 |

| 6.3.1 Substrates                             |     |

| 6.3.2 Sample Preparation                     | 173 |

| 6.3.3 n-type Si Regrowth on Templated Glass  |     |

| 6.4 Conclusion                               |     |

| 6.5 References                               | 179 |

| Chapter 7 Thesis Summary and Future Work     | 180 |

| 7.1 Summary                                  | 180 |

| 7.2 Future Work                              | 183 |

| 7.1 References                               |     |

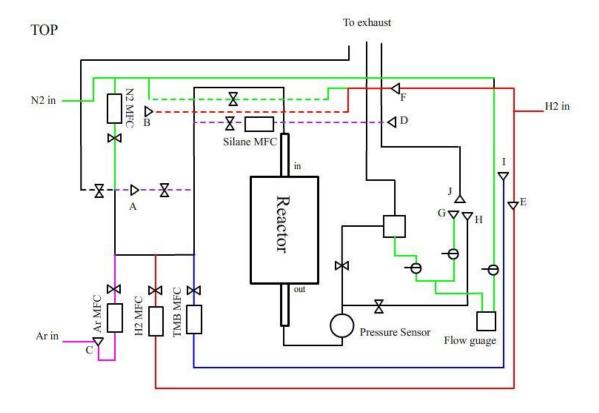

| Appendix Silicon Nanowire System Diagram     | 185 |

# LIST OF FIGURES

| Figure 1-1: The United States energy consumption in 2006                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2: Band diagram of a p-n junction                                                                                                                                                                                                                                                     |

| Figure <b>1-3</b> : Traditional planar solar cell geometry5                                                                                                                                                                                                                                    |

| Figure 1-4: Minority carrier diffusion length plotted versus doping density6                                                                                                                                                                                                                   |

| Figure 1-5: Illustration of parallel multijunction concept with like polarity layers connected in parallel                                                                                                                                                                                     |

| Figure <b>1-6</b> : High aspect ratio silicon solar cell. a.) A SiNW array grown on a Si wafer (left) and a cross-sectional view of the p-n junction (right) and b.) expanded view of a single SiNW showing the direction of carrier collection9                                               |

| Figure 1-7: a.)Schematic of a planar geometry and radial geometry and b.) Modeled current density versus voltage for both planar and radial geometry                                                                                                                                           |

| Figure <b>1-8</b> : a.) Phase diagram of Au-Si. b.) Schematic of VLS mechanism11                                                                                                                                                                                                               |

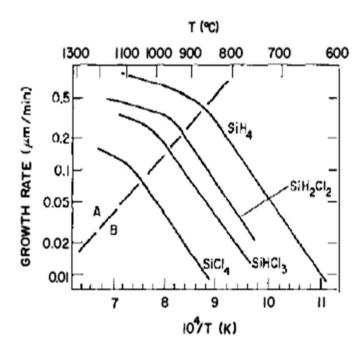

| Figure 2-1: Plot of growth rate vs 1/T for various silicon source gases under atmospheric pressure chemical vapor deposition. Region A represents mass transport limited growth and region B represents kinetically limited growth                                                             |

| Figure <b>2-2</b> : The growth rate of silicon as a function of the input concentration of SiCl <sub>4</sub> for temperatures between 800 and 1000°C                                                                                                                                           |

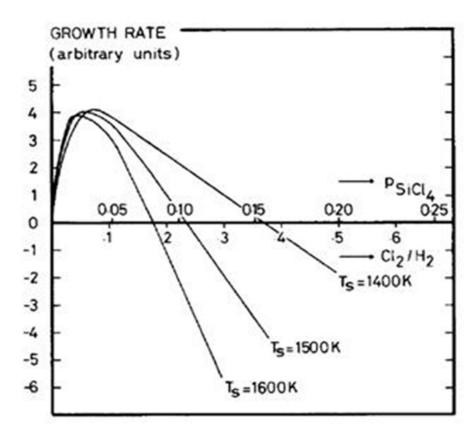

| Figure <b>2-3</b> : Modeled growth/etch curves reported by Van der Putte <i>et al.</i> at different temperatures                                                                                                                                                                               |

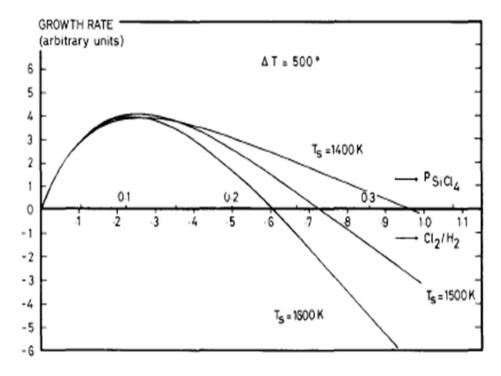

| Figure <b>2-4</b> : Calculated growth/etch curves plotted as a function of the Cl <sub>2</sub> /H <sub>2</sub> in the input gas using the third model proposed by Van der Putte. The curves are calculated at substrate temperatures of 1400-1600K and a temperature gradient of 500 degrees27 |

| Figure <b>2-5</b> : Schematic of vapor-liquid-solid mechanism for SiNW growth30                                                                                                                                                                                                                |

| Figure <b>2-6</b> : Disappearance of faceting upon deposition of recrystallized silicon layer from the liquid droplet                                                                                                                                                                          |

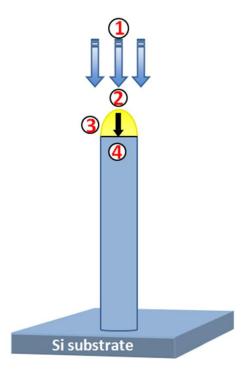

| Figure 2-7: Schematic showing steps of VLS process                                                                                                                                                                                                                                             |

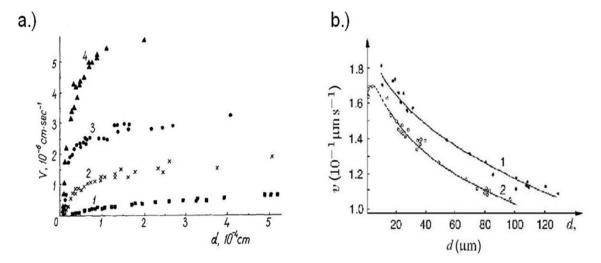

| Figure <b>2-8</b> : Opposing diameter dependencies on the SiNW growth rate (V) by a.)  Givargizov <sup>18</sup> , and b.) Weyher. <sup>29</sup>                                                                                                                                                |

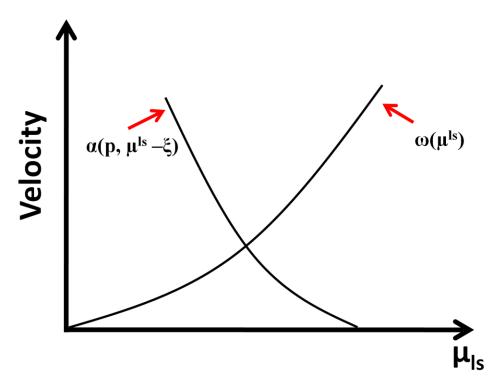

| Figure 2-9: Schematic of the incorporation velocity $\alpha$ and crystallization velocity $\omega(\mu^{ls})$ as a function of the droplet supersaturation $\mu_{ls}$                                                                                                                           |

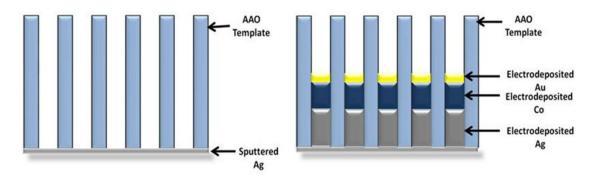

| Figure <b>3-1</b> : Schematic demonstrating the electrodeposition of metals into a free standing AAO membrane                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

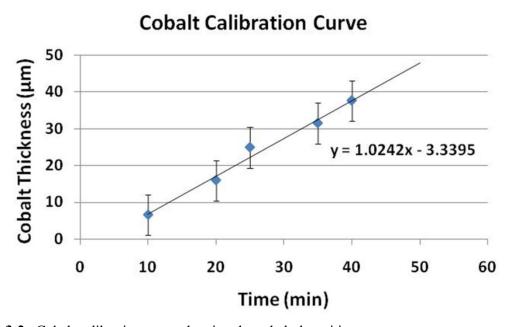

| Figure <b>3-2</b> : Cobalt calibration curve showing the cobalt deposition rate48                                                                                                                                                                                                                                                                                                     |

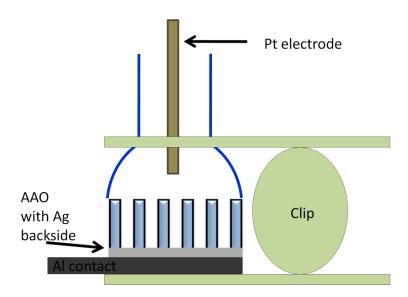

| Figure <b>3-3</b> : A schematic of the electrochemical cell set-up                                                                                                                                                                                                                                                                                                                    |

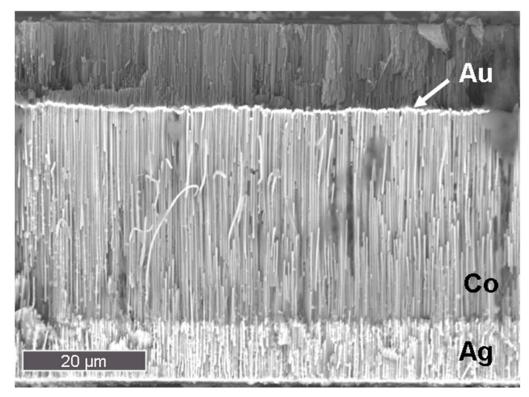

| Figure <b>3-4</b> : SEM cross-section showing the electroplated Ag, Co, and Au inside an AAO template                                                                                                                                                                                                                                                                                 |

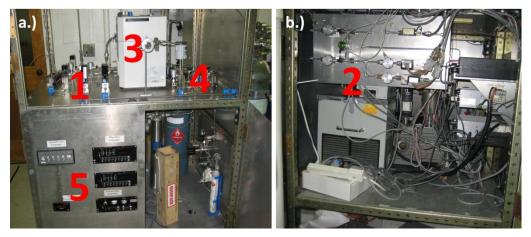

| Figure <b>3-5</b> : Image of the SiCl <sub>4</sub> nanowire system in Room 9 Hosler. The red numbers indicate where each section is located. a.) Front view: 1 Gas Manifold, 3 Reactor, 4 Exhaust, and 5 Control/Safety and b.) Side view: 2 SiCl <sub>4</sub> gas manifold                                                                                                           |

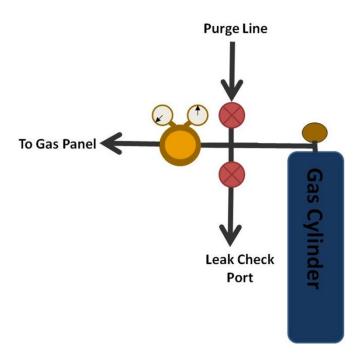

| Figure <b>3-6</b> : Schematic of the gas supply configuration                                                                                                                                                                                                                                                                                                                         |

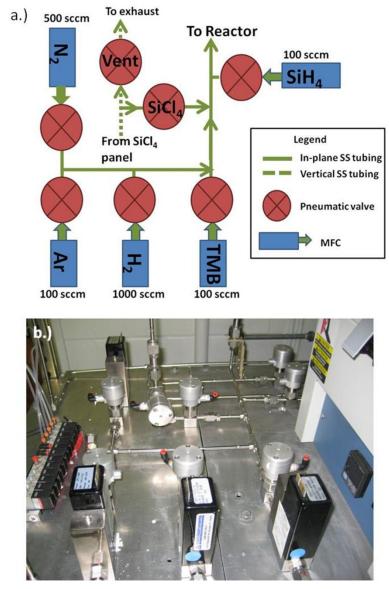

| Figure 3-7: a.) Diagram of the gas manifold showing the layout of the pneumatic valves and mass flow controllers and b.) an image of the completed manifold                                                                                                                                                                                                                           |

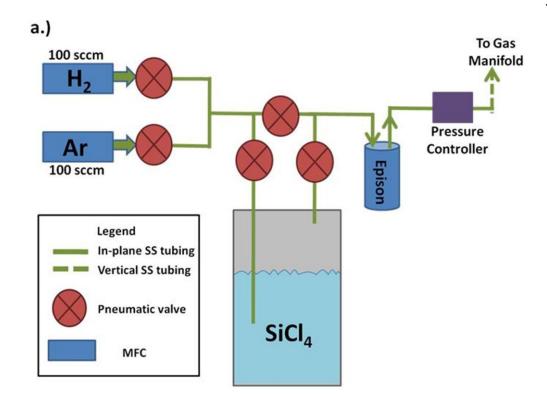

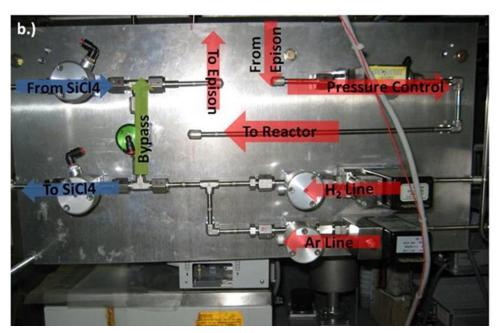

| Figure <b>3-8</b> : a.) Simplified schematic of the SiCl <sub>4</sub> gas manifold. b.) Image of the SiCl <sub>4</sub> manifold, with all of the lines and components labeled by the red arrows. The Epison unit sits behind the panel due to space restrictions in the cabinet                                                                                                       |

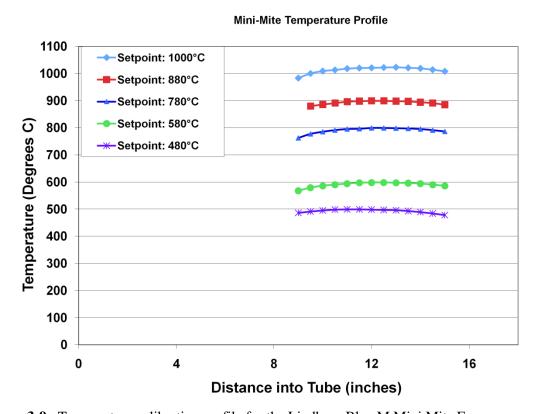

| Figure <b>3-9</b> : Temperature calibration profile for the Lindberg Blue M Mini Mite Furnace60                                                                                                                                                                                                                                                                                       |

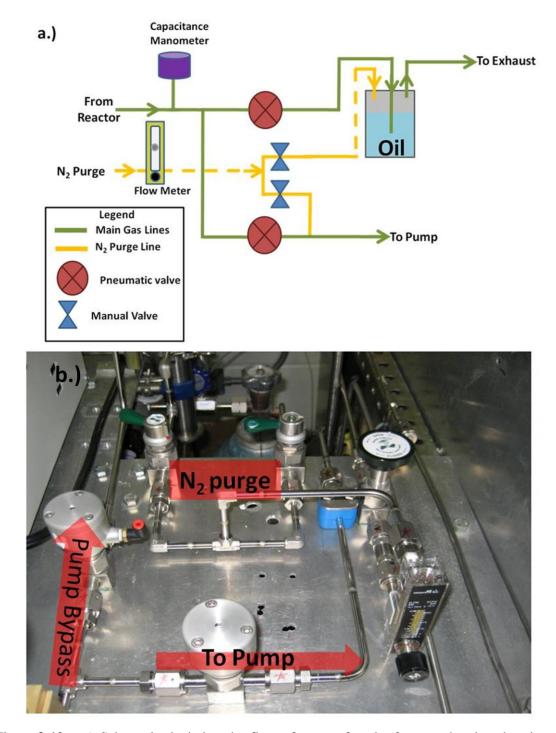

| Figure <b>3-10</b> : a.) Schematic depicting the flow of gases after the furnace showing the nitrogen purge lines and pump bypass. b.) Image of the nanowire system exhaust showing both the exhaust line to atmosphere for SiCl <sub>4</sub> growth and the exhaust line to the pump for SiH <sub>4</sub> growth. There is a N <sub>2</sub> purge line tied into each exhaust line62 |

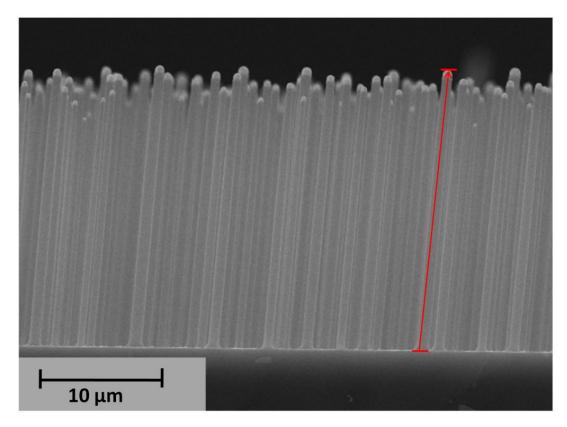

| Figure <b>4-1</b> : Cross-sectional SEM image that depicts a silicon nanowire length measurement. The sample was grown at a temperature of 900 °C                                                                                                                                                                                                                                     |

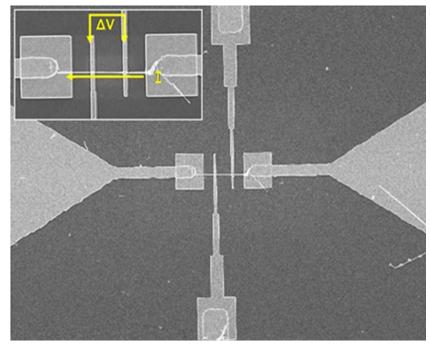

| Figure <b>4-2</b> : FESEM image of the four-point resistivity electrical testbed                                                                                                                                                                                                                                                                                                      |

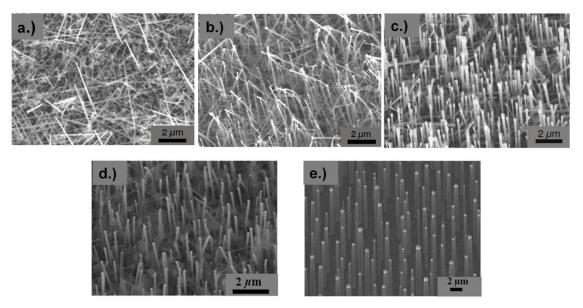

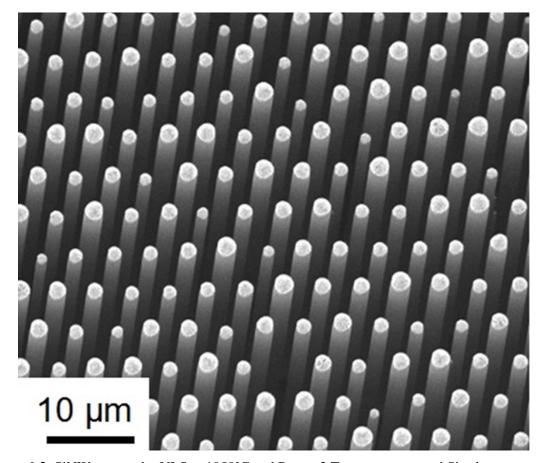

| Figure <b>4-3</b> : FESEM images tilted 15 ° to show the orientation of the nanowires with respect to the Si (111) substrate at a.) 800°C b.) 850°C c.) 900°C d.) 950°C and e.) 1050 °C.                                                                                                                                                                                              |

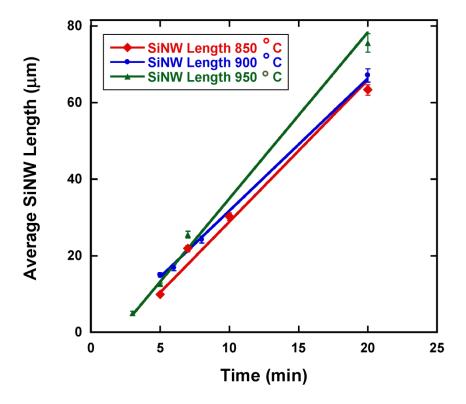

| Figure 4-4:Graph of average SiNW length versus time for different temperatures81                                                                                                                                                                                                                                                                                                      |

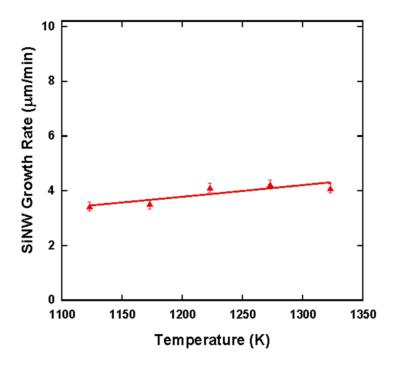

| Figure <b>4-5</b> : Plot of silicon nanowire growth rate versus temperature between 800-1100°C fit using the power law (T) <sup>n</sup>                                                                                                                                                                                                                                               |

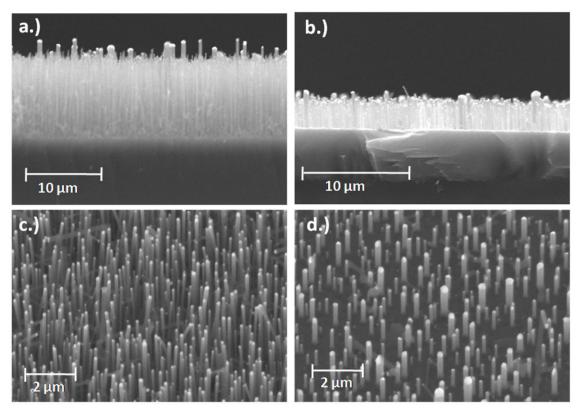

| Figure <b>4-6</b> :Cross-sectional and plan view FESEM images of SiNW arrays grown at $950^{\circ}$ C, and atmospheric pressure a.)/c.) grown at $P_{SiCl4} = 4.5$ Torr and b.)/d.) grown at $P_{SiCl4} = 14$ Torr.                                                                                                                                                                   |

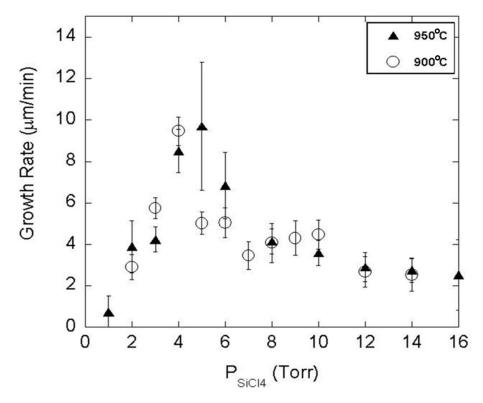

| Figure <b>4-7</b> : Growth rate versus P <sub>SiCl4</sub> for 100% H <sub>2</sub> at different temperatures86                                                                                                                                                                                                                                                                         |

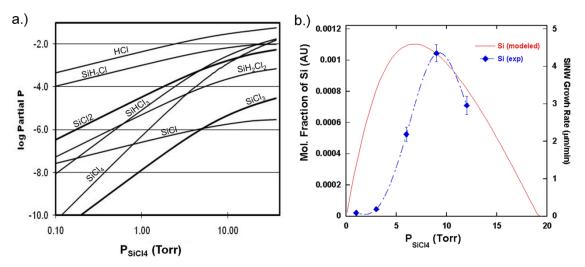

| Figure 4-8: a.)Gas phase species thermodynamically modeled using HSC chemistry and b.)Comparison of model predictions and SiNW growth rate at 1050°C 100% H <sub>2</sub> (0.5 step)                                                                                                                                                                                                    | .87  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

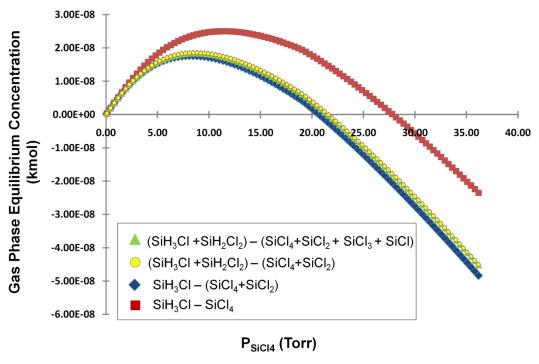

| Figure 4-9: The difference between the $SiH_xCl_y$ and $SiCl_x$ gas phase equilibrium concentrations for increasing $P_{SiCl4}$ .                                                                                                                                                                                                                                                      | .89  |

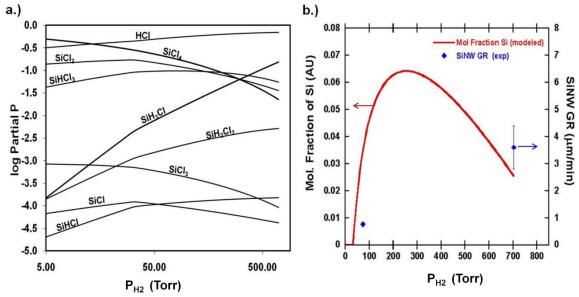

| Figure <b>4-10</b> : a.) Gas phase species thermodynamically modeled using HSC chemistry for increasing $P_{\rm H2}$ at a steady $P_{\rm SiCl4}$ . b.) Comparison of model predictions and SiNW growth rate.                                                                                                                                                                           | .90  |

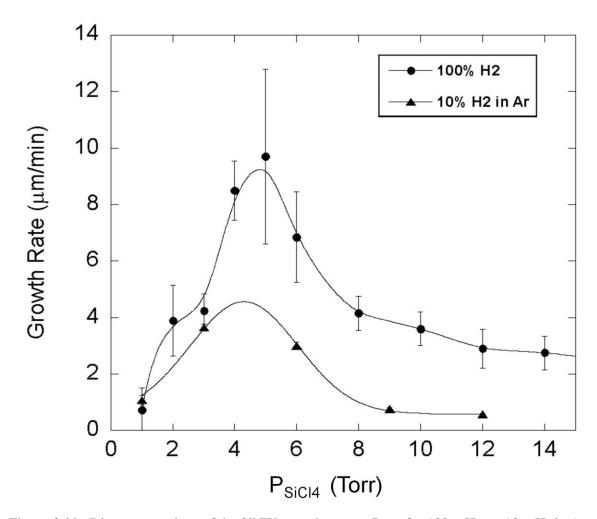

| Figure <b>4-11</b> : Direct comparison of the SiNW growth rate vs. $P_{SiCl4}$ for 100% $H_2$ vs. 10% $H_2$ in Ar carrier gas for SiNW arrays grown at atmospheric pressure, and 950 °C                                                                                                                                                                                                | .92  |

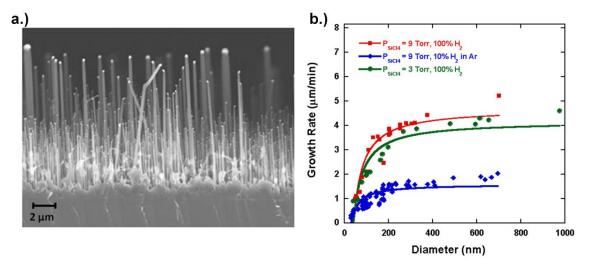

| Figure <b>4-12</b> : a.) Cross-sectional FESEM image of a SiNW array grown using 10 % $H_2$ in Ar at 950 °C and atmospheric pressure showing diameter dependence to the growth rate. b.) SiNW growth rate vs. SiNW diameter for a low $P_{\text{SiCl4}} = 3$ Torr and high $P_{\text{SiCl4}} = 9$ Torr using 100 % $H_2$ and a high $P_{\text{SiCl4}} = 9$ Torr using 10 % $H_2$ in Ar | .93  |

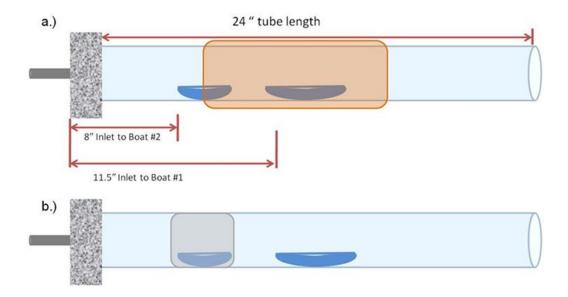

| Figure <b>4-13</b> : Schematic showing a.) the location of the quartz boats during the experiments in reference to the hotzone and b.) the location of where the Si tube deposits were located in reference to the boats and gas inlet                                                                                                                                                 | .96  |

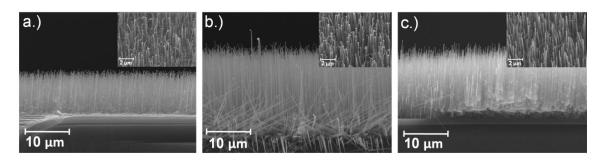

| Figure <b>4-14</b> : SEM micrographs showing both a cross-section and top down (inset) of a.) sample A closest to the inlet b.) sample B and c.) sample C. Samples were grown at $950^{\circ}$ C, total flow of $100$ sccm, and $P_{SiCl4}$ =3.6 Torr                                                                                                                                  | .97  |

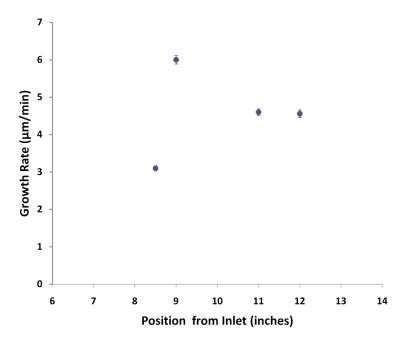

| Figure <b>4-15</b> : Growth rate versus position from gas inlet showing an increase then decrease in nanowire growth rate with respect to position in the tube during growth                                                                                                                                                                                                           | .98  |

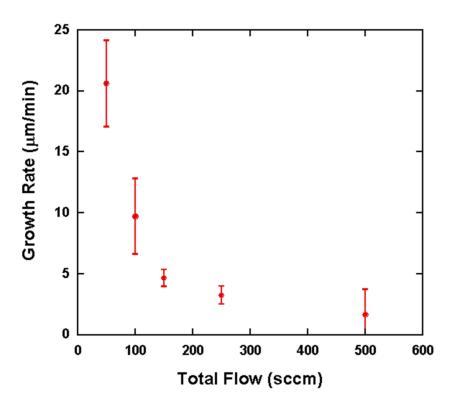

| Figure <b>4-16</b> : Graph of SiNW growth rate versus total gas flow at 950°C.                                                                                                                                                                                                                                                                                                         | .99  |

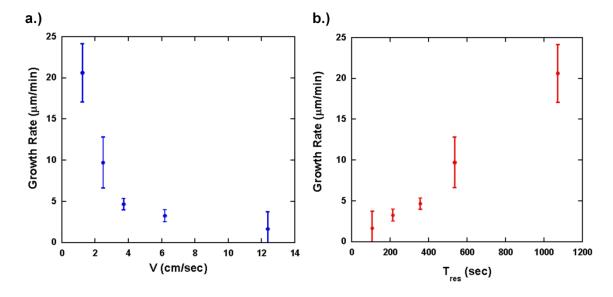

| Figure <b>4-17</b> : Graph of growth rate obtained at 950°C versus a.) gas velocity ( $v_{gas}$ ) and b.) residence time ( $t_{res}$ )                                                                                                                                                                                                                                                 | .101 |

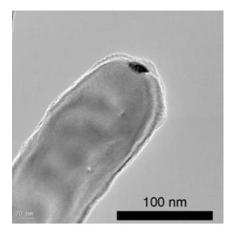

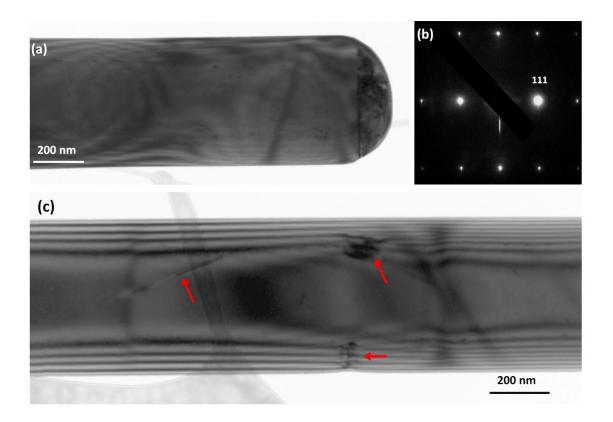

| Figure <b>4-18</b> : TEM image by Dr. Bangzhi Liu of a typical SiNW tip grown using a $P_{SiCl4} = 3$ Torr at 900°C in 100 % $H_2$ carrier gas.                                                                                                                                                                                                                                        | .102 |

| Figure <b>4-19</b> : FESEM images of SiNWS after a slow cooldown (a.) and a fast cooldown (b.).                                                                                                                                                                                                                                                                                        | .103 |

| Figure 4-20: TEM images obtained by Haoting Shen showing a.) SiNW tip and middle of nanowire and b.) the base of a SiNW for a $P_{SiCl4} = 3$ Torr with 100% $H_2$                                                                                                                                                                                                                     | .104 |

| Figure <b>4-21</b> : TEM image of a SiNW tip grown using 100 % $H_2$ at 950 °C and a $P_{SiCl4} = 10$ Torr obtained by Haoting Shen.                                                                                                                                                                                                                                                   | .105 |

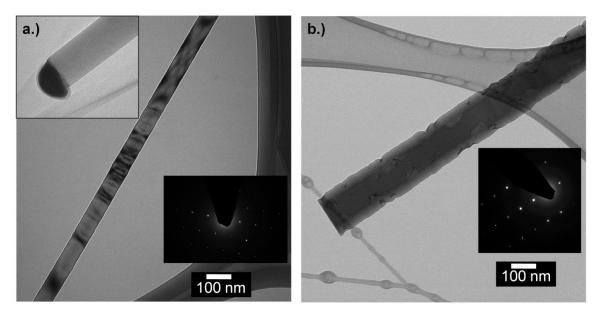

| Figure 4-22: TEM images of SiNWs grown at $10\%$ H <sub>2</sub> in Ar and a low $P_{SiCl4} = 3$ Torr at a.) low magnification showing the entire wire and high magnification of the tip, middle and base of the nanowire. Image b.) shows a low magnification of a SiNW grown at $10\%$ H <sub>2</sub> in Ar at a high $P_{SiCl4} = 9$ Torr at $950$ °C with a high magnification of the tip, middle and nanowire base. Images were taken by Haoting Shen | .106 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure <b>4-23</b> : Gated I-V measurements of undoped SiCl <sub>4</sub> grown SiNWs indicating p-type behavior                                                                                                                                                                                                                                                                                                                                           | .108 |

| Figure <b>4-24</b> : Plot showing change in growth rate with respect to the TMB/SiCl <sub>4</sub> doping ratio                                                                                                                                                                                                                                                                                                                                            | .109 |

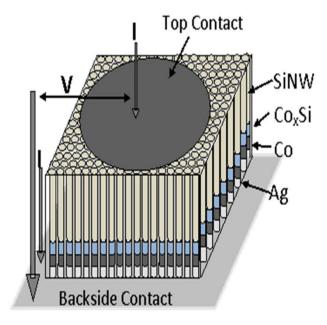

| Figure 5-1: Schematic of a silicon nanowire array on AAO coated glass substrate                                                                                                                                                                                                                                                                                                                                                                           | .115 |

| Figure <b>5-2</b> : a.) Device architecture detail, showing the Al core, p-type SiNWs growing through the insulating AAO and then coated with a continuous n-type Si layer which is then covered with an outer transparent conductive coating. b.) Complete schematic of a PV wire device showing silicon nanowires distributed about the aluminum core with a protective polymer coating.                                                                | .116 |

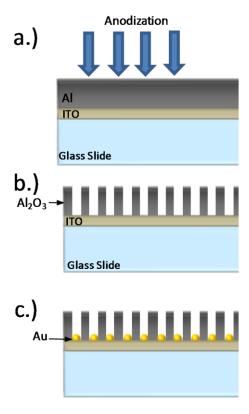

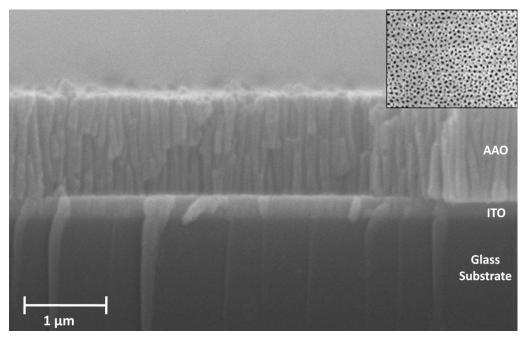

| Figure 5-3: Schematic of substrate fabrication process a.) anodic oxidation of Al thin film on an ITO layer on glass b.) AAO membrane is formed on the ITO layer through anodization, and c.) Au is electrodeposited into the pores                                                                                                                                                                                                                       | .118 |

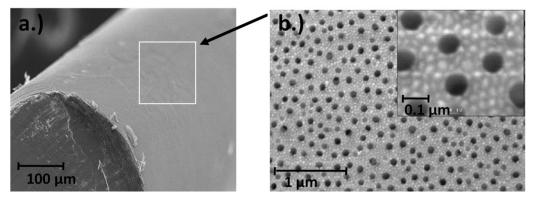

| Figure <b>5-4</b> : AAO Membrane on glass slide side view of the structure showing the glass slide with the AAO membrane on top. Inset picture shows top-down view of AAO membrane                                                                                                                                                                                                                                                                        | .119 |

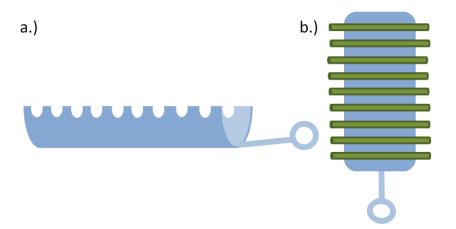

| Figure <b>5-5</b> : Schematic of the boat design both a.) side view and b.) top down view. This is required to obtain even nanowire growth in a complete 360 degrees around the aluminum wire substrates.                                                                                                                                                                                                                                                 | .120 |

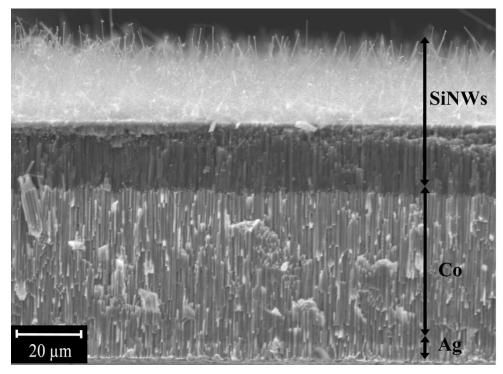

| Figure <b>5-6</b> : Cross-sectional SEM image of sample after electrodeposition and nanowire growth.                                                                                                                                                                                                                                                                                                                                                      | .122 |

| Figure 5-7: Schematic of SiNW array sample and two point electrical measurement configuration.                                                                                                                                                                                                                                                                                                                                                            | .123 |

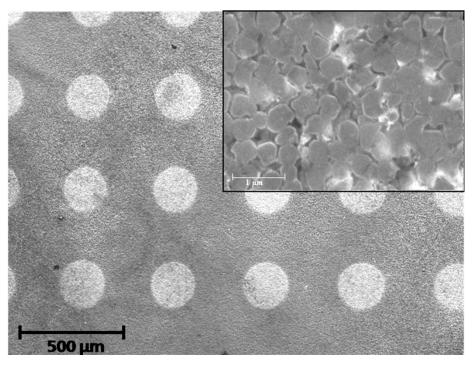

| Figure <b>5-8</b> : SEM micrograph showing polished membrane surface with an array of top contacts. Inset shows polished membrane surface before contact deposition                                                                                                                                                                                                                                                                                       | .124 |

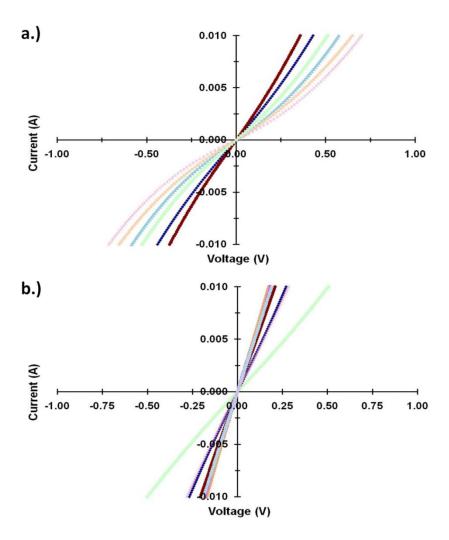

| Figure <b>5-9</b> : I-V curves for a p-type (TMB/SiH <sub>4</sub> =2x10 <sup>-3</sup> ) SiNW array both a.) before annealing and b.) after annealing                                                                                                                                                                                                                                                                                                      | .125 |

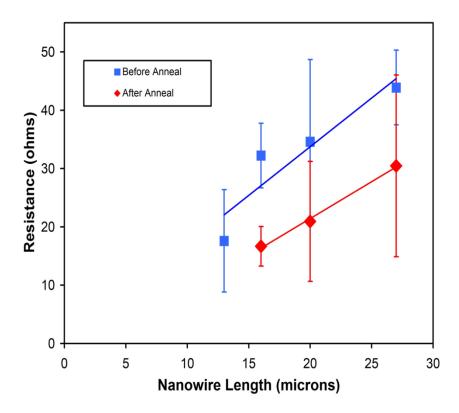

| Figure <b>5-10</b> : Total resistance versus nanowire length for the SiNW arrays sample grown with TMB/SiH <sub>4</sub> =4x10 <sup>-3</sup> before and after annealing.                                                                                                                                                                                                                                                                                   | .126 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

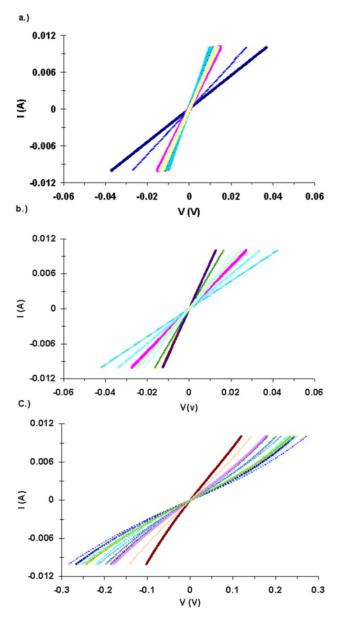

| Figu | are <b>5-11</b> : Representative I-V curves of SiNW array samples after annealing. Each I-V curve represents data obtained from different circular top contacts measured on the same sample. (a) $18\mu m \log SiNWs$ , $TMB/SiH_4=2x10^{-2}$ (b) $13\mu m \log SiNWs$ , $PH_3/SiH_4=2x10^{-5}$ and (c) $16\mu m \log SiNWs$ , undoped sample | .127 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figu | are <b>5-12</b> : The total resistance - nanowire contact area product ( $R_TNA$ ) versus silicon nanowire length for intentionally doped and nominally undoped SiNW arrays grown with varying dopant/SiH <sub>4</sub> ratios.                                                                                                                | .128 |

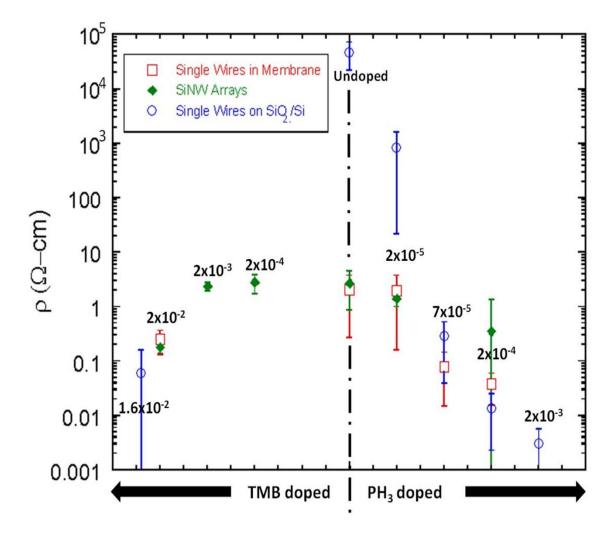

| Figu | re <b>5-13</b> : Plot of resistivity versus dopant/SiH <sub>4</sub> ratio comparing the results obtained from the nanowire array measurements to those obtained from four-point resistance measurements of individual SiNWs grown out of an alumina membrane <sup>15,16</sup> and on oxidized Si substrates.                                  | .131 |

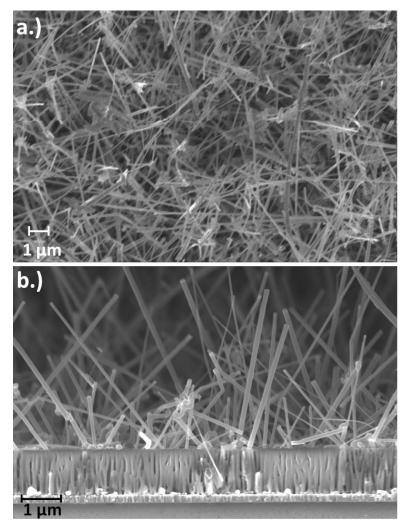

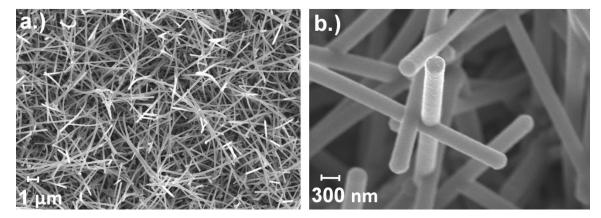

| Figu | b.) Side view of the p-type SiNW growth on AAO membrane on glass. In both images the Au tips were removed using GE 1848 Au etchant                                                                                                                                                                                                            | .134 |

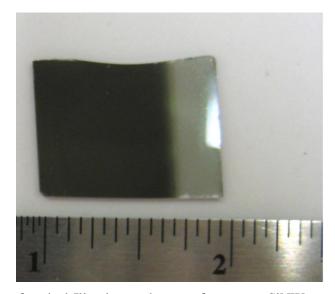

| Figu | brown area is where the SiNWs have been grown                                                                                                                                                                                                                                                                                                 | .135 |

| Figu | are <b>5-16</b> : SEM images of a.) a templated aluminum wire substrate and b.) higher magnification showing the AAO pores. Image courtesy of Illuminex Corporation                                                                                                                                                                           | .136 |

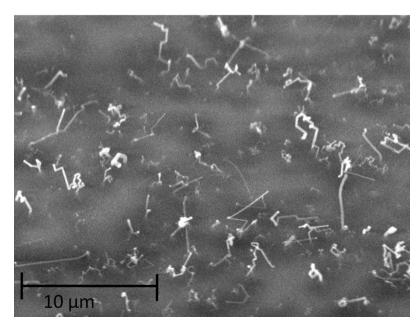

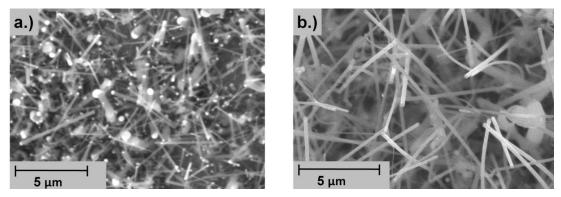

| Figu | are <b>5-17</b> : SEM image of the templated wire surface after nanowire growth at 500 $^{\circ}$ C, $P_{SiH4} = 0.65$ Torr and a system pressure of 13 Torr                                                                                                                                                                                  | .137 |

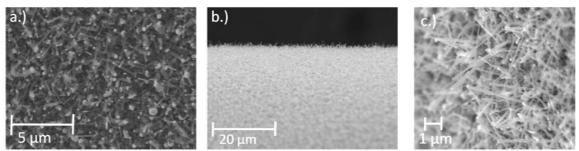

| Figu | top down b.) low magnification image showing surface curvature and c.) Side view showing high wire density.                                                                                                                                                                                                                                   | .139 |

| Figu | are <b>6-1</b> : SiNW arrays grown from a Au thin film on Si(111) and used for n-type Si regrowth experiments.                                                                                                                                                                                                                                | .143 |

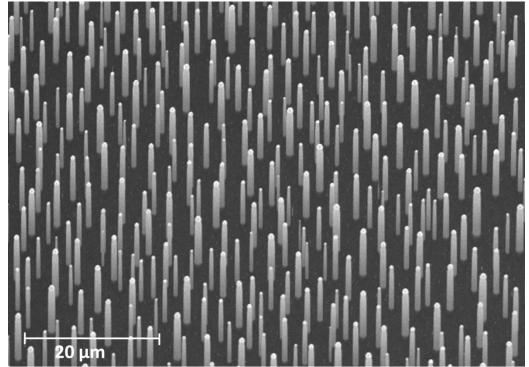

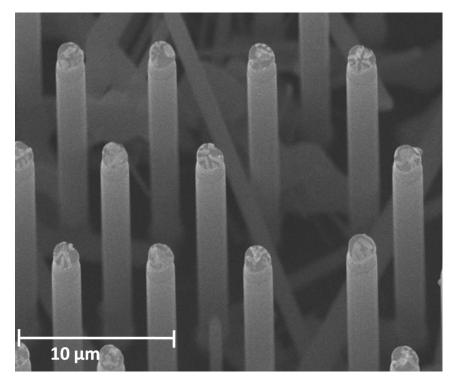

| Figu | are <b>6-2</b> : SiNWs grown by VLS at 1050 °C and P <sub>SiCl4</sub> = 3 Torr on a patterned Si substrate.                                                                                                                                                                                                                                   | .144 |

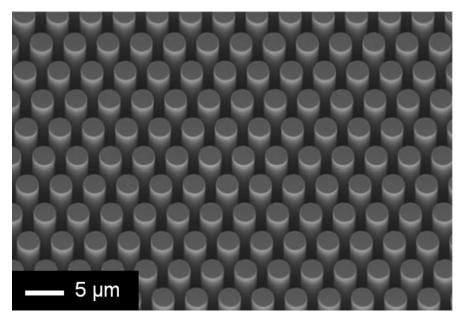

| Figu | re 6-3: FESEM image showing etched Si pillars                                                                                                                                                                                                                                                                                                 | .145 |

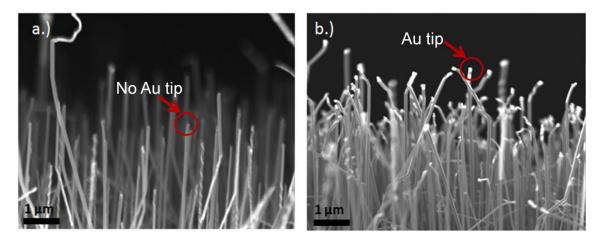

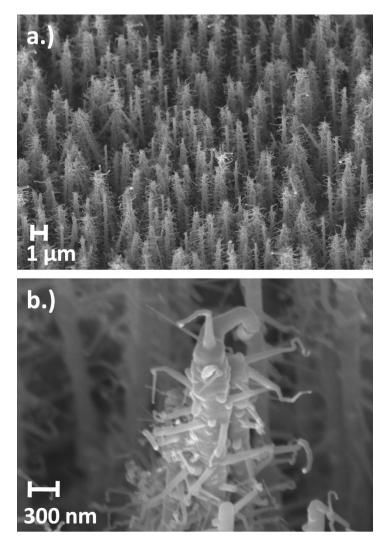

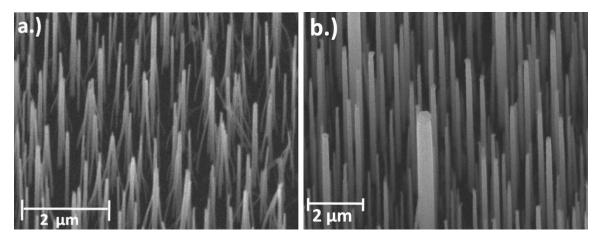

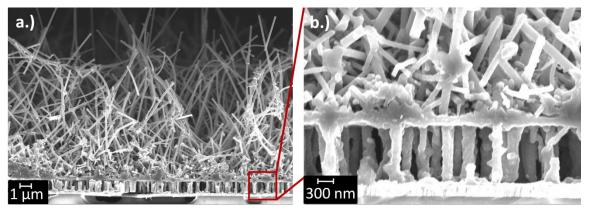

| Figu | are <b>6-4</b> : FESEM image of a.) a "nanoforest" caused by trying to epitaxially regrow SiNWs without removing the Au tip and b.) a higher magnification image showing the many branches growing from a single nanowire                                                                                                                     | .147 |

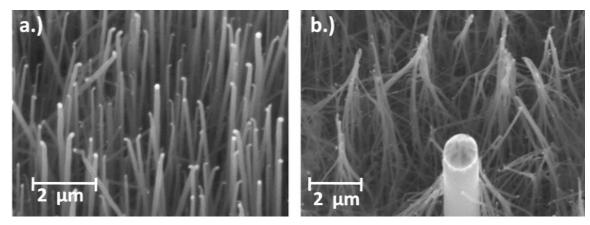

| Figu | are <b>6-5</b> : SEM image showing the free-standing SiNW samples grown using SiCl <sub>4</sub> both a.) before and b.) after the Au etching process                                                                                                                                                                                          | .148 |

| Figu | are <b>6-6</b> : SEM micrographs showing Au tip removal and sample drying in a.) hexane                                                                                                                                                                                                                                                       | 149  |

| Figure 6-7: Patterned SiNWs on Si(111) after a 30 minute Au etch                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

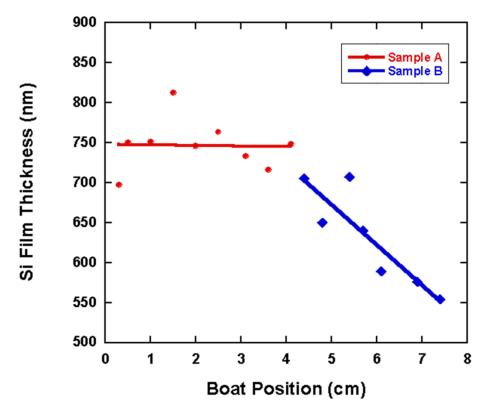

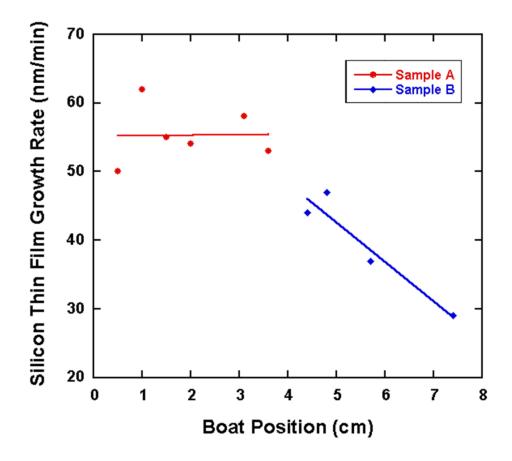

| Figure <b>6-8</b> : Initial undoped Si thin film growth at 650 °C and a pressure of 10 Torr on sapphire, where sample A was placed in front of quartz boat and sample B placed towards the back of the boat                                                                                                                                                                                                                                            |

| Figure <b>6-9</b> : Initial undoped Si thin film growth rate versus boat position at 850 °C and a pressure of 3 Torr on sapphire, where sample A was placed in front of quartz boat and sample B placed towards the back of the boat                                                                                                                                                                                                                   |

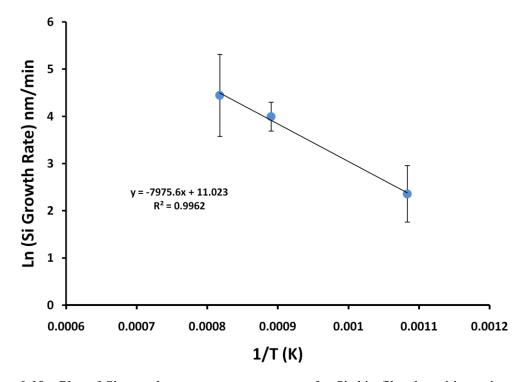

| Figure <b>6-10</b> : Plot of Si growth rate versus temperature for Si thin film deposition using a flow rate of 50 sccm SiH <sub>4</sub> , total flow of 100 sccm, and a pressure of 3 Torr157                                                                                                                                                                                                                                                         |

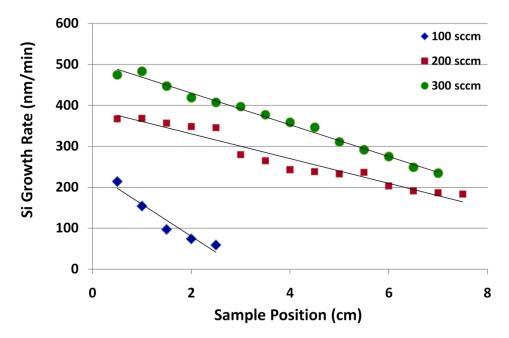

| Figure <b>6-11</b> : Plot of Si thin film growth rate versus sample position at 950 °C for different total flow rates                                                                                                                                                                                                                                                                                                                                  |

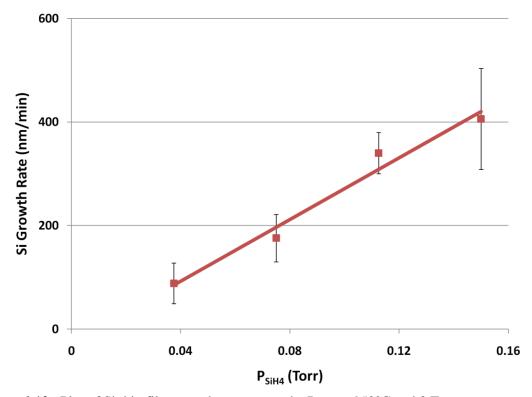

| Figure <b>6-12</b> : Plot of Si thin film growth rate versus the P <sub>SiH4</sub> at 950 °C and 3 Torr159                                                                                                                                                                                                                                                                                                                                             |

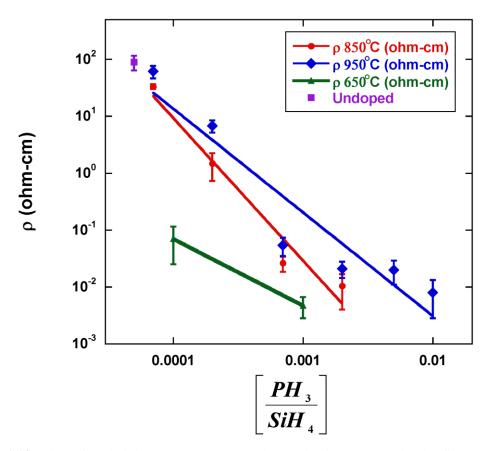

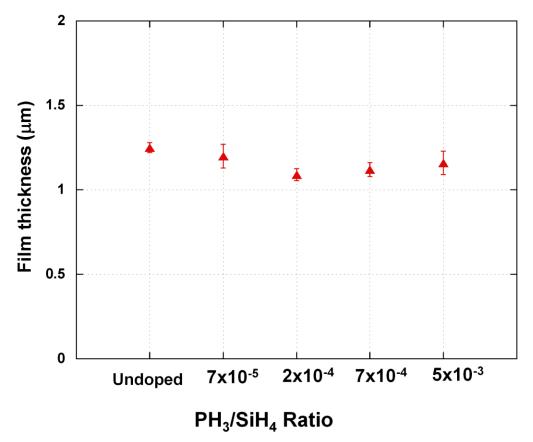

| Figure <b>6-13</b> : Plot of resistivity versus the PH <sub>3</sub> /SiH <sub>4</sub> ratio for n-type Si thin films grown on sapphire at 650, 850 and 950 °C. The undoped Si thin film was grown at 950 °C also162                                                                                                                                                                                                                                    |

| Figure <b>6-14</b> : Plot of Si thin film thickness versus PH <sub>3</sub> /SiH <sub>4</sub> ratio                                                                                                                                                                                                                                                                                                                                                     |

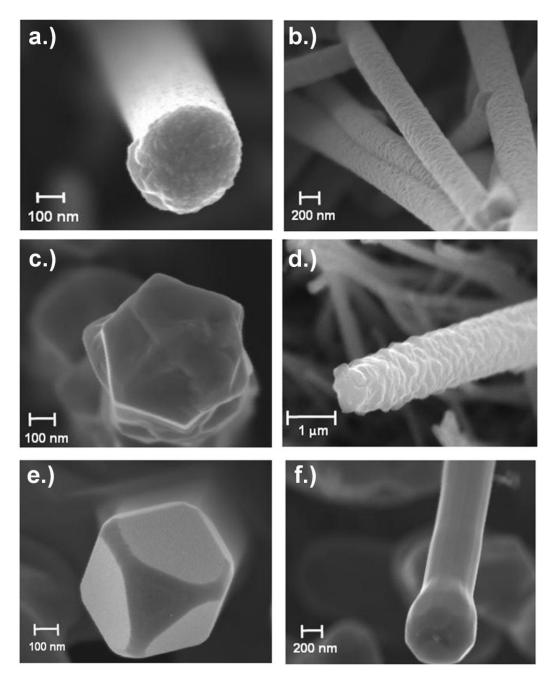

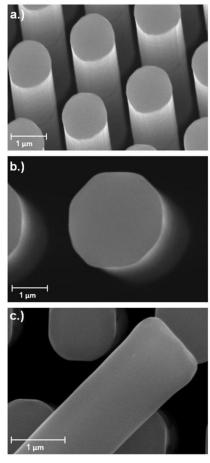

| Figure <b>6-15</b> : FESEM images of the n-type Si deposition at a temperature of (a & b) 650°C, (c & d) 850°C and (e & f) 950°C showing both the tip of the nanowire and also a side view                                                                                                                                                                                                                                                             |

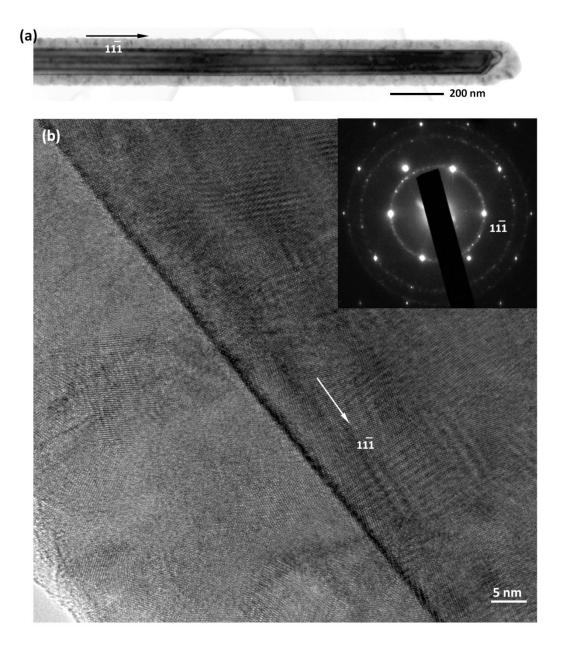

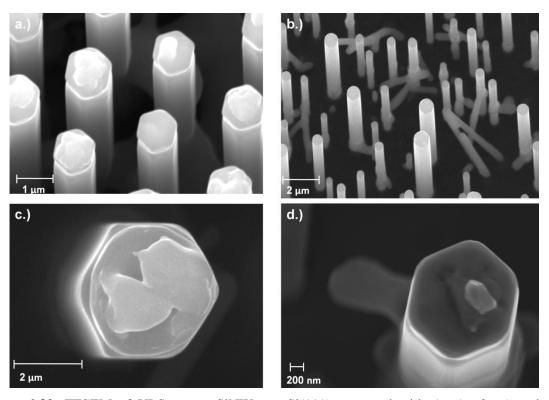

| Figure <b>6-16</b> : (a)Low-magnification bright-field TEM image of a 650°C core/shell Si NW. The shell is polycrystalline as indicated by the diffraction pattern shown in the inset of (b). High-resolution TEM shown in (b) indicates that the core/shell interface sharp                                                                                                                                                                           |

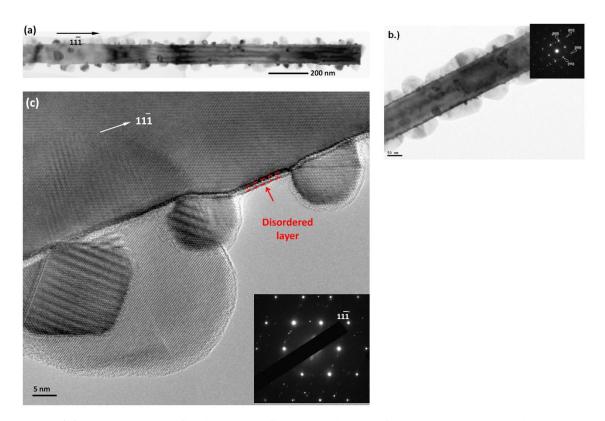

| Figure <b>6-17</b> : (a)Low-magnification bright-field TEM image of an 850°C core/shell Si NW. The shell is polycrystalline as indicated by the diffraction pattern shown in the inset of (c). The 850°C shell layer is discontinuous and consists of nanometer scale Si islands. (b) Low magnification image of a different sample, also grown at 850°C. High-resolution TEM shown in (c) reveals a thin disordered layer at the core/shell interface |

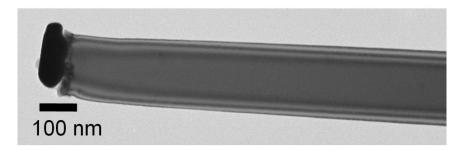

| Figure <b>6-18</b> : (a) On zone axis bright-field TEM image of a core/shell Si nanowire collected near the top of the wire. (b) is the corresponding SAD pattern collected from the nanowire body. (c) Nanometer-scale black dots are often observed within the nanowires, that are likely defects                                                                                                                                                    |

| Figure <b>6-19</b> : SEM images of the etched Si pillars after radial n-type Si deposition showing the a.) pillar array at a 15 degree tilt, b.) plan view and c.) plan view of a pillar that had fallen over showing the pillar sidewall                                                                                                                                                                                                              |

| Figure <b>6-20</b> : FESEM of VLS grown SiNWs on Si(111) patterned with Au (a. & c.) and on Si(111) with a Au thin film (b. & d.) coated radially with n-type Si                                                     | .172 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure <b>6-21</b> : SEM images before (a) and after (b) the Au tips were removed from the SiNWs grown on AAO coated glass substrates                                                                                | .174 |

| Figure <b>6-22</b> : (a) Low magnification and (b) high magnification FESEM images of sample cross-section after Au etch, HF dip and n-type Si thin film coating showing evidence of HF etching of the AAO membrane. | .175 |

| Figure <b>6-23</b> : (a) Low magnification and (b) high magnification FE-SEM images of radial p-n Si nanowires after n-type Si shell coating.                                                                        | .176 |

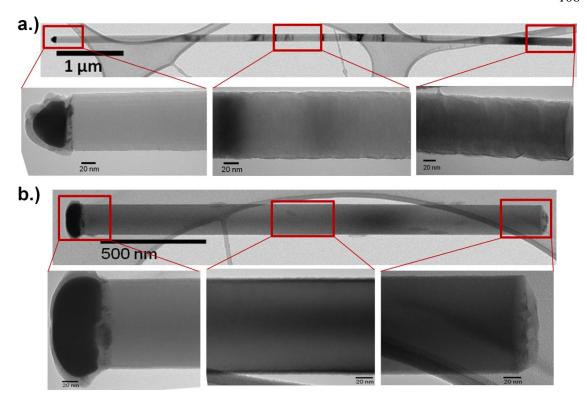

| Figure <b>6-24</b> : (a) Low magnification TEM image of radial p-n Si nanowire. (b) High magnification TEM image of radial p-n Si nanowire showing crystalline p-Si core and polycrystalline n-Si shell layer.       | .177 |

# LIST OF TABLES

| Table <b>3-1</b> : Lists the typical substrates used for silicon nanowire growth and their conditions for nanowire growth                                      | 66  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table <b>4-1</b> : Table showing the SiNW growth rates and incubation times for different growth temperatures.                                                 | 82  |

| Table <b>5-1</b> : The template wire sample and growth conditions for AAO templated Al wires.                                                                  | 138 |

| Table <b>6-1</b> : The growth rate and growth conditions that were found to be optimal for specific growth temperatures.                                       | 160 |

| Table <b>6-2</b> : A comparison of the carrier type and resistivity measurements from both 4-point probe and also Hall measurements at a.) 850°C and b.) 950°C | 161 |

## **ACKNOWLEDGEMENTS**

I would first like to express my gratitude to Dr. Joan Redwing first for giving me a job as an undergraduate and second for being willing to serve as my thesis advisor. I appreciate all that I have learned about CVD and nanowire growth. There are a few people who have also contributed to this research, and without them this project would not be complete. I would like to thank Rebeca Diaz for the initial single nanowire resistivity measurements and also Dr. Qi Zhang, Dr. Bangzhi Liu, Haoting Shen, and finally Dr. Xiaojun Weng for all of their help with TEM questions and also for the beautiful images they took.

Special thanks to Dave Snyder, Bill Everson and Randy Cavalero for giving some random high school kid a summer position working on SiC, without you guys I never would have known how much I love crystal growth and materials! I truly respect and admire you guys! Dave, thanks for pointing out what a good school PSU was! Randy, what can I say but thank you for finally leaving the door unlocked and all of the things you taught me, it truly helped in the lab!

Many thanks to the Redwing and Mohney groups both past and present members for all of their help and support. I have learned so much from all of our technical discussions! I would especially like to thank Ian for letting me borrow books from his "library", you always had the reference I needed! I would also like to extend my special thanks to Mary, Dan, Brian, and Dave for the soda breaks, running for pancakes, and also everyone who has been part of our rock band without them grad school would not have been as much fun. Dave and Erin, I do not know how to thank the both of you. I have been so lucky to have you both as friends. Dave you were a great officemate. I have learned so much from you both, and I look forward to continuing our friendship for years to come!

I would like to extend a special thank you to my family (Tom, Joan, Adam, Wayne, Elaine, Chris and Erin) and friends for all of their love and patience the past year while we have tried to finish up. Adam your visits to my office have kept life interesting and entertaining, I only hope to repay the favor someday.

Finally, to my wonderful husband, Chad, you have been my rock and can always make any day better. Thank you for all of your help scientifically but most of all thank you for all of your love and support, without you I never would have made it this far. *Armor Vincit Omnia*.

# Chapter 1

# Introduction

## 1.1 Motivation

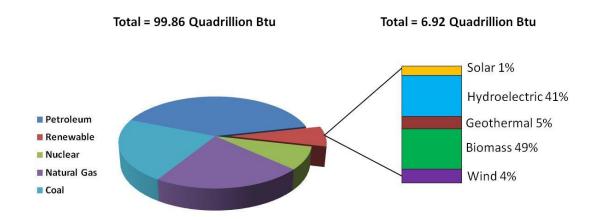

The demand for energy has risen sharply over the past decade. World energy consumption increased 2.4% in 2007<sup>1</sup>. Much of the energy comes from fossil fuels such as oil, coal or natural gas. Fossil fuels will be unable to indefinitely sustain the need for energy and also contribute to pollution through CO<sub>2</sub> emissions. As the world energy consumption increases, the cost of oil, natural gas, and coal will only increase. It has become clear the world needs to find sustainable, clean energy resources. This has propelled the drive towards renewable energy. In 2006, total renewable energy consumption increased (Figure 1-1). However, the use of renewable energy still pales in comparison to the fossil fuel usage<sup>2</sup>. Potential renewable energy sources include water, wind and sunlight. However, with energy costs rising and fossil fuels still being most heavily used, there is more of an incentive to create cleaner and cheaper ways of producing energy using these abundant resources.

Figure 1-1: The United States energy consumption in 2006.<sup>2</sup>

While sunlight is currently only being used for approximately 1% of the nation's renewable energy, it is the most abundant renewable energy resource and hits the earth with 174 petawatts of solar radiation per day. Nearly 1/3 of this gets reflected back into space but the rest comes back to earth. If all of that solar radiation were harnessed into energy, it would be double the energy of all of the earth's non-renewable (oil, natural gas, coal, uranium) resources.<sup>3</sup>

Conversion of sunlight into energy holds great promise not only for solar cells but other photovoltaic devices. This includes traditional solar cells and photoelectrochemical devices that use the sun for H<sub>2</sub> generation via water splitting. Currently, it is expensive to produce a high efficiency solar cell thus making it less appealing for consumers to use solar cells for a main source of energy. Solar cells have been around for many years but in the past decade sales have increased by 30%. This is mostly due both technological advancements combined with government and economic policies. Currently 94% of the market is dominated by silicon

photovoltaic devices including amorphous, single and polycrystalline material. Semiconductor materials are often used for both photovoltaics and photoelectrochemical cells. This is because they have bandgap energies in a range where they can convert light into energy. Silicon is widely used due to its natural abundance, its nearly ideal bandgap of  $1.1 \text{eV}^5$ , and the existing infrastructure and technology associated with the semiconductor electronics.<sup>6</sup>

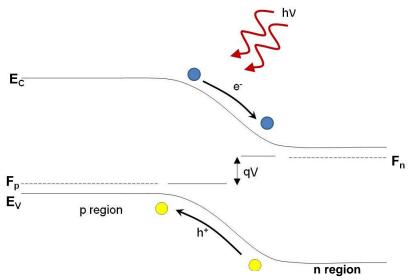

## 1.2 Silicon Photovoltaics

A typical solar cell structure consists of a junction between a n-type and p-type semiconductor<sup>7</sup>. Photons greater than the band gap are absorbed by the semiconductor. The absorption activates electron transitions from the valence band to the conduction band to generate electron-hole pairs. The carriers that diffuse into the depletion region before they recombine can be separated by the applied electric field. At the p-n junction, the electrons are swept towards the n-type side while the holes are swept towards the p-type sides thus generating a photovoltage  $(V_{OC})$  as shown in Figure 1-2. Recombination of the electron-hole pairs that are generated can lead to reduced efficiency. Recombination depends on the presence of recombination centers or carrier traps and the minority carrier diffusion length (L), which is the average distance a carrier can move from the point of generation until it recombines.

Figure 1-2: Band diagram of a p-n junction.

In solar cell devices, the photogenerated of carriers can then be collected to an external circuit and used to power devices. A photovoltage used in conjunction with an electrolyzer can drive the chemical reaction to split water and thereby produce clean  $H_2$ .<sup>8</sup> This would be advantageous for hydrogen production and use in applications such as fuel cells. The current problems associated with these photovoltaic devices and also solar cells is the need for increased efficiency and reduced cost to make these types of devices and their applications economically viable.

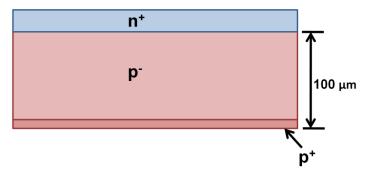

The theoretical efficiency of a single material solar cell is 31% and in operation a single crystal Si solar cell can currently reach 16-20% efficiency.<sup>4</sup> However, this can only be achieved at a high cost, which makes it less economically viable. This is because single crystal Si must be high purity to achieve long minority carrier diffusion lengths. A typical planar solar cell is shown in Figure 1-3 below.

Figure 1-3: Traditional planar solar cell geometry.

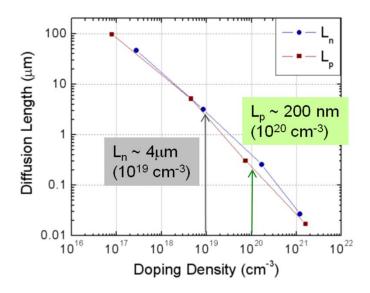

The silicon must be  $\geq 100~\mu m$  to absorb the majority of solar radiation. However, the minority carriers must be able to diffuse comparable lengths without recombining so the minority carrier diffusion length needs to be large, in order for collection efficiencies to be high. If the minority carrier diffusion length is short, the minority carriers could recombine before they are collected. The minority carrier diffusion length varies with doping level and a plot of L versus the doping for silicon is shown in Figure 1-4 below. This is calculated using the equation for minority carrier diffusion length (L)<sup>9</sup>:

$$L = \sqrt{D\tau} \tag{1.1}$$

where D is the diffusivity, and  $\tau$  is the carrier lifetime. The lifetime is determined by  $^9$ :

$$\tau = \frac{1}{R_{ec} N} \tag{1.2}$$

where N is the dopant concentration and  $R_{ec}$  is the recombination coefficient which is a function of temperature and dependent on the band structure. For calculations in Figure **1-4** a typical value for indirect-bandgap semiconductors of  $10^{-15} \text{cm}^3/\text{s}$  was used. For an n-type doping density of  $10^{19} \text{cm}^{-3}$  the minority carrier diffusion length is approximately 4 $\mu$ m, while a p-type doping density of  $10^{20} \text{cm}^{-3}$  has a minority carrier diffusion length of 200 nm. The p- region needs to be approximately  $10^{16} \text{ cm}^{-3}$  in order to have a diffusion length (L) to be  $\geq 100 \mu$ m. In order to achieve this the material needs to be high quality with very few impurities as this would lead to shorter minority carrier diffusion lengths, which would decrease the efficiency of a planar structure, such

as shown in Figure 1-3. This is why there is a large p-region in the planar solar cell geometry, so that the minority carrier diffusion length remains as large as possible.

Figure 1-4: Minority carrier diffusion length plotted versus doping density.

The problem with single crystal planar Si solar cells is the high cost due to the high purity that is required. Polycrystalline Si cells are more affordable, however, the efficiencies are decreased (11-13 %) due to charge separation and recombination at the grain boundaries.<sup>4</sup> Research has been trying to bridge the gap between expensive, high efficiency single crystal Si solar cells and the lower cost and efficiency polycrystalline devices.

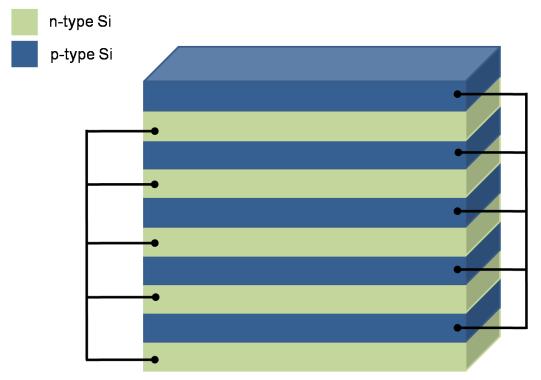

One way to improve the efficiency of devices made with lower quality silicon has been through exploration of alternative geometries that reduce the junction distance. Green *et al.* proposed a parallel multijunction solar cell with alternating p- and n-type layers. <sup>10</sup> The like polarity layers are connected in parallel shown in Figure 1-5. Fabrication involves the deposition of alternating polarity Si layers, followed by laser grooving and groove-wall doping to form channels for a buried contact. The layer thicknesses in this type of geometry are shorter than the minority diffusion carrier length, which allows for shorter collection distances and increased

efficiency. Another multijunction cell, proposed by Sater *et al.*<sup>11</sup>, utilizes edge illumination to eliminate the need for front/back contacts and allow for greater carrier collection similar to the parallel multijunction design. Fabrication of a vertical multijunction cell involves the stacking of several diffused p+nn+ silicon wafers by stacking, metalizing and alloying together. After dicing of the samples, etching to remove saw damage, passivation, and anti-reflection coatings are needed. These designs, while allowing for increased efficiencies in lower quality material, are still complex to fabricate due to numerous processing steps and do not significantly reduce the cost.

Figure 1-5: Illustration of parallel multijunction concept with like polarity layers connected in parallel.  $^{10}$

## 1.2.1 Silicon Nanowire Solar Cell

Another way to increase the surface area in the direction of incident light and obtain a thin area in the direction of carrier collection would be to fabricate radial p-n junction whisker or nanowire solar cells. Diepers et al. <sup>12</sup> originally patented a solar cell design in 1979 consisting of a radial p-n semiconductor whisker array that is similar in theory to multi-junction solar cells. The patent proposes the use of single crystal Si whiskers to increase the surface to volume ratio to increase the quantum yield as opposed to a planar geometry.

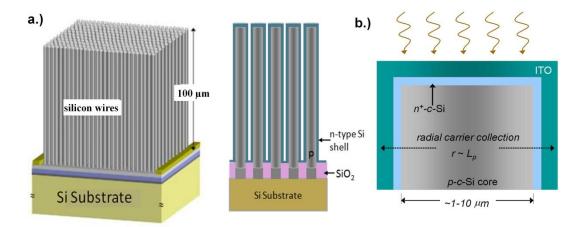

A schematic of a radial p-n high aspect ratio solar cell is shown in Figure 1-6 (a) and (b.) shows a close-up schematic showing the radial junction. Similar to the multijunction cells that take advantage of alternative architectures, this geometry may enable greater efficiency for two reasons. The first is a large distance (~100 μm) in the direction of incident light, which would allow for maximum light absorption. The second is a short distance in the direction of carrier collection to improve the collection efficiency of generated carriers. In addition, the highly textured surface provided by the wire array could provide enhanced light absorption. The sakalakos *et al.* observed increased broadband optical absorption in SiNW arrays on glass compared with solid thin films of similar thickness 13, while a similar observation by Fang *et al.* was made for arrays etched on Si(111) wafers. This kind of design in theory could produce efficiencies equal to or higher than that of planar silicon cells made today.

Figure 1-6: High aspect ratio silicon solar cell. a.) A SiNW array grown on a Si wafer (left) and a cross-sectional view of the p-n junction (right) and b.) expanded view of a single SiNW showing the direction of carrier collection.

Device physics modeling performed by Kayes *et al.*<sup>15</sup> examined the performance of creating a radial p-n junction nanorod solar cell. This geometry takes advantage of a thick area (~100  $\mu$ m) in the direction of incident light, which would allow for maximum light absorption and a short distance in the direction of carrier collection to improve the collection of generated carriers. This geometry is shown in Figure **1-6**. The model results indicated that it would be possible to achieve higher efficiencies from such a nanowire device compared to a planar Si single crystal solar cell provided that the wire radius is approximately equal to the minority carrier diffusion length and the doping levels are high enough that the nanowire radius is not fully depleted. The modeling also indicated that the trap density in the depletion region of the radial p-n junction nanorod solar cell must be relatively low ( $< 3x10^{15} cm^{-3}$ ). The length of the solar cell must also have a length approximately equal to the optical thickness. If these criteria are met, potential efficiency gains between 1.5-11% are expected.

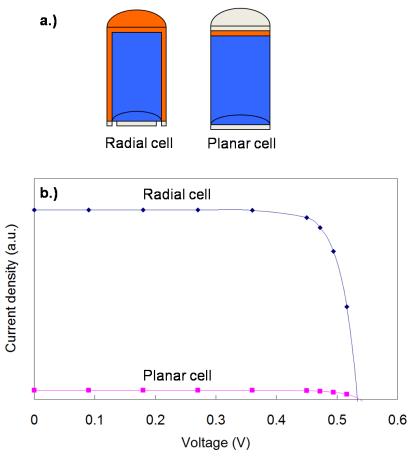

A finite element simulation of a 2D cylindrically radial p-n wire solar cell by Dr. Chito Kendrick following the approach of Kayes *et al.* and was compared to a planar device. The simulation was performed using Sentaurus TCAD software. The model was done assuming p-

type (1x10<sup>18</sup>cm<sup>-3</sup>) SiNWs of 2.5 μm diameter and 25 μm long. The n-type shell (5x10<sup>18</sup> cm<sup>-3</sup>) had a 0.5 μm shell thickness as shown schematically in Figure **1-7(a)**. The model results predict a higher current density for a radial p-n junction cell compared to that of a planar cell of similar thickness and doping density (Figure **1-7(b)**). Based on these modeling results, it is anticipated that a radial p-n junction high aspect ratio solar cell will have a high efficiency and if grown on a low cost substrate will be able to be produced cost effectively.

Figure 1-7: a.) Schematic of a planar geometry and radial geometry and b.) Modeled current density versus voltage for both planar and radial geometry.

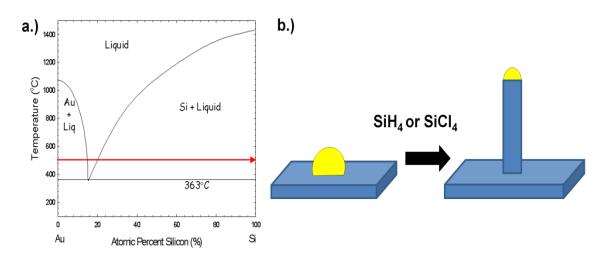

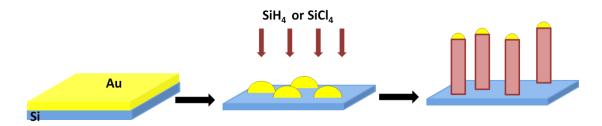

## 1.2.2 Fabrication of Silicon Nanowire Solar Cell

One way to potentially reduce the cost of such a device would be to use "bottom up" fabrication methods to create a large area high density wire array. To date, there have been numerous studies on single crystal silicon nanowire (SiNW) growth by the vapor-liquid-solid (VLS) mechanism. VLS growth uses a catalyst, most commonly Au, to create a Au-Si liquid alloy above its eutectic temperature of 363°C as seen in the phase diagram (Figure 1-8). <sup>16</sup>

Figure 1-8: a.) Phase diagram of Au-Si. b.) Schematic of VLS mechanism.

As the liquid alloy becomes supersaturated with Si, Si precipitates out to form a nanowire. <sup>16</sup> The size of the wire is controlled by the size of the initial Au catalyst. By combining VLS growth with chemical vapor deposition (CVD), complex structures such as radial and axial multijunctions can be achieved by in-situ doping through the tight control of precursor gases. <sup>17-20</sup> While there have been great strides in the understanding and control of nanowire growth, there are still many steps and details that need to be understood and mastered to utilize this approach to fabricate a large area, high aspect ratio SiNW array solar cells.

In order to create an "ideal" nanowire solar cell device there are several material requirements that must be met or addressed. The nanowires must be single crystal, and produced as a well ordered vertical array. The nanowire diameter and length should be uniform and high growth rates ( $\mu$ m/min) would be advantageous. Since the direction of light absorption is decoupled from the direction of carrier collection in this geometry, the length of the SiNWs still need to be long (100  $\mu$ m), consequently, a faster nanowire growth rate would reduce sample growth time and thus be more cost effective. The ability to incorporate dopants during nanowire growth is also required. A smooth nanowire surface is important in order to achieve a high quality radial shell. Au forms deep level states in Si, which could lead to a decrease in carrier lifetimes. Since the silicon nanowires are grown using a Au catalyst it will be important to remove the Au prior to the shell layer formation.

The radial n-type silicon coating also has important requirements. Ideally, the n-type Si should be single crystal and the interface between the n-type shell and wire should be high quality with few impurities or defects present. As mentioned, this could lead to recombination at the p-n interface and yield poor device performance. The n-type Si coating should be conformal on the high aspect ratio structures with uniform thickness. Finally, the n-type Si must be controllably doped to maintain correct p-n carrier concentrations.

Recently, there have been several papers reporting the fabrication of single wire silicon nanowire solar cells. <sup>14,18,20-24</sup> Kempa *et al.* fabricated axial p-i-n and p-n silicon nanowire photovoltaic devices. <sup>18</sup> SiNWs were synthesized using Au nanoparticles via VLS. It was found that the p-i-n structures had an increased open circuit voltage (V<sub>OC</sub>) and that the V<sub>OC</sub> increased with increasing –i layer thickness. An efficiency of 0.5% under AM 1.5G illumination and V<sub>OC</sub> of 0.29V were reported from the optimized p-i-n structure. An efficiency conversion of 0.46% under AM 1.5G illumination was also reported by Kelzenberg *et al.* for axial p-n junction single nanowire devices. <sup>21</sup> Samples were grown using SiCl<sub>4</sub> and the single nanowire backgated I-V

measurements revealed the wires to be n-type doped. Through electrical heating of a single Al contact on a SiNW, a rectifying axial p-n junction was created and exhibited photovoltaic behavior. Measurements corresponded to a solar conversion efficiency of 0.46% and  $V_{OC}$  = 0.19 V. Scanning photocurrent microscopy (SPCM) was used to determine the minority carrier diffusion length. Diffusion lengths of > 2 $\mu$ m were observed in VLS grown SiNWs.

Single wire solar cell devices have also been reported using radial p-n SiNWs. Tian *et al.* were able to produce radial p-n junction SiNWs grown via vapor-liquid-solid mechanism using SiH<sub>4</sub> as the Si precursor. <sup>20</sup> An n-type shell layer was deposited at a pressure of 25 Torr and a temperature of 650°C, using 0.15 sccm SiH<sub>4</sub> and 0.75 sccm PH<sub>3</sub>. TEM revealed that the radial n-type shell was polycrystalline. The nanowires were removed from the substrate via sonication and only single nanowire measurements were carried out. It was reported that core/shell SiNW diodes performed better when a p-i-n radial structure was used. Photovoltaic efficiencies between 2.3-3.4 % under AM 1.5G illumination were reported using the p-i-n structure. The V<sub>OC</sub> was 0.26 V. The catalyst used for p-type nanowire growth was not removed prior to shell deposition, which could lead to issues with device performance.

Several groups have reported radial p-n SiNW solar cell devices fabricated using large area nanowire arrays. These radial arrays were fabricated by wet etching <sup>14,24</sup>, and also through vapor-liquid-solid growth. <sup>20-23</sup> Tsakalakos *et al.* grew p-type SiNWs via VLS growth with SiH<sub>4</sub>, H<sub>2</sub> and HCl. The p-type wires were grown using a Au catalyst and Trimethylboron (TMB) at 650°C on stainless steel foil. The SiNWs were oxidized and stripped with HF prior to deposition of an n-type amorphous Si layer using PECVD to create the radial junction. <sup>22</sup> For these conditions the best V<sub>OC</sub> was 0.13V and the devices exhibited a low efficiency due to a high series resistance.

Garnett *et al.* produced radial p-n junction SiNW arrays using wet etching of single crystal Si substrates to create the n-type core and LPCVD to deposit a p-type amorphous shell.<sup>24</sup> In trying to use low-energy, scalable processes, the SiNW arrays were fabricated by etching. The