# The Pennsylvania State University

## The Graduate School

# Department of Electrical Engineering

# ANALYSIS, DESIGN AND IMPLEMENTATION OF A CHARGE-EQUALIZATION CIRCUIT FOR USE IN AUTOMOTIVE BATTERY MANAGEMENT SYSTEMS

A Thesis in

**Electrical Engineering**

by

Nicholas James Brannen

© 2008 Nicholas James Brannen

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science

August 2008

The thesis of Nicholas James Brannen was reviewed and approved\* by the following:

Jeffrey S. Mayer Associate Professor of Electrical Engineering Thesis Advisor

John D. Mitchell Professor of Electrical Engineering

Joel R. Anstrom Research Associate of Mechanical Engineering

W. Kenneth Jenkins Professor of Electrical Engineering Head of the Department of Electrical Engineering

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

A charge-equalization circuit for an automotive battery management system has been designed and implemented. The selection of the circuit topology is based on an analysis of several different topologies and criteria for utilizing the battery management system in two Penn State research vehicles. The design process included the selection of appropriate power electronic components, the adaptation of a current-mode controller to facilitate proportional control, and the design of the necessary analog electronics and communication network. Implementation included the fabrication of a printed circuit board, the population of the board, and the testing of the sub-circuits. The system was tested for its ability to transfer prescribed currents. Recommendations for improvements are discussed.

# **TABLE OF CONTENTS**

| LIST OF FIGURES                                                         | vi  |

|-------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                          | X   |

| ACKNOWLEDGEMENTS                                                        | xii |

| Chapter 1 Introduction                                                  | 1   |

| 1.1 Automobile Industry Transition toward Electric Vehicles             | 1   |

| 1.2 Batteries and Battery Management Systems                            |     |

| 1.3 Penn State Research Vehicles                                        | 6   |

| 1.4 Organization of Thesis                                              |     |

| Chapter 2 Candidate Solutions                                           | 9   |

| 2.1 Evaluation Criteria                                                 | 9   |

| 2.2 General System Structures.                                          |     |

| 2.3 Series Systems                                                      |     |

| 2.3.1 Shunt-Resistor System.                                            |     |

| 2.3.2 Switched-Capacitor System.                                        |     |

| 2.3.3 Current-Diverter System                                           |     |

| 2.3.4 Bidirectional Current-Diverter System                             |     |

| 2.4 Parallel Systems                                                    |     |

| 2.4.1 Flyback-Converter System                                          |     |

| 2.4.2 Bidirectional Flyback-Converter System                            |     |

| 2.4.3 Centralized Forward-Converter System                              |     |

| 2.5 Hybrid Systems.                                                     |     |

| 2.5.1 Hybrid System #1                                                  |     |

| 2.5.2 Hybrid System #2                                                  |     |

| 2.6 System Selection for the Penn State Research Vehicles               |     |

| Chapter 3 Analysis, Design, and Implementation of a Charge-Equalization |     |

| Circuit                                                                 | 46  |

| 3.1 Operating Conditions                                                | 46  |

| 3.2 Analysis                                                            | 47  |

| 3.2.1 Discharging the Battery Module                                    | 49  |

| 3.2.2 Charging the Battery Module                                       |     |

| 3.3 Design                                                              |     |

| 3.3.1 Current, Voltage, and Power Levels                                |     |

| 3.3.2 Power Electronics                                                 |     |

| 3.3.3 Control                                                           |     |

| 3.3.4 Communication                                         | 75  |

|-------------------------------------------------------------|-----|

| 3.3.5 Microcontroller                                       | 78  |

| 3.3.6 Power                                                 | 79  |

| 3.3.7 Software                                              |     |

| 3.4 Implementation                                          | 85  |

| 3.4.1 Circuit Layout                                        |     |

| 3.4.2 On-Board DC-to-DC Converters                          | 86  |

| 3.4.3 Microcontroller Hello World                           | 86  |

| 3.4.4 Communication Validation                              | 88  |

| 3.4.5 Gate Drive Validation                                 | 90  |

| 3.4.6 Feedback Signal Filter Circuits Validation            | 93  |

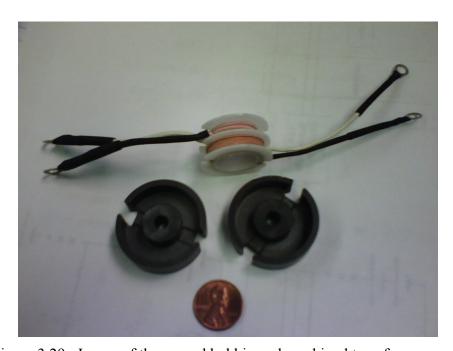

| 3.4.7 Building the Transformer                              | 101 |

| Chapter 4 Experimental Results                              | 106 |

| 4.1 Open-loop Peak-Current Test                             |     |

| 4.1.1 MOSFET Peak-Current Test                              | 107 |

| 4.1.2 IGBT Peak-Current Test                                | 111 |

| 4.2 Proportional Control Test                               | 115 |

| 4.3 Observations and Recommended Changes                    | 115 |

| Chapter 5 Summary and Conclusions                           | 119 |

| Bibliography                                                | 122 |

| Appendix A Communication Messages                           | 126 |

| Appendix B Microcontroller Code                             | 130 |

| Appendix C Schematic, Printed Circuit Board, and Parts List | 150 |

| **                                                          |     |

# LIST OF FIGURES

| Figure 1.1: Penn State Electric-Lion vehicle and battery pack                                                                         | 7  |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Penn State HyLion vehicle and battery pack                                                                                | 7  |

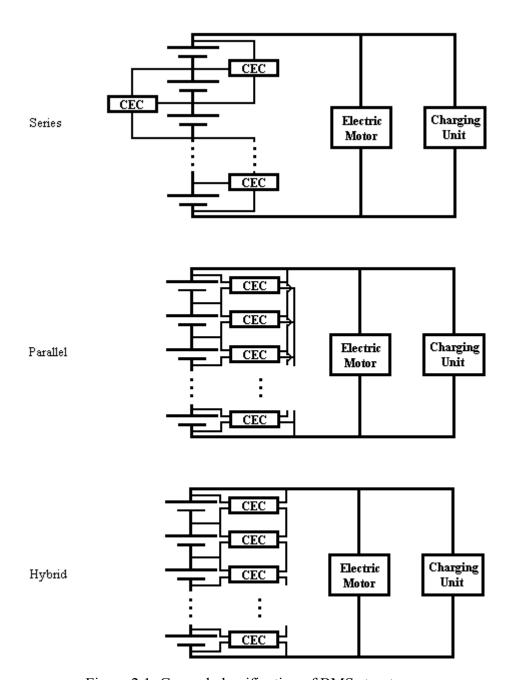

| Figure 2.1: General classification of BMS structures.                                                                                 | 12 |

| Figure 2.2: Schematic diagram for the Shunt-Resistor system                                                                           | 14 |

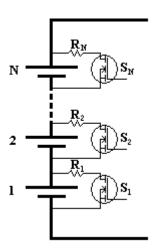

| Figure 2.3: Schematic diagram for the Switched-Capacitor system                                                                       | 16 |

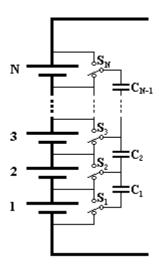

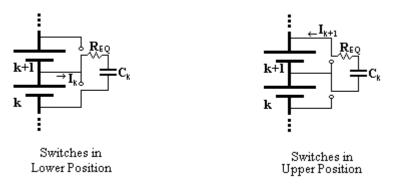

| Figure 2.4: Switched-Capacitor system transferring energy from battery cell k to battery cell k+1                                     | 17 |

| Figure 2.5: Schematic diagram for the Current-Diverter system                                                                         | 19 |

| Figure 2.6: Current-Diverter system diverting charging current around the k <sup>th</sup> battery cell                                | 20 |

| Figure 2.7: Current-Diverter system diverting charging current around the first battery cell                                          | 21 |

| Figure 2.8: Schematic diagram for the Bidirectional Current-Diverter system                                                           | 23 |

| Figure 2.9: Bidirectional Current-Diverter system diverting discharging current around the k <sup>th</sup> battery cell               | 24 |

| Figure 2.10: Schematic diagram for the Flyback-Converter system                                                                       | 27 |

| Figure 2.11: Flyback-Converter system transferring energy from the k <sup>th</sup> battery cell to the high-voltage bus               | 28 |

| Figure 2.12: Schematic diagram for the Bidirectional Flyback-Converter system                                                         | 30 |

| Figure 2.13: Bidirectional Flyback-Converter system transferring energy from the high-voltage bus to the k <sup>th</sup> battery cell | 31 |

| Figure 2.14: Schematic diagram for the Centralized Forward-Converter system                                                           | 33 |

| Figure 2.15: The Centralized Forward-Converter system transferring current from the high-voltage bus to the individual battery cells  | 34 |

| Figure 2.16: Schematic diagram of the Hybrid System #1                                                                                | 36 |

| Figure 2.17: The Hybrid System #1 discharging current from the k <sup>th</sup> battery cell                                           | 37 |

| Figure 2.18: The Hybrid System #1 redistributing energy from the k <sup>th</sup> battery cell to the other battery cells | .38  |

|--------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.19: Schematic diagram of the Hybrid System #2                                                                   | .40  |

| Figure 2.20: The Hybrid System #2 discharging current from the k <sup>th</sup> battery cell                              | .41  |

| Figure 2.21: The Hybrid System #2 discharging current from the N <sup>th</sup> battery cell                              | .42  |

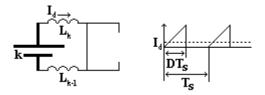

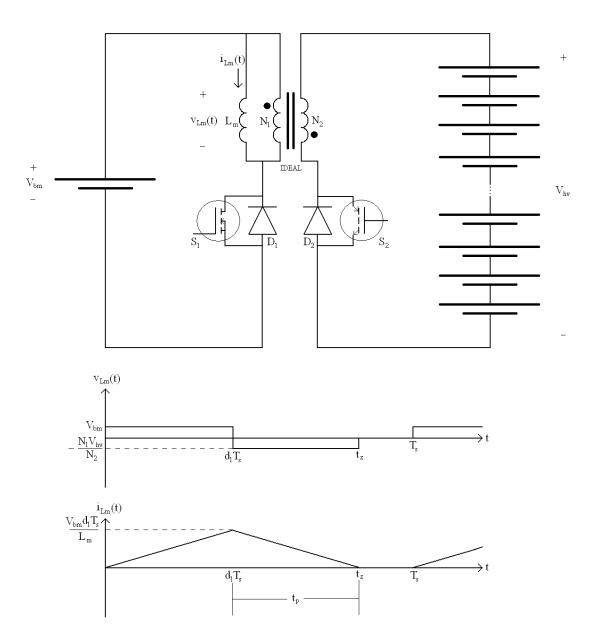

| Figure 3.1: Schematic Diagram for the analysis of the Bidirectional Flyback-Converter system                             | .48  |

| Figure 3.2: Voltage and current waveforms of the magnetizing inductance during a discharge sequence                      | .50  |

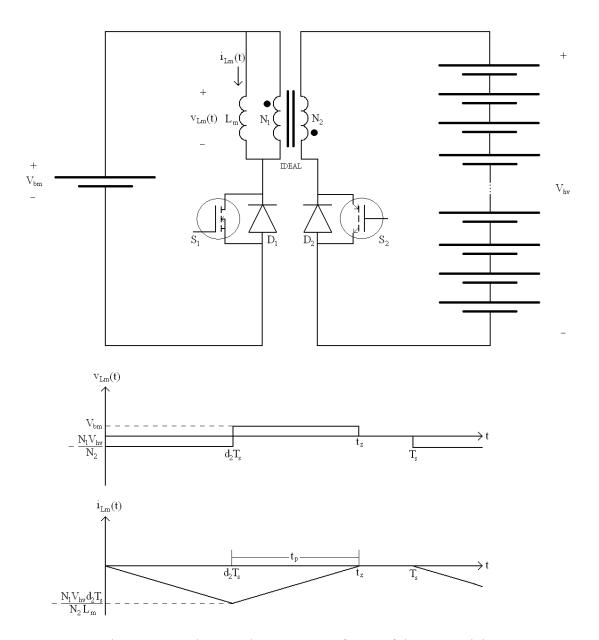

| Figure 3.3: Voltage and current waveforms of the magnetizing inductance during a charging sequence                       | . 54 |

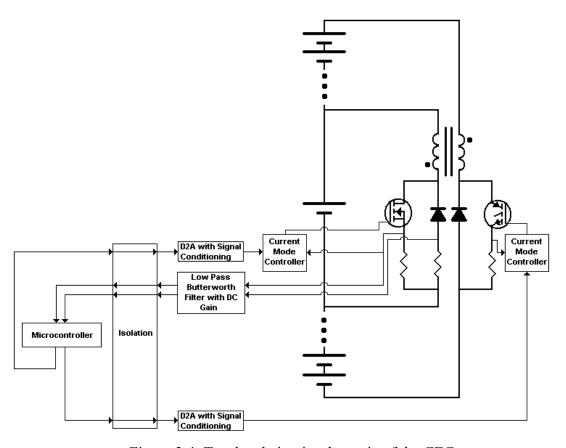

| Figure 3.4: Top-level circuit schematic of the CEC                                                                       | .58  |

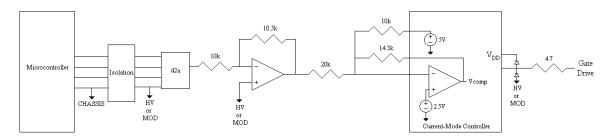

| Figure 3.5: Gate drive schematic                                                                                         | .69  |

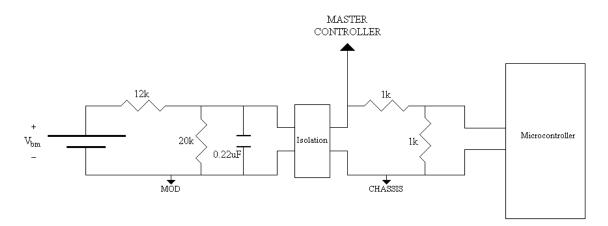

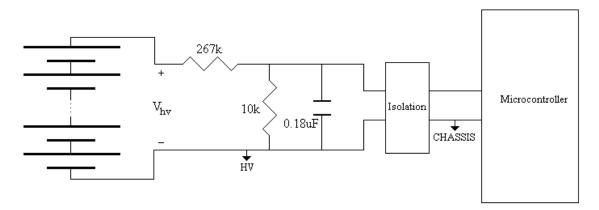

| Figure 3.6: Single-pole, low-pass RC filter of the battery module voltage                                                | . 70 |

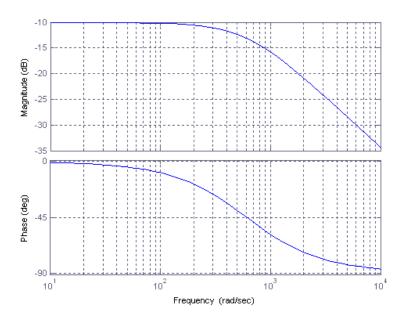

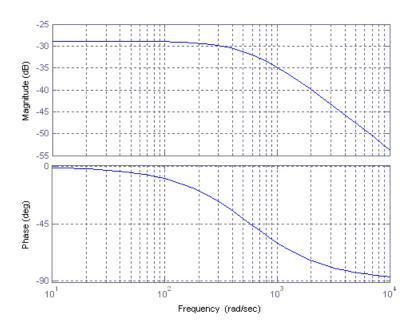

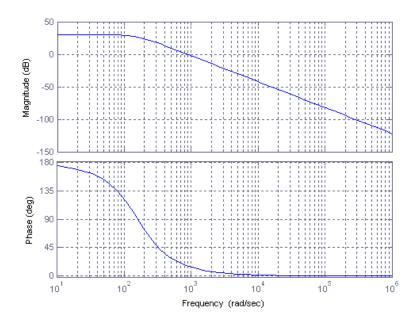

| Figure 3.7: Bode magnitude and phase plots of the battery module voltage RC filter                                       | .71  |

| Figure 3.8: Single-pole, low-pass RC filter of the high-voltage bus voltage                                              | .72  |

| Figure 3.9: Bode magnitude and phase plots of the high-voltage bus voltage RC filter                                     | .72  |

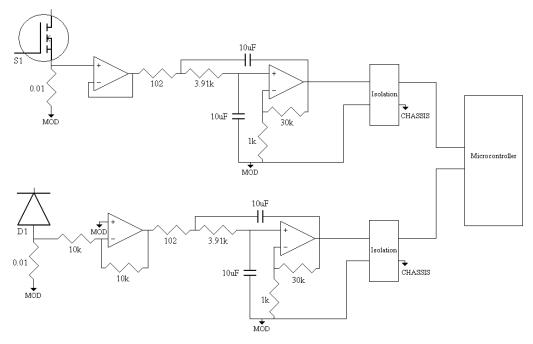

| Figure 3.10: Circuit schematics of the current-signal active filters                                                     | .74  |

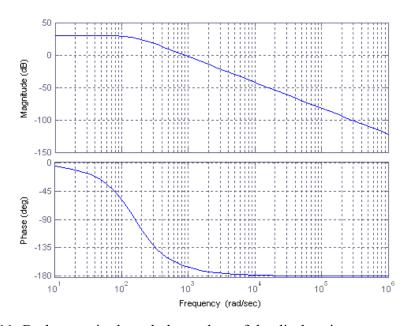

| Figure 3.11: Bode magnitude and phase plots of the discharging-current active filter                                     | .74  |

| Figure 3.12: Bode magnitude and phase plots of the charging-current active filter                                        | .75  |

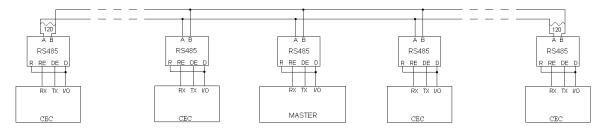

| Figure 3.13: Schematic diagram of the RS485 communication network                                                        | .76  |

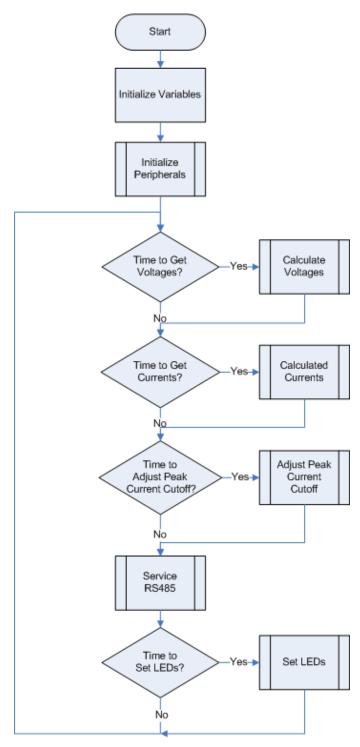

| Figure 3.14: Main loop                                                                                                   | . 83 |

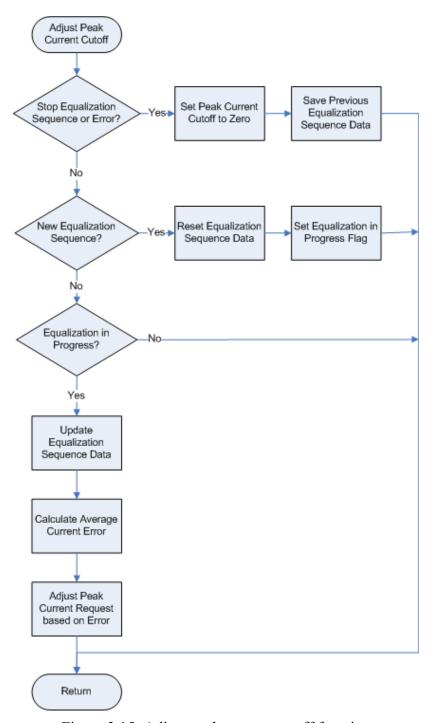

| Figure 3.15: Adjust peak-current cutoff function                                                                         | . 84 |

| Figure 3.16: Microcontroller hello world                                                                                 | .87  |

| Figure 3.17: UART bit timing                                                                                                | .88   |

|-----------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 3.18: Transmission of a packet on the RS485 bus                                                                      | .89   |

| Figure 3.19: Computer to CEC packet transmission and reply                                                                  | .90   |

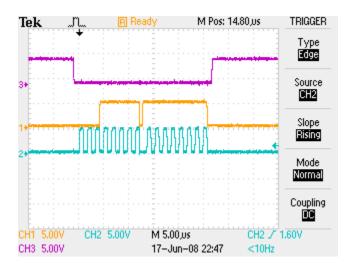

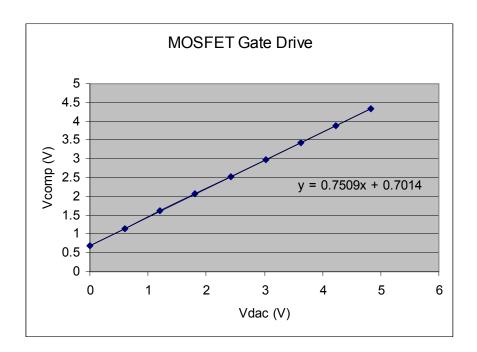

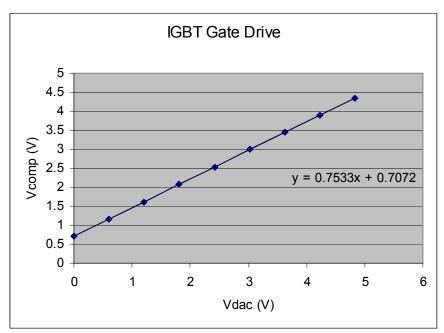

| Figure 3.20: SPI communication to the DAC                                                                                   | .91   |

| Figure 3.21: Relationship of compensation pin voltage to DAC voltage                                                        | .92   |

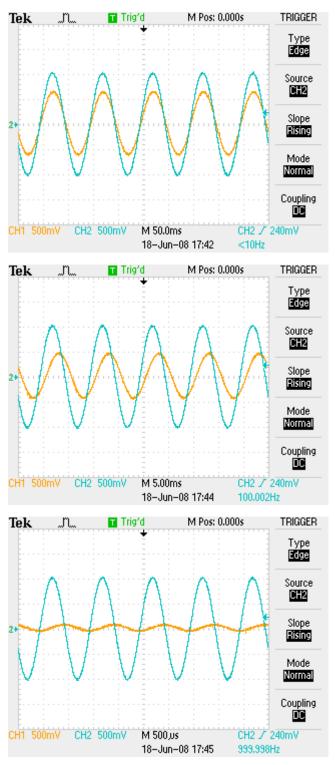

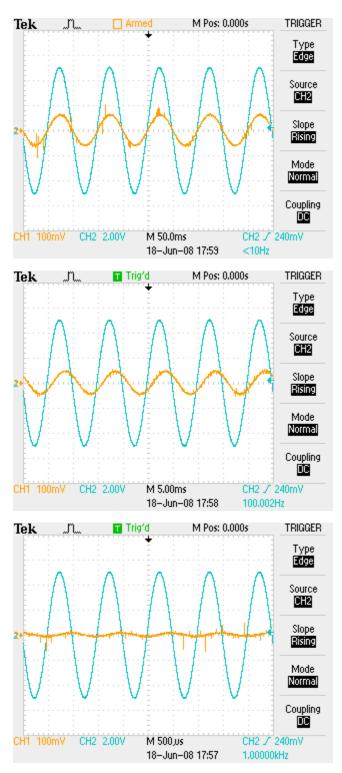

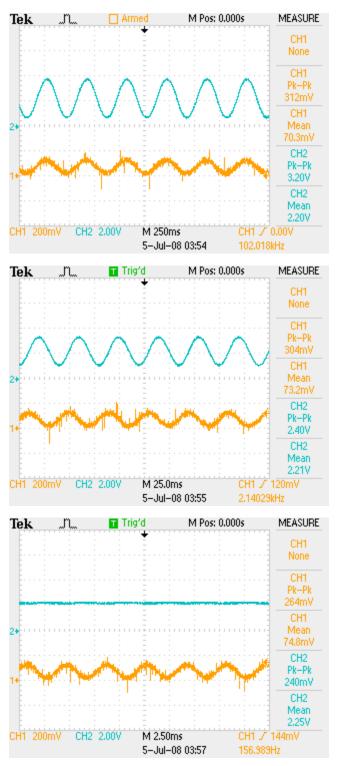

| Figure 3.22: Response of the battery module voltage filter to input signals with 10 Hz, 100 Hz, and 1 kHz frequencies       | .94   |

| Figure 3.23: Response of the high-voltage bus voltage filter to input signals with 10 Hz, 100 Hz, and 1 kHz frequencies     | .96   |

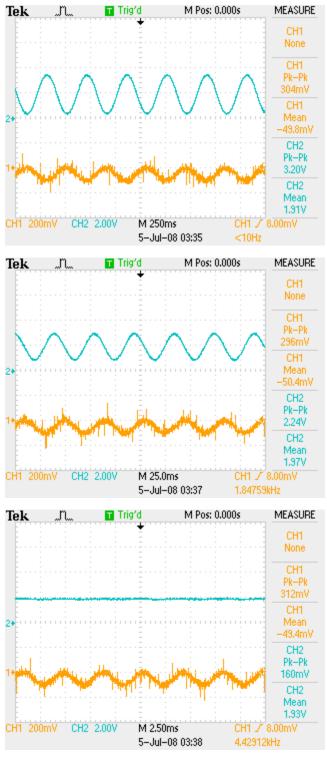

| Figure 3.24: Response of the average charging current filter to input signals with 2.5 Hz, 25 Hz, and 250 Hz frequencies    | .98   |

| Figure 3.25: Response of the average discharging current filter to input signals with 2.5 Hz, 25 Hz, and 250 Hz frequencies | .100  |

| Figure 3.26: Mounting clamp used to machine the transformer core                                                            | .102  |

| Figure 3.27: Machining the transformer core                                                                                 | .102  |

| Figure 3.28: Tinning the litz wire                                                                                          | . 104 |

| Figure 3.29: Image of the wound bobbin and machined transformer cores                                                       | . 104 |

| Figure 3.30: Completed transformer core wired to the CEC                                                                    | .105  |

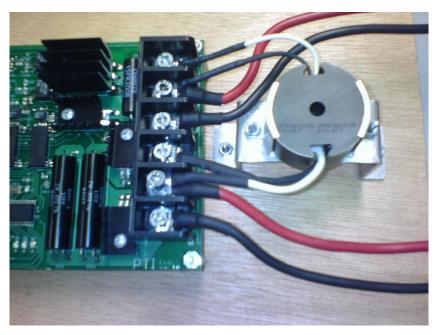

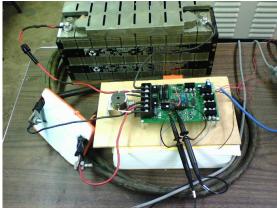

| Figure 4.1: Peak-current test setup                                                                                         | .107  |

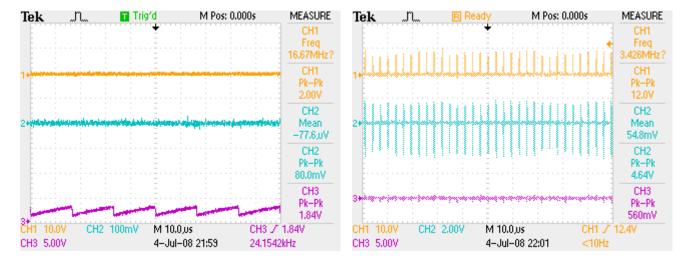

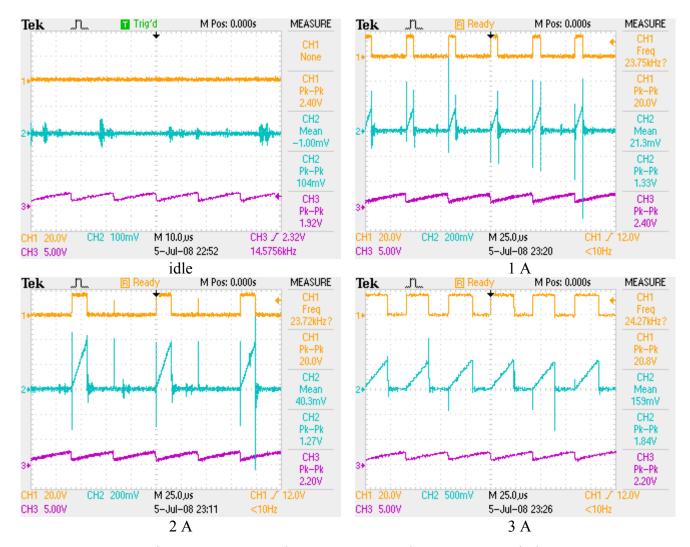

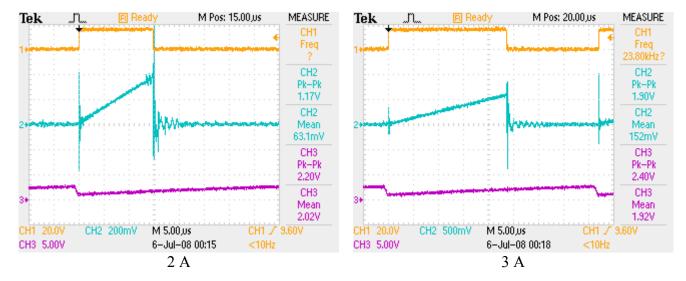

| Figure 4.2: MOSFET idle snapshot and 20-A peak-current test snapshot                                                        | .108  |

| Figure 4.3: MOSFET peak-current test with jumper snapshots at a 25-μs window                                                | .109  |

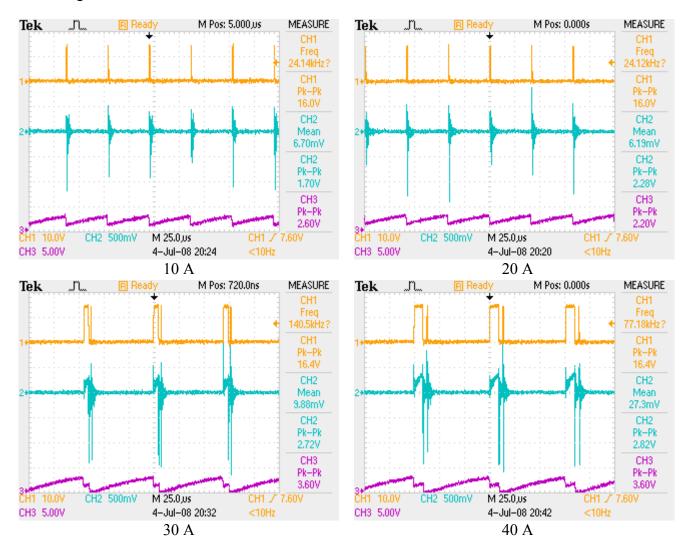

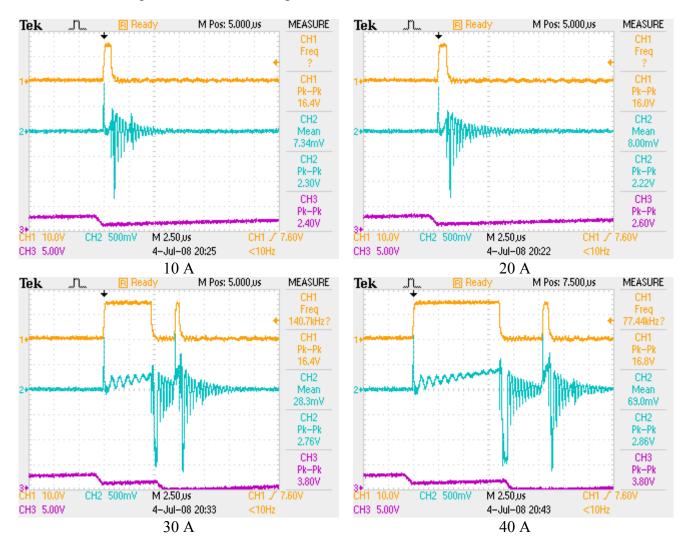

| Figure 4.4: MOSFET peak-current test with jumper snapshots at a 2.5 μs window                                               | .110  |

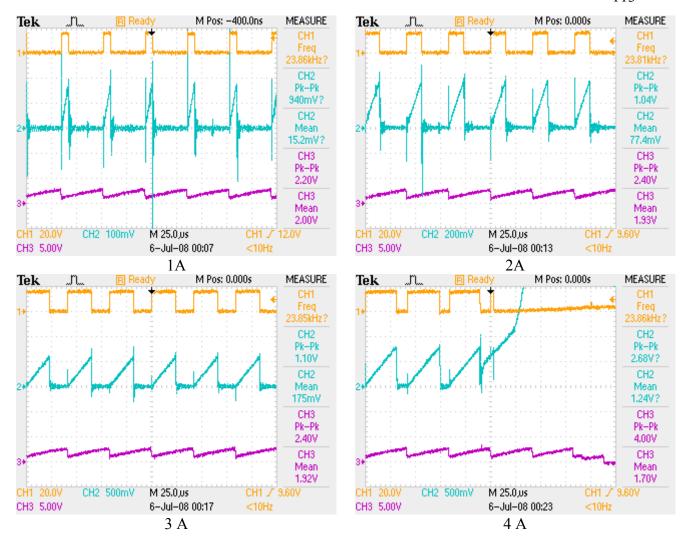

| Figure 4.5: IGBT peak-current test snapshots at a 25-μs window                                                              | .112  |

| Figure 4.6: IGBT peak-current test with jumper snapshots at a 25-µs window                                                  | .113  |

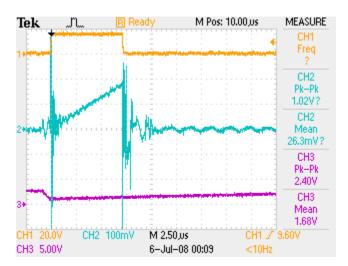

| Figure 4.7: IGBT 1-A peak-current test with jumper snapshot at a 2.5-µs window                                              | .114  |

| Figure 4.8: IGBT peak-current test with jumper snapshots at a 5-µs window                                                   | .114  |

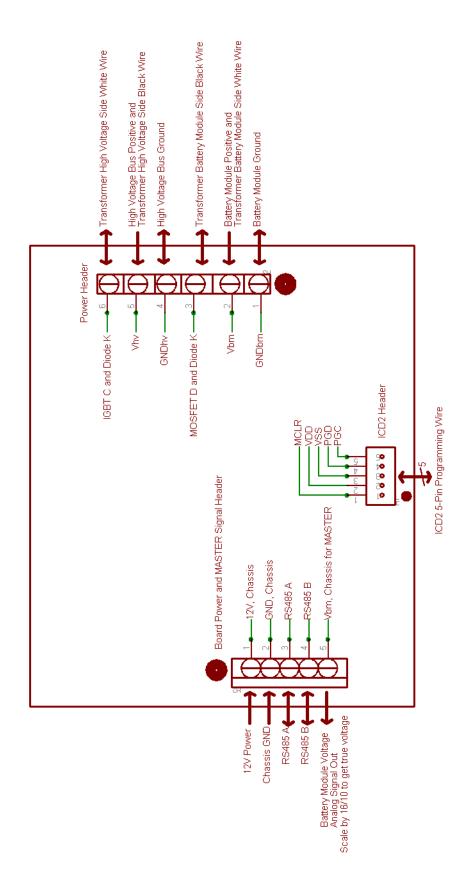

| Figure C.1: Input and output headers schematic                     | 151 |

|--------------------------------------------------------------------|-----|

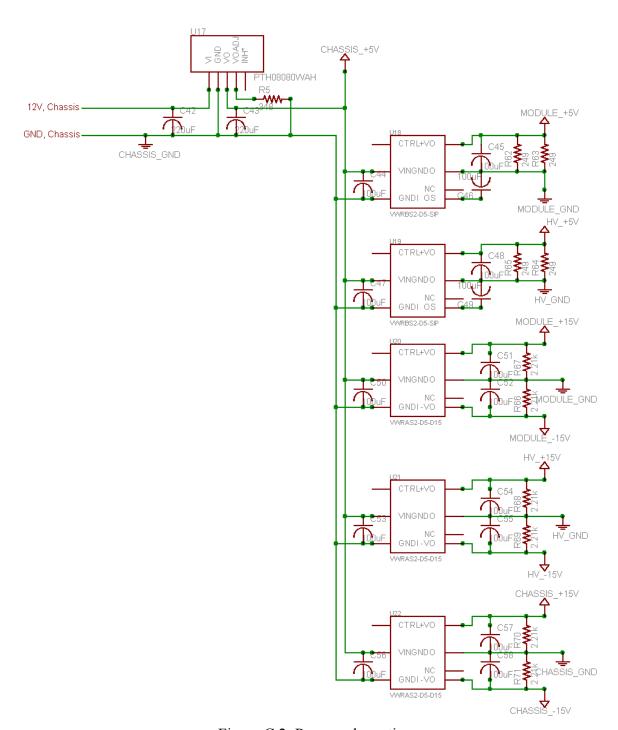

| Figure C.2: Power schematic                                        | 152 |

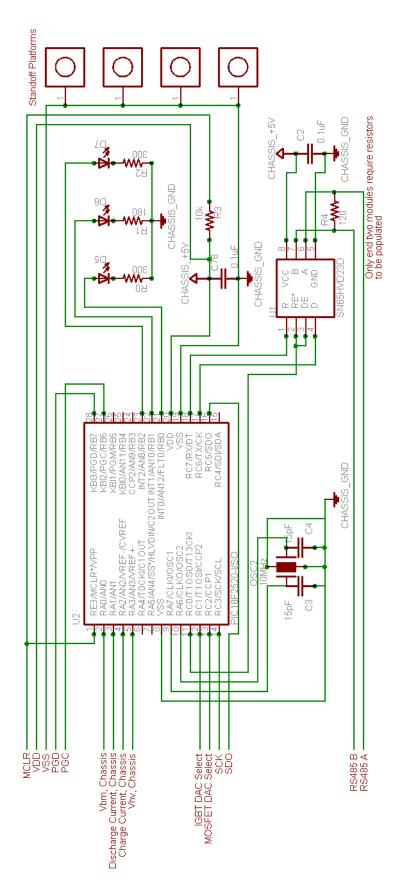

| Figure C.3: Chassis ground schematic                               | 153 |

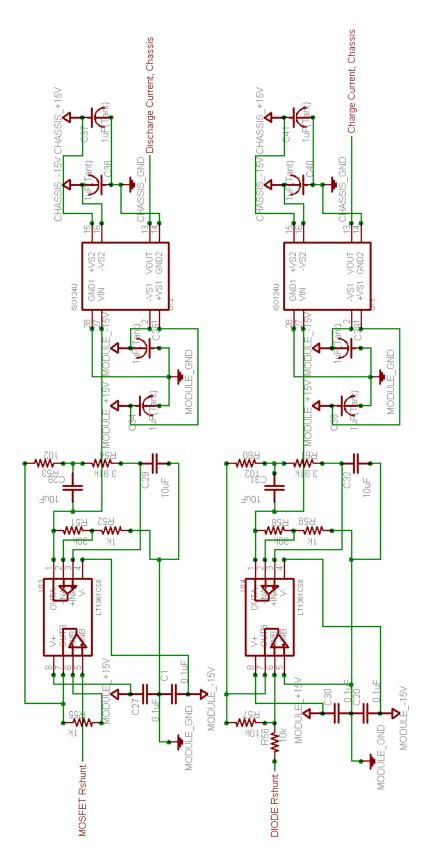

| Figure C.4: Charge and discharge current filters                   | 154 |

| Figure C.5: Battery module voltage RC filter and MOSFET gate drive | 155 |

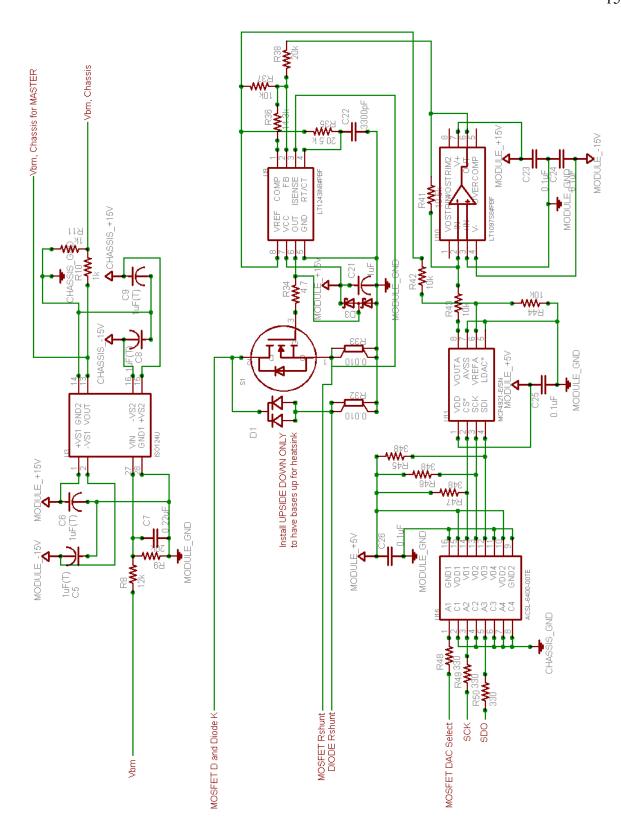

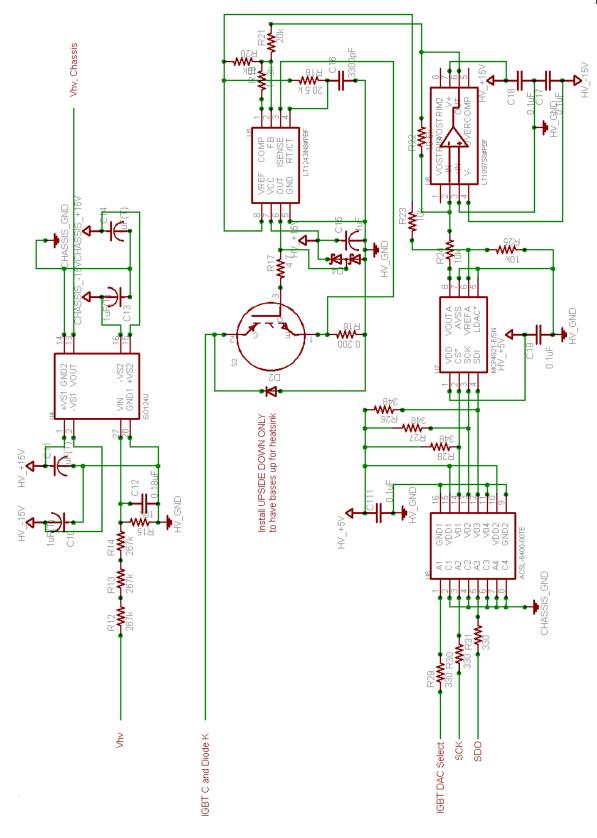

| Figure C.6: High-voltage bus voltage RC filter and IGBT gate drive | 156 |

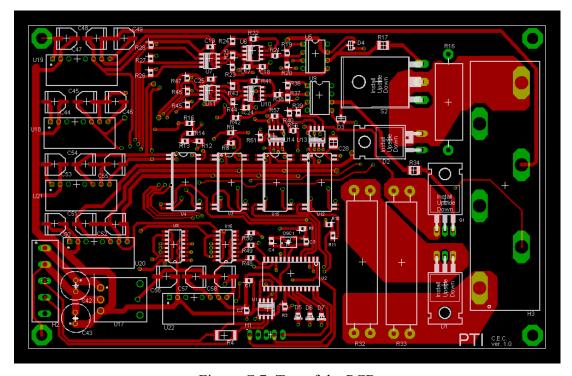

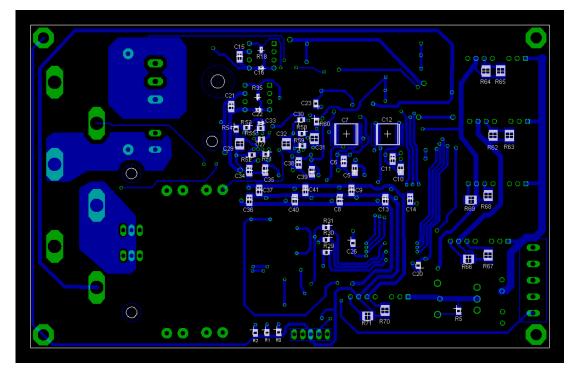

| Figure C.7: Top of the PCB                                         | 157 |

| Figure C.8: Bottom of the PCB                                      | 158 |

# LIST OF TABLES

| Table 2.1: Summary of component characteristics for the Shunt-Resistor system                       | . 14 |

|-----------------------------------------------------------------------------------------------------|------|

| Table 2.2: Summary of component characteristics for the Switched-Capacitor system                   | .16  |

| Table 2.3: Summary of component characteristics for the Current-Diverter system.                    | . 19 |

| Table 2.4: Summary of component characteristics for the Bidirectional Current-Diverter system       | .23  |

| Table 2.5: Summary of component characteristics for the Flyback-Converter system                    | .27  |

| Table 2.6: Summary of component characteristics for the Bidirectional Flyback-Converter system      | .30  |

| Table 2.7: Summary of component characteristics for the Centralized Forward-Converter system        | .33  |

| Table 2.8: Summary of component characteristics of the Hybrid System #1                             | .36  |

| Table 2.9: Summary of component characteristics of the Hybrid System #2                             | .40  |

| Table 2.10: Criteria weight factors for the Penn State research vehicles                            | .44  |

| Table 3.1: Maximum duty cycles for various transformer winding ratios                               | .60  |

| Table 3.2: Magnetizing inductance values required to achieve 10 A of average battery module current | .61  |

| Table 3.3: Calculated duty cycles to achieve 10 A of average battery module current                 | .61  |

| Table 3.4: Calculated current and voltage levels for the power electronic components                | . 62 |

| Table 3.5: Power levels when transferring 10 A of average battery module current                    | .63  |

| Table 3.6: Selected electronic switches and diodes characteristics                                  | . 63 |

| Table 3.7: Recommended values for a pot-core transformer with square-wave excitation.               | . 65 |

| Table 3.8: General communication message structure                       | 77  |

|--------------------------------------------------------------------------|-----|

| Table 3.9: Voltage and power requirements of the CEC                     | 80  |

| Table 3.10: Advanced Circuits printed circuit board specifications       | 85  |

| Table 3.11: Measured output voltages of the on-board dc-to-dc converters | 86  |

| Table C.1: Capacitor list                                                | 159 |

| Table C.2: Diode list                                                    | 160 |

| Table C.3: Resistor list.                                                | 161 |

| Table C.4: Electronic switch list                                        | 162 |

| Table C.5: Integrated circuit list                                       | 162 |

| Table C.6: Header list                                                   | 162 |

#### **ACKNOWLEDGEMENTS**

My research was financially supported by the Mid-Atlantic Universities

Transportation Center (MAUTSC), the Department of Environmental Protection (DEP),

and the Pennsylvania Department of Community and Economic Development (DCED).

I would like to thank the Thomas D. Larson Pennsylvania Transportation Institute for providing the equipment and space that was required to conduct my research. I would also like to thank Dr. Anstrom for giving me the inspiration, means, and guidance to complete this work. Dr. Mayer, thank you for providing me with direction in my academic career and guidance in completing this work. Dr. Mitchell, thank you for taking the time to review this work and to serve on my thesis committee.

Last but not least, I would like to express my sincerest gratitude to my family. Without their support, I would not have been able to complete this journey.

### Chapter 1

#### Introduction

Electrically-powered vehicles are an active area of research in the automotive industry and academic community. One area of electric-vehicle technology that is receiving considerable attention is energy sources. Electrochemical batteries are currently the prevalent energy source. They require a robust battery management system (BMS) with a specialized charge-equalization circuit (CEC) to operate safely and maintain their performance over the lifetime of the vehicle.

# 1.1 Automobile Industry Transition toward Electric Vehicles

The internal combustion engine (ICE) has been the powerplant of choice in the automobile for the greater part of the past century. The cost of ownership of these vehicles has been low enough that the majority of Americans could afford one, and their effect on the environment was not considered to be substantial. However, most major automobile manufacturers are currently investigating the use of an electric motor as either a supplement to or direct replacement of the ICE. The Toyota Prius, Chevy Volt, and Tesla Roadster are examples of the recent interest in the integration of the electric motor into the automobile powertrain. The driving factors in the on-going transition from the ICE to the electric motor are economic and environmental.

The energy of one gallon of gasoline and one kWh of electricity can be converted to 130,800,000 J and 3,600,000 J, respectively [1]. Therefore, the energy in one gallon of gasoline is equivalent to approximately 36.3 kWh of electricity. Recently, the United States national average price of one gallon of gasoline has reached a record level at over \$3.50 [2]. In comparison, the United States national average cost of one kWh of electricity in 2007 was \$0.1064 [3]. Therefore, it would cost approximately \$3.86 to get the energy equivalent of one gallon of gasoline from electricity. From an energy standpoint, electricity currently costs about the same amount as gasoline. However, studies have found that the maximum efficiency in converting latent chemical energy of fuel to propulsion for the ICE and its driveline was 15%, and the maximum efficiency for the electric motor with gear reduction was in excess of 90% [4][5]. The actual efficiencies that are achieved by current electric vehicles are substantially lower, but this is due to the limitations in energy storage. While energy storage is preventing the electric motor from being the current automotive powerplant of choice, it is clear that with energy source improvements, the efficiency of the electric motor has the potential to significantly exceed that of the ICE. Consequently, research is on-going in developing electric motor technology to increase the energy efficiency, and therefore lower the total cost of ownership, of the automobile.

The second significant contributor to the reduction of interest in the ICE is its environmental impact. Automobile exhaust pollutants consist of carbon monoxide, hydrocarbons, and nitrogen oxide. It also is a major contributor of the carbon dioxide that is released into the environment [6]. Carbon monoxide reduces the flow of oxygen in the bloodstream and is particularly dangerous to people with heart disease. Some

hydrocarbons are toxic and have the potential to be carcinogenic. Nitrogen oxide reacts with hydrocarbons to cause ozone and also contributes to the formation of acid rain. Finally, carbon dioxide is considered a greenhouse gas that contributes to the potential for global warming.

The Environmental Protection Agency estimates that automobiles contribute about 60% of the carbon monoxide, 44% of the hydrocarbons, and 31% of the nitrogen oxides emitted in the United States [7]. While the federal government is slow in bringing change to its vehicle emission standards, individual states are beginning to take action to reduce it. In 2004 California had set its own emissions standards that are aimed at reducing air pollution from cars and light trucks by 25% and from sport utility vehicles by 18%. California has also filed suit against General Motors, Toyota, Ford, Honda, Chrysler and Nissan in an attempt to hold them accountable for the greenhouse gases that their vehicles produce [8]. There is a growing awareness of the impact of the ICE on the environment and a mounting push for cleaner alternatives.

To conform to the tougher emission regulations, automobile manufacturers are turning to the electric motor because it produces zero local emissions. One study has found that, in comparison to the ICE emissions, the generation of energy for automotive electric motors results in the emissions savings of 2% of carbon monoxide, 76% of carbon dioxide, 56% of nitrogen oxides, and 9% of hydrocarbons [9]. Therefore, even at the global level, the electric motor has shown it has the potential to make a much smaller impact on the environment then the ICE.

## 1.2 Batteries and Battery Management Systems

The main barrier that prevents the electric motor from becoming the automobile powerplant of choice is the lack of an acceptable energy source. To allow the motor to do a reasonable amount of work, the energy source is required to have a high energy density. Greater potential to do work results in a longer range of distance traveled for an electric vehicle or a series hybrid-electric vehicle, and it results in a higher fuel efficiency for a parallel hybrid-electric vehicle. It also must have a high power density to satisfy the peak power demand of the electric motor. The charge time has to be kept to a minimum. It is paramount that its operation be safe. Finally, it should be maintenance free and environmentally friendly [10]. The difficulty in finding an appropriate solution is that energy sources generally excel in one characteristic or another, but not all.

At the present time, electrochemical batteries are often the energy source that is utilized. However, an individual battery cell outputs a voltage level that is too low to reasonably meet the power demand of automotive electric motors. Automobiles must have a high-power powerplant to satisfy the consumers' demand for acceleration. Power ratings of currently used electric motors are in the range from 50 kW to 185 kW, as found in the efficiency-inspired 2008 Toyota Prius and the performance-inspired 2008 Tesla Roadster, respectively [11][12]. To increase the power output that can produced from batteries, a large number of battery cells are placed in series to create a high-voltage battery pack. The high voltage of the battery pack allows it to meet the power demand of the electric motor at a reasonable current level. Efficiencies are increased because the

power losses due to resistance are decreased. The battery pack voltage can be 360 V or even higher [13].

The state of charge (SOC) of a battery cell is defined as the ratio of the amount of remaining, usable energy to its completely-charged, usable energy. The charge efficiency of a battery cell is defined as the ratio of its discharged A·h to its charged A·h [10]. Due to the series configuration of the pack, all of the battery cells conduct the same current that is demanded from the electric motor or is supplied from the charging unit. However, manufacturer tolerances and uneven battery pack temperatures will result in varying charge efficiencies of the battery cells [14]. As the battery pack is used over time, the different charge efficiencies will result in battery cells with varying SOC.

Without a BMS, the individual battery cell voltages of the battery pack must be approximated by an average value that is calculated from the overall voltage. This results in errors when monitoring the SOC of the individual battery cells. During a discharge sequence these errors can lead to some battery cells that are over-discharged, and during a charge sequence it can lead to some battery cells that are over-discharged. Cycling a battery cell beyond its rated limit may damage the cell. The damage may consist of capacity loss, a higher self-discharge rate, and lower charge efficiency [14]. Extreme cases may lead to a thermal runaway condition, which can result in a gas fire or explosion [15]. A BMS must monitor the state of charge of the individual battery cells and prevent an overcharge or over-discharge event from occurring.

The battery pack can only be discharged until the battery cell with the lowest SOC reaches its cutoff limit. Likewise, it can only be charged until the battery cell with the highest SOC reaches its cutoff limit. This lowers the useable amount of energy in the

battery pack as the variability in the battery pack increases. As a result, the contribution that the electric motor can make in powering the vehicle is reduced. One study had found that after 60 cycles of a battery pack, it could only produce 58% of its rated energy before its lowest SOC battery cell had reached its cutoff limit [14]. Consumers expect long lifetimes and consistent performance from their automobiles. Therefore, the BMS must also have a CEC that can effectively correct the SOC variability that develops within the battery pack.

#### 1.3 Penn State Research Vehicles

Two hybrid electric vehicles are currently under development at Penn State. One vehicle, the Electric-Lion, is based on a 1992 Ford Escort chassis. It is considered a range-extending, series, hybrid-electric vehicle. The torque at the wheels is generated from the electric motors only. It employs two Solectria, 35-kW, ac induction motors to power the front wheels. A Kawaski, 12-kW, two-piston ICE and generator are used to charge the battery pack. The 144-V battery pack consists of 12 SAFT (SAFT is a manufacturer of batteries), 12-V nominal, 100-A·h nickel-metal hydride (NiMH) battery modules. A picture of the Electric-Lion and its battery pack are shown in Figure 1.1.

Figure 1.1: Penn State Electric-Lion vehicle and battery pack

The second vehicle, the HyLion, is based on a 1997 General Motors EV1 chassis. It is also considered a range-extending, series, hybrid-electric vehicle. Similarly to the Electric-Lion, the HyLion propulsion is produced from the electric motor only. It employs a 100-kW, ac induction motor to power the front wheels. A Ballard (Ballard is a manufacturer of Fuel Cells), 1.2-kW, hydrogen fuel cell is used to charge the battery pack. The 300-V battery pack consists of 25 Panasonic, 12-V nominal, 95-A·h, NiMH battery modules. A picture of the HyLion and its battery pack are shown in Figure 1.2.

Figure 1.2: Penn State HyLion vehicle and battery pack

Neither vehicle has a BMS; they both are currently operated based on an estimation of battery cell voltage. The current BMS under development has a centralized, master controller that is programmed using MATLAB's Simulink software. This simplifies the software development that is required, and it allows the BMS to be used as an instructional tool for students that span across multiple disciplines. The master controller monitors the SOC of the battery modules, instructs the CEC in how to manage the energy variability in the battery pack, and communicates to the vehicle controller. The scope of the research presented here is the analysis, design, and implementation of the CEC for the developing BMS.

# 1.4 Organization of Thesis

The thesis is organized into five chapters. The next chapter presents evaluation criteria and general system structures of CECs. Systems presented in the literature are investigated in how well they perform against the evaluation criteria, and a system is chosen for the Penn State research vehicles. The focus of Chapter 3 will be the analysis, design, and implementation of the selected CEC. In Chapter 4, the implemented CEC will be tested, the results and observations presented, and recommendations for future work will be made. Finally, in Chapter 5, the thesis will be summarized.

## Chapter 2

#### **Candidate Solutions**

A Charge-Equalization Circuit (CEC) allows a battery management system (BMS) to maintain an appropriate distribution of energy throughout a battery pack.

Many different CECs have been presented in the literature, and the particular application must be analyzed to determine which one is optimal. Several different CEC systems are examined in this chapter, and one is then selected for the Penn State research vehicles.

#### 2.1 Evaluation Criteria

Several criteria have been determined to evaluate the various CECs. Applications must weight the different criteria to determine which CEC is optimal.

• Equalization Power: The charging and discharging sequences of the battery pack can be large in magnitude and short in duration, which can make the equalization process difficult. The CEC must have the power capability to be able to eliminate the state of charge (SOC) variability of the battery pack. This will allow a vehicle controller to utilize the full energy potential of the battery pack continuously. All systems are evaluated in the context of equalizing battery cells with a common, quasistatic voltage value. Therefore, power capability of each CEC is directly proportional to the maximum average value of current that it can transfer.

- **Modular Setup**: A modular setup facilitates assembly and repair, as well as adaptability to battery packs of different size.

- **Simple/Robust Control Strategy**: The system should not be overly complex and should have a low probability of failure.

- **Expense**: Relative to the battery cells it equalizes and the cost of the automobile, the implementation cost should be kept to a minimum.

- Equalization at the Battery Cell Level: Charge efficiencies can vary from battery cell to battery cell. This leads to SOC variation between neighboring battery cells. The system should have the resolution to remove this variability.

- High SOC and Low SOC Equalization: Battery cells can develop SOC variation that is higher or lower than average. To achieve maximum efficiency, a system should have the ability to equalize both variations in SOC. For example, consider a system that can only equalize battery cells that have higher-than-average SOC. When one cell has a lower-than-average SOC, the system will have to decrease the energy in all other battery cells to equalize the battery pack. This would result in a substantial amount of energy that is lost in the equalization process.

• Even Energy Redistribution: When equalizing a battery cell, the energy should be redistributed evenly throughout the battery pack. The equalization process should not induce SOC variability in the other battery cells.

## 2.2 General System Structures

Several different systems have been presented in the literature. They can be separated into series, parallel and hybrid structures. The connectivity of the respective series, parallel and hybrid structures is shown in Figure 2.1. The series systems have the circuits arranged in series with each other, and they distribute energy to (from) a battery cell along the natural flow of energy within the battery pack. The parallel systems have the circuits arranged in parallel to each other, and they distribute energy to (from) a battery cell in a path that is perpendicular to the natural flow of the battery pack energy. Hybrid configurations utilize circuit characteristics from both series and parallel systems in an attempt to capture the benefits of both.

Systems that incorporate dc-to-dc converters are typically implemented in the discontinuous conduction mode, which helps to simplify the control schemes.

Consequently, the analyses presented here will also be for the discontinuous conduction mode.

Figure 2.1: General classification of BMS structures.

## 2.3 Series Systems

Series systems often utilize simpler circuit structures and require less wiring than the parallel and hybrid systems. The tradeoff is the distribution of energy to (from) a battery cell is redistributed unevenly (if redistributed at all) among the remaining battery cells. These systems are advantageous in terms of cost and are well suited for space-sensitive applications that do not require large amounts of energy to be redistributed.

# 2.3.1 Shunt-Resistor System

The only dissipative system, the Shunt-Resistor system equalizes SOC imbalance by dissipating charging energy through a switched, power resistor [16][17]. During a charging cycle, the system can shunt current around battery cells with higher-than-average SOC and allow the other battery cells to continue to charge. For *N* battery cells, the system consists of *N* electronic switches (typically MOSFETs) and *N* power resistors. A schematic diagram is shown in Figure 2.2, and a summary of component characteristics is given in Table 2.1.

Figure 2.2: Schematic diagram for the Shunt-Resistor system

Table 2.1: Summary of component characteristics for the Shunt-Resistor system

| Description    | Number | Voltage Rating |

|----------------|--------|----------------|

| MOSFET         | N      | $V_{cell}$     |

| Power Resistor | N      | $V_{cell}$     |

To examine how the Shunt-Resistor system equalizes SOC imbalance, consider the situation when the  $k^{th}$  battery cell has a higher-than-average SOC. During a charging sequence, the BMS acts to shunt the charging current around that battery cell. The other battery cells continue to receive the charging current. The average current  $I_k$  that is shunted around the  $k^{th}$  battery cell is approximated by Equation 2.1, where  $v_k$  is the voltage of the  $k^{th}$  battery cell,  $D_k$  is the duty cycle of  $S_k$ , and  $R_k$  is the resistance of the resistor.

$$I_k = \frac{v_k D_k}{R_k}$$

$k = 1, 2, ..., N$  2.1

The Shunt-Resistor system has a completely modular structure. In addition, it uses only a few, off-the-shelf components. This results in a system with a low implementation cost, and is applicable for equalization at the battery cell level. Finally, it does not induce SOC variability in the other battery cells because all excess energy is dissipated in the power resistors.

However, a primary motivator in the use of the electric motor is to increase the energy efficiency of the automobile. Since the system dissipates all of the excess energy as heat in power resistors, a shunt-resistor system is typically designed with a low power capacity. The control scheme is moderately complex, with gate drive and voltage feedback signals required for each battery cell. Finally, it only has the ability to equalize battery cells that have higher-than-average SOC.

## 2.3.2 Switched-Capacitor System

The Switched-Capacitor system equalizes SOC imbalance by charging a capacitor up to the voltage of a battery cell and discharging the energy into a neighboring battery cell with a lower voltage [18][19][20]. For *N* battery cells, the system consists of *N* single-pole, double-throw (SPDT) switches and *N*-1 capacitors. A schematic diagram is shown in Figure 2.3, and a summary of component characteristics is given in Table 2.2.

Figure 2.3: Schematic diagram for the Switched-Capacitor system

Table 2.2: Summary of component characteristics for the Switched-Capacitor system

| Description | Number | Voltage Rating |

|-------------|--------|----------------|

| SPDT Switch | N      | $V_{cell}$     |

| Capacitor   | N-1    | $V_{cell}$     |

To evaluate how the Switched-Capacitor system equalizes SOC imbalance, consider the situation when battery cell k has a higher voltage than the battery cell k+1. When the switches are in the lower position, battery cell k charges capacitor  $C_k$  up to its voltage  $v_k$ , with an average current  $I_k$ . When the switches are in the upper position, battery cell k+1 discharges capacitor  $C_k$  down to its voltage  $v_{k+1}$ , with an average current  $I_{k+1}$ . The reference directions of the average currents are shown in Figure 2.4, where  $R_{eq}$  is the equivalent resistance of the wire, switches and capacitor. The net average current between the two adjacent cells,  $I_{k,k+1}$  is approximated by Equation 2.2 [20], where  $f_s$  is the switching frequency. Without external control or a feedback loop, this current decreases

with a decreasing voltage difference. It is zero at the limit when the battery cells achieve the same voltage.

Figure 2.4: Switched-Capacitor system transferring energy from battery cell k to battery cell k+1.

$$I_{k,k+1} = \frac{v_k - v_{k+1}}{\frac{1}{f_s C_k} + R_{eq}} \quad k = 1, 2, ..., N-1$$

2.2

The Switched-Capacitor system has a completely modular setup. In addition, it utilizes only a few, off-the-shelf components. Also, it is intended to be operated continuously, thereby removing the need for a supervisory control system. This results in a system with low implementation cost that is applicable for equalization at the battery-cell level. Finally, it has the ability to equalize battery cells with both higher-than-average and lower-than-average voltages.

However, the equalization power is limited. Practical current rates of only Capacity/(500 h) and Capacity/(2000 h) (Capacity is the nominal capacity of the battery cell in A·h) are achievable at a voltage differential of 10 mV per cell [20]. In addition, the system only distributes recovered energy to neighboring battery cells. Because of its

continuous operation the energy is eventually distributed across the pack, but at the cost of compounding efficiencies. Finally, equalization is only performed when neighboring battery cells have different voltages. Some battery chemistries exhibit very small changes in voltage across large spans of SOC. When these batteries do exhibit a significant voltage difference, there could be a large variation in energy, and this system might not have the power capacity to eliminate it in a timely manner.

# 2.3.3 Current-Diverter System

The Current-Diverter system equalizes SOC imbalance by diverting charging current around an unbalanced battery cell [21]. For *N* battery cells, the system is composed of *N*-1 buck-boost converters and one flyback converter. Its components consist of *N* electronic switches (typically MOSFETs), *N*-1 inductors, *N* diodes, and one transformer. A schematic diagram is shown in Figure 2.5, and a summary of component characteristics is given in Table 2.3.

Figure 2.5: Schematic diagram for the Current-Diverter system

Table 2.3: Summary of component characteristics for the Current-Diverter system

| Description | Number | Voltage Rating        |

|-------------|--------|-----------------------|

| MOSFET      | N-1    | 2*V <sub>cell</sub>   |

| Diode       | N-1    | 2*V <sub>cell</sub>   |

| Diode       | 1      | 2*N*V <sub>cell</sub> |

| Transformer | 1      | 1:N turns ratio       |

| Inductor    | N-1    | n/a                   |

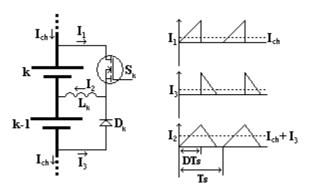

To evaluate how the Current-Diverter system equalizes SOC imbalance, consider the circuit diagram and current waveforms in Figure 2.6. In this case, the  $k^{th}$  battery cell has a higher-than-average SOC. To compensate for this, the BMS acts to divert the average charging current  $I_{ch}$  around that cell. This prevents the battery cell from being charged while the remaining cells continue to be charged. Note that any portion of  $I_{ch}$

could be diverted; for this example it has been chosen to be equal to the charging current. Therefore, the  $k^{th}$  battery cell will not receive any charging current, while the other battery cells will continue to charge as normal.

Figure 2.6: Current-Diverter system diverting charging current around the k<sup>th</sup> battery cell

Initially,  $S_k$  is switched on until its average current  $I_1$  is equal to  $I_{ch}$ . The average current  $I_1$  is defined by Equation 2.3, where  $v_k$  is the voltage of the  $k^{th}$  battery cell,  $L_k$  is the inductance of the inductor, and  $D_k$  is the duty cycle of  $S_k$ .  $S_k$  is then switched off, and the freewheeling diode conducts current until the inductor is demagnetized. The average charging current of the  $k^{th}$  battery cell is the difference between  $I_{ch}$  and  $I_1$ , and in this case results in zero amps.

$$I_1 = \frac{v_k D_k}{2L_k}$$

$k = 2, 3, ... N$  2.3

The average current of the inductor  $I_2$  is the sum of currents  $I_1$  and the average current of the diode  $I_3$ . The average charging current of the k-1 battery cell is the sum of  $I_{ch}$  and  $I_3$ , and the charging currents of the remaining battery cells are unchanged at  $I_{ch}$ .

This analysis applies to all battery cells except the first battery cell of the battery pack. To evaluate how the Current-Diverter system equalizes SOC imbalance in the first battery cell, consider the circuit diagram and waveforms in Figure 2.7. In this case, the first battery cell has a higher-than-average SOC. The BMS acts to correct this by diverting the charging current  $I_{ch}$  around it. Note that any portion of  $I_{ch}$  can be diverted; in this example it has been chosen to be all of the charging current. Therefore, the first battery cell will not receive any current from  $I_{ch}$ , while the remaining battery cells will continue to receive  $I_{ch}$ .

Figure 2.7: Current-Diverter system diverting charging current around the first battery cell

Initially,  $S_1$  is switched on until its current reaches an average current level  $I_1$ , which is set to be equal to  $I_{ch}$ . The average current  $I_1$  is approximated by Equation 2.4, where  $v_I$  is the voltage of the first battery cell,  $D_1$  is the duty cycle of  $S_1$ , and  $L_m$  is the magnetizing inductance of the transformer.  $S_1$  is then switched off, and the freewheeling diode will conduct current until the transformer is demagnetized. The average current through the diode  $I_2$ , where  $|I_{ch}| > |I_2|$ , is then redirected back into the battery pack. The

net average charging current of the first battery cell is equal to  $I_2$ , and the net average charging currents for the other battery cells are the sum of  $I_{ch}$  and  $I_2$ .

$$I_1 = \frac{v_1 D_1}{2L_m}$$

2.4

The power capability of the Current-Diverter system is greater then the previous two systems discussed, and through the proper selection of components it can be tailored to most applications. In addition, the system has a relatively modular setup; only the flyback converter must be designed for a specific battery pack. Finally, the system uses a moderate number of off-the-shelf components, with only the transformer being a custom component.

However, the control scheme is moderately complex. It requires a gate drive signal and a current feedback signal for each battery cell. The complexity in the control scheme and the moderate cost of the power electronic components make this system applicable for equalization down to groups of battery cells only (battery-module level). In addition, equalization can only be performed on battery cells with higher-than-average SOC. Finally, the redistribution of recovered energy is poor. For the buck-boost converters, the energy is redistributed to the neighboring battery cell only. This causes the neighboring battery cell to charge faster then the other battery cells in the pack, which may exacerbate the SOC variation.

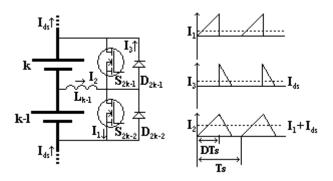

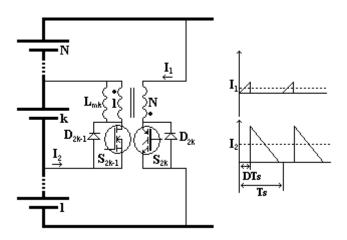

# 2.3.4 Bidirectional Current-Diverter System

An adaptation to the Current-Diverter system, the Bidirectional Current-Diverter system also equalizes SOC imbalance by diverting current around a battery cell. Both systems can divert current around a battery cell during a charging sequence; however, the bidirectional system can also divert current around a battery cell during a discharging sequence [21]. For *N* battery cells, the system is composed of *N*-2 bidirectional, buckboost converters. Its components consist of 2*N*-2 electronic switches (typically MOSFETs), 2*N*-2 diodes, and *N*-1 inductors. A schematic diagram is shown in Figure 2.8, and a summary of component characteristics is given in Table 2.4.

Figure 2.8: Schematic diagram for the Bidirectional Current-Diverter system

Table 2.4: Summary of component characteristics for the Bidirectional Current-Diverter system

| Description | Number | Voltage Rating       |

|-------------|--------|----------------------|

| MOSFET      | 2N-2   | 2* V <sub>cell</sub> |

| Diode       | 2N-2   | 2* V <sub>cell</sub> |

| Inductor    | N-1    | n/a                  |

When diverting current around an inner battery cell with a higher-than-average SOC, the circuit analysis is the same as the Current-Diverter system. The Bidirectional Current-Diverter system has the added feature that it can divert discharging current around an inner battery cell that has a lower-than-average SOC. To analyze the ability of the system to divert discharging current, consider the circuit diagram and current waveforms in Figure 2.9.

Figure 2.9: Bidirectional Current-Diverter system diverting discharging current around the k<sup>th</sup> battery cell

In this case, the  $k^{th}$  battery cell has a lower-than-average SOC. The BMS will act to correct this by diverting the discharging current  $I_{ds}$  around it. This allows the battery cell to maintain its energy while the remaining battery cells continue to discharge. Note that any portion of  $I_{ds}$  could be diverted around the battery cell; for this example, it will be the entire discharging current. This will allow the battery cell to maintain all of its energy while the remaining battery cells continue to discharge.

Initially,  $S_{2k-2}$  is switched on, which generates the average current  $I_1$ . It is then switched off, and the freewheeling diode conducts current until the inductor is demagnetized. The net average discharge current on the k-1 battery cell is the sum of  $I_1$  and  $I_{ds}$ .

The average current of the diode  $I_3$  is set to  $I_{ds}$ . The average current  $I_3$  is approximated by Equation 2.5, where  $v_k$  is the voltage of the  $k^{th}$  battery cell,  $v_{k-1}$  is the voltage of the k-1 battery cell,  $D_{2k-2}$  is the duty cycle  $S_{2k-2}$ ,  $L_{k-1}$  is the inductance of the inductor, and  $I_s$  is the switching frequency. The net average current being discharged from the  $k^{th}$  battery cell is equal to the difference between  $I_3$  and  $I_{ds}$ , which results in zero amps.

$$I_3 = \frac{v_{k-1}^2 D_{2k-2}^2 T_s}{2v_k L_{k-1}} \quad k = 1, 2, ..., N-1$$

2.5

The power capability of the Bidirectional Current-Diverter system matches the power capability of the Current-Diverter system, and likewise can be tailored to most applications. In addition, the system uses off-the-shelf components in a modular setup.

However, the control scheme is complex. It requires two gate drive signals and two current feedback signals per battery cell. The complexity in the control scheme and the cost of the components make this system applicable for equalization at only the battery-module level. In addition, the flexibility in current diversion is not completely bidirectional. The first battery cell can only be equalized when it has a higher-than-average SOC, not lower. Likewise, the last battery cell can only be equalized when it has a lower-than-average SOC. Finally, the recovered energy is only distributed to or from the neighboring battery cells, which may exacerbate the SOC variation.

## 2.4 Parallel Systems

Parallel systems provide the most even distribution of the recovered energy. The tradeoff is that they require custom transformers to provide galvanic isolation between the respective battery-cell grounds and the high-voltage bus ground. They also require more wiring than the series systems. These systems are advantageous in applications that have high-energy battery packs and require significant amounts of energy redistribution.

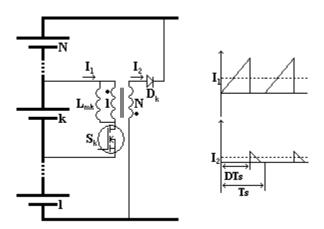

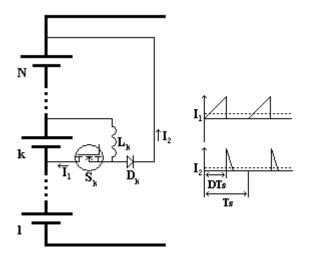

# 2.4.1 Flyback-Converter System

The Flyback-Converter system equalizes SOC imbalance by taking energy from the individual battery cells and redistributing it to the high voltage bus [22]. For *N* battery cells, the system consists of *N* transformers, *N* electrical switches (typically MOSFETs), and *N* diodes. The schematic diagram is shown in Figure 2.10, and a summary of component characteristics is given in Table 2.5.

Figure 2.10: Schematic diagram for the Flyback-Converter system

Table 2.5: Summary of component characteristics for the Flyback-Converter system

| Description | Number | Voltage Rating      |

|-------------|--------|---------------------|

| MOSFET      | N      | 2*V <sub>cell</sub> |

| Diode       | N      | $2*N*V_{cell}$      |

| Transformer | N      | 1:N turns ratio     |

The Flyback-Converter system has the ability to transfer energy from a battery cell with a higher-than-average SOC to the high-voltage bus. The recovered energy can be used to charge the entire battery pack or applied to the electric motor, depending on the current state of the vehicle. To analyze the ability of the system to transfer energy from a battery cell to the high-voltage bus, consider the circuit diagram and current waveforms in Figure 2.11.

Figure 2.11: Flyback-Converter system transferring energy from the  $\mathbf{k}^{\text{th}}$  battery cell to the high-voltage bus

In this case, the  $k^{th}$  battery cell has a higher-than-average SOC. The BMS acts to correct this by transferring energy from it to the high-voltage bus. It has determined that an average discharge current  $I_1$  from the  $k^{th}$  battery will equalize the battery pack in a reasonable amount of time. Initially,  $S_k$  is switched on until its average current reaches  $I_1$ .  $I_1$  is approximated by Equation 2.6, where  $v_k$  is the voltage of the  $k^{th}$  battery cell,  $D_k$  is the duty cycle of  $S_k$ , and  $L_k$  is the magnetizing inductance of the transformer.  $S_k$  is then switched off, and the freewheeling diode conducts current until the transformer is demagnetized. The average current of the diode  $I_2$ , where  $|I_1| > |I_2|$ , is transferred to the high-voltage bus.

$$I_1 = \frac{v_k D_k}{2L_k}$$

$k = 1, 2, ..., N$  2.6

During a discharging sequence,  $I_2$  supplements the discharging current of the battery pack in powering the electric motor. In an idle or charging sequence,  $I_2$  is redirected back into the battery pack. An idle battery pack results in the  $k^{th}$  battery being

charged with the difference between  $I_1$  and  $I_2$ , while the other battery cells are charged with  $I_2$ . A charging sequence results in the  $k^{th}$  battery cell being charged with  $I_{ch} + I_2 - I_1$ , while the other battery cells are charged with the sum of  $I_{ch}$  and  $I_2$ .

The Flyback-Converter system has the power capability that can be tailored to most applications. In addition, the setup is completely modular. Finally, it evenly redistributes the recovered energy by transferring it directly to the high-voltage bus.

However, the control scheme is moderately complex. It requires a gate drive signal and current feedback signal for each battery cell. In addition, it uses a custom designed transformer and a moderate amount of power electronics. The moderate control complexity and component cost make this system applicable for equalization at the battery module level. Finally, equalization can only be performed on battery modules with a higher-than-average SOC.

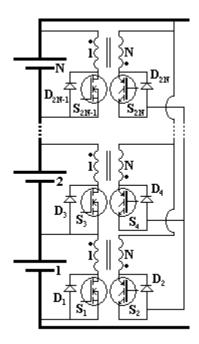

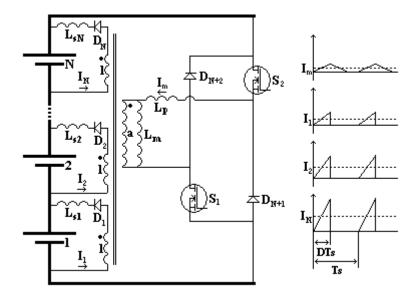

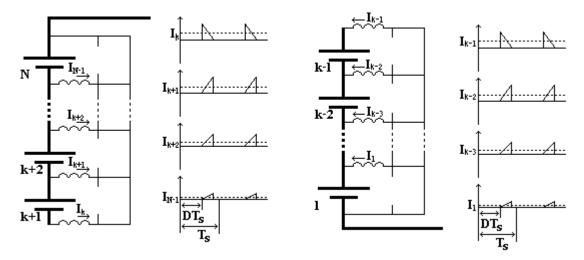

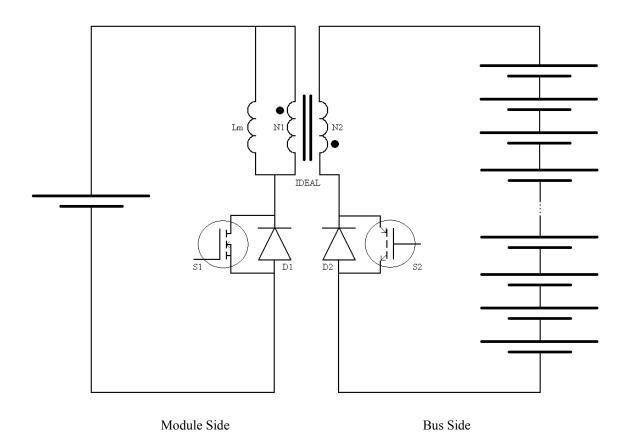

# 2.4.2 Bidirectional Flyback-Converter System

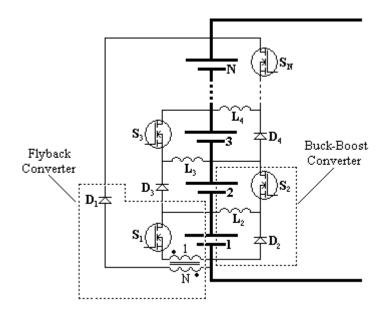

The Bidirectional Flyback-Converter system equalizes SOC imbalance by taking energy from (to) a battery cell and transferring it to (from) the high-voltage bus [23]. For *N* battery cells, the system consists of 2*N* electronic switches (typically *N* MOSFETs and *N* IGBTs), 2*N* diodes, and *N* transformers. A schematic diagram is shown in Figure 2.12, and a summary of component characteristics is given in Table 2.6.

Figure 2.12: Schematic diagram for the Bidirectional Flyback-Converter system

Table 2.6: Summary of component characteristics for the Bidirectional Flyback-Converter system

| Description | Number | Voltage Rating        |  |  |  |  |  |

|-------------|--------|-----------------------|--|--|--|--|--|

| MOSFET      | N      | 2*V <sub>cell</sub>   |  |  |  |  |  |

| Diode       | N      | 2*V <sub>cell</sub>   |  |  |  |  |  |

| IGBT        | N      | 2*N*V <sub>cell</sub> |  |  |  |  |  |

| Diode       | N      | 2*N*V <sub>cell</sub> |  |  |  |  |  |

| Transformer | N      | 1:N turns ratio       |  |  |  |  |  |

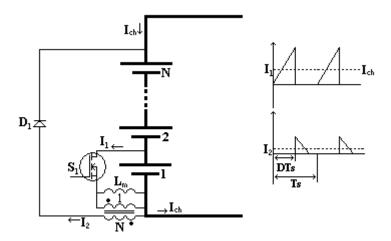

The system has the ability to transfer energy from the high-voltage bus to a battery cell a lower-than-average SOC, and to transfer energy from a battery cell with a higher-than-average SOC to the high-voltage bus. When equalizing a battery cell with a higher-than-average SOC the circuit analysis is the same as the Flyback-Converter system. To

analyze its ability to equalize a battery cell with a lower-than-average SOC, consider the circuit diagram and current waveforms in Figure 2.13.

Figure 2.13: Bidirectional Flyback-Converter system transferring energy from the high-voltage bus to the k<sup>th</sup> battery cell

In this case, the  $k^{th}$  battery cell has a lower-than-average SOC. The BMS acts to correct this imbalance by transferring energy from the high-voltage bus to this battery cell. It has determined that the average charging current  $I_2$  will equalize the imbalance of the battery pack in a reasonable amount of time. First,  $S_{2k}$  is switched on until its average current reaches  $I_1$ . It is then switched off, and the battery-cell side freewheeling diode conducts current until the transformer is demagnetized.  $I_2$  is approximated by Equation 2.7, where  $v_{pk}$  is the voltage of the battery pack,  $v_{cell}$  is the voltage of the battery cell,  $v_{cell}$  is the voltage of the battery pack,  $v_{cell}$  is the voltage of the transformer, and  $v_{cell}$  is the duty cycle of the IGBT.

$$I_2 = \frac{v_{pk}^2 D_k^2 T_s}{2N^2 v_{cell} L_k} \quad k = 1, 2, ..., N$$

2.7

When the battery pack is in a discharging state with an average current  $I_{ds}$ , where  $|I_{ds}| > |I_2| > |I_1|$ , the net average discharging current of the  $k^{th}$  battery cell is  $I_{ds} + I_1 - I_2$ . The net average discharging currents of the other battery cells are the sum of  $I_{ds}$  and  $I_1$ . When the battery pack is idle, the net average charging current of the  $k^{th}$  battery cell is the difference between  $I_2$  and  $I_1$ . The average discharging currents of the other battery cells are  $I_1$ . When the battery pack is charging with an average charging current  $I_{ch}$ , the net average charging current of the  $k^{th}$  battery cell is  $I_{ch} + I_2 - I_1$ . The net average charging currents of the other battery cells are the difference between  $I_{ch}$  and  $I_1$ .

The power capability of the Bidirectional Flyback-Converter system can be tailored to most applications. In addition, the setup is completely modular. Also, battery cells with higher-than-average SOC and lower-than-average SOC can be equalized. Finally, the recovered energy is evenly redistributed to (from) the high-voltage bus.

However, the system requires custom-designed transformers, and a significant amount of power electronics. In addition, the control scheme is complex. It requires two gate drive signals and two current feedback signals for each battery cell. The complexity in the control scheme and the high cost of its components results in the system being applicable for equalization at the battery-module level.

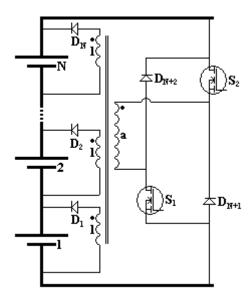

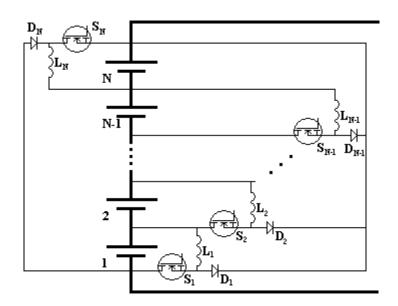

### 2.4.3 Centralized Forward-Converter System

The Centralized Forward-Converter system equalizes SOC imbalance by transferring energy from the high-voltage bus to the battery cells [24][25]. For *N* battery cells, the system consists of 2 electronic switches (typically MOSFETs), *N*+2 diodes, and

one coaxial-winding transformer. A schematic diagram is shown in Figure 2.14, and a summary of component characteristics is given in Table 2.7.

Figure 2.14: Schematic diagram for the Centralized Forward-Converter system

Table 2.7: Summary of component characteristics for the Centralized Forward-Converter system

| Description     | Number | Voltage Rating       |

|-----------------|--------|----------------------|

| MOSFET          | 2      | N* V <sub>cell</sub> |

| Diode           | 2      | $N^* V_{cell}$       |

| Diode           | N      | $V_{cell}$           |

| Coaxial-Winding |        |                      |

| Transformer     | 1      | 1:a turns ratio      |

The variation of SOC is equalized by providing different charging currents to the individual battery cells from the high-voltage bus. The charging currents to each battery cell are automatically set by its voltage. To illustrate the equalization process, consider the diagram and current waveforms shown in Figure 2.15.

Figure 2.15: The Centralized Forward-Converter system transferring current from the high-voltage bus to the individual battery cells

In this example, the first battery has the highest voltage and the  $N^{th}$  battery has the lowest voltage. First, both  $S_1$  and  $S_2$  are switched on. This applies the voltage of the battery pack  $v_{pk}$  to the primary side of the transformer. The driving impedance of the current in the primary winding is its magnetizing inductance  $L_m$  and primary leakage inductance  $L_p$ . Likewise, the driving impedances of the currents in the secondary windings are their corresponding leakage inductances  $L_k$ . The average charging currents of the battery cells are approximated by Equation 2.8, where  $v_k$  is the voltage of the  $k^{th}$  battery cell, and D is the duty cycle of the MOSFETs.

$$I_{k} = \frac{(\frac{v_{pk}}{a} - v_{k})D}{2(L_{k})} \quad k = 1, 2, ..., N$$

2.8

Then both  $S_1$  and  $S_2$  are switched off, the freewheeling diodes conduct current until the transformer is demagnetized. In this state, the secondary-side diodes are reverse biased and do not conduct current. The freewheeling diodes transition to open circuits when transformer is demagnetized.

The power capability of the Centralized Forward Converter system can be tailored to most applications. In addition, the control strategy is simple, as it only requires one gate drive signal. Finally, the energy used to charge the battery cells is sourced evenly from the high-voltage bus.

However, the system requires a custom transformer core and an *N*-signal, co-axial secondary wire, which are costly to implement. In addition, the system is not modular. The cost of the components and non-modular setup make this system applicable for equalization at the battery module level. Also, equalization can only be performed to correct lower-than-average SOC. Finally, the system is only effective when the battery chemistry has a voltage profile that is proportional to SOC.

## 2.5 Hybrid Systems

Hybrid systems utilize off-the-shelf circuit components and attempt to redistribute energy evenly to the other battery cells. They do not use electrical transformers as found in the parallel systems, but do require more wiring than the series systems. These systems are advantageous to space sensitive applications that require large amounts of energy to be redistributed.

# 2.5.1 Hybrid System #1

The Hybrid System #1 equalizes SOC imbalance by transferring energy from a battery cell with a higher-than-average SOC and distributing it to the other battery cells [26]. For *N* battery cells, the system consists of *N* electronic switches (typically MOSFETs), *N* diodes, and *N*-1 inductors. A schematic diagram is shown in Figure 2.16, and a summary of component characteristics is given in Table 2.8.

Figure 2.16: Schematic diagram of the Hybrid System #1

Table 2.8: Summary of component characteristics of the Hybrid System #1

| ge Rating |

|-----------|

|           |

|           |

|           |

|           |

To analyze the ability of the Hybrid System #1 to equalize SOC imbalance, consider the case when the  $k^{th}$  battery cell has a higher-than-average SOC. To correct this, the BMS switches  $S_k$  on, which generates the average discharge current  $I_d$  that is shown in Figure 2.17. Equation 2.9 approximates  $I_d$ , where  $v_k$  is the voltage of the  $k^{th}$  battery cell,  $D_k$  is the duty cycle of  $S_k$ ,  $T_s$  is the switching period,  $L_k$  is the inductance of the  $k^{th}$  inductor, and  $L_{k-1}$  is the inductance of the k-1 inductor.

Figure 2.17: The Hybrid System #1 discharging current from the k<sup>th</sup> battery cell

$$I_d = \frac{v_k D_k^2 T_s}{4(L_k + L_{k-1})} \quad k = 2, 3, ..., N - 1$$

2.9

When  $I_d$  reaches a desired level that has been determined to equalize the SOC imbalance,  $S_k$  is switched off. The energy is then redistributed to the other battery cells, as shown in Figure 2.18. The average inductor currents  $I_k$  and  $I_{k-1}$  are approximated by Equation 2.10 and Equation 2.11, respectively.

Figure 2.18: The Hybrid System #1 redistributing energy from the k<sup>th</sup> battery cell to the other battery cells

$$I_{k} = \frac{v_{k}^{2} D_{k}^{2} T_{s}}{8L_{k} \sum_{i=k+1}^{N} v_{i}} \quad k = 2, 3, ..., N-1$$

2.10

$$I_{k-1} = \frac{v_k^2 D_k^2 T_s}{8L_{k-1} \sum_{i=1}^{k-1} v_i} \quad k = 2, 3, ..., N-1$$

2.11

The voltages present in the system induce currents to flow in the other inductors as well. The average inductor currents above the  $k^{th}$  battery cell are approximated by Equation 2.12, and the average inductor currents below the  $k^{th}$  battery cell are approximated by Equation 2.13.

$$I_{x} = \frac{v_{k}^{2} D_{k}^{2} T_{s} \sum_{j=x+1}^{N} v_{j}}{8 L_{x} \left(\sum_{j=k+1}^{N} v_{j}\right)^{2}} \quad x = k+1, k+2, ..., N-1$$

2.12

$$I_{x} = \frac{v_{k}^{2} D_{k}^{2} T_{s} \sum_{j=1}^{x} v_{j}}{8 L_{x} (\sum_{j=1}^{k-1} v_{j})^{2}} \quad x = 1, 2, ..., k-2$$

2.13

The average battery cell currents above the *k*th battery cell are approximated by Equation 2.14, and the average battery cell currents below the *k*th battery cell are approximated by Equation 2.15.

$$I_{cellx} = \sum_{i=k+1}^{x} I_{i-1}$$

$x = k+2, k+3, ..., N$  2.14

$$I_{cellx} = \sum_{i=k-1}^{x} I_i$$

$x = 1, 2, ..., k-1$  2.15

The equalization power of the Hybrid System #1 can be tailored to most applications. In addition, the use of off-the-shelf parts permits a moderate implementation cost. Finally, it utilizes a completely modular setup.

However, the control scheme is moderately complex. It requires a gate drive signal and current feedback signal for each battery. The moderate control complexity and implementation cost makes this system applicable for equalization at the battery module level. In addition, equalization can only be performed on a battery cell with a higher-than-average SOC. Finally, the redistribution of energy is uneven. The closer a battery cell is to the battery cell being equalized, the less charging current it receives.

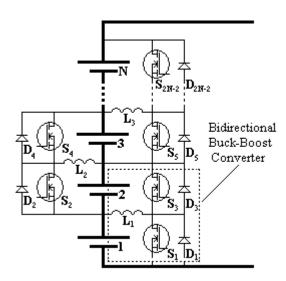

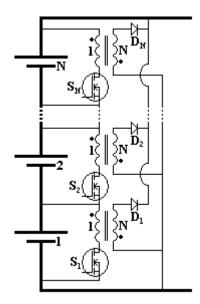

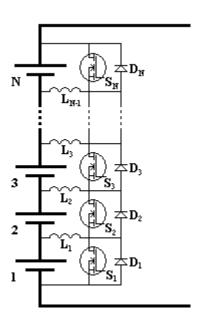

# 2.5.2 Hybrid System #2

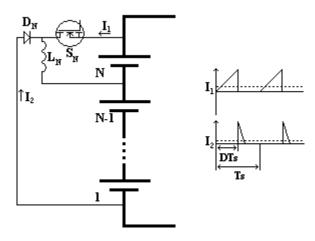

The Hybrid System #2 equalizes SOC imbalance by discharging energy from battery cells with higher-than-average SOC. For the top battery cell in the battery pack, the energy is redistributed to the battery cells below it. For all other battery cells, the energy is redistributed to the battery cells that are above them [27][28][29][30]. For *N* battery cells, the system consists of *N* electrical switches (typically MOSFETs), *N* diodes, and *N* inductors. A schematic diagram is shown in Figure 2.19, and a summary of component characteristics is given in Table 2.9.

Figure 2.19: Schematic diagram of the Hybrid System #2

Table 2.9: Summary of component characteristics of the Hybrid System #2

| Description | Number | Voltage Rating                                                            |

|-------------|--------|---------------------------------------------------------------------------|

| MOSFET      | N      | $V_{cell}$                                                                |

|             |        | 2: N*V <sub>cell</sub>                                                    |

| Diode       | N      | 1: (N-1)*V <sub>cell</sub> , (N-2)*V <sub>cell</sub> ,, V <sub>cell</sub> |

| Inductor    | N      | n/a                                                                       |

To analyze how the Hybrid System #2 equalizes SOC imbalance, consider the case when the  $k^{\text{th}}$  battery cell a higher-than-average SOC, where  $1 \ge k \ge N-1$ . The BMS acts to correct this variation by discharging energy from the battery cell and redistributing it to the battery cells that are higher up on the battery pack. The circuit diagram and typical current waveforms are shown in Figure 2.20.

Figure 2.20: The Hybrid System #2 discharging current from the k<sup>th</sup> battery cell

The BMS has determined that the average discharging current  $I_1$  will equalize the SOC variability of the battery pack.  $S_k$  is switched on, until its average current reaches  $I_1$ . This current is approximated by Equation 2.16, where  $v_k$  is the voltage of the battery cell,  $D_k$  is the duty cycle of  $S_k$ , and  $L_k$  is the inductance of the inductor.  $S_k$  is then switched off, and the diode conducts current until the inductor is demagnetized. The average current  $I_2$  charges the battery cells that are above the k<sup>th</sup> battery cell in the battery pack.

$$I_1 = \frac{v_k D_k}{2L_k}$$

$k = 1, 2, ..., N-1$  2.16

To analyze how the Hybrid System #2 equalizes SOC imbalance in the  $N^{th}$  battery cell, consider the case when it has a higher-than-average SOC. The BMS acts to correct this variation by discharging energy from it and redistributing the energy to the battery cells that are below it. The circuit diagram and typical current waveforms are shown in Figure 2.21.

Figure 2.21: The Hybrid System #2 discharging current from the N<sup>th</sup> battery cell

The BMS has determined that an average discharge current  $I_1$  will equalize the SOC variation.  $S_N$  is switched on until its average current reaches  $I_1$ .  $I_1$  is approximated by Equation 2.17, where  $v_N$  is the voltage of the  $N^{th}$  battery cell,  $D_N$  is the duty cycle of  $S_N$ , and  $L_N$  is the inductance of the inductor.  $S_N$  is then switched off, and the freewheeling diode conducts current until the inductor is demagnetized. The average current  $I_2$  charges the other battery cells in the battery pack.

$$I_1 = \frac{v_N D_N}{2L_N}$$

2.17

The equalization power of the Hybrid System #2 can be tailored to most applications. In addition, the use of off-the-shelf components keeps the implementation cost moderate. Finally, it utilizes a relatively modular setup, with only the  $N^{th}$  circuit requiring its design to be specific to the battery pack.

However, the control system is moderately complex. It requires a gate drive signal and current feedback signal for each battery cell. The moderate control complexity implementation cost make the system applicable for equalization at the battery module level. In addition, equalization can only be performed on battery modules with higher-than-average SOC. Finally, the redistribution of energy is uneven. Except for the  $N^{th}$  battery cell, all other battery cells redistribute the recovered energy unevenly.

# 2.6 System Selection for the Penn State Research Vehicles

To determine which system to implement for the Penn State research vehicles, the evaluation criteria are weighted based on importance to the project. Each criterion is compared to the other criteria. A score of one indicates the criterion is more important than the other criterion, and a score of zero indicates that it is less important than the other criterion. The scores of each criterion are totaled, and then a weight factor is determined. The weight factor is the ratio of the score of the criterion to the total of all criteria scores. The higher the weight factor, the more important it is to the research vehicles. The results are shown in Table 2.10.

Table 2.10: Criteria weight factors for the Penn State research vehicles

| ±≒                                                                                                                                    |              |          |               |                 |                  | _       |                 |                  |       |              |     | _            |             | _              |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|---------------|-----------------|------------------|---------|-----------------|------------------|-------|--------------|-----|--------------|-------------|----------------|

| Weig<br>Facto                                                                                                                         |              | 0.25     | 0.15          |                 | 0.05             | 0.00    |                 |                  | 0.05  |              |     | 0.20         |             | 0 30           |

| Total<br>Score                                                                                                                        |              | ω        | m             |                 | -                | 0       |                 |                  | -     |              |     | 적            |             | ی              |

| Even Energy Total Weight<br>Redistribution Score Factor                                                                               |              | 0        | 0             |                 | 0                | 0       |                 |                  | 0     |              |     | 0            |             | >              |

| High and Low<br>SOC Equalization                                                                                                      |              | -        | 0             |                 | 0                | 0       |                 |                  | 0     |              |     | ×            |             |                |

| Equalization at the High and Low Even Energy   Total   Weight Battery Cell Level   SOC Equalization   Redistribution   Score   Factor |              | _        | 1             |                 | 0                | 0       |                 |                  | ×     |              |     | _            |             | _              |

| Expense                                                                                                                               |              | _        | -             |                 | 1                | ×       |                 |                  | 0     |              |     | -            |             | _              |

| Equalization Modular Simple / Robust Power Setup Control Strategy Expense                                                             |              | -        | 1             |                 | Х                | 0       |                 |                  | 1     |              |     | -            |             | _              |

| Modular<br>Setup                                                                                                                      |              | <u>_</u> | ×             |                 | 0                | 0       |                 |                  | 0     |              |     | <u></u>      |             | -              |

| Equalization<br>Power                                                                                                                 |              | ×        | 0             |                 | 0                | 0       |                 |                  | 0     |              |     | 0            |             |                |

|                                                                                                                                       | Equalization | Power    | Modular Setup | Simple / Robust | Control Strategy | Expense | Equalization at | the Battery Cell | Level | High and Low | 200 | Equalization | Even Energy | Redistribution |

The ability to evenly redistribute energy to (from) the battery pack is the most important criterion. Intuitively this makes sense, because a system that induces SOC variability in other battery cells is counter-productive. The second most important criterion is the ability to generate substantial equalization power. A design goal of 160 W (10 A) was established to provide enough equalization power to eliminate the variability in the 100-A·h and 95-A·h battery packs. The third most important criterion is the ability to equalize both higher-than-average and lower-than-average SOC. With significant equalization expected, the flexibility to equalize both situations is desired to reduce efficiency losses. The fourth most important criterion is to have a modular setup. The system must be able to be adapted to two differently sized battery packs.

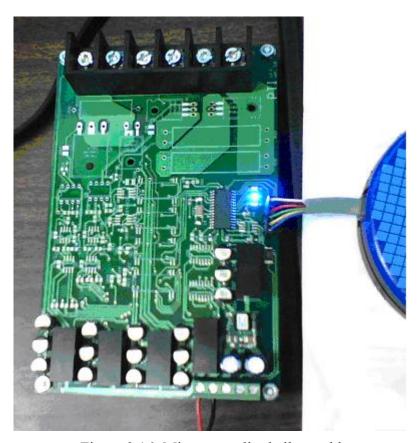

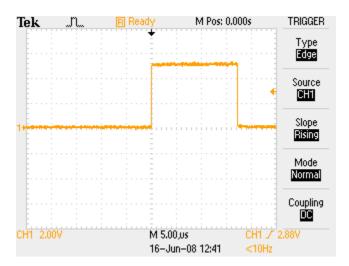

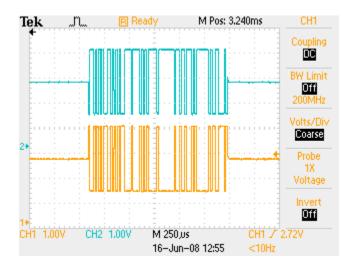

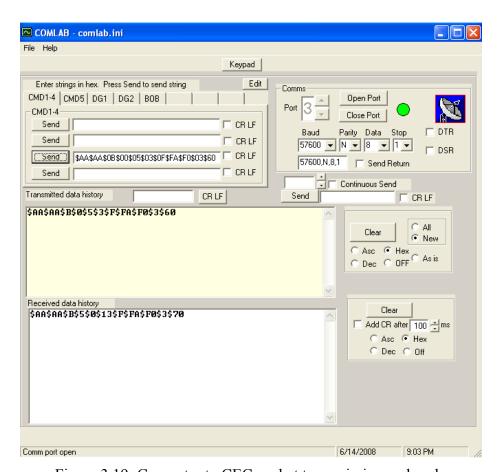

The criteria that were considered least important were a simple/robust control strategy, equalization at the battery cell level, and expense. It is acceptable to use the amount of control that is required to achieve the desired criteria, as long as a fail-safe design is followed. Equalization at the battery cell level is not tremendously important, because the batteries are packaged in ten-cell battery modules. When a failure is acknowledged, the battery module will be replaced. Finally, low expense is not important because it is being developed as a research vehicle, not a commercial vehicle.