# The Pennsylvania State University The Graduate School

# TOWARD UNDERSTANDING THE ELECTRICAL PROPERTIES OF METAL/SEMICONDUCTOR SCHOTTKY CONTACTS: THE EFFECTS OF BARRIER INHOMOGENEITIES AND GEOMETRY IN BULK AND NANOSCALE STRUCTURES

A Dissertation in

Engineering Science and Mechanics

by

Karthik Sarpatwari

© 2009 Karthik Sarpatwari

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2009

The thesis of Karthik Sarpatwari was reviewed and approved\* by the following:

Osama O. Awadelkarim Professor of Engineering Science and Mechanics Dissertation Co-Advisor, Co-Chair of Committee

Suzanne Mohney Professor of Materials Science and Engineering Dissertation Co-Advisor, Co-Chair of Committee

Bernhard R. Tittmann Professor of Engineering Science and Mechanics Schell Professor

Samia A. Suliman Assistant Professor of Engineering Science and Mechanics

Suman Datta Associate Professor of Electrical Engineering

Judith A. Todd P. B. Breneman Department Head of Engineering Science and Mechanics

<sup>\*</sup>Signatures are on file in the Graduate School.

#### **Abstract**

The work presented in this thesis comprises of two parts. Part I deals with Schottky contacts to the wide bandgap (WBG) semiconductors SiC, GaN and ZnO. These semiconductors offer great promise for a wide variety of electronic and optoelectronic applications. Schottky barriers to WBG semiconductors are attractive in particular for high temperature/high power diodes, photodetectors, and gas sensors. However, the Schottky barriers exhibit non-ideal behavior, due in part to inhomogeneities originating from immature crystal growth and device processing technologies. Apart from being a versatile electronic component, the Schottky diode is a valuable test structure. The Schottky contact is routinely used to probe substrate and epilayer quality by different electrical characterization techniques.

It is well established that the current-voltage-temperature (I-V-T) characteristics of Schottky contacts are routinely affected by the presence of barrier height inhomogeneities (BHI). Consequently, Schottky diode parameters such as the Schottky barrier height and the Richardson constant extracted using the I-V-T measurements can deviate from their actual values. The effects of BHI on the extracted Schottky barrier height have been studied in the literature. However, the effects of BHI on the Richardson constant have not been thoroughly explored and are the focus of the first part of this thesis. Based on the inhomogeneous Schottky barrier model provided by Tung, a new method for the extraction of the Richardson constant determination of n-type ZnO and GaN. Excellent agreement with the theoretical value is obtained in both cases.

The advent of the nanoelectronics era has resulted in the Schottky contact evolving from the relatively simple, planar structure into a more complex structure. Compared to bulk Schottky contacts, the Schottky barrier properties are expected to be widely different at the nanoscale. For example, the I-V characteristics of nanoscale Schottky contacts are affected by the contact size and geometry. Due to the increased surface-to-volume ratio, the conduction properties of nanoscale Schottky contacts are also influenced by surface conditions such as surface charge and traps. Depending on contact size, geometry and surface conditions, an enhanced tunneling current contribution can be expected, further distorting the I-Vcharacteristics from the simple thermionic emission model. Determination of the true Schottky barrier height in nanoscale contacts to semiconductor nanowires is important from both technological and fundamental scientific perspectives. In the second part of this thesis, we employ a simulation-based approach to study the conduction properties of an axial Schottky nanocontact to a surround-gate nanowire. A systematic study of the effects of surface charge on the I-V characteristics of the axial nano Schottky/nanowire system is undertaken. Based on the study, a method is proposed to extract the true Schottky barrier height from the I-V characteristics. The proposed method can serve as a valuable aid for interpreting experimental I-V data and can facilitate exploration of size effects on the Schottky barrier formation at the nanoscale.

# **Table of Contents**

| List o | Figures                                       | viii |

|--------|-----------------------------------------------|------|

| List o | Tables                                        | xii  |

| Ackn   | wledgments                                    | xiii |

| Chap   | er 1 Schottky barrier: Modeling and Physics   | 1    |

| 1.1    | Semiconductor surface                         | 1    |

| 1.2    | MS interface                                  | 4    |

|        | 1.2.1 Gap state models                        | 5    |

| 1.3    | Carrier transport                             | 10   |

|        | 1.3.1 Thermionic emission                     |      |

|        | 1.3.2 Observation of BHI                      | 15   |

| 1.4    | BHI framework                                 | 17   |

|        | 1.4.1 Zero-order model                        | 17   |

|        | 1.4.2 First-order interacting model           | 18   |

| 1.5    | WBG semiconductors                            |      |

|        | 1.5.1 Substrate growth processes              |      |

|        | 1.5.2 Doping, etching and annealing processes |      |

| 1.6    | Contacts to WBG semiconductors                | 31   |

| 1.7    | Thesis organization: Part I                   |      |

| 1.8    | Contacts at nano dimensions                   |      |

|        | 1.8.1 Scaling of Schottky contacts            |      |

|        | 1.8.2 Interface and surface effects           | 36   |

|        | 1.8.3 Size and geometry effects               | 38   |

| 1.9    | Thesis organization: Part II                  | 40   |

| Chap   | er 2 Minority carrier injection               | 42   |

| 2.1    | Introduction                                  | 42   |

| 2.2    | Experimental procedure                        | 44   |

|                  | 2.2.1 Diode fabrication                                       | 44         |

|------------------|---------------------------------------------------------------|------------|

| 2.3              | Electrical characterization                                   | 47         |

|                  | 2.3.1 $I$ - $V$ and $C$ - $V$                                 |            |

|                  | 2.3.2 Transient measurements                                  | 48         |

| 2.4              | Results and Discussion                                        | 51         |

| Chapte           | er 3 Effects of barrier height inhomogeneities on Richard-    |            |

|                  | son constant determination                                    | 61         |

| 3.1              | Introduction                                                  | 61         |

| 3.2              | Review of existing methods                                    | 63         |

|                  | 3.2.1 Temperature dependence of $\Phi_B$                      | 65         |

|                  | 3.2.2 Flat band barrier height analysis                       | 66         |

|                  | 3.2.3 Werner and Güttler's model                              | 68         |

|                  | 3.2.4 Tung's model                                            | 69         |

| 3.3              | Extended inhomogeneity analysis                               | 74         |

|                  | 3.3.1 $n$ - $\Phi_{\rm B}$ and $T_0$ analysis                 | 74         |

|                  | 3.3.2 Richardson plot                                         | 79         |

|                  | 3.3.3 Application of existing methods                         | 80         |

| 3.4              | Proposed approach                                             | 84         |

| 3.5              | Application to $IrO_x/n$ -ZnO $I$ - $V$ - $T$ characteristics | 88         |

| 3.6              | Application to Au/Ni/n-GaN $I$ - $V$ - $T$ data               | 93         |

|                  | 3.6.1 Fabrication procedure                                   | 93         |

|                  | 3.6.2 Device characterization                                 | 93         |

| 3.7              | Summary of results                                            | 97         |

| $\mathbf{Chapt}$ | ě v ě                                                         |            |

|                  |                                                               | 100        |

| 4.1              | Introduction                                                  |            |

| 4.2              | Simulated device structure and parameters                     |            |

| 4.3              | Gate bias effects                                             |            |

| 4.4              | $n$ - $\Phi_{\rm B}$ analysis                                 |            |

|                  | 4.4.1 Effect of NW doping density                             |            |

|                  | 4.4.2 Effect of temperature                                   |            |

|                  | 4.4.3 Effect of interface traps                               |            |

|                  | 4.4.4 Effect of gate overlap                                  |            |

| 4 5              | 4.4.5 Image force lowering effect                             |            |

| 4.5              | Application to experimental data                              |            |

|                  | 4.5.1 Fabrication procedure                                   |            |

| 16               |                                                               | 124<br>124 |

| 4 ()             | VARIATION/115                                                 | 1 / 4      |

| Chapte  | er 5 Low frequency three terminal charge pumping applied |     |

|---------|----------------------------------------------------------|-----|

|         | to silicon nanowire field-effect-transistors             | 127 |

| 5.1     | Introduction                                             | 127 |

| 5.2     | Experimental procedure                                   | 129 |

| 5.3     | Results and discussions                                  | 131 |

| 5.4     | Conclusion                                               | 138 |

| Chapte  | er 6 Conclusions and Future Work                         | 139 |

| 6.1     | Contacts to WBG Semiconductors                           | 139 |

| 6.2     | Contacts to Nanowires                                    | 141 |

| 6.3     | Future Work                                              | 143 |

| Appen   | dix A Non-technical abstract                             | 144 |

| Bibliog | graphy                                                   | 146 |

# **List of Figures**

| 1.1 | Band bending and surface dipole under surface depletion and accu-                                                                                                                 |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | mulation conditions                                                                                                                                                               | 3  |

| 1.2 | Band diagram of the Schottky metal/semiconductor contact under                                                                                                                    |    |

|     | equilibrium conditions                                                                                                                                                            | 4  |

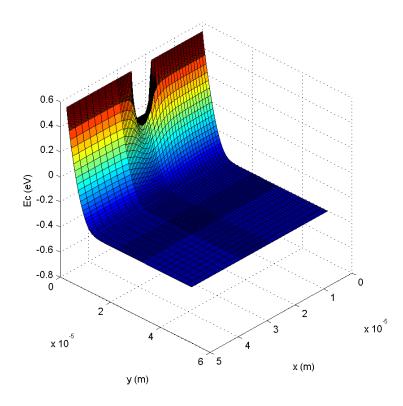

| 1.3 | Pinch-off effect of the high barrier region on the embedded low                                                                                                                   |    |

|     | barrier region                                                                                                                                                                    | 20 |

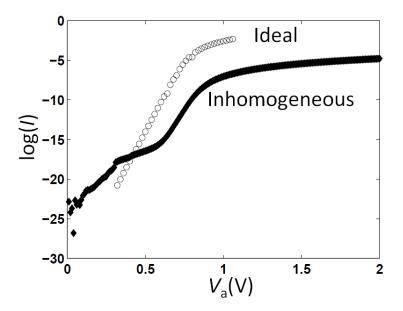

| 1.4 | Typical current-voltage response of an ideal and inhomogeneous diode                                                                                                              | 21 |

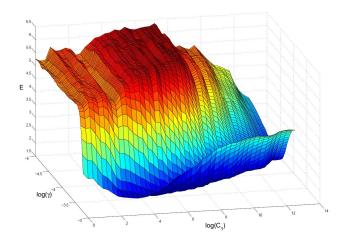

| 1.5 | Energy topography in $C_1$ and $\gamma$ space for inhomogeneous diodes                                                                                                            | 24 |

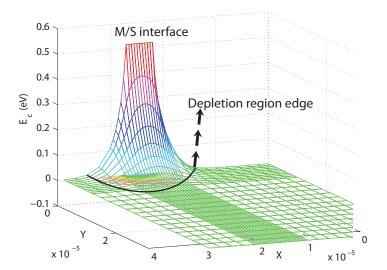

| 1.6 | Barrier profile for the case of a nanoscale contact to a bulk semi-<br>conductor. Figure also shows the isopotential contours indicating                                          |    |

|     | the depletion region edge profile                                                                                                                                                 | 38 |

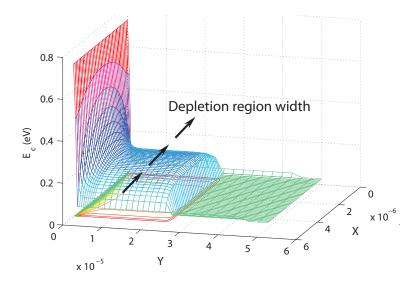

| 1.7 | Barrier profile for a nanocontact to a nanowire with positive charge                                                                                                              | 90 |

| 1.1 | placed along the nanowire length. Isopotential contours depicting                                                                                                                 |    |

|     | the depletion region edge have also been shown                                                                                                                                    | 39 |

|     | the depletion region edge have also been shown.                                                                                                                                   | 00 |

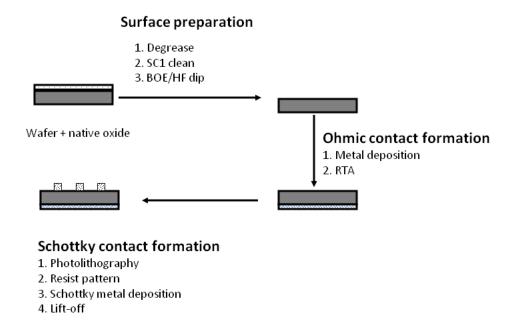

| 2.1 | Summary of Schottky diode fabrication process flow                                                                                                                                | 45 |

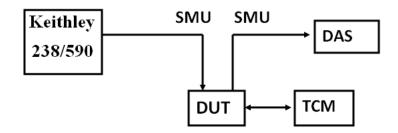

| 2.2 | Schematic of a general $I$ - $V$ - $T/C$ - $V$ - $T$ measurement                                                                                                                  | 47 |

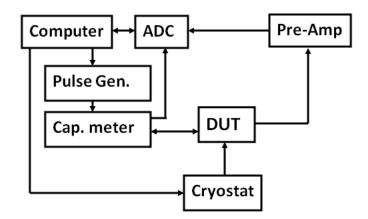

| 2.3 | Block diagram schematic of a typical DLTS experiment                                                                                                                              | 49 |

| 2.4 | Input voltage pulse train and corresponding capacitance transient                                                                                                                 |    |

|     | output from the DUT                                                                                                                                                               | 50 |

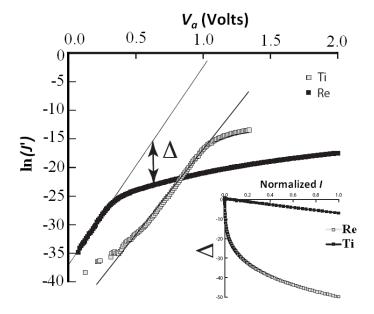

| 2.5 | Typical $J$ - $V$ characteristics of the Re and Ti/4H-SiC Schottky diodes.<br>The y-axis in this case is $\ln \left( \frac{J}{A^*T^2} \right)$ and is denoted as $\ln (J')$ . The |    |

|     | inset shows the parameter $\Delta$ as a function of normalized current                                                                                                            |    |

|     | for titanium and rhenium diodes (as described in Section 2.4)                                                                                                                     | 52 |

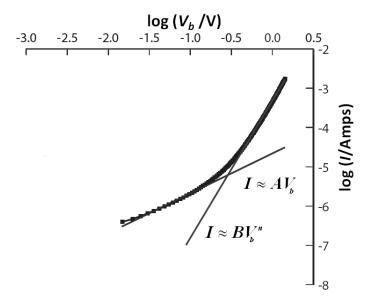

| 2.6 | Current as a function of potential drop across SiC bulk showing                                                                                                                   |    |

|     | typical space charge limited current behavior                                                                                                                                     | 55 |

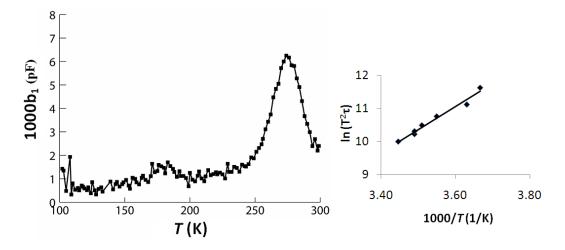

| 2.7 | DLTS signal from the Re/4H-SiC Schottky diode. Inset shows the                                                                                                                    |    |

|     | Arrhenius plot for the $Z_1$ trap                                                                                                                                                 | 56 |

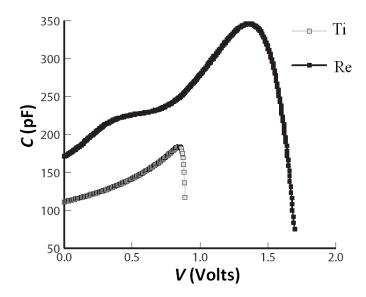

| 2.8 | Forward bias capacitance-voltage curve of Re and Ti/4H-SiC Schot-                                                                                                                 |    |

|     | tky diodes                                                                                                                                                                        | 58 |

| 3.1 | I- $V$ - $T$ characteristics simulated using Tung's equations. A homoge-                                                                                                          |    |

| J.1 | neous barrier height of 1.2 eV, $C_1$ of $10^7$ cm <sup>-2</sup> and $\sigma$ of $10^{-4}$ cm <sup>2/3</sup> eV <sup>1/3</sup>                                                    |    |

|     |                                                                                                                                                                                   | 73 |

|     | have been used in this case                                                                                                                                                       | 19 |

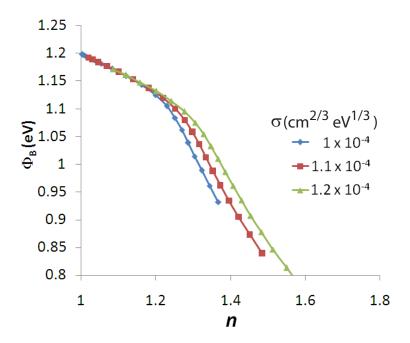

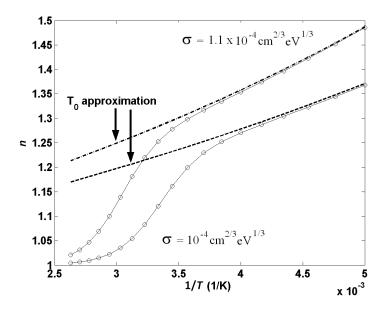

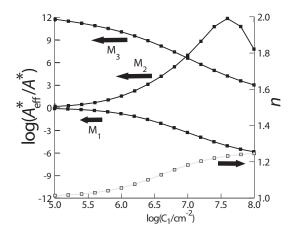

| $n$ - $\Phi_{\text{Beff}}$ plot for devices simulated with different $\sigma$ values and a patch density of $C_1 = 10^7 \text{cm}^{-2}$ . A homogeneous barrier height of 1.2 eV |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| was used in the simulation                                                                                                                                                       |                                                                                                         | 75                                                                                                                                                                                                                                                                                                       |

| Temperature dependence of the extracted ideality factor for two dif-                                                                                                             |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| barrier height of 1.2 eV is assumed                                                                                                                                              |                                                                                                         | 76                                                                                                                                                                                                                                                                                                       |

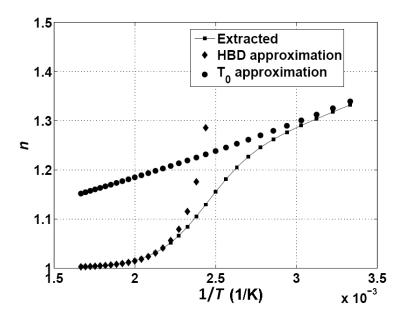

| Extracted ideality factor, $T_0$ approximation and HBD approxima-                                                                                                                |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| tion for a simulated device                                                                                                                                                      |                                                                                                         | 77                                                                                                                                                                                                                                                                                                       |

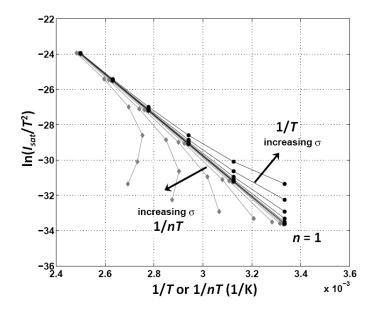

| Effect of $\sigma$ on the Richardson and modified Richardson plot. Larger                                                                                                        |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| 1 0                                                                                                                                                                              |                                                                                                         | 79                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| v e                                                                                                                                                                              |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| - · · · · · · · · · · · · · · · · · · ·                                                                                                                                          |                                                                                                         | 81                                                                                                                                                                                                                                                                                                       |

| 1                                                                                                                                                                                |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| -                                                                                                                                                                                |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| and $\sigma = 1 \times 10^{-4} \text{ cm}^{2/3} \text{ eV}^{-1/3}$ were used in the simulations. In                                                                              |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| · · ·                                                                                                                                                                            |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         | 82                                                                                                                                                                                                                                                                                                       |

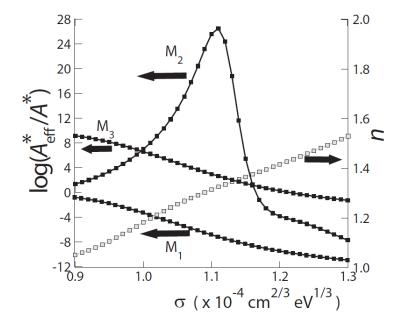

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| · 7==                                                                                                                                                                            |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| have been assumed in this case                                                                                                                                                   |                                                                                                         | 86                                                                                                                                                                                                                                                                                                       |

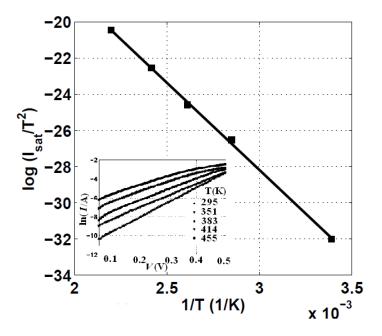

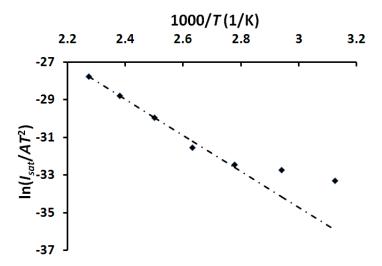

| Typical Richardson plot extracted from $I$ - $V$ - $T$ data (shown in the                                                                                                        |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| inset) of a Schottky contact to n-ZnO. From the I-V data at differ-                                                                                                              |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| ent temperatures, $n$ and $I_{\text{sat}}$ can be extracted using Eq. 3.1                                                                                                        |                                                                                                         | 89                                                                                                                                                                                                                                                                                                       |

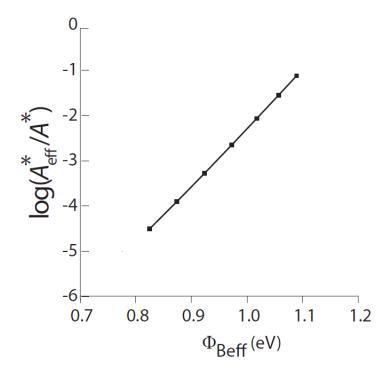

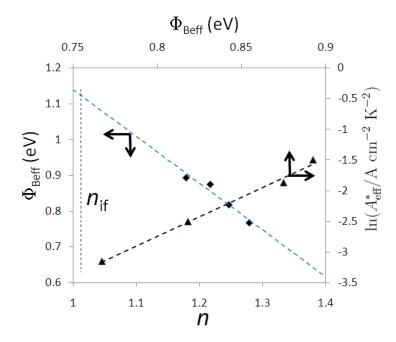

| Linear correlation between $\ln(A_{\text{eff}}^*)$ and $\Phi_{\text{Beff}}$ obtained from the                                                                                    |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                            |                                                                                                         | 91                                                                                                                                                                                                                                                                                                       |

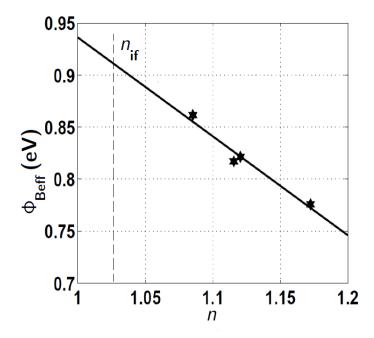

| $\Phi_{\text{Beff}}$ -n plot used to determine the homogeneous barrier height of                                                                                                 |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                  |                                                                                                         | 92                                                                                                                                                                                                                                                                                                       |

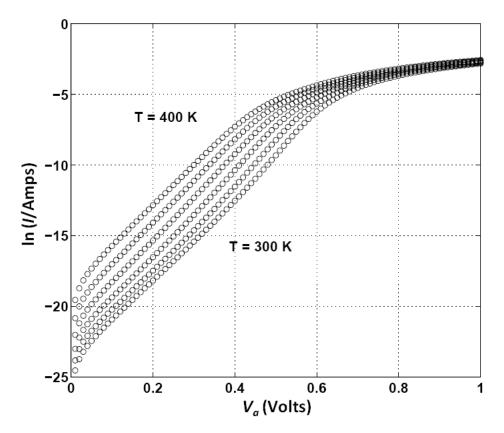

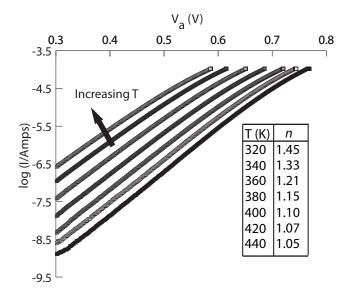

| Typical $I$ - $V$ - $T$ characteristics measured for Au/Ni/n-GaN Schottky                                                                                                        |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| diodes                                                                                                                                                                           |                                                                                                         | 94                                                                                                                                                                                                                                                                                                       |

| Typical Richardson plot obtained for the Au/Ni/n-GaN Schottky                                                                                                                    |                                                                                                         |                                                                                                                                                                                                                                                                                                          |

| diode                                                                                                                                                                            |                                                                                                         | 95                                                                                                                                                                                                                                                                                                       |

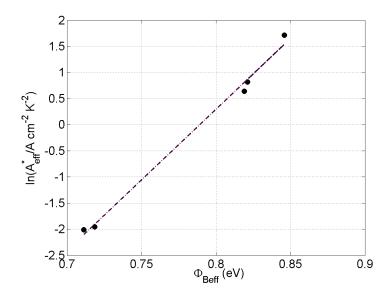

| Linear correlations between $n$ - $\Phi_{\text{Beff}}$ values and $\Phi_{\text{Beff}}$ - $\ln(A_{\text{eff}}^*)$ values                                                          |                                                                                                         | 96                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                  | density of $C_1=10^7 {\rm cm}^{-2}$ . A homogeneous barrier height of 1.2 eV was used in the simulation | density of $C_1=10^7 {\rm cm}^{-2}$ . A homogeneous barrier height of 1.2 eV was used in the simulation. Temperature dependence of the extracted ideality factor for two different $\sigma$ values. A patch density of $1\times10^7 {\rm cm}^{-2}$ and a homogeneous barrier height of 1.2 eV is assumed |

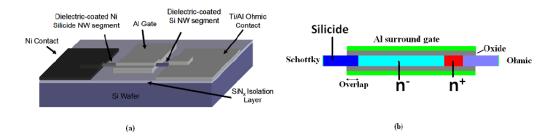

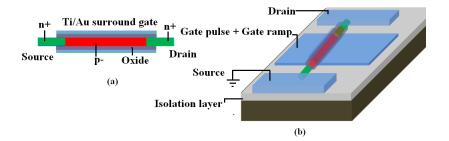

| 4.1  | (a) Schematic of a surround-gate nickel silicide/n-Si NW Schot-<br>tky diode structure. The specific metals shown were used in the |     |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | nanofabricated device described later in the paper, while the sim-                                                                 |     |

|      | ulations are more general for metallic and Si segments. (b) Cross-                                                                 |     |

|      | sectional schematic showing gate and silicide overlap                                                                              | 102 |

| 4.2  | Typical $I$ - $V$ characteristics simulated using SDEVICE for the struc-                                                           | 102 |

| 4.2  | ture shown in Figure 4.1                                                                                                           | 103 |

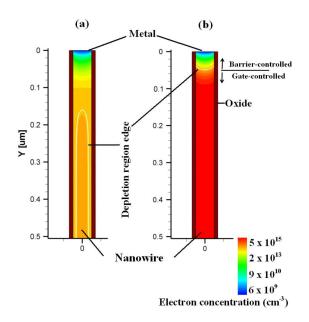

| 4.3  | Depletion region edge profile under (a) surface depletion and (b)                                                                  | 100 |

| 4.0  | surface accumulation conditions                                                                                                    | 106 |

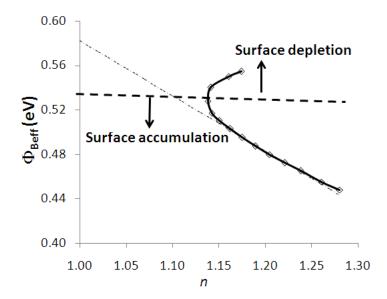

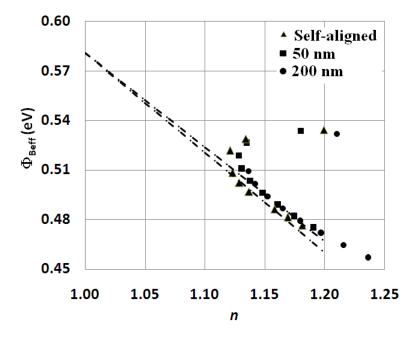

| 4.4  | Typical $n$ - $\Phi_{\text{Beff}}$ plot constructed using values extracted from $I$ - $V$                                          | 100 |

| 1.1  | characteristics at different gate biases                                                                                           | 107 |

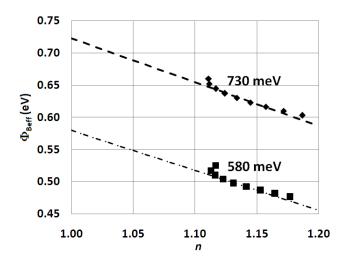

| 4.5  | Linear correlation between $n$ and $\Phi_{\text{Beff}}$ for two different input barrier                                            | 101 |

| 1.0  | height cases. Gate bias values ranging between 0.2–1 V were used                                                                   |     |

|      | in both cases                                                                                                                      | 109 |

| 4.6  | Effect of nanowire doping density on the $n$ - $\Phi_{\text{Beff}}$ plot. An input                                                 | 100 |

| 1.0  | Schottky barrier height of 580 meV, oxide/nanowire interface trap                                                                  |     |

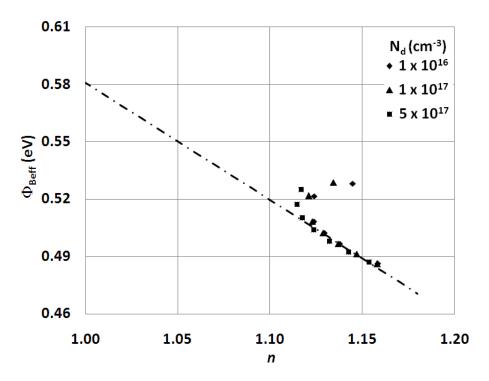

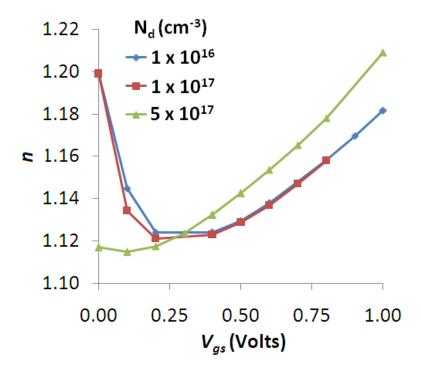

|      | density of $1 \times 10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> and $T = 300$ K have been assumed.                                 | 110 |

| 4.7  | Extracted ideality factor as a function of $V_{qs}$ for different nanowire                                                         |     |

|      | doping densities.                                                                                                                  | 111 |

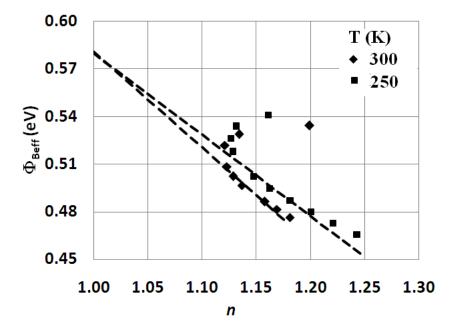

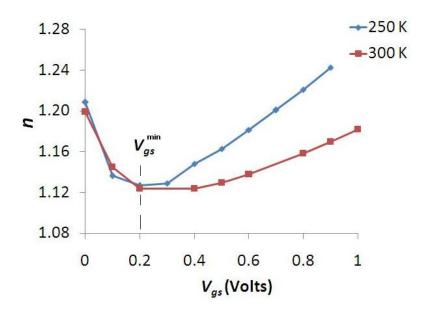

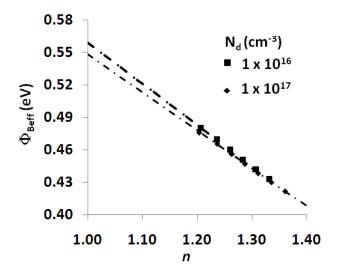

| 4.8  | Effect of temperature on the $n$ - $\Phi_{\text{Beff}}$ plot for the case of a nanowire                                            |     |

|      | doped to $10^{16}$ cm <sup>-3</sup> with an interface trap density of $10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> .                |     |

|      | In this case, an input Schottky height of 580 meV has been used                                                                    | 112 |

| 4.9  | $n$ - $V_{qs}$ variation for different temperatures                                                                                | 114 |

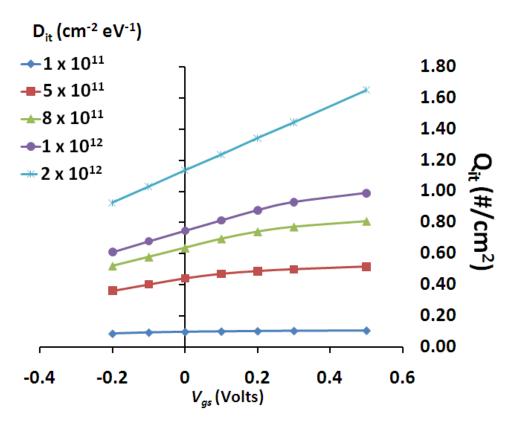

| 4.10 | Trapped interface charge (for different interface trap densities) as a                                                             |     |

|      | function of the applied gate bias                                                                                                  | 115 |

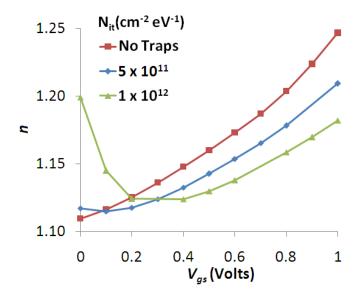

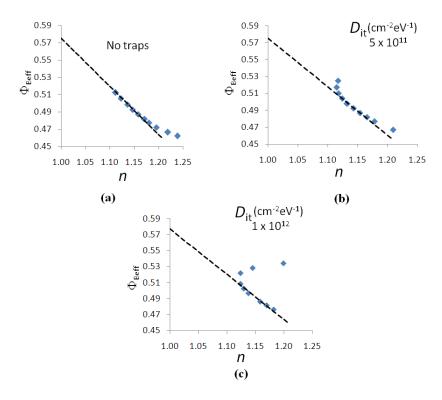

| 4.11 | Effect of interface trap density on the $n$ - $V_{qs}$ plot                                                                        | 116 |

|      |                                                                                                                                    |     |

|      | traps with $0 < V_{gs} < 0.5$ was used for the linear correlation, (b)                                                             |     |

|      | $5 \times 10^{11}$ cm <sup>-2</sup> eV <sup>-1</sup> traps with $0.2 < V_{gs} < 0.7$ was used for the linear                       |     |

|      | correlation, and (c) $1 \times 10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> traps with $0.4 < V_{gs} < 1$ was                        |     |

|      | used for the linear correlation. An input Schottky barrier height of                                                               |     |

|      | 580 meV, nanowire doping density of $10^{16}$ cm <sup>-3</sup> , and $T = 300$ K                                                   |     |

|      | have been assumed                                                                                                                  | 117 |

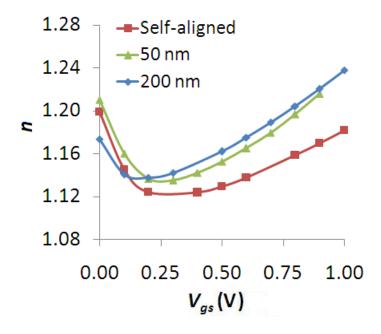

|      | Effect of gate overlap over the $n$ - $V_{gs}$ plot                                                                                | 119 |

| 4.14 | Effect of gate overlap over the $n$ - $\Phi_{\text{Beff}}$ variation. An input Schottky                                            |     |

|      | barrier height of 580 meV, nanowire doping density of $10^{16}$ cm <sup>-3</sup> ,                                                 |     |

|      | and interface trap density of $10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> have been assumed.                                       | 119 |

| 4.15 | Effect of image force lowering on the $n$ - $\Phi_{\text{Beff}}$ plot for the two differ-                                          |     |

|      | ent doping densities. An interface trap density of $10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup> ,                                   |     |

|      | input Schottky barrier height of 580 meV, and $T = 300$ K have                                                                     | 101 |

| 1 10 | been assumed                                                                                                                       | 121 |

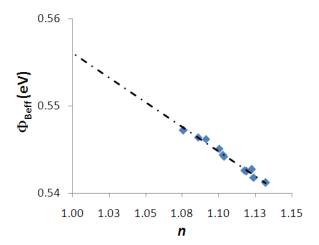

| 4.16 | Linear correlation between $n$ and $\Phi_{\text{Beff}}$ obtained from experimental                                                 | 105 |

|      | <i>I-V</i> characteristics                                                                                                         | 125 |

| 5.1 | a) Cross sectional schematic of the active device segment b) Schematic              |     |

|-----|-------------------------------------------------------------------------------------|-----|

|     | of the 3T-CP setup                                                                  | 130 |

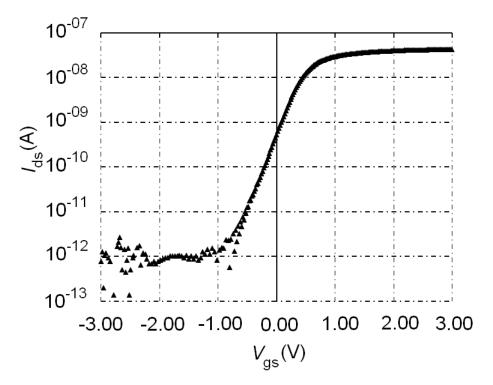

| 5.2 | Transfer characteristics measured by sweeping $V_{qs}$ from -3 to +3V               |     |

|     | while holding $V_{ds}$ at 100 mV                                                    | 132 |

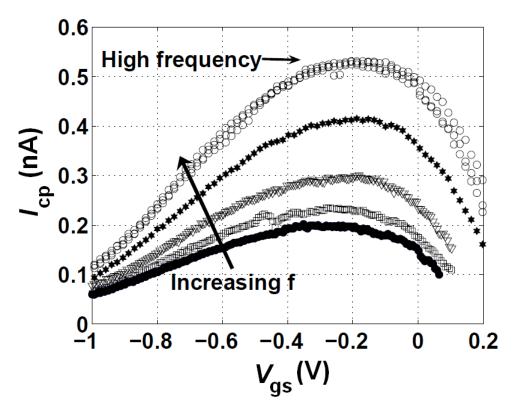

| 5.3 | 3T-CP signal in a SG-NWFET measured at different pulse frequen-                     |     |

|     | cies                                                                                | 134 |

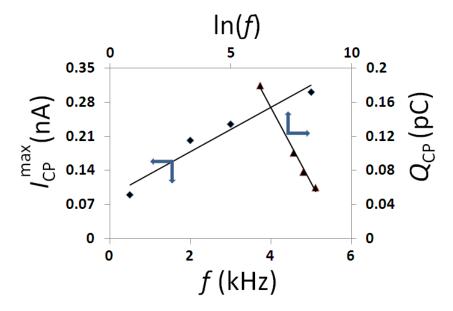

| 5.4 | $I_{CP}^{max}$ as a function of applied frequency and $Q_{CP}^{max}$ variation with |     |

|     | ln(f) measured in our SG-NWFET                                                      | 135 |

|     |                                                                                     |     |

# **List of Tables**

| 1.1 | Summary of basic properties and comparison between 4H-SiC, GaN and ZnO                                                              | 28 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Extracted effective Richardson constant and barrier height values for different devices obtained using the original Richardson plot | 90 |

| 3.2 | Extracted Richardson constant values for different GaN Schottky                                                                     |    |

|     | diodes obtained using the original Richardson plot                                                                                  | 96 |

## **Acknowledgments**

I have spent several days delaying to write this segment of the thesis and it is entirely due to the fact that it is hard to convey the immense sense of gratitude i feel towards everyone involved directly or indirectly in shaping my graduate life at Penn state. Any combination of words i come up with feel inadequate, and keeping this in mind, i feel a simple thank you is the best i can do. I thank my advisors for their guidance and support all through these years. Without their inputs, ideas and effort, i would not have been able to complete this work. I would like to thank Dr.Samia for serving on my committee and also offering help and encouragement on numerous occasions. My other committee members, Dr.Tittmann and Dr.Suman Datta, have been immensely gracious with their time and inputs that have been really useful to me. My thanks to several other faculty members across Penn state who have been very kind in clearing road blocks so that i could carry on my research smoothly. Dr. Vijaykrishnan, Dr. Jian Xu, Dr. Ashok, Dr. Tom Jackson, Dr. Theresa Mayer, Dr. Mark Horn have provided access to their lab equipment, resources and time that have helped me immensely. Interaction with their graduate students have often resulted in very fruitful discussions and for that i am grateful. Special thanks to Dr. Steve Durbin and Dr. Martin Allen for their fantastic collaborative effort that has formed the basis for a large part of this thesis. The department of Engineering Science and Mechanics has provided support for my graduate studies all through these years and i am really thankful for the help and support. The ESM faculty and staff have been kind to answer my questions and guide me through different stages of my graduate life. For that, i am really thankful.

Over the few years, i have been at Penn State, i have had the opportunity to collaborate with several people. It will be hard to name each and every one of them but i will try: Lucas, Subbu, Shiva, Suresh, PP, HP, Charan, Martin, Fan, Alan, Brian, Bob, Chad, Nick, Heayoung. I am confident that i have forgotten several others but i still acknowledge their help on countless occasions. My friends at PCG and elsewhere have often readily offered help through their words (sometimes loaded with sarcasm) and actions (sometimes proven counter-productive). Finally,

my family...

Several years ago, i received a call some time in the night that i got into Penn state and I still remember the excitement i felt. Late in to the night, my parents and I discussed about the prospect of getting a PhD. My mother had named me Karthik based off a character in one of her favorite novels. Although i think she intended me to be a different kind of doctor, it will not be too bad if i do end up as the other doctor. I am really grateful to have a very dear, caring family and an incredible wife. They have offered their criticism in their own unique ways and made the whole job about ten times easier (approximately). Thank you all!

Chapter 1

# Schottky barrier: Modeling and

### **Physics**

#### 1.1 Semiconductor surface

The surface plays an important role and can often dictate the electronic properties of a semiconductor device. The surface is basically an extended defect where the periodic structure of the crystal is interrupted. An unpassivated surface such as a freshly cleaved wafer has an abundance of dangling bonds that represent a non-equilibrium energy state. Under such conditions, the surface can spontaneously reconstruct to form a lower energy surface structure. Surface re-construction is driven by the need to maintain charge neutrality and is dictated by chemical bonding [1]. For example, silicon is tetravalent and covalently bonds using sp<sup>3</sup> orbitals. At the surface of a single crystal silicon cleaved along the <111> direction the tetragonal

bonding of the surface atoms are severed resulting in an sp<sup>2</sup> hybridization and a lone pair. The lone pair has a higher energy as compared to a bond pair and contributes to the overall surface energy. The lone pair also interacts with the sp<sup>3</sup> orbitals and distorts the tetrahedral structure. In response, the surface tends to re-construct to minimize the free energy of the surface, and also return to overall charge neutrality. Kinetic constraints imposed by growth conditions, foreign contaminants and defects can all affect the final atomic structure of the surface.

The surface of a semiconductor inherently contains some surface states that are characteristic of the semiconductor surface. Depending on the detailed electronic and atomic structure at the surface, discrete energy states can be distributed within the bandgap of the semiconductor. Surface states can be of either acceptor or donor types with the density of donor type being larger closer to the conduction band minima (CBM). On the other hand, the acceptor states tend to have larger density close to the valence band maxima (VBM), and at a certain energy location within the band gap the acceptor state density matches the donor state density. The cross-over point is known as the charge neutrality level (CNL) and has special significance in the physics of heterojunctions and interfaces.

The relative difference between CNL and the equilibrium Fermi-energy level determines the intrinsic band bending, charge state and magnitude present at the semiconductor surface. When the Fermi-level is below the CNL, positive charge is stored in the surface states, and for an n-type semiconductor a slightly downward

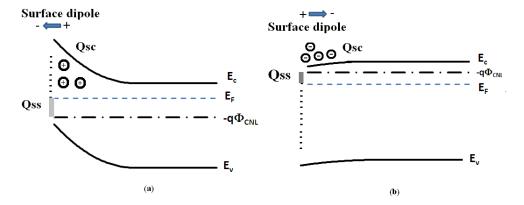

Figure 1.1. Band bending and surface dipole under surface depletion and accumulation conditions

band bending and surface charge accumulation results. On the contrary, when the CNL is above the Fermi-level, a net negative charge appears in the surface states, and consequently, the bands bend upwards resulting in a surface depleted condition [2]. Figure 1.1 shows the two different scenarios discussed above. The charge stored in the surface states  $(Q_{ss})$  along with the charge induced in the semiconductor  $(Q_{sc})$  forms a surface dipole layer. A flat band condition arises when the CNL coincides with the Fermi-level position, but in most semiconductors, the CNL differs from the Fermi level by a few tenths of an eV giving rise to either surface depleted or accumulated conditions. The magnitude and direction of the surface dipole is dependent on the semiconductor band structure, semiconductor growth and surface preparation conditions. Apart from the dependence of the surface properties on the intricate atomic and electronic structure of the native surface, the surface properties can be also influenced by the introduction of a metal layer on the semiconductor.

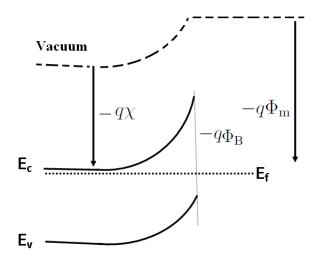

**Figure 1.2.** Band diagram of the Schottky metal/semiconductor contact under equilibrium conditions

#### 1.2 Metal/semiconductor (MS) interface

A simple view of the MS interaction is shown as a band diagram in Figure 1.2. A Schottky contact results due to the workfunction difference between the metal and semiconductor. The Schottky-Mott model predicts that the difference between the metal workfunction  $(\Phi_m)$  and the semiconductor electron affinity  $(\chi)$  would equal the resultant barrier height  $(\Phi_B)$ :

$$\Phi_{\rm B} = \Phi_{\rm m} - \chi \tag{1.1}$$

The Schottky-Mott model predicts that for a given semiconductor the Schottky barrier height (SBH) changes along with the metal workfunction. However, experimentally measured SBH on several semiconductor systems often do not seem to follow eq. 1.1, as predicted by the Schottky-Mott theory. The simple view assumed by the Schottky-Mott model is often violated at a real MS interface. The Schottky-Mott model is considered to describe the non-interacting limit of the SB formation models since it considers the SBH as a result of the bulk metal and semiconductor workfunction differences. The Schottky-Mott model does not place any emphasis on the MS interface properties, and hence, does not account for the effect of the metal/semiconductor interaction on the resultant Schottky barrier.

Over the past few decades, several studies have focused on extending the Schottky-Mott model to account for the wide range of deviations observed. Earlier approaches relied on the presence of a thin interfacial layer with high defect density to screen the effect of metal workfunction. Experimental evidence of SBH insensitivity to metal workfunction even in intimate MS contacts led to alternate approaches such as the metal-induced-gap-states. Subsequent approaches have almost always relied on the presence of the interface or surface states that can pin the Fermi level. The key difference between the various models is the dominant source for these interface states or pinning traps. These models can be collectively classified as gap states based models and are briefly examined next.

#### 1.2.1 Gap state models

Apart from the intrinsic surface state distribution, gap states related to metal atoms, foreign contaminants or defects can also be present. A thin interfacial layer with inherently high defect density is often assumed to be present at the MS

interface. Surface states present at the interface have been suggested as a source for Fermi-level pinning. However, Fermi-level pinning has also been suggested at intimate MS interfaces, and to account for FL pinning, Heine proposed that the surface states are induced due to the interaction of metal with the semiconductor surface [3]. The metal-induced-gap-states (MIGS) model proposes that the electron wave function within the metal tails into the semiconductor giving rise to overlap of the metal and semiconductor conduction bands. As a result, electronic states can exist within the energy band gap, and for intimate MS interfaces these gap states can still pin the Fermi-level.

The primary effect of the surface states is to pin the surface Fermi-level, limiting the workfunction dependence of the obtained SBH. On the other hand, gap states can be induced through the metal deposition process resulting in defect creation. The unified defect-induced-gap-state (DIGS) model relies on pinning due to defects generated by the metal deposition process [4, 5].

Based on the MIGS approach, the barrier height can be related to the CNL and the pinning parameter  $(S = \partial \Phi_{\rm B}/\partial \Phi_m \ [6])$  through

$$\Phi_{\rm B} = \Phi_{CNL} + S(\gamma_m - \gamma_s). \tag{1.2}$$

In eq. 1.2,  $\Phi_{\text{CNL}}$  is the CNL potential from the Fermi-level,  $\chi_m$  and  $\chi_s$  are the electronegativities of the metal and the semiconductor, respectively. In the case of strongly pinned interfaces, the SBH is independent of the metal workfunction and

is said to approach the Bardeen limit (S = 0). Strong surface Fermi-level pinning has been shown to occur for surface state densities exceeding  $10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> [7]. For a weakly pinned surface, the SBH dependence on the metal workfunction approaches the Schottky-Mott limit, and in this case the value of S approaches 1.

The MIGS approach accounts for the semiconductor contribution through CNL  $(\Phi_{\text{CNL}})$  and the metal/semiconductor bulk contributions through the electronegativity difference. The SBH is determined primarily by the CNL (solely determined by the semiconductor) and the effect of secondary factors such as surface dipoles due to the electronegativity difference. Surface states or foreign contaminants can further contribute to the deviation.

Another approach that has been recently developed by Tung is based on the chemical interaction between the metal and semiconductor right at the interface [8]. Bond polarization (BP) theory, as proposed by Tung, accounts for the interaction between the metal and the underlying semiconductor through charge re-distribution that occurs at a metal/semiconductor interface. For a stable MS contact, chemical bonding occurs to some degree and this involves breaking of surface bonds and formation of new bonds. Brillson reported the dependence of the pinning parameter on the heat of formation and emphasized that for the case of a reactive MS interface the pinning was weak [9]. In the BP scenario, the MS interface properties are affected by all three components of the MS system: metal, semiconductor and the interface-specific region (ISR). In contrast to other models,

which account for the observed metal workfunction dependence solely through the bulk metal and semiconductor properties, the ISR is a direct result of the chemical interaction between the metal and the semiconductor atoms at the interface, and the surface charge distribution depends on the electronegativity difference between the atoms present at the interface. Prior to the metal deposition, the semiconductor atoms are involved in some kind of bonding with their nearest neighbors. The bond length is different from the bulk, and the surface structure is essentially disordered. A fraction of the surface atoms still have dangling bonds and are energetically favored to form new bonds. The presence of surface defects such as micropipes or dislocations further contributes to the complexity of the surface structure and introduces localized structural variations.

In order to obtain a more intuitive understanding of the BP model, consider two planes of atoms A and B located at the surface and just below the surface, respectively. The bond polarity between the two planes depends on the electronegativity difference and results in charge re-distribution between the involved atoms. When a plane of metal atoms (M) approaches the surface, the surface bonding picture changes to accommodate the incoming metal atoms. The interface structure is dictated by similar constraints of chemical bonding, free energy minimization and charge neutrality that govern the surface re-construction process. Depending on the electronegativity difference between M, A and B, one can envision a partial bonding to emerge between M, A and B planes. This process involves charge

transfer across the interface, and the final charge distribution is dictated by the interface structure and conversely the interface structure is refined by the charge transfer. The final ISR structure determines the bond length between the metal and semiconductor surface atoms, and this bond length can vary spatially across the interface (especially for polycrystalline metal films). The charge transfer across the MS interface results in an interface dipole that can vary spatially as well. The magnitude of charge transfer depends on the bulk metal and semiconductor properties (such as electronegativity difference and semiconductor ionicity) and the equilibrium bond length is specific to the interface (depends critically on growth and processing conditions). Hence, the resultant interface dipole depends on the bulk metal and semiconductor properties and also is characteristic of the specific interface structure.

The preceding discussion points to the fact that the barrier height depends on details of the interface structure. Specifically, a surface dipole layer induced by intrinsic surface states, defects, MIGS or possibly other sources affects the interface barrier height. In the case of polycrystalline metal contacts to a semiconductor, the surface dipole can vary spatially and can result in lateral variations of barrier height. The interface barrier height variation has a profound impact on the carrier injection and transport properties of a Schottky diode. Early evidence of the inhomogeneous nature of the Schottky contact was observed as low barrier regions within a high barrier height background [10]. The inhomogeneous nature

of the contact was attributed to non-uniform interfacial reaction of the metal with the semiconductor. Careful analysis of transport properties can be a valuable aid to develop, validate and understand the Schottky barrier formation mechanism. Advanced surface characterization tools such as the ballistic electron emission microscopy (BEEM), as well as scanning electron microscopy coupled with the electrical characterization methods, provide essential and comprehensive experimental data required to validate any proposed models. In the next section, we review the basics of carrier transport across Schottky contacts with a special emphasis on the inhomogeneous barrier framework.

# 1.3 Carrier injection and transport across the M/S interface

Transport across the metal/semiconductor system is dictated by carrier injection, trapping and carrier transport processes. The relative rates of these processes are generally bias and temperature dependent, and the conduction properties of the system are a result of an interplay between these processes. For example, in a Schottky contact to a moderately-doped semiconductor, at low bias values the conduction properties are limited by carrier injection over the barrier. However, in the case of low mobility and large trapping density materials such as organic semiconductors, the injected carriers need not be transported effectively. In such

cases, carrier transport and trapping/de-trapping mechanisms would determine the conduction behavior of the system. Carrier trapping/de-trapping and injection phenomena are usually temperature activated processes, and hence, their effect on conduction properties are heavily affected by the measurement temperature.

In the case of a Schottky contact to an ordered single crystal semiconductor, carrier injection rather than transport determines the conduction properties of the diode. Transport across a spatially homogeneous Schottky barrier, in the ideal case, is given by the thermionic emission theory. Carrier transport occurs by emission over the barrier, and the key assumption is that the Fermi-level remains constant across the depletion region. Under thermionic emission the emitted carries are termed hot carriers, since these carriers have higher energy compared to the carriers in thermal equilibrium within the metal. The emitted hot carriers loose their additional energy through collisions with the metal lattice and with other carriers.

#### 1.3.1 Thermionic emission

Under thermionic emission theory, as proposed by Bethe, the current-voltagetemperature characteristics of the Schottky diode are given by

$$I = AA^*T^2 \exp(-\beta \Phi_{\rm B}) \exp(\frac{\beta V}{n}) \{1 - \exp(-\beta V)\}, \qquad (1.3)$$

where A is the geometric area of the Schottky contact,  $A^*$  is the Richardson constant, and n is a phenomenological term known as the ideality factor. V is the voltage drop across the diode and is related to the applied bias  $V_a$  by  $V = V_a - IR_s$ , where  $R_s$  is the parasitic resistance. Figure 1.4 shows the typical forward bias I-V characteristics measured at room temperature. For an ideal diode, at low forward bias values, the I-V characteristics are linear on a semi-log scale. At higher current levels, the I-V characteristics are dominated by series resistance, and a sub-linear behavior is seen on the semi-log scale. In the reverse-bias regime, the current-voltage relation is expected to approach the saturation current  $(I_{sat})$  given by

$$I_{sat} = AA^*T^2 \exp\left(-\beta \Phi_{\rm B}\right) \tag{1.4}$$

Experimental current-voltage-temperature (I-V-T) characteristics are often fitted to the ideal thermionic emission equation, and this exercise provides a baseline from which deviations are measured and interpreted. Traditionally, the extent of deviation from ideality is inferred through the extracted values of the ideality factor (n) and the barrier height  $(\Phi_B)$ . Under ideal conditions, the value of n equals 1 and the barrier height should equal the Schottky-Mott limit,  $\Phi_m - \chi$ . If one considers the effects of image force lowering, then the ideal values of n and  $\Phi_B$  would be slightly different. The effect of image force lowering is a slight increase in the ideality factor and a corresponding lowering of the barrier height.

The image force controlled ideality factor can be estimated using

$$n_{if} \approx 1 + \frac{1}{4} \left[ \frac{q^3 N_d}{8\pi^2 \epsilon_s^3 V_{bb}^3} \right]^{\frac{1}{4}},$$

(1.5)

and the corresponding barrier lowering is given by

$$\Delta\Phi_{\rm B} \approx \left(\frac{q^3 N_d V_{bb}}{8\pi^2 \epsilon_s^3}\right)^{\frac{1}{4}}.\tag{1.6}$$

In equations 1.5 and 1.6,  $N_d$  is the semiconductor doping,  $V_{bb}$  is the band bending and  $\epsilon_s$  is the dielectric constant of the semiconductor. The value of  $n_{if}$  depends on the doping density and, typically, ranges between 1.01 for moderate doping levels to about 1.03 for a heavily doped semiconductor. Extracted ideality factor values, however, tend to be much larger than the image force limit, and this suggests other dominant mechanisms such as tunneling across the barrier. Minority carrier injection can also contribute to the total current. Depending on the barrier profile, these mechanisms can also dominate the total current.

The extracted ideality factor and barrier height values exhibit bias and temperature dependence, and a variety of trends have been reported in the literature [11, 12]. The temperature dependence of the ideality factor and barrier height is often used to identify the dominant transport mechanisms (for example, [13, 14, 15]). Prior to the inhomogeneous Schottky barrier model, deviant trends exhibited by ideality factor and extracted barrier height were typically attributed to interface

and surface traps. A thin interfacial layer was assumed to be present at the MS interface that could influence the *I-V-T* characteristics. Interface traps or surface states (in the case of intimate MS interfaces) along with other mechanisms (such as field emission and generation-recombination) have been held responsible for greater-than-unity ideality factors. Recently, the notion of an inhomogeneous barrier has been gaining wide applicability and seems to be able to explain the wide variety of trends observed in real Schottky diodes [16, 17]. Prior to the inhomogeneous barrier models, analytic approaches implicitly assumed that the emission occurs over a spatially homogeneous barrier.

Apart from high ideality factors, a Schottky diode can exhibit a larger reverse leakage current than expected from thermionic emission theory. In some cases, a double diode behavior can be seen and has been reported for several semiconductor systems. Preliminary analytical approaches handled this behavior using a parallel diode approach, wherein two (or more) distinct regions with different barrier heights were assumed to contribute to the total current. The current-voltage relation in this case is a sum of all the individual diode contributions and can be written as

$$I(V_a) = A^* T^2 \sum_i A_i \exp\left(-\beta \Phi_{bi}\right) \left\{ \exp\left(\frac{\beta V_a}{n_i}\right) - 1 \right\},\tag{1.7}$$

where  $A_i$ ,  $n_i$  and  $\Phi_{bi}$  are, respectively, the area, ideality factor and barrier height of the i<sup>th</sup> diode.

#### 1.3.2 Observation of barrier height inhomogeneities (BHI)

Electrical characterization of Schottky contacts provides valuable insights into the metal/semiconductor interface, near-surface and bulk semiconductor properties. For this reason, the Schottky contact is often used as a test structure to assess intrinsic material quality, and the Schottky test structure is also a valuable process monitor (for deposition processes). Quasi-static electrical characterization such as current-voltage-temperature (I-V-T) and capacitance-voltage-temperature-frequency (C-V-T- $\omega$ ) measurements are simple to set-up but can provide a comprehensive set of information. Coupled with physical analysis methods such as ballistic electron emission microscopy (BEEM), scanning electron microscopy (SEM) and other microscopy methods, the interface and bulk semiconductor properties can be thoroughly investigated. Apart from quasi-static electrical characterization, transient measurements such as deep level transient spectroscopy (DLTS) and random telegraph signal (RTS) noise measurements can give information about energetically shallow and deep defects.

Experimental evidence for lateral variations of the barrier height were observed in the form of double diode behavior, and the variations were attributed to a non-uniform interfacial reaction [18]. Several electrical, optical and physical characterization tools have been used for observing and verifying barrier inhomogeneities in different metal/semiconductor systems. The effect of barrier height inhomogeneities on I-V-T characteristics has been reported by several groups (for example,

[19, 20, 21, 22]). The *I-V-T* measurements are, by far, the most sensitive electrical characterization methods. On the other hand, capacitance-voltage measurements are more affected by the mean barrier height and are relatively insensitive to barrier height fluctuations. Internal photoemission (IPE) studies have also revealed the presence of barrier inhomogeneities [23]. RTS noise from the inhomogeneous Schottky diode has been associated with charge trapping and de-trapping by interface traps in defective patches. RTS noise signal has been used to probe the energy location and density of traps in the patch [24].

Depth-resolved cathodoluminescence spectroscopy (DR-CLS) studies on Ni/SiC Schottky diodes reveal spatially non-uniform interface traps giving rise to spatial variation in Fermi-level pinning [25, 26]. In GaN Schottky diodes, inhomogeneities are associated with the presence of threading dislocations [27]. In the case of SiC, the inhomogeneities are associated with few extrinsic localized defects [28, 29]. Metal grain boundary and morphology induced inhomogeneities have been reported in [30, 31]. Different sources have been cited for various metal/semiconductor systems, and the source and nature of inhomogeneity is not always apparent from any individual measurement.

Comprehensive physical characterization using ballistic electron emission microscopy (BEEM), scanning tunneling microscopy, scanning capacitance microscopy, and atomic force microscopy to map the location variation of barrier height has been reported [28, 32, 33, 34, 35, 36]. These studies reveal a broad distribution

of barrier heights and propose that the low barrier patches lie at the tail end of the distribution. Low barrier patches around localized defects in GaN have also been detected using these characterization methods. These measurements are usually coupled with the observed current-voltage characteristics to obtain a complete physical and electrical picture of the diodes. For I-V analysis, over the past three decades, different theories have been developed and these are examined in the following sections.

#### 1.4 Framework for barrier height inhomogeneities

#### 1.4.1 Zero-order model