## The Pennsylvania State University

#### The Graduate School

## Department or Engineering Science and Mechanics

# STUDIES OF THIN SILICON OXIDES AND HIGH-K MATERIALS FOR GATE DIELECTRICS IN METAL-INSULATOR-SEMICONDUCTOR STRUCTURES

A Thesis in

Engineering Science and Mechanics

by

Jiayu Jiang

© 2004 Jiayu Jiang

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2004

We approve the thesis of Jiayu Jiang.

|                                                                                                                        | Date of Signature |

|------------------------------------------------------------------------------------------------------------------------|-------------------|

|                                                                                                                        |                   |

| Osama O. Awadelkarim Professor of Engineering Science and Mechanics Thesis Advisor Chair of Committee                  |                   |

| S. Ashok<br>Professor of Engineering Science                                                                           |                   |

| Mark W. Horn Associate Professor of Engineering Science and Mechanics                                                  |                   |

| Jerzy Ruzyllo<br>Professor of Electrical Engineering                                                                   |                   |

| Christopher R. Wronski Professor of Electrical Engineering Leonhard Professor of Microelectronic Devices and Materials |                   |

| Judith A. Todd P. B. Breneman Department Head Chair                                                                    |                   |

Professor and Head of the Department of Engineering Science and Mechanics

<sup>\*</sup> Signatures are on file in the graduate school

#### **ABSTRACT**

The development of a gate stack system (dielectric, electrode, and their compatibility with plasma etching processes and the scaled complementary metal oxide semiconductor [CMOS] integrated circuit [IC] process flow) presents major materials and processing challenges as IC industry approaches the sub-100 nm technology generation by the year 2006 and beyond. The continually shrinking gate-oxide thickness, necessitated by the requirement of higher gate capacitances for high drive current, results in direct tunneling and excessive leakage currents in metal-oxide-Si field-effect transistors (MOSFETs). To obtain high gate capacitance and inhibit tunneling, relatively thick insulators of high dielectric constants (high-k) are needed in place of gate oxides in MOSFETs. The research in this thesis will cover a series of issues related to the scaling of submicron devices.

In the first part of this thesis we examined the plasma-process induced damages in thin-gate oxide MOSFETs and its identification and characterization through electrical measurements. We found that, with the aggressive shrinking of oxide thickness around and below 50Å, conventional transistor parameter measurements such as threshold voltage ( $V_{th}$ ), transconductance ( $G_m$ ) and subthreshold swing (S) failed to resolve differences in devices with variable degree of plasma-process induced damage. We demonstrated that in these thin-oxide MOSFETs the gate leakage current ( $I_g$ ) is the only transistor parameter which can detect plasma-processing induced changes in oxide charge and interface states. These results are interpreted in terms of the strong dependence of  $I_g$

on trap-assisted tunneling which dominates conduction in oxides within the studied thickness regime.

In subsequent studies, thin-gate oxide MOS capacitors and MOSFETs were subjected to Fowler-Nordheim (FN) stress and Hot-Carrier (HC) stress, respectively, and tested with deep level transient spectroscopy (DLTS) to monitor trap generation during plasma process as well as during device operation. Charge states in SiO<sub>2</sub> and Si/SiO<sub>2</sub> interface states were observed under different FN stress temperatures and their causes were attributed to carrier injection during the stress. For the first time bulk Si defects are reported to be generated by FN stressing on thin gate oxides which raises a serious concern of carrier mobility in channel region of corresponding MOSFETs. During HC stress, we found that HC stress in thin-oxide transistors promotes interface damage while oxide charge trapping becomes less significant. The observed degradation is no longer localized near the drain side.

In the second part of the thesis, we focus our studies on the electrical properties of high-k gate stack systems. Different high-k dielectrics, SrTa<sub>2</sub>O<sub>6</sub>, ZrSiO<sub>4</sub>, ZrO<sub>2</sub> and HfO<sub>2</sub> prepared by liquid source misted chemical deposition, and TiO<sub>2</sub> prepared by chemical vapor deposition were used as the insulators in metal-insulator-Si (MIS) capacitors which were examined using CV/IV and DLTS. It is revealed, for the first time, that the accumulation capacitance of the MIS with the high-k dielectric is strongly dependent on the measuring temperature and frequency. The capacitance dependence on temperature in the MIS with the high-k dielectric is seen to proceed in an opposite direction to that of MOS capacitors while the capacitance dependence on frequency in the MIS is

significantly larger than that of MOS capacitors. An equivalent circuit model is proposed and the discrepancy is explained by the impedance contributions from a thin and low quality interfacial layer, between the high-k dielectric and the Si substrate, often inadvertently incorporated during the high-k dielectric growth. These observations call for efforts to be put towards the careful evaluation and possible elimination of this low-quality interfacial layer from gate dielectric stacks.

## TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                      | ix   |

|----------------------------------------------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                                                                       | xiii |

| ACKNOWLEDGMENTS                                                                                                      | xiv  |

| Chapter 1 An Overview of Metal-Oxide-Semiconductor (MOS) Device Scaling: Past, Present and Future                    | 1    |

| 1.1 Miniaturization in CMOS     1.2 Ultra-thin Gate Oxides: Properties, Issues, Problems and Scaling     Limitations |      |

| Limitations                                                                                                          | 7    |

| Chapter 2 Experimental Procedure: Test Structures and Electrical Characterization Methods                            | 14   |

| 2.1 Test Structures     2.2 Electrical Characterization Methods                                                      |      |

| 2.2.1 Transistor Parameter Measurements 2.2.2 Capacitance Voltage (CV) Measurements                                  | 16   |

| 2.2.3 Charge Pumping Measurement 2.2.4 Deep Level Transient Spectroscopy                                             | 20   |

| 2.3 Measurement Equipment                                                                                            |      |

| Chapter 3 Thin Gate Oxides: (I) Plasma Induced Damage and Damage Detection                                           |      |

| 3.1 Introduction                                                                                                     |      |

| 3.2 Device Fabrication and Test Structures  3.3 Experimental Results                                                 |      |

| 3.4 Discussion                                                                                                       |      |

| 3.5 Conclusion                                                                                                                | 31  |

|-------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 4 Thin Gate Oxides : (II) Fowler-Nordheim Stress Reliability                                                          | 40  |

| 4.1 Introduction                                                                                                              | 40  |

| 4.2 On the Device Structures and the Experimental Procedure                                                                   |     |

| 4.3 Experimental Results                                                                                                      |     |

| 4.4 Discussion.                                                                                                               |     |

| 4.5 Conclusion                                                                                                                |     |

| Chapter 5 Thin Silicon Dioxide: (III) Hot Carrier Stress Reliability                                                          | 56  |

| 5.1 A Brief Overview of Hot Carrier Induced Damage on Thin Oxide                                                              | 5.6 |

| MOSFETs                                                                                                                       |     |

| 5.1.1 Hot Carrier Stress Induced Damage                                                                                       |     |

| 5.1.2 The Physics of Hot-Carrier Interactions                                                                                 |     |

| 5.1.3 Characterization and Prevention of Hot Carrier Damage                                                                   |     |

| 5.2 On the Experimental Procedure                                                                                             |     |

| 5.3 Experimental Results and Discussion                                                                                       |     |

| 5.3.1 Threshold Voltage and Maximum Transconductance                                                                          |     |

| 5.3.2 Charge Pumping (CP) Results and Analysis                                                                                |     |

| 5.4 Summary                                                                                                                   | 69  |

| Chapter 6 Electrical Studies of Selected Metal/High-k Gate Dielectric/Si Material Systems                                     | 79  |

| 6.1 Introduction                                                                                                              | 70  |

| 6.1 Introduction                                                                                                              |     |

| 6.2 On the Experimental Procedure                                                                                             |     |

| 6.3 Experimental Results and Discussion.                                                                                      | 83  |

| 6.3.1 Accumulation Capacitance Dependence on Temperature and                                                                  | 02  |

| Frequency                                                                                                                     |     |

| 6.3.2 Estimation of EOT from CV Data                                                                                          |     |

| 6.3.3 Analysis of Accumulation Capacitance                                                                                    |     |

| 6.3.4 The Effects of Nitridation on the Substrate/Interface                                                                   |     |

| 6.3.5 Contamination to Si from High-k Dielectric Deposition                                                                   |     |

| Chapter 7 Conclusion                                                                                                          |     |

| •                                                                                                                             |     |

| 7.1 On the Thin Gate Oxides                                                                                                   | 115 |

| 7.1.1 Gate Leakage Current as the Only Sensitive Transistor Parameter for Plasma-Processing Induced Damage in Thin Gate-Oxide |     |

| MOSFETs                                                                                                                       | 115 |

| 7.1.2 Trap Generation in SiO <sub>2</sub> /Si Interface and in Bulk Si by Fowler-                                             |     |

| Nordheim Stressing of Thin-Gate-Oxide Capacitor Structures                                                                    | 116 |

| 7 1 3 Hot Carrier (HC) Stress Effects                                                                                         | 117 |

| 7.2 On the High-k Gate Dielectrics                               | 118 |

|------------------------------------------------------------------|-----|

| 7.2.1 The Temperature and Frequency Dependence of Accumulation   |     |

| Capacitance in MIS structures with High-k Dielectrics            | 118 |

| 7.2.2 The Effects of Pre-High-k-Deposition Substrate-Nitridation | 119 |

| 7.3 Suggestions for Future Work                                  | 120 |

| BIBLIOGRAPHY                                                     | 121 |

## LIST OF FIGURES

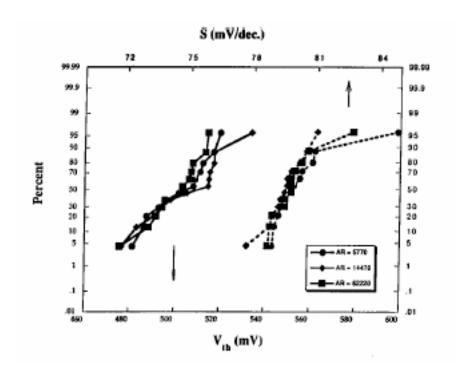

| Figure 3.1: The threshold voltage V <sub>th</sub> and subthreshold swing S plots for Type I module (45Å-thick gate-oxide, antennas employed at poly-Si gate, metal 1 and metal 2 etch steps with AR=5770, 14470 and 62220)                                          | .34  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

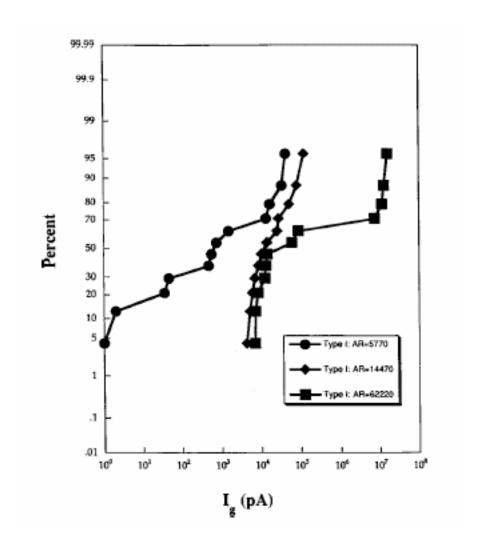

| Figure 3.2: The gate leakage current I <sub>g</sub> plot for Type I module (45Å-thick gate-oxide, antennas employed at poly-Si gate, metal 1 and metal 2 etch steps with AR=5770, 14470 and 62220)                                                                  | .35  |

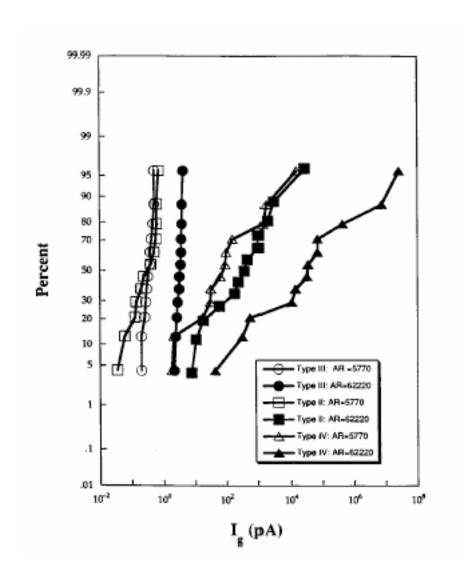

| Figure 3.3: The gate leakage current I <sub>g</sub> plots for Type II, III and IV modules (65Å-thick gate-oxide devices)                                                                                                                                            | .36  |

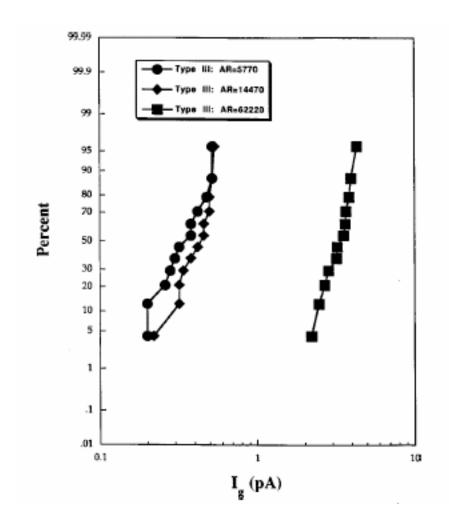

| Figure 3.4: The gate leakage current I <sub>g</sub> plots for Type III module (65Å-thick gate-oxide, antennas employed at metal 2 process only with AR=5770, 14470 and 62220)                                                                                       | .37  |

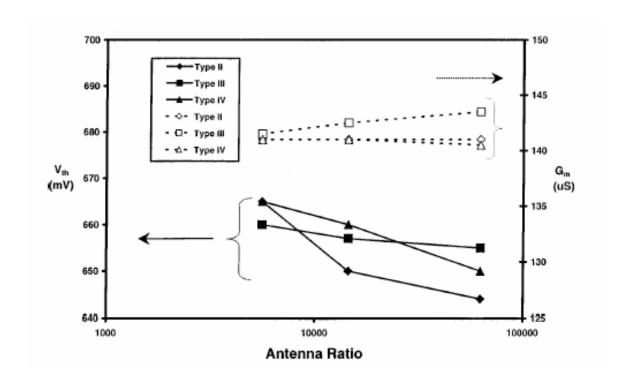

| Figure 3.5: The threshold V <sub>th</sub> and transconductance Gm plots for Type II, III and IV modules (65Å-thick gate-oxide). The mean values from corresponding probability curves were plotted here as a function of antenna ratios (AR=5770, 14470 and 62220). | .38  |

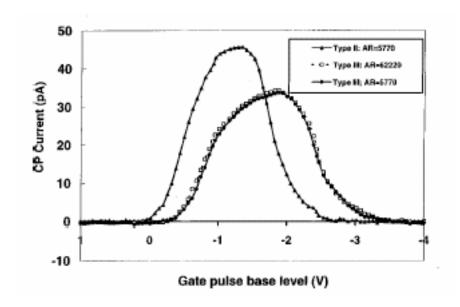

| Figure 3.6: The charge pumping curves for Type II module (AR=5770) and Type III module (AR=5770,62220). The measurement conditions were: reverse-bias-voltage $V_{rev} = 0V$ , voltage-pulse height $V_{pulse} = 2.2V$ and frequency $f = 1$ MHz.                   | .39  |

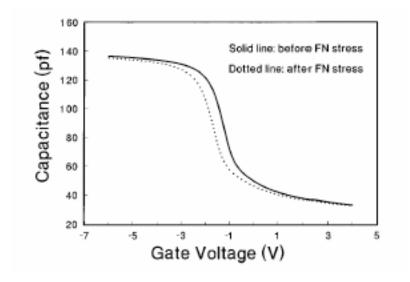

| Figure 4.1: CV spectra on a MOS capacitor before and after FN stressed at 300 K. The solid line is the CV curve measured before FN stress while the dotted line is the one measured after FN stress.                                                                | . 64 |

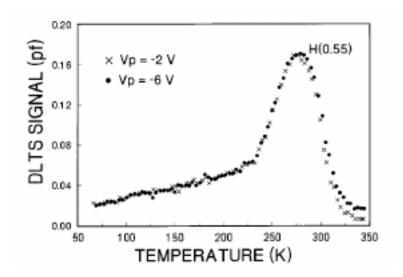

| Figure 4.2: : DLTS spectra taken in temperature scans from 350 K down to 60 K in a capacitor that was FN-stressed at 300 K. The spectra were taken at a filling pulse V <sub>p</sub> of -2V and -6V in a zero-biased capacitor                                      | .65  |

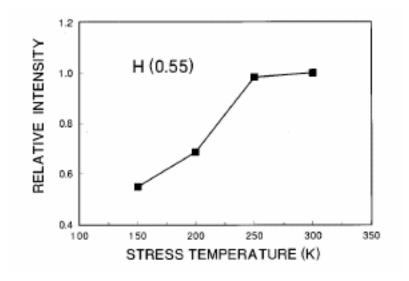

| Figure 4.3: The relative intensity of H(0.55) DLTS signal as a function of the FN stress temperature.                                                                                                                                                               | .66  |

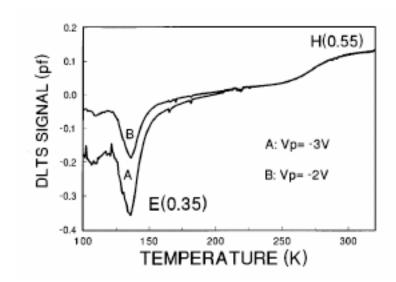

| Figure 4.4: The DLTS spectra taken in a zero-biased capacitor at a filling pulse of -2V and -3V with temperature scan from 320 K down to 60 K. Prior to taking the DLTS spectrum the capacitor was FN-stressed at 150 K and subsequently warmed up to 320 K.                                                                                                                                                                                                                                                                         | 57          |

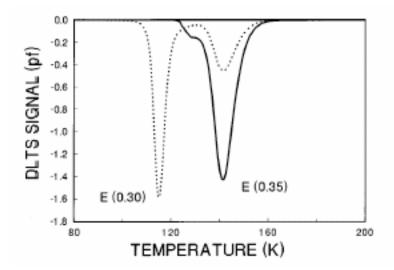

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 4.5: The DLTS spectra of different temperature scan directions taken in a zero-biased capacitor at a filling pulse of -4V. The capacitor was stressed at 100 K before the DLTS measurement and subsequently warmed up to 300 K. The solid line spectrum was taken in a temperature scan from 300 K to 60 K, whereas the dotted line spectrum was taken immediately after the completion of the solid line spectrum in a reverse temperature scan from 60 K up to 300 K. Only the spectral region 80 K to 200 K is shown here. | 58          |

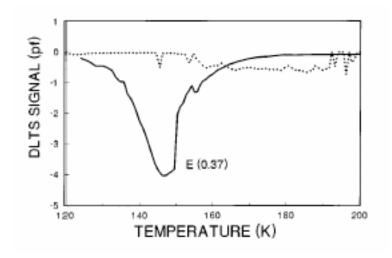

| Figure 4.6: The DLTS spectra measured in a zero-biased capacitor at a filling pulse of -4V in a temperature scan from 60 K to 300 K (solid line) followed immediately by another DLTS measurement with a temperature scan from 300 K to 60 K (dotted line). Only the spectra between 200 K and 120 K is shown. Prior to taking the solid line DLTS spectrum the capacitor was FN-stressed at 50 K and subsequently measured from 60 K to 300 K                                                                                       | 59          |

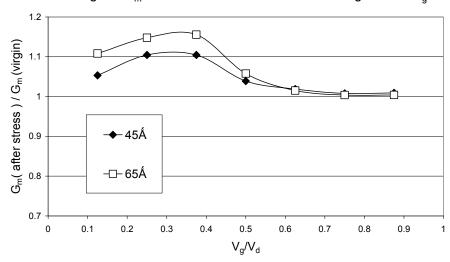

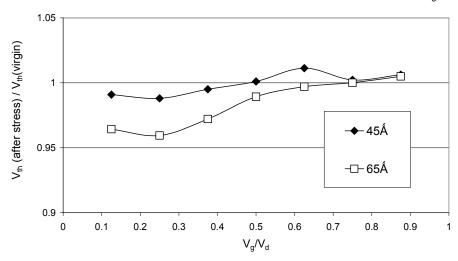

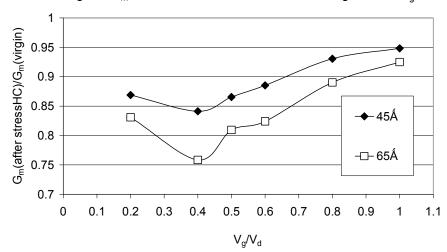

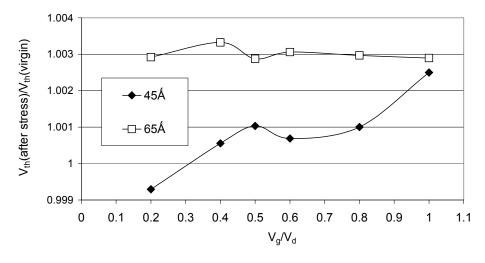

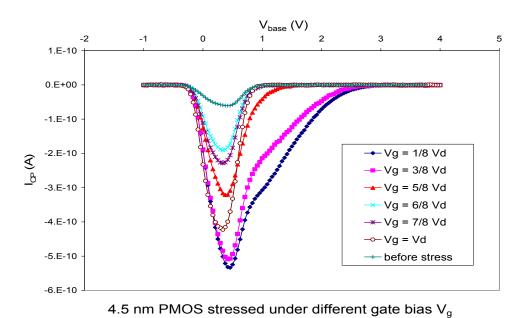

| Figure 5.1: Threshold voltage and maximum transconductance results for PMOS samples under different HC stress conditions. (t=10 s, V <sub>d</sub> =-8V for transistors with 65Å-thick gate oxide, t=10 s, V <sub>d</sub> =-5V for transistors with 45Å-thick gate oxide, the gate bias V <sub>g</sub> varies from 1/8 V <sub>d</sub> to V <sub>d</sub> )                                                                                                                                                                             | 34          |

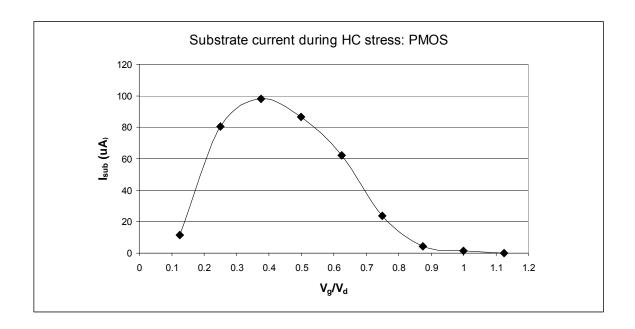

| Figure 5.2: Substrate current for PMOS transistor with 45 Å-thick gate oxide during HC stress under different gate bias V <sub>g</sub> ,                                                                                                                                                                                                                                                                                                                                                                                             | 35          |

| Figure 5.3: Threshold voltage and maximum transconductance results for NMOS samples under different HC stress conditions. (t=10 s, V <sub>d</sub> =5V for transistors with 65Å-thick gate oxide, 3.5V for transistors with 45Å-thick gate oxide, the gate bias V <sub>g</sub> varies from 1/5 V <sub>d</sub> to V <sub>d</sub> )                                                                                                                                                                                                     | $3\epsilon$ |

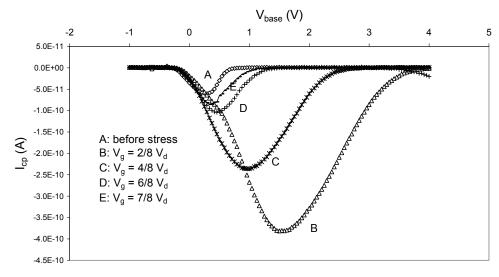

| Figure 5.4: CP results on PMOS transistors with different oxide thickness. The HC stress condition were $t=10s$ , $V_d=-8V$ for samples with 65Å-thick gate oxide, $V_d=-5V$ for samples with 45Å-thick gate oxide, $V_g$ varies from 1/8 $V_d$ to $V_d$ .                                                                                                                                                                                                                                                                           | 37          |

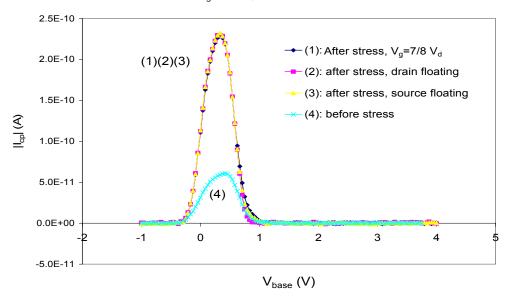

| Figure 5.5: CP measurement on PMOS transistors with 45 Å-thick gate oxide under different source/drain configuration (Absolute I <sub>cp</sub> current value is used in this plot)                                                                                                                                                                                                                                                                                                                                                   | 38          |

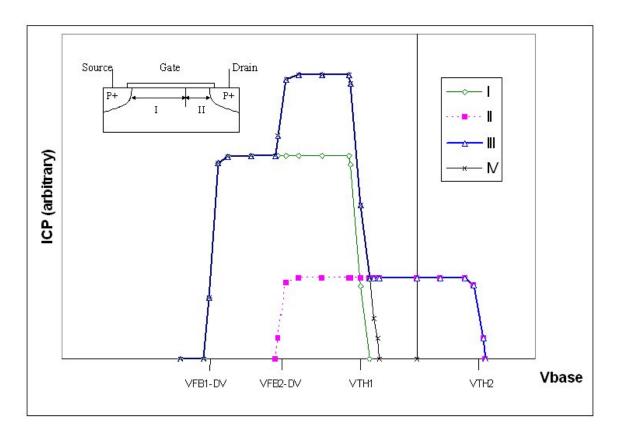

| Figure 5.6: Charge Pumping curves for a PMOS transistor with nonuniformly distributed degradation. Region I of the channel is not degraded, Region II has negative trapped charge and increased interface trap desity. Curve I: CP curve of region I; Curve II: CP curve of region II; Curve III: CP curve of the                                                                                                                                                                                                                    |             |

| whole transistor; Curve IV: CP curve of the whole transistor with drain side floated. DV is the pulse height $\Delta V_A$                                                                                                                                                                                                                                                         | .89   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

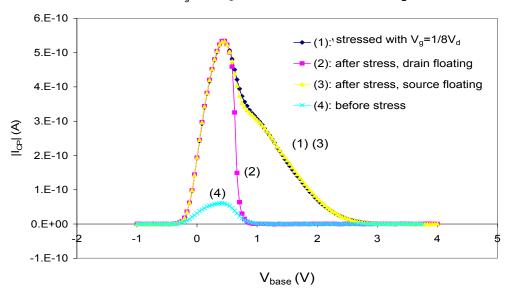

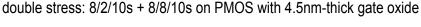

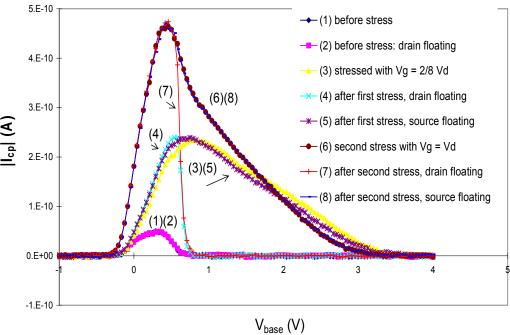

| Figure 5.7: CP measurement on PMOS transistors with 45Å-thick gate oxide. Sample was first subjected to 10 s HC stress with $V_g$ =2/8 $V_d$ , after CP tests, it was then subjected to another 10 s HC stress with $V_g$ = $V_d$ . Different source/drain configurations were adopted during the CP tests as indicated in figure. (Absolute $I_{cp}$ value is used in this plot) | .90   |

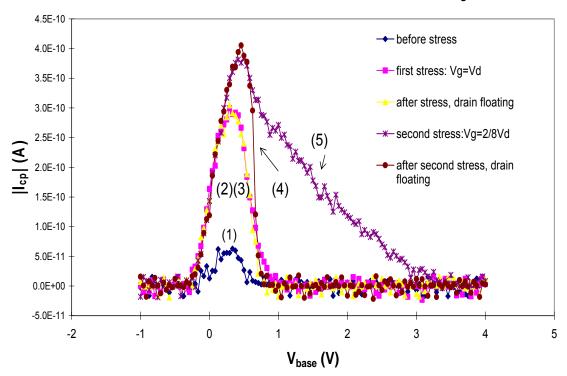

| Figure 5.8: CP measurement on PMOS transistors with 45Å-thick gate oxide. Sample was subjected to 10 s HC stress with $V_g$ = $V_d$ , after CP tests, it was then subjected to another 10 s HC stress with $V_g$ = $2/8V_d$ . Different source/drain configurations were adopted during the CP tests as indicated in figures. (Absolute $I_{cp}$ value is used in this plot)      | .91   |

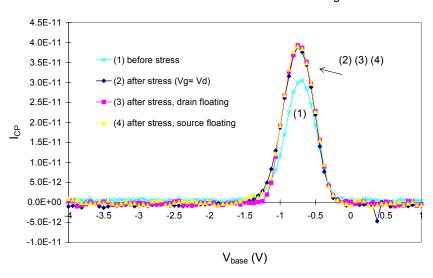

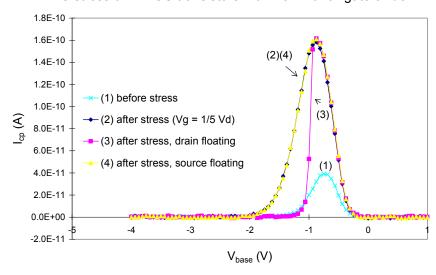

| Figure 5.9: CP results on NMOS transistor with 45 Å-thick gate oxide thickness. (a) Sample was subjected to HC stress of 10 s, $V_g=V_d$ ; (b) sample was subjected to HC stress of 10 s, $V_g=1/5$ $V_d$ . CP measurements were performed with drain floating, source floating, respectively in both cases                                                                       | .92   |

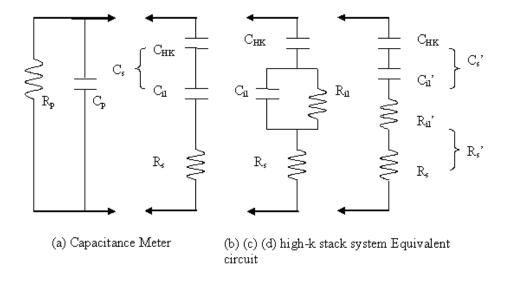

| Figure 6.1: Equivalent circuits in accumulation region in MIS with a high-k gate stack system.                                                                                                                                                                                                                                                                                    | .99   |

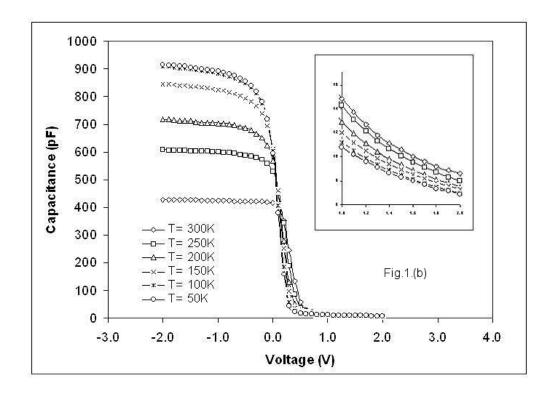

| Figure 6.2: CV curves for 5.0nm SrTa <sub>2</sub> O <sub>6</sub> /p-type Si capacitor measurement at different temperatures. The inset shows capacitance measured between +1V to +2V (deep depletion region)                                                                                                                                                                      | . 100 |

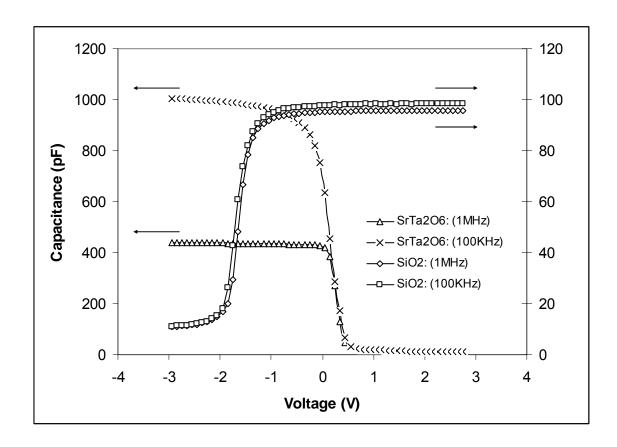

| Figure 6.3: CV curves for both SiO <sub>2</sub> /n-type Si MOS capacitor and SrTa <sub>2</sub> O <sub>6</sub> /p-type Si MIS capacitor structures measured at different frequencies (1M Hz and 100k Hz)                                                                                                                                                                           | . 101 |

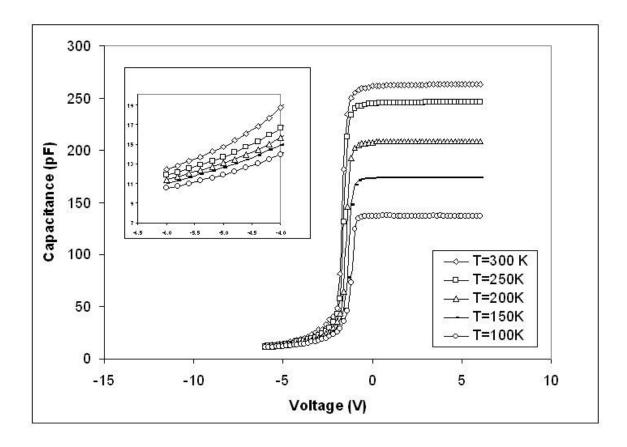

| Figure 6.4: CV curves for 20 nm SiO <sub>2</sub> /n-type Si MOS capacitor structure measured at different temperatures. The inset shows capacitance between - 6.5V to -4 V (deep depletion region)                                                                                                                                                                                | . 102 |

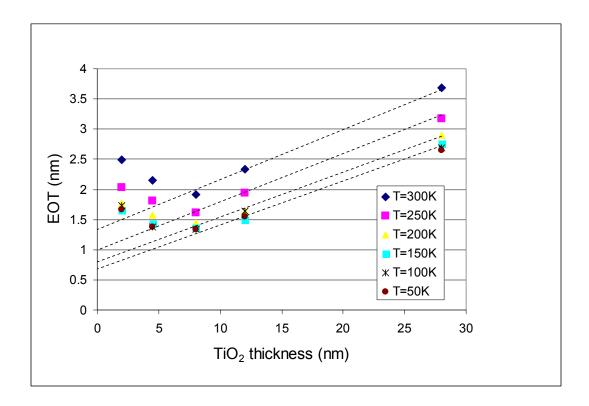

| Figure 6.5: Equivalent oxide thickness (EOT), in a MIS capacitor with a TiO <sub>2</sub> gate dielectric on nitridated silicon as a function of the deposited thickness of the TiO <sub>2</sub> and CV measurement temperature.                                                                                                                                                   | . 103 |

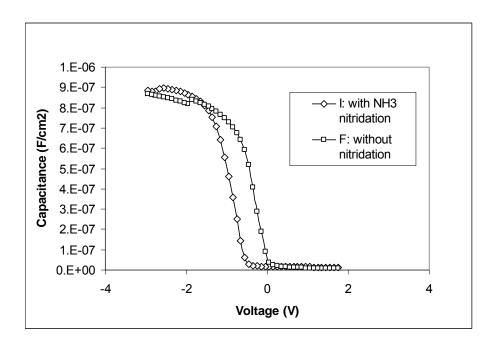

| Figure 6.6: CV and IV curves for Sample I (12 nm-thick TiO <sub>2</sub> gate oxide with NH <sub>3</sub> -nitridation) and Sample F (12 nm-thick TiO <sub>2</sub> gate oxide without NH <sub>3</sub> -nitridation).                                                                                                                                                                | . 104 |

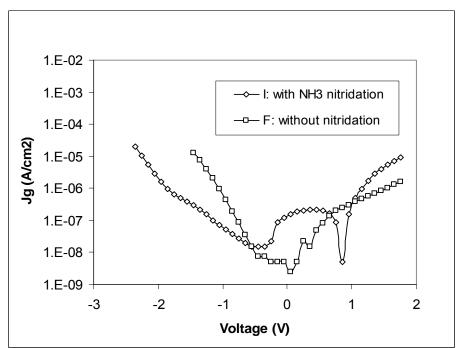

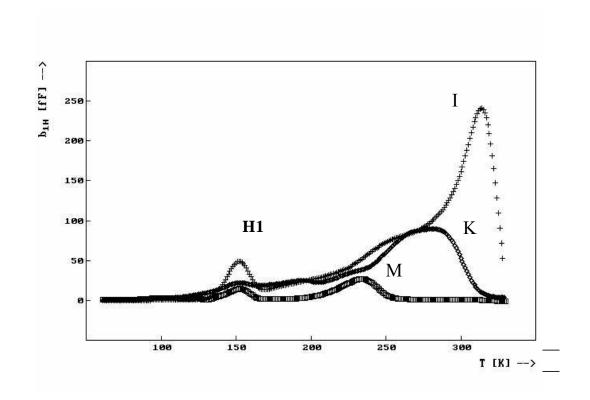

| Figure 6.7: DLTS results on capacitor samples with different TiO <sub>2</sub> gate dielectric thicknesses. Sample I has TiO <sub>2</sub> thickness of 12 nm, while sample K and M have TiO <sub>2</sub> thicknesses of 8 nm and 2 nm, respectively. The DLTS                                                                                                                      |       |

| measurement condition is reverse bias of $V_r$ =0.5V and pulse height of $V_p$ =0V for all three spectra.                                                                                                                               | . 105 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

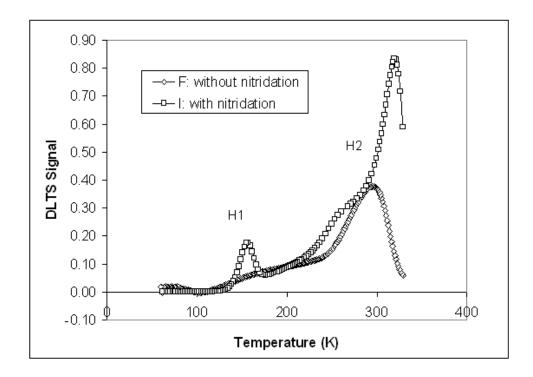

| Figure 6.8: DLTS spectra on capacitors subjected to pre-deposition NH <sub>3</sub> nitridation (sample I) and samples without pre-deposition nitridation (F). Both samples are of similar TiO <sub>2</sub> gate oxide thickness (12nm). | .106  |

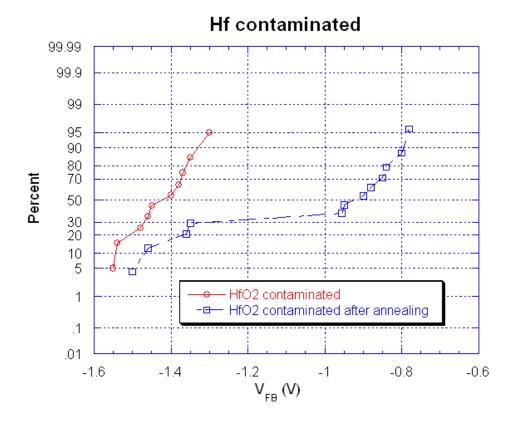

| Figure 6.9: Probability plots of flat-band voltages for $HfO_2$ contaminated samples before and after forming gas anneal. The data were collected from 10-12 structures. The anneal condition is $T=400^{\circ}C$ and $t=30$ mins.      | .107  |

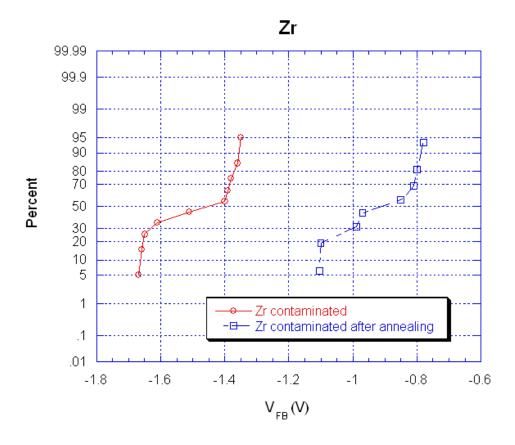

| Figure 6.10: Probability plots of flat-band voltages for $ZrO_2$ contaminated samples before and after forming gas anneal. The data were collected from 8-10 structures. The anneal condition is $T=400^{\circ}C$ and $t=30$ mins.      | .108  |

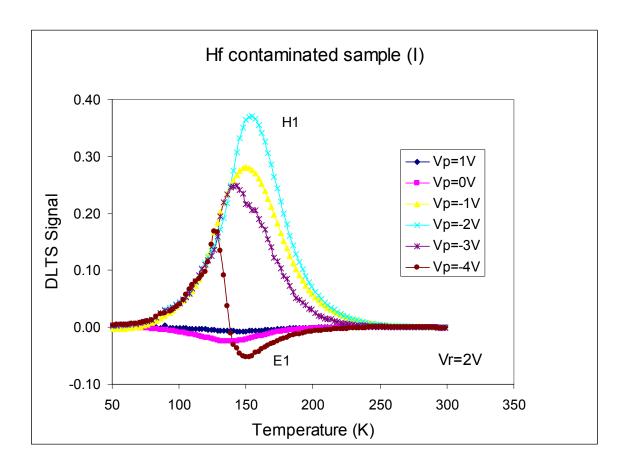

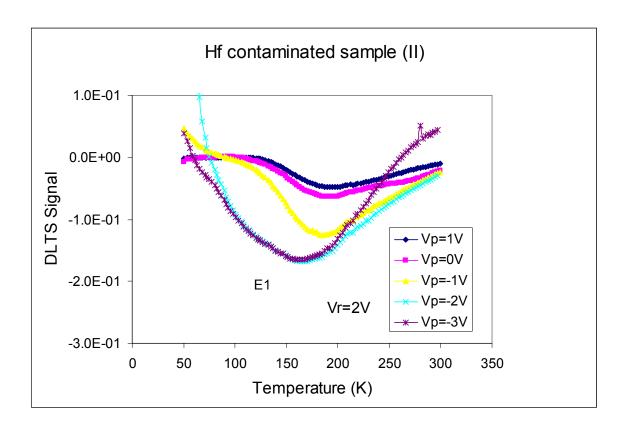

| Figure 6.11: A typical DLTS spectra on HfO <sub>2</sub> contaminated capacitors after forming gas anneal (400°C, 30mins). The measurements were performed under reverse bias of 2V and various pulse height from -4V to 1V              | . 109 |

| Figure 6.12: Another typical DLTS spectra on HfO <sub>2</sub> contaminated capacitors after forming gas anneal (400°C, 30mins). The measurements were performed under reverse bias of 2V and various pulse heights from -4V to 1V.      | .110  |

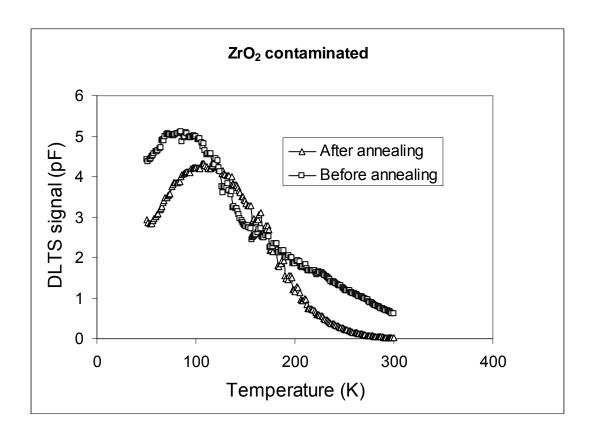

| Figure 6.13: DLTS spectra on $ZrO_2$ contaminated samples before and after forming gas anneal (400°C, 30min). The measurement used reverse bias of $V_r$ = 2V and had pulse height of $V_p$ =-2V.                                       | .111  |

## LIST OF TABLES

| Table 1–1: Electrical properties of some high-k candidates            | 27  |

|-----------------------------------------------------------------------|-----|

| Table 3–1: Test Modules                                               | 33  |

| Table 6–1: TiO <sub>2</sub> sample list                               | 112 |

| Table 6–2: Summary of CV/IV measurements on the contamination samples | 113 |

#### **ACKNOWLEDGMENTS**

The work presented here could not have been accomplished without the guidance and help of my advisor, Professor Osama Awadelkarim. I am thankful for his teaching, support and encouragement. His emphasis on searching for the physics behind the phenomena has been my guideline during my research. I am thankful to Professor Ruzyllo and his group for preparing some of the high-k dielectrics used in this research. I would also like to thank Professors Ashok, Horn, Ruzyllo, and Wronski for serving in my committee.

I am grateful to my colleagues Dr. Dong-oh Lee, Dr. Levent Trabzon and Dr M.

Okandan for their discussion and assistance throughout my research. I wish them the best of luck in their careers.

I would like to thank my wife and my parents for their love, understanding, and continuous support throughout the different stages of this work.

Last but not least, I would like to thank the personnel in the Penn State

Nanofabrication Facility, the faculty members and staff in the Engineering Science and

Mechanics department for their support.

#### Chapter 1

## An Overview of Metal-Oxide-Semiconductor (MOS) Device Scaling: Past, Present and Future

#### 1.1 Miniaturization in CMOS

Semiconductor industry has continued to prosper and to foster the growth of multiple industries ever since early 1970s. It has grown at a very fast 15% compounded annual growth rate (CAGR), with semiconductor sales reaching \$160B in 1998, representing 16% of the total electronic equipment sales (\$900B). Without any doubt, semiconductor industry has become the main driving force for the new information age. At the center of this sustained growth, resides the unique factor that has made the semiconductor industry successful: decrease in device feature size have provided improved functionality at a reduced cost. The first commercial microprocessor, the 4004 invented by Intel in 1971, contained a mere 2300 transistors and performed about 60,000 calculations in a second. Three decades later, and at the same or even lower cost, Intel Pentium III and AMD Athlon microprocessors run at 500M-1G Hz, have more than 22 million transistors performing hundreds of millions of calculations each second [1].

Complementary metal-oxide-Si (CMOS) technology has become the dominant very-large-scale-integrated (VLSI) circuit technology and its dominance has permitted the industry to focus primarily on scaling. Device linear features have indeed decreased at a rate of  $\sim 70\%$  every three years throughout most of the industry's relatively short history. Moreover, acceleration to a 2-year cycle has been experienced in the most recent years. Cost per function has simultaneously decreased at an average rate of  $\sim 25$ - 30%/year/function [2]. In 1965, Gordon Moore, the founder of Intel Inc., predicted that the number of transistors on a chip would quadruple every 36 months. He further updated his prediction in 1985 and reduced the cycle to 24 months. It is interesting how CMOS scaling has strictly followed this law for the last thirty years of its development.

The promise of CMOS scaling is to speed up the device while at the same time increase the integration density to lower the overall cost. This is made possible by continuous miniaturization of transistor's dimensions, e.g. shorten the channel length to reduce the carrier traveling time from drain to source, reduce the gate oxide thickness, minimize the transistor area, etc. This is also made possible by the development of many new processing technologies, such as extreme UV, e-beam and X-ray lithographies. Over the years, silicidation processes were added to CMOS processing sequence so as to lower the sheet resistance of the poly-Si electrode and source/drain regions. Lightly-doped drain (LDD) and double diffused drain (DDD) structures have been developed to improve the transistor robustness to hot carrier induced degradation [3]. Barrier metals and W-Plugs were added to the Al-alloy interconnection process flow for improved reliability.

According to the Semiconductor Industry Association (SIA) predictions, the expected transistor gate length reaches 250nm (50Å oxide thickness) in 1998-1999, 180nm (25 Å oxide thickness) in 2001, 130nm in 2004 and eventually 100nm in 2007. The first two phases have already been achieved, whereas the shorter gate lengths are currently within reach. The reduction of transistor channel length reduces the carrier traveling time between source and drain, thus improves the device speed. Meanwhile, the reduction of gate oxide thickness is necessary to maintain the device scaling, e. g. threshold voltage and capacitance. However, it appears that the fundamental limits of the materials constituting the building blocks of the planar CMOS process will be reached soon, and the physics behind device operation will begin to change to accommodate quantum physics effects. Present research focuses on two important questions. The first question is what is the impact of ultra-thin gate oxide (<50Å) on device fabrication and operation? The second is, given the role of the oxide in device characteristics, what is the ultimate limit of oxide thickness reduction?

#### 1.2 Ultra-thin Gate Oxides: Properties, Issues, Problems and Scaling Limitations

Two of the most significant properties that are inherent to the ultra-thin gate oxides are the direct tunneling current and a new failure mechanism referred to as soft-breakdown. In the metal-oxide-Si (MOS) structure with 50Å or above oxide thickness, when a constant current is injected into the oxide, the conduction mechanism is Fowler Nordheim (FN) tunneling. In this mechanism electrons are injected across a triangular barrier at the SiO<sub>2</sub>-gate or SiO<sub>2</sub>/Si substrate [4, 5]. FN tunneling usually occurs during

device fabrication, especially during plasma based depositions or etching processes.

Damage to devices induced by FN current flow is very well studied [6]. However, below 50Å, a new type of conduction mechanism in the oxide comes into play. This mechanism is direct tunneling which is well above the level of Fowler-Nordheim tunneling at similar applied biases. This is because the film thickness is reduced to the point at which electrons can tunnel directly from cathode to anode and no longer require the effective barrier thinning that is necessary for the F-N conduction mode [7, 8].

The large tunneling current poses a fundamental limitation on the scaling of oxide thickness. While it may be at a negligible level compared with the ON-state current of a device, it will directly have an effect on the overall standby power. For a total active gate area of  $0.1 \text{cm}^2$ , chip standby power limits the maximum tolerable gate leakage current to the order of  $1-10 \text{A/cm}^2$ , which occurs for gate oxides in the range of 15-18 Å [9]. Moreover, the quantum tunneling current, especially in the large area devices that are often used in process control and reliability circuits may totally obscure the leakage from breakdown. Also, the large gate current renders some characterization techniques, such as threshold voltage, transconductance measurement, and even quasi-static capacitance-voltage (CV) measurement less accurate and less reliable [10].

In spite of the above disadvantages associated with thin oxides, it is also found out that using ultra thin oxides comes with some advantages too. For example, it is observed that plasma induced damage in the ultra-thin gate oxide transistor is much less severer than that in thicker gate oxide transistor. It is well known that the plasma induced damage arises from the stressing of the gate oxide, thereby resulting in increased

interface defect density, in shifted device parameters and in degraded device density [6]. In the past, it has been firmly established that damage from plasma processing increases with the reduction of gate oxide thickness, from 20nm to 8nm [11], or to 4nm [12]. When the gate oxide is reduced beyond these thicknesses, however, better gate oxide reliability is reported as a result of the direct tunneling current. It has been suggested that plasma charging damage will no longer pose a severe threat to the thin gate oxide once it is scaled below 3 nm [13]. A possible explanation here is that injected electrons gain energy as they travel in the oxide and they need to travel a certain distance beyond which their energy is high enough to create charge-trapping defects. An ultra-thin oxide may not be thick enough to accommodate such a distance. Also in a very thin oxide an electron may travel ballistically (without scattering or collisions) [14,15]: this means that there will be less collisions between electrons and atoms, and therefore fewer number of generated defects. Moreover, some of the charge trapped in these few defects will be easily swept off by the high electric field in the gate oxide during the process [16]. However, we should point out that at this point the results are not yet conclusive, recent reports indicate that high level of plasma damage is observed in 2nm-thick oxides.

Soft-breakdown is another issue that is unique to ultra-thin oxide MOS devices. It is observed as an increase in the low-level leakage current, but not as a catastrophic failure [17,18]. It becomes more prevalent the thinner the oxide and for oxides stressed at lower voltages. An ultra-thin oxide device (25Å) exhibiting soft-breakdown shows no abrupt voltage drop, no abrupt current jump, even no increase in low-voltage leakage current. The only indication of the soft breakdown is an increase in gate noise [19]. The

device with soft breakdown can operate normally in some applications, but soft breakdown could be detrimental in any analog or flash memory system [20]. Also, due to the lack of a sharp transition in the increasing leakage current, it is often difficult to define soft-breakdown and distinguish it from catastrophic breakdown in ultra-thin gate oxides. Combining this with the high tunneling leakage, the ultra-thin gate dielectrics under temperature and bias stressing show increase in stress-induced leakage currents (SILC) and soft-breakdown characteristics well in advance of the true hard breakdown/wear-out. The implications being that there are no well defined criteria for the gate-dielectric failure in the sub 50Å thickness range.

There are also other issues related to the ultra-thin oxides. Among these issues is the standard formula for oxide lifetime prediction which would no longer provide accurate estimate on the mechanism that causes the oxide to fail. One test on the low SILC measurement leads to the conclusion that the reliability of 2.2 nm gate oxide at 25°C has reached an unacceptable level.

All of the above issues and problems associated with ultra thin gate oxides have resulted in the presently accepted limit for the CMOS scaling of 100 nm gate length, or 15 Å gate oxide thickness. Further investigations on this limitation are currently in progress utilizing gate oxides as thin as 13 Å [21]. These investigations include "dynamic" gate tunneling leakage, loss of inversion layer charge, carrier mobility degradation and the temperature dependence of all these variables.

#### 1.3 High-k Materials for Gate Dielectrics in MOS Structures

Traditional scaling, which has been at the heart of the semiconductor industry for the last 30 years, is indeed beginning to show the fundamental limits of the materials constituting the building blocks of the planar CMOS process. However, new materials can be introduced in the basic CMOS structure to replace and/or augment the existing ones to further extend the device scaling approach. Since the assimilation of these new materials into the modified CMOS process gives the device physicist and the circuit designer improved electrical performance similar to the historical trends, this new regime is often identified as "equivalent scaling'. It is expected that these new materials will provide a viable solution to extending the limits of the planar CMOS process for the next 5 to 10 years. Examples of the introduction of these new materials are; using copper to replace aluminum to reduce the resistivity, or using low dielectric constant materials as surrounding dielectrics to reduce coupling between CMOS interlayers [22].

To break the 100nm-feature-size/15Å-thick-oxide barrier, the most significant step is the introduction of high dielectric constant (high-k) materials. As discussed in the previous sections, the shortening of transistor channel length leads to the corresponding scaling of gate area as well as gate oxide thickness in order to maintain the same transistor parameters such as gate threshold voltage and capacitance, which is proportional to the gate area and dielectric constant while inversely proportional to the gate thickness. If the reduction of the gate dioxide thickness is to reach its limit at  $\sim 15$  Å, the alternative way might be to look for new materials that offer higher dielectric constants. *Table 1–1* shows the electrical properties of a few promising candidates. With

a high dielectric constant (k) a thick gate dielectric layer ( $\geq$  200 Å) gives an appropriate capacitance value equal to that of a thin equivalent oxide thickness (EOT) which is usually in the range of 5-15Å. Thus the required dielectric capacitance obtained by making oxide thickness thinner is alternatively achieved in a much thicker but proportionately higher k dielectric. The advantage of using the relatively thick high k dielectrics is in the elimination of direct tunneling and soft-breakdown. High k materials, therefore, present excellent candidates for the replacement of the traditional SiO<sub>2</sub> gate oxide.

If a high-k material is to replace  $SiO_2$  as a gate dielectric, in addition to high dielectric constant (k>25), this high k material must have a reasonable energy gap (>4eV), a barrier height relative to Si greater than 1V or at least greater than the supply voltage  $V_d$  to be used with the dielectric, a low leakage current (no Frenkle-Poole, F-P, i.e., trap-assisted tunneling or other defects degrading dielectric reliability), a low interface state density ( $D_{it}$ ) and a low bulk dielectric charge. Furthermore the high k material must have no or minimal capacitance-voltage hysteresis effects, no more than an atomic layer of oxide at the silicon/dielectric interface, excellent thermal stability, and high process immunity to hot carrier effects [23,24]. In brief these high k materials must possess all the excellent qualities that had qualified  $Si/SiO_2$  system and gave it the monopoly over all MOS structure devices. These qualities are over and above that of high k.

We can break the high-k materials listed in *Table 1–1* into four groups. The first group consists of  $Si_3N_4$  and  $Al_2O_3$ . These two dielectrics have relatively low k value

compared to the other materials. However, they are very well studied and can be easily integrated into the conventional CMOS process. Some might regard them as an "extension" of SiO<sub>2</sub> but they are also a necessary segue to the high-k era, given the difficulties faced in choosing a suitable high-k dielectric [25]. Well-controlled nitridated films of 15Å thickness have already been reported. The second group consists of Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub> and BaSrTiO<sub>3</sub>. Their k values are highest among all dielectrics. However, thermodynamic studies indicate that Ta and Ti are not thermodynamically stable on silicon and thus form an interfacial layer. This interfacial layer is shown, later in this thesis, to greatly degrade the EOT value. Moreover, the interaction of these two materials with the polysilicon or metal gate electrode is of a large concern [26]. The third group consists of other types of binary oxides such as La<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, who have been proven to be thermodynamically stable on silicon. However, these materials are often efficient diffusers of oxygen therefore post-deposition annealing in an oxidizing ambient can easily cause the formation of interfacial layers [27]. The last group is comprises mainly silicides such as HfSi<sub>x</sub>O<sub>v</sub>, ZrSi<sub>x</sub>O<sub>v</sub>, SrTaO<sub>6</sub> or ZrSiO<sub>4</sub>. These multi-component oxides are compatible with and stable on silicon substrate.

Up until now, none of the above materials has emerged as the most likely candidate to meet all of the complex and stringent requirements associated with processing, device performance and reliability. Most research has been focused on the different growth technologies of the high-k dielectrics. Chemical vapor deposition (CVD) and metal-organic CVD (MOCVD) are still most commonly used on some of the materials. Ion-beam sputtering can produce SrTiO<sub>3</sub> films with well-crystallized and void-

free structures. RF magnetron sputtering, laser ablation, and electron cyclotron resonance plasma-assisted RF sputtering all have been tried in growing high-k materials [28]. Molecular Beam Epitaxy (MBE) and Atomic Layer Deposition (ALD) are also used to precisely control the growth of high-k dielectrics. One of the promising reports comes from the thermal oxidation of amorphous La to directly form La<sub>2</sub>O<sub>3</sub> dielectric layer. The resulting capacitor has 33Å La<sub>2</sub>O<sub>3</sub> layer with EOT of 4.8Å and a k-value of 27. It also has low leakage current 0.06A/cm<sup>2</sup> at ~1V and high breakdown field of 13.5MV/cm [23]. The thermal oxidation method used here is very similar to the conventional thermal SiO<sub>2</sub> growth in comparison with CVD or sputtering deposited gate dielectrics. Recently, Ruzyllo's group at Penn State developed a liquid source misted chemical deposition (LSMCD) technique in which the liquid metal-organic precursors is atomized and deposited in a controlled amount in the form of sub-micron mist droplets onto the wafer surface at room temperature and atmospheric pressure [29].

Buffer layers are usually used between the Si and the high k dielectric. Jet vapor-deposited (JVD) nitride film or NH<sub>3</sub>/NO nitrided films are reported to improve the interface quality, reduce the stress, and suppress the inter-diffusion between Si and the high-k dielectric. However, the results are far from being conclusive. MOS capacitors (MOSCAPs) and MOS field-effect transistors (MOSFETs) with thin HfO<sub>2</sub> dielectrics and n<sup>+</sup> polycrystalline silicon (poly-Si) gate electrodes can be made without any barrier layer but they require rapid thermal annealing (RTA) activation of the poly-Si gate instead of furnace annealing [30].

Very few studies have been conducted to show how high-k dielectric growth could affect the quality of the interface between the high-k dielectric and silicon, or the region just below the interface. As is well known, one of the major advantages of using silicon dioxide for the gate dielectric is its near perfect match with the silicon substrate. Without a high quality interface, interface states and near-interface bulk states can act as minority carrier traps that are detrimental to the MOS device operation.

The study of high k materials and the corresponding gate stack system (high-k dielectric, interfacial layers, electrode, and their compatibility with plasma processing and the CMOS process flow) still remains at the research stage and far from production line. Major breakthroughs are very much welcome and are eagerly searched for to prepare for the 100 nm technology generation fast approaching and due in the year 2006.

#### 1.4 Thesis research scope

The first part of this thesis research is on the study of the various issues related to miniaturization and scaling of MOS structures. We focused on thin silicon dioxide that is currently in use as a gate dielectric in CMOS but is steadily reduced in thickness to meet CMOS standards. The severity of damage to the silicon dioxide induced by processing, especially plasma etching is one of the research areas addressed in this thesis. Effective ways of characterizing the thin oxide and, hence, evaluate MOSFETs and MOS capacitors performance are discussed. Subsequently, we subjected the oxide to Fowler-Nordheim and hot carrier stresses, thereby mimicking device damage by processing and/or device aging. In the second phase of this thesis research we examined a number of

high-k candidates to replace the oxide as a gate dielectric. These high-k dielectrics are investigated in terms of their dielectric, interface, leakage and breakdown properties. The interfacial layer between the high-k dielectrics and the silicon substrate, either grown intentionally or unintentionally, are examined and their effects on the electrical properties of the gate dielectric stack are analyzed in details. Also, the impact of high-k dielectrics deposition on the underneath silicon substrate is investigated in the course of thesis studies

*Table 1–1:* Electrical properties of some high-k candidates

|                                  | - (       | T        |

|----------------------------------|-----------|----------|

| Gate Dielectric                  | $E_g(eV)$ | K        |

| SiO <sub>2</sub>                 | 9         | 3.9      |

| Si <sub>3</sub> N <sub>4</sub>   | 5         | 7.5      |

| Al <sub>2</sub> O <sub>3</sub>   | 8.7       | 8.5-10.5 |

| Ta <sub>2</sub> O <sub>5</sub>   | 4-4.5     | 20-35    |

| TiO <sub>2</sub>                 | 3-3.5     | 30-100   |

| BaSrTiO <sub>3</sub>             | *         | 200-300  |

| La <sub>2</sub> O <sub>3</sub>   | *         | 27       |

| Y <sub>2</sub> O <sub>3</sub>    | 5.6       | 15       |

| CeO <sub>2</sub>                 | 5.5       | 26       |

| HfO <sub>2</sub>                 | 5.7       | 25       |

| ZrO <sub>2</sub>                 | 5.8       | 25       |

| HfSi <sub>x</sub> O <sub>y</sub> | 6         | 15-25    |

| ZrSi <sub>x</sub> O <sub>y</sub> | 6         | 15-25    |

| SrZrO <sub>3</sub>               | 5.4       | 30       |

| SrHfO <sub>3</sub>               | *         | 28       |

| Sr <sub>2</sub> TiO <sub>4</sub> | 5.2       | 50       |

| L <sub>a</sub> AlO <sub>3</sub>  | 5.7       | 25       |

|                                  |           |          |

. . .

<sup>\*:</sup> no reliable values are published for these parameters.

#### Chapter 2

**Experimental Procedure: Test Structures and Electrical Characterization Methods**

#### 2.1 Test Structures

The performance of a MOS transistor is largely determined by the quality of gate dielectrics and its interface with the silicon substrate. The effective carrier mobility, which essentially determines the speed of a MOS transistor, largely depends on the density and distribution of interface/bulk/dielectric traps. Most electrical characterization techniques are focused on how to locate and identify these traps. And most characterization methods are applied on two basic types of test structures: MOS capacitors and MOS transistors.

During the early stages of the development of MOS technology, the MOS capacitor has been used as the principal test vehicle for investigating and understanding the properties of the MOS system. In fact, much of the present knowledge of the properties of this system has been acquired by small signal admittance measurements on MOS capacitors. As pointed out by Nicollian and Brews, more than 20 properties of the MOS system can be measured and monitored using MOS capacitors [31].

Unfortunately, with the continuous miniaturization of CMOS, some new effects and phenomena appear to be inherent to MOS transistor itself and can only be observed by direct characterization on the transistor. These include junction edge effects, short channel effects, hot carrier induced interface degradation and mobility degradation due to thin gate oxides [32, 33, 34]. For this reason, the characterization of the submicron MOS transistor becomes mandatory for the development of new CMOS circuits and semiconductor memories.

Does that mean the characterization techniques on the capacitor structure have lost their significance? The answer to this question is no. Let us take the case of charging damage to oxide during the gate poly-Si etching process as an example. Both of these two test structures, MOS capacitor and transistor, have their advantages and disadvantages. A transistor is a very sensitive device and requires much smaller antenna than the capacitor for the charging damage detection. However it requires additional steps to complete the fabrication after the gate poly-Si etching. Therefore, the damage caused by gate poly-Si definition etching may be obscured by subsequent processing steps. Alternatively, a capacitor can detect the charging damage directly after the gate poly-Si definition etching. On the other hand, capacitance measurements require a large antenna. Therefore, in order to obtain detailed information one needs to perform the tests on both device structures and preferably using different techniques. This is what we attempt to do in our proposed studies. We will use both MOS capacitor and transistor structures, and we will utilize a number of electrical characterization techniques.

In the following sections, we will discuss the electrical characterization techniques that are employed in our studies. The physical principles utilized in these techniques are well documented in various books and journal articles and thus will be only briefly reviewed below. We will mainly highlight the advantages and limitations of these characterization methods. We will also point out some precautions we need to take during the tests and data interpretation.

#### 2.2 Electrical Characterization Methods

#### 2.2.1 Transistor Parameter Measurements

There are three principal DC MOSFET parameters, threshold voltage ( $V_{th}$ ), transconductance ( $G_m$ ) and subthreshold swing (S). The easiest way to understand the information on the state of the MOSFET provided by these three transistor parameters is to write down their expressions using an enhanced mode n-channel device as an example [35,36]. These expressions are :.

$$V_{th} = V_{fb} + 2\Phi_f - \frac{1}{C_{or}}(Q_d + Q_{it})$$

(2.1)

where  $V_{fb}$  is the flat-band voltage,  $\Phi_f$  is the Fermi potential,  $C_{ox}$  is the oxide accumulation capacitance, and  $Q_d$  and  $Q_{it}$  are the depletion and interface charges, respectively; and

$$G_{m} = \frac{dI_{d}}{dV_{g}} = \left(\frac{W}{L}\right) C_{ox} V_{d} \frac{C_{i}}{C_{ox} + C_{d} + C_{i} + C_{ii}} \frac{\mu_{eff}^{2}}{\mu_{o}}$$

(2.2)

where  $I_d$  is the drain current,  $V_g$  the gate voltage, and  $V_d$  the drain voltage. The capacitances  $C_i$ ,  $C_d$ , and  $C_{it}$  are for the insulator, depletion region, and interface, respectively.  $\mu_{eff}$  is the effective mobility,  $\mu_o$  is the low-field mobility (at the threshold where  $Q_{it}$ , the interface charge, is zero). W and L are the channel's width and length, respectively;

$$S = \frac{G_m}{I_d}, D_{it} = \frac{C_{ox}}{q} \left( \frac{q}{SkT} - 1 - \frac{C_d}{C_{ox}} \right)$$

(2.3)

where S is the swing and  $D_{it}$  is the interface state density. q, T, and k are the electronic charge, absolute temperature, and Boltzmann constant, respectively.

As can be seen above,  $V_{th}$  reveals the polarity and quantity of charge trapped in the interface and bulk gate dielectric.  $G_m$  is proportional to the effective carrier mobility, and S is inversely proportional to the interface density.

Transistor parameter measurements are fast and informative. Cumulative probability results are usually collected from 14 to 20 devices to determine the uniformity of the transistor fabrication process. The characterization systems are easy to operate.

They usually serve as in-house monitoring tools to control the quality of device fabrication. Also they are very useful tools in the characterization of stressed devices [37].

However, despite of these formulas, these three transistor parameters usually serve as visual and qualitative measures of transistor condition. The subthreshold swing,

S, is only appropriate when the interface trap density is relatively high (> $5x10^{10}$ - $10^{11}$  eV<sup>-1</sup>cm<sup>-2</sup>) thus is not adequate for the evaluation of the interface trap density in virgin MOS devices fabricated using state-of-the-art technology where  $D_{it}$  lies in the range of  $5x10^9$ - $10^{10}$  eV<sup>-1</sup>cm<sup>-2</sup> [38]. The transconductance  $G_m$  is strongly affected by the short channel effects that are present in submicron devices [39]. Also from the threshold voltage data, it is hard to distinguish the effects of bulk dielectric charge from those of interface traps. Moreover, it will be shown in the following chapter that one of the main conclusions of our studies is that these three transistor parameters become less sensitive in characterizing devices with ultra thin gate oxides that are thinner than 50Å [40].

#### 2.2.2 Capacitance Voltage (CV) Measurements

Capacitance-versus-voltage (CV) measurements are the most common characterization techniques used on MOS capacitors. A quick and simple CV scan can yield doping profiles of diffusions, implants, or bulk materials. It can reveal oxide characteristics which may be influenced by oxide deposition, annealing, stress or device damage, and it can also be used to calculate interface characteristics such as interface trap density (D<sub>it</sub>) and metal-semiconductor work functions [41,42]. However, we must take a few precautions when measuring and interpreting CV data, especially on VLSI capacitors. We must also note the limitations of CV measurements on ultra thin oxide capacitors as we point out in the following.

First, the voltage sweep should be performed from inversion to accumulation after a stable inversion condition is established. This insures that we obtain a correct flat

inversion capacitance instead of a slowly decreasing deep depletion capacitance [43]. Secondly, series resistance plays an increasing role in measurements performed on capacitors with extremely thin gate oxide. This is illustrated in the simple formula given below which applies to most commercial CV systems,

$$C_p = \frac{C_s}{1 + \omega^2 R_s^2 C_s^2} \tag{2.4}$$

where  $C_p$  and  $C_s$  are the measured capacitance and actual oxide capacitance, respectively.  $R_s$  is the series resistance which originates primarily in the substrate and in the back contact between the substrate and the probe chuck. Most monitoring capacitors tend to have large areas while maintaining the same thin oxide thickness, i.e. they give much larger capacitances than the real devices. The coupling of  $R_s$  and  $C_s$  could cause a significant distortion in CV data and misleads their interpretation [44,45]. Thirdly, CV measurements are often unsuccessful on ultra thin gate oxide (<50Å) capacitors, mainly due to the large gate leakage current. Park and co-workers pointed out the difficulty of obtaining reasonable CV data on their 52Å-thick gate oxide,  $40\mu m \times 40\mu m$  capacitors, which effectively rules out the possible observation of CV shift on samples with different metal peripheral length [46].

#### 2.2.3 Charge Pumping Measurement

The charge pumping technique was first introduced by Brugler and Jespers [47] in 1969. This technique is based on a recombination process at the Si/SiO<sub>2</sub> interface of a MOS transistor involving the interface states. This recombination induces a substrate current that can be directly related to the interface-state density. Ever since then, several authors have developed and presented different ways of applying this principle for the determination of the average density of interface traps [47-50], their energy distribution [51,52], and even the geometric mean value of the capture cross section for electrons and holes at these traps [50].

The major advantage of the charge pumping (CP) measurement is it can be performed directly on the actual MOS transistors instead of monitoring MOS capacitors. Not only it eliminates the extrapolation of results from capacitors to transistors, it also can detect most phenomena that are unique to the transistor system [53].

Through CP measurement, the lateral distribution of interface traps as well as the energy distribution of these states can be determined. In modern short channel devices, the channel is usually non-uniform, either from process damage or from being subjected to hot-carrier stress. CP technique enables the probing of the interface as a function of position in the non-uniform channel [54]. It is quick, relatively simple, and it can yield precise results on the damage from FN stress, radiation, and/or hot carrier stress.

#### 2.2.4 Deep Level Transient Spectroscopy

Deep-level transient spectroscopy (DLTS) was first developed by D.V.Lang [55]. It monitors the change of capacitance transients by controlled filling and emptying of carriers from deep levels. The activation energy level, cross section and the space distribution of the traps can thus be derived from the DLTS signal. There are two basic ways to perform DLTS measurements. The traditional way is through a 'rate window': a system which produces a peak output when the time constant of the input transient corresponds to a reference time set on the instrument. This can be implemented using a double "box-car" system, a lock-in amplifier or an exponential correlator. Another way is called Fourier-transform deep level transient spectroscopy (FTDLTS) [56]. In this technique the capacitance-time transients are digitized, and the discrete Fourier coefficients are found via numerical Fourier transformation. These coefficients can be used to calculate amplitude and time constant of the transients for discrete trap levels.

The transient signal from DLTS measurement can result from traps located in the semiconductor substrate, the semiconductor-silicon interface, and in the bulk oxide region close to the semiconductor oxide interface. DLTS is the most widely used technique for the characterization of deep states in semiconductors, especially for routine material evaluation, because it presents the information in a convenient quasi-spectroscopic form that can be visually interpreted.

DLTS can be applied on both capacitor and transistor structures. In the latter case, bias and pulse voltage are applied to gate while the drain-source current is monitored instead of the capacitance. The basic principle here is still the same. The change of

current transient comes from the filling and emptying of carriers from deep levels [57-59].

There are a few limitations on the DLTS technique, however. It requires an elaborate experimental set-up using synchronized pulse sources, integrators and time averagers. It also requires a relatively large area test device to get distinguishable capacitance/current signal. Also, each DLTS scan requires much longer time (0.5-1 hour) than a routine IV/CV/CP measurement (a few minutes) therefore it is not realistic to use it to produce statistical data. Because of that, there have been very few reports on its application on VLSI devices [60]. On the other hand, the DLTS technique offers a wealth of information that is not possible to get from other characterization techniques.

#### 2.3 Measurement Equipment

A 4142B Hewlett-Packard Semiconductor Parameter Analyzer was used to measure transistor parameters which included  $V_{th}$ , S, the leakage current ( $I_g$ , measured at a gate voltage  $V_g$ =2V), and maximum transconductance ( $G_m$ ), which is hereafter referred to as transconductance for brevity. Probability plots were then generated from the data with each plot containing results from at least 12 transistors. Charge pumping measurements were performed using a Wavetech 20 MHz Frequency Generator and the 4142B HP Parameter Analyzer. The CV and DLTS measurements were done using a Keithley system and a Bio-Rad DL8010 Fourier-transform DLTS system, respectively.

## Chapter 3

Thin Gate Oxides: (I) Plasma Induced Damage and Damage Detection

#### 3.1 Introduction

Any device parameter that is sensitive to oxide charge and interface traps can be used to monitor the degradation of MOSFETs. The threshold voltage ( $V_{th}$ ), maximum transconductance ( $G_m$ ) and subthreshold swing (S) are the three traditional transistor parameters which are commonly used in device characterization. For more than three decades, these three parameters were used as indicators of process-induced damage to MOSFETs [61,62,64]. However, in this chapter we demonstrate that  $V_{th}$ ,  $G_m$  and S cease to be effective in monitoring plasma-induced damage in very thin gate oxide ( $\leq$ 65Å) MOSFETs.

In this chapter, we examined the plasma-induced damage aspects in 65Å-thick and 45Å-thick gate-oxide MOSFETs. These devices were fabricated using a  $0.35\mu m$  full CMOS process flow and subjected to damage from different plasma processes, e.g., contact or via etching. We found out that  $V_{th}$ ,  $G_m$  and S measurements revealed very little to no information with respect to process induced damage in these devices. Even charge pumping (CP) measurement, one of the most sensitive characterization methods, was not able to probe process-induced damage aspect in these very thin gate-oxide devices. In contrast, we clearly establish that gate leakage current ( $I_g$ ) becomes a very sensitive

parameter which could be reliably used in assessing damage to thin gate oxide MOSFETs.

### 3.2 Device Fabrication and Test Structures

The n-channel MOSFETs used in this study were fabricated on 200 mm boron-doped (~10<sup>17</sup>cm<sup>-3</sup>) epitaxial silicon substrates using the SEMATECH 132AZ mask set [69]. The channel length and width for these transistors were 0.35 and 5.0μm, respectively. The thickness of the gate oxide, grown at 900°C in dry O<sub>2</sub> ambient, was either 65Å or 45Å. The poly-Si gate definition etching, the contact etching and the metal etching employed a Cl<sub>2</sub>/HBr, a CHF<sub>3</sub>/CF<sub>4</sub> and a BCl<sub>3</sub>/N<sub>2</sub>/Cl<sub>2</sub> based chemistries, respectively. All etching processes were performed using commercial reactive-ion-etching and transformer coupled plasma tools. After metallization, all transistors were given annealing in forming gas (6% H<sub>2</sub> and 94% N<sub>2</sub>) at 400 °C for 30 minutes.

Four test modules, Type I, II, III and IV, were used in this study. These modules differ in oxide thickness and/or vulnerability to damage from a certain plasma process, as given in *Table 3–1*. Each module comprises transistors that had different antenna ratios (ARs). Here AR refers to the area ratio between poly-Si field oxide, metal 1 pad, or metal 2 pad coverage and gate-oxide coverage, depending on the plasma process examined. The ARs used were 5770, 14470 and 62220. The number of via holes in Type I and IV modules, and the number of contact holes in Type I module were 58×58 (the number of holes is given as a product of two numbers to emphasize the rectangular geometry of the via or contact hole arrays with a total number of holes that is equal to the product). In

Type II and III modules, the number of contact and via holes were kept at a minimum of 2×2 to minimize the corresponding damage. In Type III sample, the area of metal 1 interlayer was also kept as minimum to reduce the damage from metal 1 process. All modules had the same size of metal 2 pad.

# **3.3 Experimental Results**

Figure 3.1 shows V<sub>th</sub> and S for Type I module (45Å-thick gate-oxide) with different antenna ratios (AR=5770, 14470 and 62220 at poly-Si, metal 1 and metal 2 etch steps). No significant differences can be seen in both  $V_{\text{th}}$  and S for different ARs. The percentage distributions of data for different AR are similar. The maximum median variations in V<sub>th</sub> and S, as a function of AR, are less than 5 mV and 0.2 mV/dec., respectively. G<sub>m</sub> for this Type I module (not shown) also yields a similar pattern to V<sub>th</sub> and S: no observable changes in G<sub>m</sub> with AR. In essence, none of the three parameters, V<sub>th</sub>, S and G<sub>m</sub>, has been able to discern differences in damage from different ARs. However, it is currently very well established that charging damage clearly increases with increasing AR [66, 70]. We reiterate that this Type I module is designed such that it would be subjected to the highest charging damage from the poly-Si etch and the two metal etches. During the poly-Si gate definition and the metal etching processes, the poly-Si or metal pads attached to the thin gate oxide act as charge collecting electrodes, which will impose a stress voltage across the oxide and Si/SiO<sub>2</sub> interface. This voltage increases with increasing pad area that is proportional to the AR, and results in a Fowler-Nordheim (FN) tunneling current flow through the thin oxide. The larger the AR, the

higher the stress voltage and current across the oxide and consequently the higher the damage to the MOSFET [62, 64-66, 70]. It is not likely that reducing the oxide thickness would totally eliminate this damage [66]. We can only assume that the damage is so low that  $V_{th}$ ,  $G_m$ , S can no longer reveal its dependence on AR.

The  $I_g$  probability plots for the same Type I MOSFETs are shown in *Figure 3.2*. Even when a logarithmic scale is used as in *Figure 3.2*, the dependence of  $I_g$  on AR is very clear. The transistors with the largest AR (62220) yield the largest leakage currents (a median current of  $10^2 \sim 10^3$  nA), while transistors with the smallest AR (5770) have leakage currents only in the range of  $\sim 1$ nA. The differences in  $I_g$  are up to three orders of magnitude. As explained before, this is what we would expect from these transistors – the larger AR a transistor has, the more damage it incurs during the plasma processing. Measurements on other modules in this 45Å-oxide wafer were performed and all results showed similar patterns: larger AR yielded larger  $I_g$ , while no clear shifts in  $V_{th}$ ,  $G_m$  and S could be observed. Therefore we may reasonably conclude that, at least for the 45Å gate-oxide devices,  $I_g$  is a more sensitive parameter than  $V_{th}$ ,  $G_m$  and S in monitoring plasma-induced damage in the MOSFETs.

Figure 3.3 shows the  $I_g$  data from measurements on Type II, III and IV modules (all with oxide thickness of 65Å) with two different ARs (AR=5770, 62220). Two general trends can be observed. First, for transistors in the same module but with different ARs, those with larger ARs yield larger  $I_g$ . This is exactly what we found in type I module. Second, for different modules,  $I_g(IV) > I_g(III) > I_g(III)$  where the Roman numbers between brackets indicate the type. Type IV module is sensitive to damage from metal 1,

via and metal 2 etch steps since transistors bear charging antennas for each one of these processes. Therefore, expectedly, this module must be the most damaged as witnessed by the largest  $I_g$ . Type II module was primarily sensitive to metal 1 etch damage. Although this module employed a small metal 2 AR to reduce the damage from metal 2 etching, the size of metal 2 pad, which is kept the same for all modules, is still large enough to induce significant additional damage during the metal 2 process. Hence, Type II module shows an intermediate  $I_g$  between that of Type IV and Type III. Type III module, however, employed a minimum area of metal 1 inter-pad that is much smaller than the metal 2 pad. Therefore it only experienced damage during the metal 2 process. Consequently,  $I_g$  becomes the smallest one. Here again  $I_g$  is able to differentiate between slight changes in the degree of damage for different modules.

Figure 3.4 shows the  $I_g$  dependence on AR for Type III module. It is interesting to note here that in spite of the very low leakage current ( $\sim$ pA), it is still possible to observe the AR dependence of  $I_g$ . The small  $I_g$  in this module strongly implies that Type III module suffered the least damage during the whole process.

We now move on to study the other three transistor parameters  $V_{th}$ ,  $G_m$ , S in the 65Å-thick gate-oxide devices and see if they exhibit similar patterns to those in *Figure 3.3 . Figure 3.5* shows  $V_{th}$  and  $G_m$  for Type II, III and IV modules with different ARs. The results in *Figure 3.5* are the median values from probability curves of sets of 12 devices.  $G_m$ , for different modules and ARs, does not reveal any differences. When AR = 5770, all three modules have roughly the same  $G_m$  (~141 $\mu$ S), whereas when AR increases to 62220, the difference in  $G_m$  between the three modules is still less than 3  $\mu$ S. As for

V<sub>th</sub>, we notice that it decreases with increasing AR, which indicates positive charge buildup in the oxide. However, unlike I<sub>g</sub>, we are not able to find any correlation between the three modules, and the variance in V<sub>th</sub> is less than 4%, or 25 mV. We also note that there is no significant change in S (not plotted) for different modules and different ARs. Charge pumping (CP) measurement was used to detect the damage aspects in the 65Åthick oxide modules. Figure 3.6 shows typical CP curves for Type III module with AR=5770 and 62220. As can be seen, the two curves of the Type III module almost overlap with each other. Repeated CP measurements on the same Type III modules in different locations in the wafer show that differences in CP current with different ARs are less than 5%. We also performed CP measurements on Type II and IV modules. At AR=5770, Type II yields slightly higher CP current peak than Type III, as shown in Fig. 3.6. When AR further increases, the height of the CP current peak increases but is quickly undermined by the high leakage current tail. No CP curve could be obtained in Type IV due to the high gate leakage current even at low AR. Higher CP peak indicate more damage in the transistor, especially at the Si/SiO<sub>2</sub> interface. The CP data in Fig 3.6 enables us to draw the following conclusions: (1) just like  $V_{th}$ ,  $G_m$  and S, CP is unable to resolve interface damage dependence on AR in lightly damaged Type III module; and (2) from CP it is possible to observe differences in damage degree between the different modules. Our CP data agrees with I<sub>g</sub> measurements in that the Type IV module was the most damaged, whereas Type III was the least damaged.

### 3.4 Discussion

We have shown that the gate leakage current  $I_g$  is a very sensitive parameter to monitor the quality of thin gate-oxide MOSFETs. It can differentiate between damage aspects from different plasma processes, as well as the damage dependence on antenna ratio. Longer plasma process with harsher processing conditions and larger AR in a processed device results in more damage, which is correlated to larger  $I_g$ . Traditional transistor parameters  $V_{th}$ ,  $G_m$  and S are no longer good characterization parameters as the gate oxide becomes too thin ( $\leq$ 65Å). In our experiments, these three parameters failed or partially failed to give sufficient information regarding damage from plasma processing. On the other hand, charge pumping measurement, which is believed to be extremely sensitive to defect states at  $Si/SiO_2$  interface and in the channel region of MOSFETs, is also not informative in the case of ultra-thin oxides, since it did not reveal the AR dependence in lightly damaged samples (Type III), and it failed when gate leakage current became large.

It should be noted that all of our measurements were performed on thin gate-oxide (45Å and 65Å) devices, i.e., results of the type presented in section (III) are the consequence of continuously shrinking the oxide thickness in submicron MOSFETs. In fact, our previous work on relatively thick oxide ( $\geq$ 90Å) devices did not call for the importance of Ig [70]. In 90Å-thick gate-oxide MOSFETs, Ig was very small within the range of 100 fA/ $\mu$ m² or less, thus it could hardly be used to distinguish damage between different samples. Our results also showed that, in 90Å-thick oxide MOSFETs, measurements of V<sub>th</sub>, G<sub>m</sub> and S were capable of bringing out the damage dependence on

ARs. Due to the hydrogen passivation of defects during post-metal annealing, the shifts of these parameters as a function of AR were extremely small, nonetheless these shifts were still observable [70]. However, when the oxide becomes thinner ( $\leq$ 65Å), these shifts become less and less significant, as shown in our previous figures. Comparing  $V_{th}$  in *Figure 3.1* with  $V_{th}$  in *Figure 3.5*, we notice that shifts in  $V_{th}$  with different AR are much smaller in 45Å-thick gate-oxide samples (5mV) than in 65Å-thick gate-oxide samples (25mV). This is also the case with shifts in  $G_m$  and S.