## The Pennsylvania State University

### The Graduate School

### SYSTEM LEVEL POWER AND RELIABILITY MODELING

A Thesis in

Computer Science and Engineering

by

Ing-Chao Lin

© 2007 Ing-Chao Lin

Submitted in Partial Fulfillment

of the Requirements

for the Degree of

Doctor of Philosophy

August 2007

The thesis of Ing-Chao Lin was reviewed and approved\* by the following:

Vijaykrishnan Narayanan Professor of Computer Science and Engineering Thesis Advisor, Chair of Committee

Mary Jane Irwin Distinguished Professor of Computer Science and Engineering Evan Pugh Professor, A. Robert Noll Chair of Engineering

Yuan Xie Assistant Professor of Computer Science and Engineering

W. Kenneth Jerkins Professor of Electrical Engineering

Nagu Dhanwada Senior R&D Engineer and Team Lead, IBM Special Member

Raj Acharya Professor of Computer Science and Engineering Head of the Department of Computer Science and Engineering

<sup>\*</sup>Signatures are on file in the Graduate School.

# **Abstract**

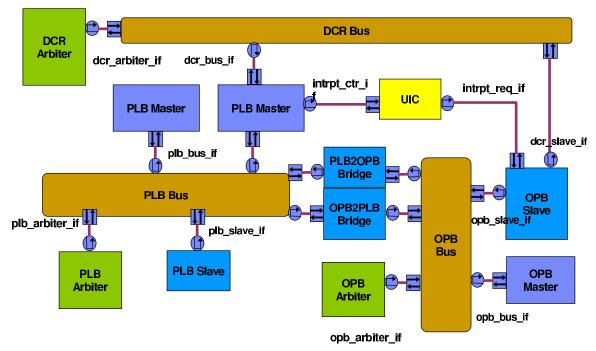

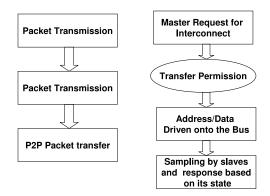

This thesis provides system level modeling for power, reliability, and device degradation. In the system level power modeling, we use transaction level modeling. Transaction level modeling (TLM) represents the communications of IP cores as transactions and provides higher simulation speed than lower level of abstraction. We construct a hierarchical power modeling tree and augment the transaction level models with power estimation functions. We demonstrate the power estimation methodology on PCI Express transaction level models, and create various scenarios and validate the methodology on IBM CoreConnect platform. We also present experimental results to validate the accuracy and speed of our approach.

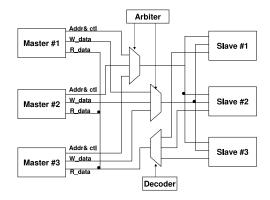

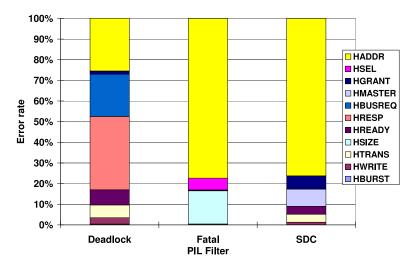

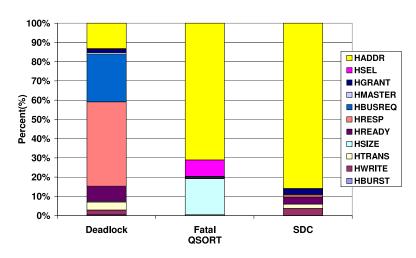

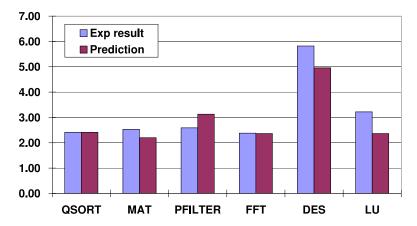

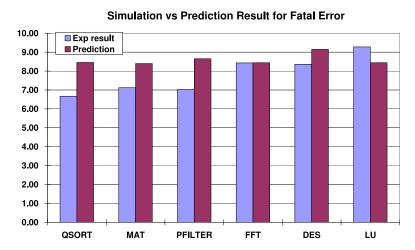

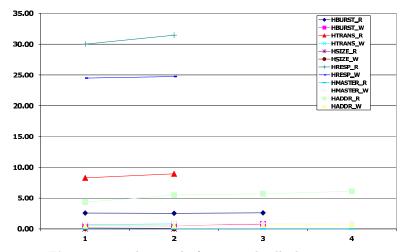

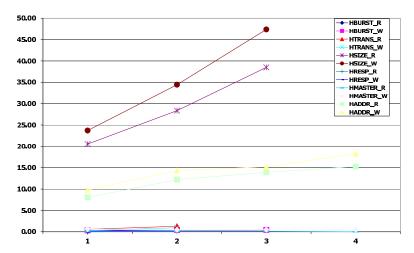

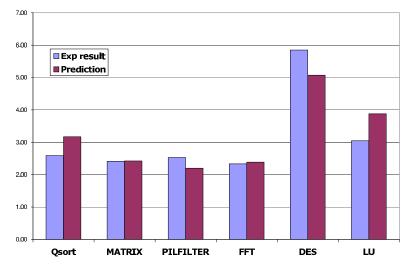

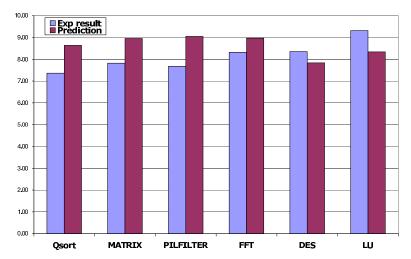

In the system level reliability modeling, we propose a transaction-based error susceptibility model for a bus-based System-on-Chip system. This reliability model provides a detailed analysis of different kinds of errors and the susceptibility of such systems to such errors on various components that comprise the bus. We inject single and multi-bit error during the execution of various transactions and examine the effect of the errors. Experimental results demonstrate error susceptibility of signals are similar across the benchmarks. Such transaction-based analysis helps us to develop an effective prediction methodology to predict the effect of a single and multi-bit error on any application running on a bus-based architecture. We demonstrate that our transaction-based prediction scheme works with an average accuracy of 91% over all the benchmarks when compared with the actual simulation results.

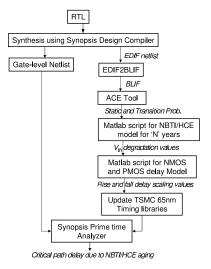

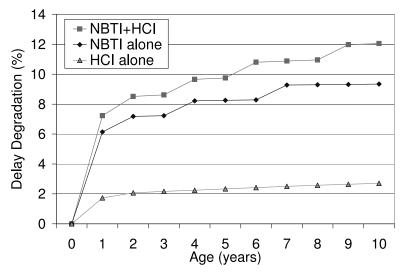

In the system level modeling for device degradation, we explore how Negative Bias Temperature Instability (NBTI) and Hot Carrier Effects (HCE) cause device degradation in the system. We discuss the tool we developed: a HCE and NBTI Incorporated Tool for ASICs (HANITA), for the complete analysis of circuit degradation. The tool analyzes the degradation impact on bus systems and the vulnerability of buses to such circuit degradation. We propose a hardware-based mechanism to detect the timing degradation and we further propose a PROactive BUS (PROBUS) architecture that dynamically adapts to retain the system functionality even after the system timing degrades.

# **Table of Contents**

| Lis            | t of                             | Figur   | es                                                           | vii          |

|----------------|----------------------------------|---------|--------------------------------------------------------------|--------------|

| Lis            | t of                             | Table   | S                                                            | ix           |

| $\mathbf{Acl}$ | kno                              | wledgr  | nents                                                        | $\mathbf{x}$ |

| $\mathbf{Ch}$  | apte                             | er 1    |                                                              |              |

|                | $\overline{\operatorname{Intr}}$ | oduct   | ion                                                          | 1            |

|                | 1.1                              | Thesis  | s Contribution                                               | 5            |

| $\mathbf{Ch}$  | apto                             | er 2    |                                                              |              |

| -              | Tra                              | nsactio | on Level Power Modeling                                      | 8            |

|                | 2.1                              | Trans   | action Level Modeling                                        | 9            |

|                |                                  | 2.1.1   | Definition of Transaction Level Modeling                     | 10           |

|                |                                  | 2.1.2   | Advantages of Transaction Level Modeling                     | 14           |

|                | 2.2                              | Trans   | action Level Power Modeling                                  | 15           |

|                | 2.3                              | PCI E   | Express Architecture                                         | 16           |

|                | 2.4                              | Trans   | action Level Models for PCI Express                          | 21           |

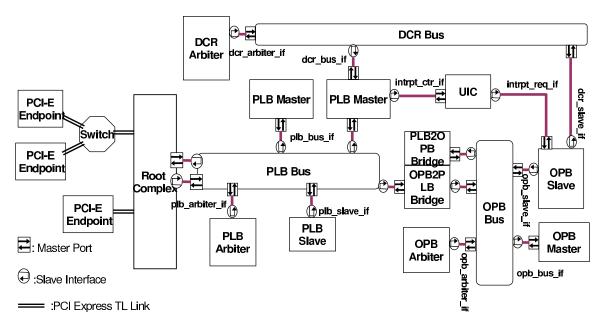

|                |                                  | 2.4.1   | IBM PowerPC 405 Evaluation Kit                               | 22           |

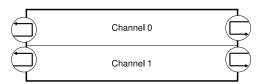

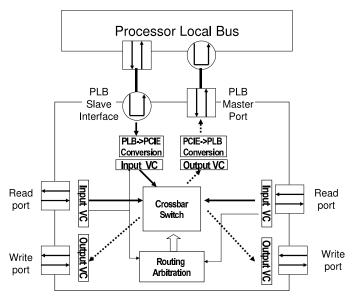

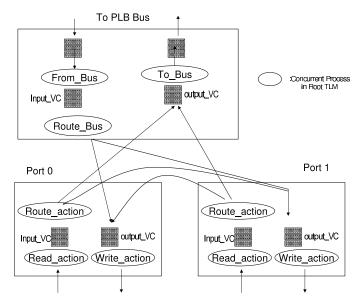

|                |                                  | 2.4.2   | PCI Express Transaction Level Models                         | 23           |

|                | 2.5                              | Power   | Estimation Methodology for Transaction Level Models          | 30           |

|                |                                  | 2.5.1   | Identify Transactions and Parameters                         | 32           |

|                |                                  | 2.5.2   | Parameters for PCI Express TLM                               | 32           |

|                |                                  | 2.5.3   | Characterize Power Consumption of Each Transaction and Build |              |

|                |                                  |         | HTLP Trees                                                   | 34           |

|                |                                  | 2.5.4   | Augment TLM with Power Estimation Functions                  | 35           |

|                |                                  | 2.5.5   | Simulation Execution                                         | 36           |

|                | 2.6                              | System  | m Instantiation and Simulation for PCI Express TLM           | 37           |

|                | 2.7                              | Valida  | ation of Power Estimation Methodology                        | 41           |

| Chapter 3 Transaction-based Reliability Modeling for Bus-based SoC 3.1 Introduction and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44<br>45<br>47<br>49<br>50<br>52<br>52<br>54<br>55<br>56<br>58 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Transaction-based Reliability Modeling for Bus-based SoC  3.1 Introduction and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 45<br>47<br>49<br>50<br>52<br>52<br>54<br>55<br>56<br>58       |

| 3.1 Introduction and Motivation 3.2 Related Work 3.3 Bus Architectures 3.4 Error Characterization Model 3.4.1 Single-bit Error Injection 3.4.2 Consequences of Both Single- and Multi-bit Errors 3.4.3 Single-bit Transaction-based Error Characterization 3.4.4 Single-bit System Level Error Prediction 3.4.5 Single-bit Error Experimental Setup 3.4.6 Single-bit Error Injection Results 3.5 Multi-bit Error Characterization Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47<br>49<br>50<br>52<br>52<br>54<br>55<br>56<br>58             |

| 3.2 Related Work 3.3 Bus Architectures 3.4 Error Characterization Model 3.4.1 Single-bit Error Injection 3.4.2 Consequences of Both Single- and Multi-bit Errors 3.4.3 Single-bit Transaction-based Error Characterization 3.4.4 Single-bit System Level Error Prediction 3.4.5 Single-bit Error Experimental Setup 3.4.6 Single-bit Error Injection Results 3.5 Multi-bit Error Characterization Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47<br>49<br>50<br>52<br>52<br>54<br>55<br>56<br>58             |

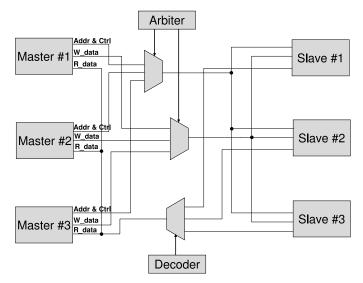

| 3.3 Bus Architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49<br>50<br>52<br>52<br>54<br>55<br>56<br>58                   |

| 3.4 Error Characterization Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 50<br>52<br>52<br>54<br>55<br>56<br>58                         |

| 3.4.1 Single-bit Error Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52<br>52<br>54<br>55<br>56<br>58                               |

| 3.4.2 Consequences of Both Single- and Multi-bit Errors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52<br>54<br>55<br>56<br>58                                     |

| 3.4.3 Single-bit Transaction-based Error Characterization 3.4.4 Single-bit System Level Error Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>55<br>56<br>58                                           |

| 3.4.4 Single-bit System Level Error Prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 55<br>56<br>58                                                 |

| 3.4.5 Single-bit Error Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>58                                                       |

| 3.4.6 Single-bit Error Injection Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 58                                                             |

| 3.5 Multi-bit Error Characterization Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62                                                             |

| order right are Error injection to the terror to the terro | 62                                                             |

| 3.5.2 System Level Prediction for Multi-bit Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                             |

| 3.5.3 Multi-bit Error Injection Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65                                                             |

| 3.6 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                              |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |

| System Level Modeling for Device Degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>68</b>                                                      |

| 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                             |

| 4.2 Related Work and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72                                                             |

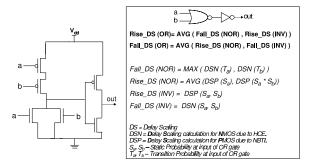

| 4.3 HANITA: HCE And NBTI Incorporated Tool for ASICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73                                                             |

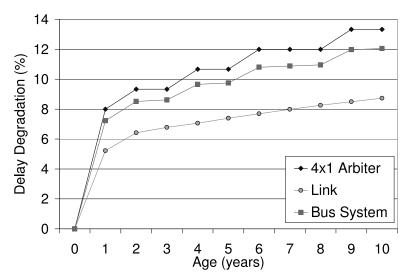

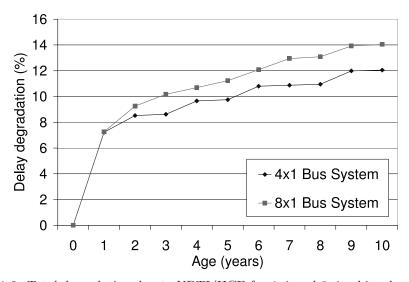

| 4.4 Degradation Analysis of On-chip Bus System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 76                                                             |

| 4.5 Countering Aging in Bus System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                             |

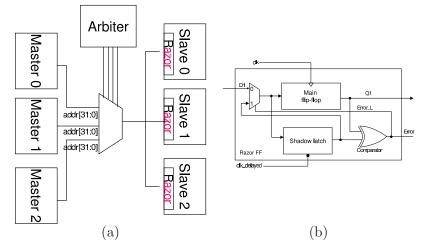

| 4.5.1 Detecting Degradation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 80                                                             |

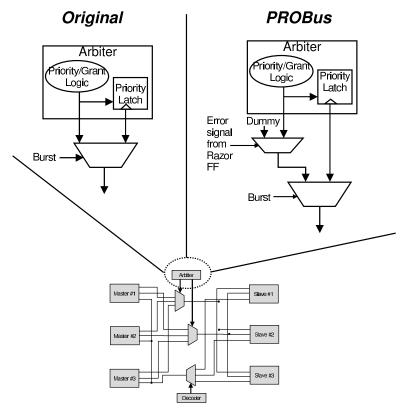

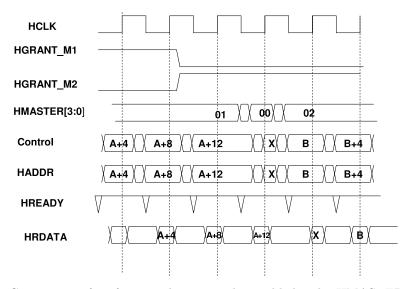

| 4.5.2 PROBUS - Proactive BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 82                                                             |

| 4.5.3 Frequency Adjustment Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86                                                             |

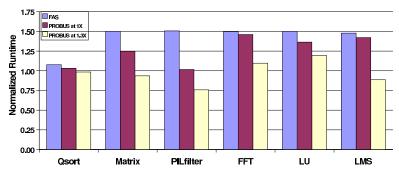

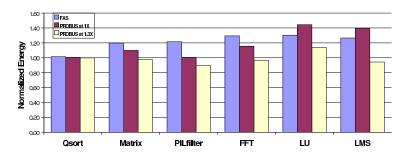

| 4.6 Experimental Setup and Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87                                                             |

| 4.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 88                                                             |

| Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                |

| Conclusion and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 90                                                             |

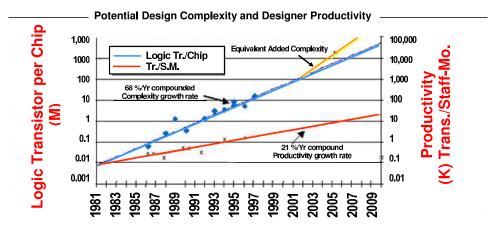

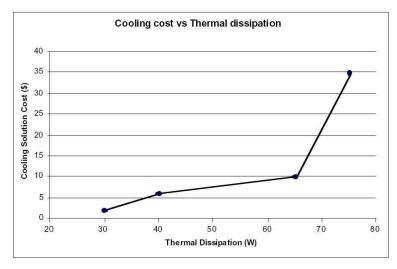

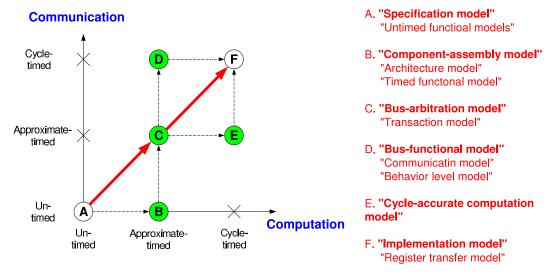

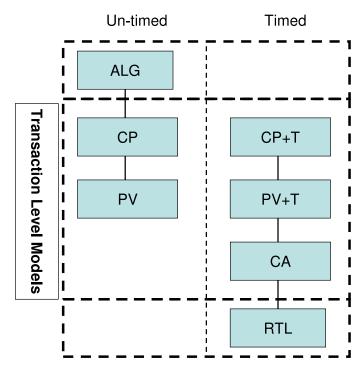

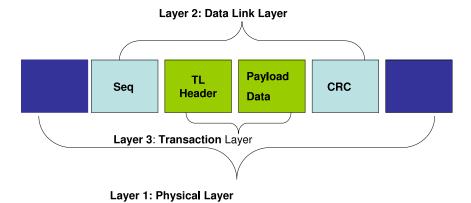

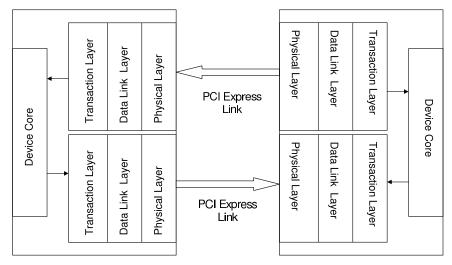

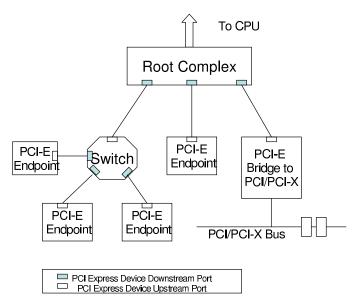

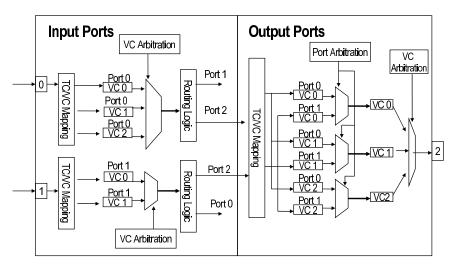

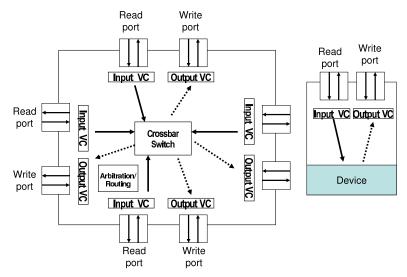

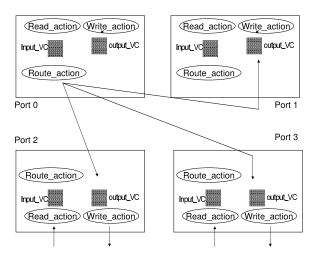

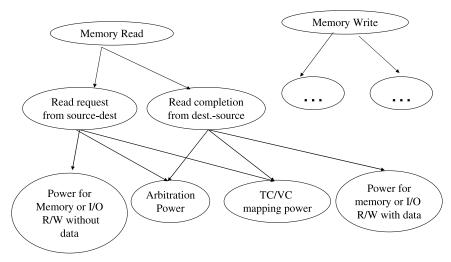

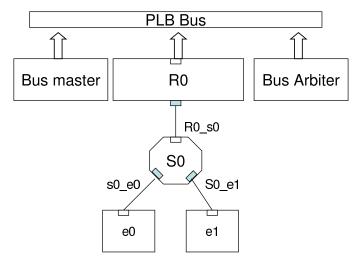

| 5.1 Transaction Level Power Modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 90                                                             |