# The Pennsylvania State University

## The Graduate School

Department of Computer Science and Engineering

# SOFTWARE AND HARDWARE OPTIMIZATIONS FOR NOC-BASED CHIP

## **MULTIPROCESSORS**

A Thesis in

Computer Science and Engineering

by

Feihui Li

© 2007 Feihui Li

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

August 2007

This thesis of Feihui Li was reviewed and approved\* by the following:

Mahmut Kandemir Associate Professor of Computer Science and Engineering Thesis Adviser Chair of Committee

Mary Jane Irwin Evan Pugh Professor of Computer Science and Engineering and A. Robert Noll Chair in Engineering

Yuan Xie Assistant Professor of Computer Science and Engineering

Kenan Unlu Professor of Mechanical and Nuclear Engineering

Raj Acharya Professor of Computer Science and Engineering Head of the Department of Computer Science and Engineering

<sup>\*</sup>Signatures are on file in the Graduate School.

## **Abstract**

When semiconductor technology scales into the deep sub-micro regime, billions of transistors can pack into a single chip. It turns out that traditional monolithic processor architectures scale poorly with technology due to diminishing improvements in clock rates and the increasing interconnect delay. Such architectures cannot efficiently transform the fertile on-chip resources into computing capability. Chip Multiprocessors (CMPs), integrating multiple relatively simple processing cores on a single chip, are becoming the trend for microprocessor design, as witnessed by both industry and academia.

Processors, interconnection networks, and memories constitute the three major components of a CMP architecture. This thesis optimizes two of these components, namely, interconnection network and memory subsystem. When the number of processing nodes of CMPs scales up, a new type of interconnection network, Network-on-Chip (NoC), is normally employed. Thus, we study the emerging interconnection network for CMPs: NoC, and a critical component of the memory subsystem for CMPs: the on-chip, level-2 (L2) Non-Uniform Cache Architecture (NUCA). Targeting these components, this thesis proposes a set of hardware and software optimization schemes.

The first part of this thesis uses compiler-directed approaches to reduce the energy consumption of NoCs. Three compiler approaches are proposed, including proactive communication link turn-on/off, compiler-directed voltage selection for communication links, and profile-driven message rerouting. The experimental results with array/loop-intensive applications demonstrate that the compiler-directed approaches are more efficient in reducing the NoC energy consumption than pure hardware-based power management schemes.

The second part of this thesis targets the design of high-performance L2 NUCA design and optimization for CMPs. The contribution of this part includes both a novel 3D NoC-bus hybrid NUCA design and a migration-based NUCA design. We demonstrate, through extensive experiments, that the 3D circuit technology is quite efficient in shortening the wire delay and thus reduces the L2 NUCA access latency. The other NUCA proposal is a careful migration scheme (eviction-triggered migration and access-triggered migration), aiming at finding a proper physical location for each cache line in L2. The experimental results show that this scheme generates significant improvements in L2 cache performance.

Overall, this thesis demonstrates that it is possible to reduce power consumption and improve performance of NoC-based CMPs through hardware and software directed optimization schemes.

# **Table of Contents**

| List of Tabl | es                                                       | viii |

|--------------|----------------------------------------------------------|------|

| List of Figu | res                                                      | ix   |

| Acknowled    | gments                                                   | XV   |

| Chapter 1.   | Introduction                                             | 1    |

| 1.1          | Chip Multiprocessors                                     | 1    |

| 1.2          | Network-on-Chip: Interconnection of Future CMPs          | 3    |

| 1.3          | Non-Uniform Cache Architecture: Memory Subsystem of CMPs | 4    |

| 1.4          | Thesis Scope                                             | 5    |

| Chapter 2.   | Compiler-Directed Power Management for Network-on-Chip   | 8    |

| 2.1          | Background                                               | 8    |

| 2.2          | Architecture Abstraction                                 | 10   |

| 2.3          | Power Model                                              | 14   |

| 2.4          | Compiler-Directed Proactive Link Turnoff and Activation  | 15   |

|              | 2.4.1 Hardware Support for Link Turnoff and Activation   | 16   |

|              | 2.4.2 Link Turnoff                                       | 18   |

|              | 2.4.3 Link Pre-activation                                | 22   |

|              | 2.4.4 Experiments                                        | 24   |

| 2.5          | Compiler Directed Voltage Scaling on Communication Links | 20   |

|            |         |                                                        | vi  |

|------------|---------|--------------------------------------------------------|-----|

|            | 2.5.1   | Motivation                                             | 30  |

|            | 2.5.2   | Inter-Process Communication Graph                      | 33  |

|            | 2.5.3   | Critical Path Analysis                                 | 40  |

|            | 2.5.4   | Code Modification                                      | 50  |

|            | 2.5.5   | Experiments                                            | 55  |

| 2.6        | Profile | -driven Message Rerouting                              | 60  |

|            | 2.6.1   | Motivation                                             | 60  |

|            | 2.6.2   | Hardware Support for Compiler-Directed Message Routing | 61  |

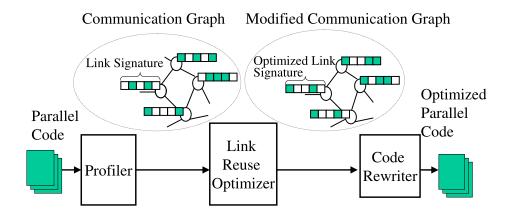

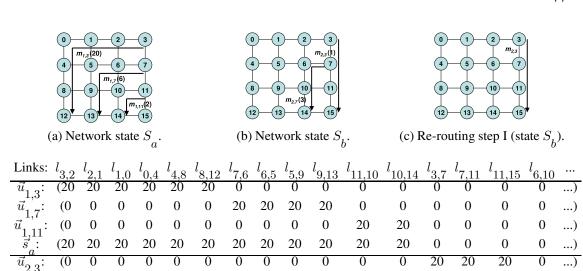

|            | 2.6.3   | Link Signature and Communication Graph                 | 63  |

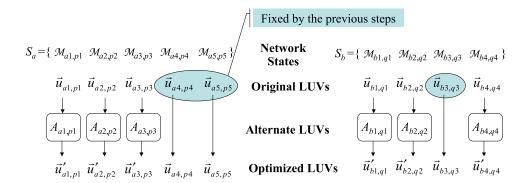

|            | 2.6.4   | Optimizing Link Reuse                                  | 68  |

|            | 2.6.5   | Code Rewriter                                          | 78  |

|            | 2.6.6   | Experiments                                            | 78  |

| 2.7        | Summa   | ary                                                    | 86  |

| Chapter 3. | Non-U   | niform Cache Architecture for Chip Multiprocessors     | 88  |

| 3.1        | Backgı  | round                                                  | 88  |

| 3.2        | Emplo   | ying 3D Integration for CMP NUCAs                      | 92  |

|            | 3.2.1   | Motivation                                             | 92  |

|            | 3.2.2   | 3D NoC-Bus Hybrid Architecture                         | 93  |

|            |         | 3.2.2.1 Using dTDMA Bus as Communication Pillars       | 96  |

|            |         | 3.2.2.2 NoC Router Architecture                        | 100 |

|            |         | 3.2.2.3 CPU Placement                                  | 101 |

|            | 3.2.3   | Cache Management Policies                              | 103 |

|            |        |            |                                      | vii  |

|------------|--------|------------|--------------------------------------|------|

|            |        | 3.2.3.1    | Processor and L2 Cache Organization  | 103  |

|            |        | 3.2.3.2    | Cache Management Policies            | 103  |

|            | 3.2.4  | Experim    | ents                                 | 106  |

| 3.3        | Migrat | ion-based  | NUCA design                          | 111  |

|            | 3.3.1  | Motivation | on                                   | 111  |

|            |        | 3.3.1.1    | Shared L2 Access Pattern             | 111  |

|            |        | 3.3.1.2    | Motivation for Migration-based NUCAs | 115  |

|            | 3.3.2  | Migratio   | n-Based NUCA Baseline Design         | 119  |

|            | 3.3.3  | Migratio   | n Algorithm for Shared Cache Lines   | 124  |

|            |        | 3.3.3.1    | Problem Formulation                  | 124  |

|            |        | 3.3.3.2    | Hardware Implementation              | 127  |

|            | 3.3.4  | Experime   | ents                                 | 131  |

| 3.4        | Summ   | ary        |                                      | 140  |

| Chanton 1  | Comple | . din D    | cules and Enture Worls               | 1.41 |

| Chapter 4. | Conclu | iding Kem  | arks and Future Work                 | 141  |

| 4.1        | Future | Work       |                                      | 144  |

References

146

# **List of Tables**

| 2.1 | Controlling link state by using flags HOLD and LAST of a message and flag       |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | SHARED of the link. X: don't care; Reset: reset the time-out counter to the     |     |

|     | maximum value; -: the state (value) is not changed. Whenever there is a         |     |

|     | message coming and its targeting link is power-off, this link will reactivate   | 18  |

| 2.2 | Benchmark codes                                                                 | 26  |

| 2.3 | Default system configuration parameters                                         | 27  |

| 2.4 | (a) Default values of our major simulation parameters. (b) Available link volt- |     |

|     | age/frequency levels                                                            | 56  |

| 2.5 | Benchmarks and their important characteristics                                  | 57  |

| 2.6 | Routing decisions based on orientation and routing command bits (N: North; S:   |     |

|     | South; W: West; E: East)                                                        | 63  |

| 2.7 | Benchmarks from experiments and their important characteristics. Energy val-    |     |

|     | ues are in mJ, and the latency values are in million cycles                     | 82  |

| 3.1 | Area and power overhead of dTDMA bus                                            | 97  |

| 3.2 | Area overhead of inter-wafer wiring for different via pitch sizes               | 98  |

| 3.3 | Default system configuration parameters (L2 cache is organized as 16 clusters   |     |

|     | of size 16x64KB)                                                                | 108 |

| 3.4 | Our benchmarks                                                                  | 108 |

| 3.5 | Default system configuration parameters                                         | 132 |

| 3.6 | Our benchmarks                                                                  | 132 |

# **List of Figures**

| 2.1  | A message-passing based parallel computing system consisting of computation                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------|----|

|      | nodes and a set of switches                                                                                        | 11 |

| 2.2  | Internal structures of a computation node and a switch                                                             | 12 |

| 2.3  | A mesh-based network architecture                                                                                  | 12 |

| 2.4  | High level view of proactive link energy optimization                                                              | 15 |

| 2.5  | The architecture supporting link shutdown and activation. Output buffer, Tx,                                       |    |

|      | Rx, and input buffer can turn off to conserve energy. HOLD and LAST are                                            |    |

|      | flags in the message header                                                                                        | 17 |

| 2.6  | Both $ec{eta}_1$ and $ec{eta}_2$ are constant vectors. The overall execution time for loop itera-                  |    |

|      | tions within $[\vec{I}-\vec{\beta}_1,\vec{I}+\vec{\beta}_2]$ is equal to the time-out period of links; the overall |    |

|      | execution time the loop iterations within $[\vec{I}, \vec{I} + \vec{\beta}_2]$ is equal to the delay due to        |    |

|      | activating a power-off link                                                                                        | 23 |

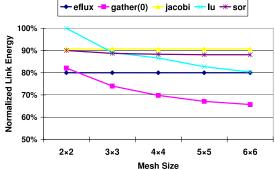

| 2.7  | Normalized link energy consumption. HW: hardware-based approach; SW: our                                           |    |

|      | compiler-based approach                                                                                            | 27 |

| 2.8  | Performance penalty of the hardware-based approach (over the case when no                                          |    |

|      | power optimization is performed)                                                                                   | 27 |

| 2.9  | The impact of mesh size (benchmark: jacobi)                                                                        | 29 |

| 2.10 | The impact of data size                                                                                            | 29 |

| 2.11 | Two example scenarios                                                                                              | 31 |

| 2.12 | High level view of compiler-directed channel voltage scaling                                                       | 31 |

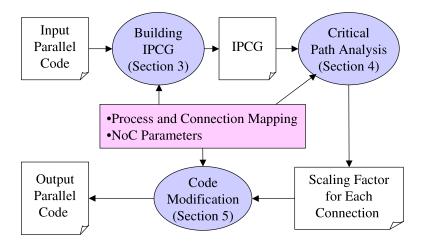

| 2.13 | Symbols used for different IPCG vertices. (a) Start point of loop $x_i$ . (b) Back-                     |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | jump instruction $b_i$ . (c) Send instruction $s_i$ . (d) Delivery point $d_i$ . (e) Receive            |    |

|      | instruction $r_i$                                                                                       | 39 |

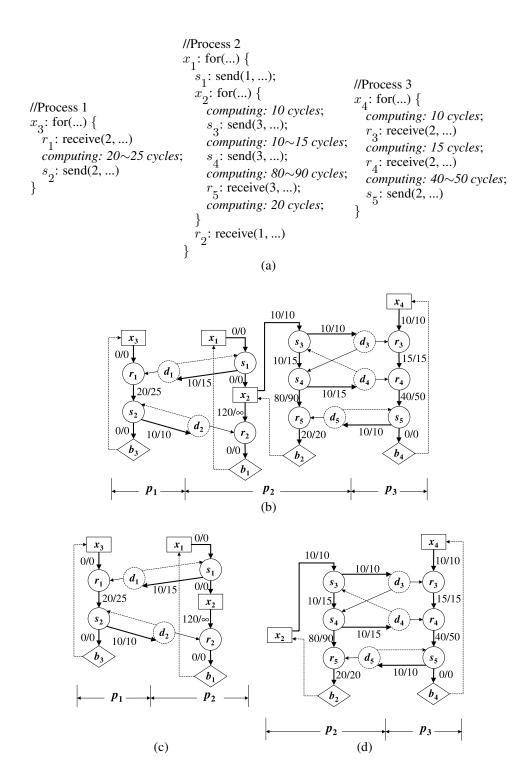

| 2.14 | (a) Code for a message-passing parallel program; " $x \sim y$ " indicates that a                        |    |

|      | computation task can take minimum $\boldsymbol{x}$ and maximum $\boldsymbol{y}$ cycles to complete. (b) |    |

|      | The IPCG for the code shown in (a). (c) The LCG for parallel group $\{x_1, x_3\}$ .                     |    |

|      | (d) The LCG for parallel group $\{x_2,x_4\}.$ $\ \ldots$                                                | 41 |

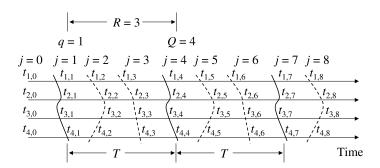

| 2.15 | Timing for an example parallel execution. In this particular example, there exist                       |    |

|      | constants $q=1$ and $R=3$ such that $t_{i,j}=t_{i,j+R}+T$ for all $j\geq q$ , where $T$                 |    |

|      | is a constant                                                                                           | 43 |

| 2.16 | Algorithm for critical path analysis: Phase 1                                                           | 47 |

| 2.17 | Algorithm for critical path analysis: Phase 2                                                           | 48 |

| 2.18 | Algorithm for critical path analysis: Phase 3                                                           | 48 |

| 2.19 | An example parallel code (a) and its IPCG (b)                                                           | 51 |

| 2.20 | Computing $t_{\alpha}$ and $t_{\beta}$ for the IPCG shown in Figure 2.19. (a) At the beginning          |    |

|      | of phase 1, all $t_{\alpha}[i,0]{\rm s}$ are initialized to 0. (b) The situation at the beginning of    |    |

|      | the second iteration of phase 1. (c) The $t_{\alpha}$ value for each vertex the beginning               |    |

|      | of the third iteration of phase 1. (d) The $t_{\alpha}$ value at the end of phase 1. (e) The            |    |

|      | $t_{eta}$ value for each vertex computed in phase 2                                                     | 52 |

| 2.21 | Determining scaling factors $k[1,2], k[2,3], {\rm and} k[3,1]$ assuming $\delta=10\%.$ At               |    |

|      | each step of Phase 3, we try to reduce the scaling factor of one connection. The                        |    |

|      | tables in (a) through (f) show the values of $k$ and $t$ at each step. $\dots$                          | 53 |

| 2.22 | An example parallel code with voltage/frequency control instructions inserted.                          | 54 |

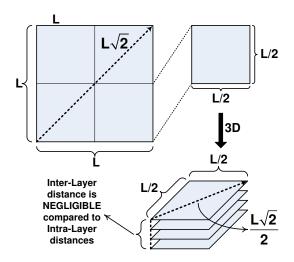

| 3.1  | Wiring scales in length as the square root of the number of layers in three di-     |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | mensions                                                                            | 93  |

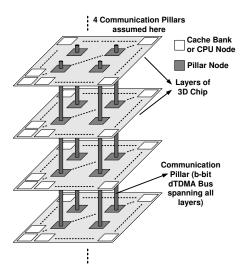

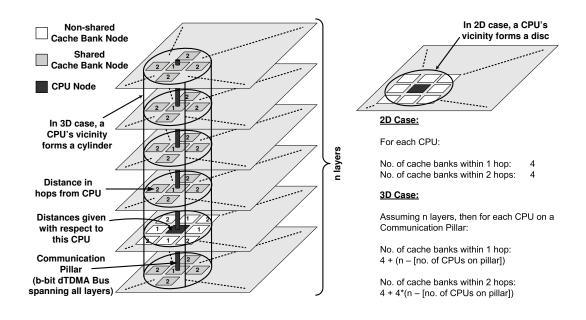

| 3.2  | Proposed 3D Network-in-Memory architecture                                          | 95  |

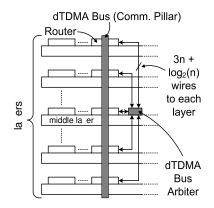

| 3.3  | Side view of the 3D chip with the dTDMA bus (pillar)                                | 96  |

| 3.4  | A high-level overview of the modified router of the pillar nodes                    | 99  |

| 3.5  | A CPU has more cache banks in its vicinity in the 3D architecture                   | 99  |

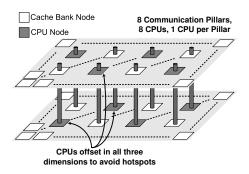

| 3.6  | Hotspots can be avoided by offsetting CPUs in all three dimensions                  | 102 |

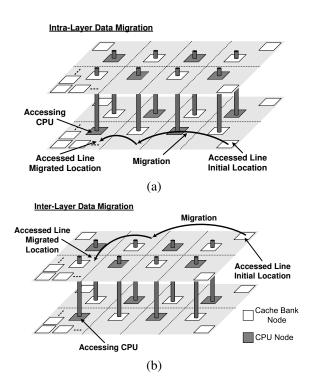

| 3.7  | Intra-layer and inter-layer data migration in the 3D L2 architecture. Dotted        |     |

|      | lines denote clusters                                                               | 104 |

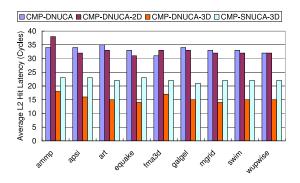

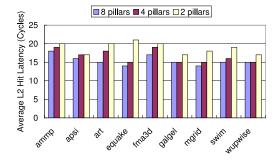

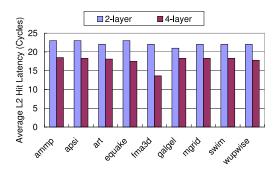

| 3.8  | Average L2 hit latency values under different schemes                               | 109 |

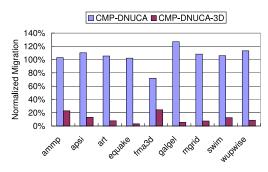

| 3.9  | Number of block migrations for CMP-DNUCA and CMP-DNUCA-3D, nor-                     |     |

|      | malized with respect to CMP-DNUCA-2D                                                | 109 |

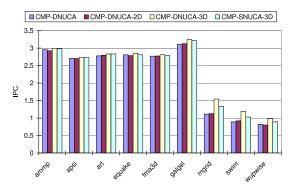

| 3.10 | IPC values under different schemes                                                  | 109 |

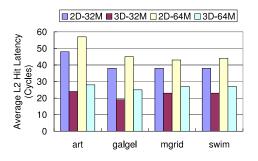

| 3.11 | Average L2 hit latency values under different schemes                               | 109 |

| 3.12 | Impact of the number of pillars (the CMP-DNUCA-3D scheme)                           | 109 |

| 3.13 | Impact of the number of layers (the CMP-SNUCA-3D scheme)                            | 109 |

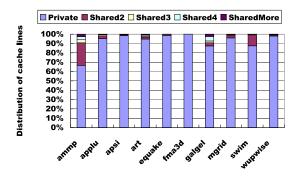

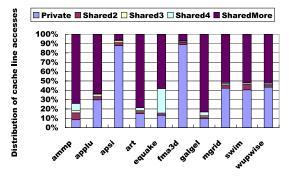

| 3.14 | Distribution of different types of L2 cache lines (Private: private L2 cache lines; |     |

|      | Shared $N$ : L2 cache lines shared by $N$ processors)                               | 113 |

| 3.15 | Distribution of different types of L2 cache accesses (Private: accesses to private  |     |

|      | L2 cache lines; Shared $N$ : accesses to L2 cache lines, which are shared by $N$    |     |

|      | processors)                                                                         | 113 |

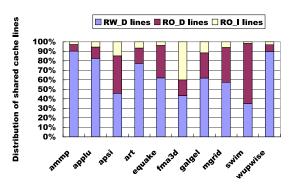

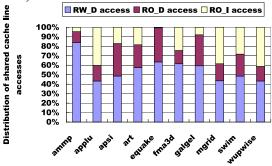

| 3.16 | Distribution of shared L2 cache lines (RW_D: read-write data; RO_D: read-only       |     |

|      | data; RO_I: instructions)                                                           | 113 |

| 3.17 | Distribution of accesses to shared L2 cache lines (RW_D: accesses to read-write         |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | data; RO_D: accesses to read-only data; RO_I: accesses to instructions)                 | 113 |

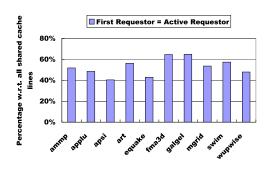

| 3.18 | Percentage of shared cache lines for which the first requestor is also the most         |     |

|      | active requestor                                                                        | 115 |

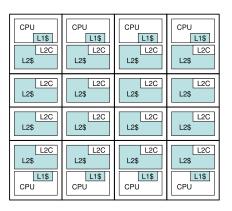

| 3.19 | A NUCA-based mesh CMP (L2C: L2 controller)                                              | 115 |

| 3.20 | NUCA for a uniprocessor architecture                                                    | 116 |

| 3.21 | A distributed algorithm for updating the cluster priority ( $n$ is the total number     |     |

|      | of clusters)                                                                            | 122 |

| 3.22 | Migration policy implementation for a victim cache line (function $\mathrm{d}(C_i-C_j)$ |     |

|      | gives the Manhattan Distance between $C_i$ and $C_j$ )                                  | 122 |

| 3.23 | An example of setting the cluster priority levels and determining the eviction-         |     |

|      | based cache line migration according to the algorithm in Figure 3.22                    | 123 |

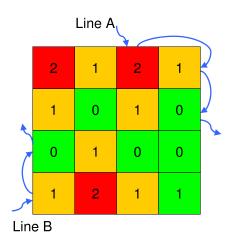

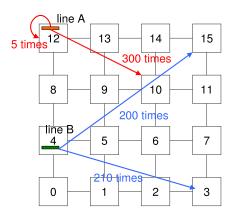

| 3.24 | Motivating examples for determining suitable locations for the hot shared cache         |     |

|      | lines                                                                                   | 123 |

| 3.25 | The algorithm for computing the X coordinate of the target cluster for a shared         |     |

|      | cache line. The Y coordinate can be computed similarly.                                 | 128 |

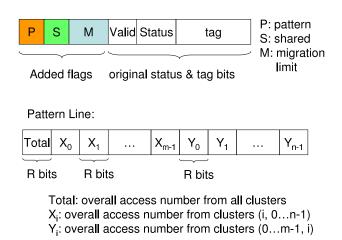

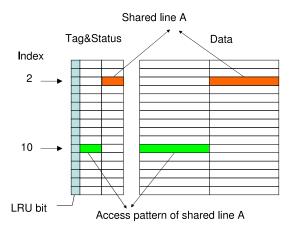

| 3.26 | Hardware support for tracking the access patterns of shared cache lines                 | 129 |

| 3.27 | Allocating a pattern line for a shared cache line                                       | 129 |

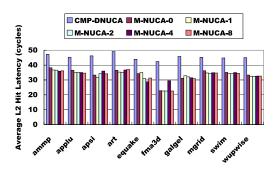

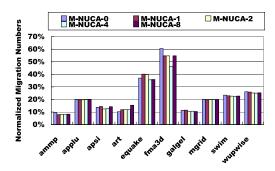

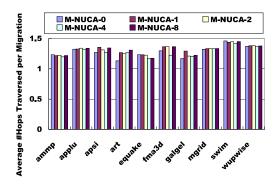

| 3.28 | Average L2 hit latency                                                                  | 136 |

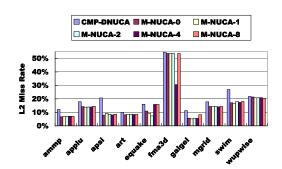

| 3.29 | L2 cache miss rate under the different schemes                                          | 136 |

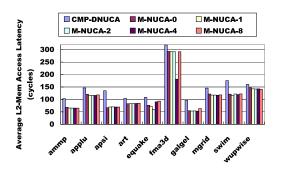

| 3.30 | Average L2 access latency (including both hits and misses)                              | 136 |

| 3.31 | Number of migrations performed (normalized with respect to the number of                |     |

|      | migrations under the CMP-DNUCA scheme)                                                  | 136 |

|      |                                                                                   | XIV |

|------|-----------------------------------------------------------------------------------|-----|

| 3.32 | Average number of hops a migration traverses                                      | 137 |

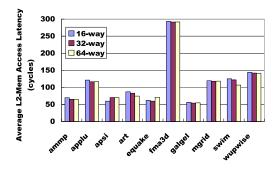

| 3.33 | Average L2 access latency under different cache associativities (migration limit  |     |

|      | is 2)                                                                             | 137 |

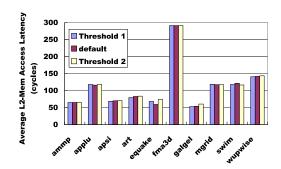

| 3.34 | Average L2 access latency under different priority setting thresholds (migration  |     |

|      | limit: 2; default: 350 L2 misses per million cycles; Threshold 1: 35 L2 misses    |     |

|      | per million cycles; Threshold 2: 3500 L2 misses per million cycles)               | 139 |

| 3.35 | The average L2 access latency with different thresholds for triggering the mi-    |     |

|      | gration of shared cache line migration (migration limit: 2; default: 40 accesses; |     |

|      | Threshold 1: 400 accesses; Threshold 2: 4000 accesses)                            | 139 |

# Acknowledgments

My sincerest gratitude is to my thesis advisor, Prof. Mahmut Taylan Kandemir. He gave me the opportunity to explore the exciting research areas of computer architecture and optimizing compilers and guided my research with great enthusiasm. His constant encouragement, support and guidance were key for me to complete this thesis.

I am indebted to Prof. Mary Jane Irwin for her precious time devoted reading my research papers, my proposal, and this dissertation. I have benefited a lot from her broad vision and helpful advices. I am grateful to Dr. Vijaykrishnan Narayanan and Dr. Yuan Xie for their insightful suggestions, enlightening discussions, and their friendship. I would also like to thank my other committee member, Dr. Kenan Unlu, for his valuable comments on my Ph.D. work and for serving in my thesis committee.

Many thanks are to past and present MDL members for providing a supportive and productive environment during my stay at Penn State. Especially, I thank Guangyu Chen, Chrys Nicopoulos, Jie Hu, Guilin Chen, Madhu Mutyam, and Yuh-Fang Tsai for the happy time we worked together.

Finally, I owe my deepest gratitude to my family members. I thank my parents, my parents-law, my brother and my sister-in-law for their love, support and understanding. Also, this thesis would not happen without love, understanding and encouragement from my dear husband, Haisang Wu.

# Chapter 1

# Introduction

#### 1.1 Chip Multiprocessors

The rapid scaling of semiconductor technology into the deep sub-micron regime has been accompanied by a dramatic increase in transistor density. Packing billions of transistors on a single chip is now a reality. The challenge for designing billion-transistor processors is how to efficiently utilize the fertile on-chip resources. Conventional monolithic superscalar architectures, which feature sophisticated microarchitectural functions such as dynamic scheduling, speculative execution, and dynamic branch prediction, scale poorly with technology [3] due to the diminishing improvements in clock rates and the continuing increase in interconnect delays. As a result, superscalar architectures cannot provide sustained performance growth that has been achieved during the past decades. Chip Multiprocessors (CMPs) [69, 33] emerge as a promising alternative for fully utilizing the increasing integration density of microprocessor chips. Compared to traditional monolithic architectures, CMPs integrate multiple relatively simple processing cores on a single die.

As stated by Hammond et al [33], CMPs are favorable (over conventional monolithic architectures) due to the advantages in speed, design complexity, execution parallelism, and other issues. First, CMPs dramatically reduce, and sometimes even completely avoid, the complexity of some microarchitectural components, such as the branch predictors and the issue queues. Consequently, processing cores of CMPs are relatively small and simple, and thus can operate

with quite high clock rates. Simple and fast processing cores also indicate accelerated design and validation cycles. Second, CMPs can employ thread-level and/or process-level parallelism. Having multiple threads of control in parallel is effective in hiding cache-miss penalties, since the execution of some threads can overlap with the stalls of others. superscalar architectures have only a single thread of control. They extract parallel instructions at the cost of complicated hardware, while the instruction level parallelism (ILP) is quite limited due to true dependencies and control dependencies. Simultaneous Multi-Threading (SMT) processors [99] support multiple concurrent threads on a single core. However, SMTs are still monolithic and suffer the same scaling problem as superscalar processors. For example, one important issue for SMTs is the contention among different threads to the single shared primary cache. CMPs normally assign independent primary caches to different processing cores and eliminate the contention. Besides these issues, CMPs are also preferable from the wire delay viewpoint. The wire delay is becoming dominant, since it scales much more slowly than the logic gate delay when technology scales. This fact affects the design of tradition superscalar processors. However, CMPs accommodate to such a trend very well because of their naturally partitioned structures. That is, frequently communicating components are clustered closely, while less relevant components are apart from each other. Finally, CMPs are arguably simpler than complex monolithic systems in terms of validation and verification.

Currently almost all major CPU manufacturers are producing commercial CMP chips. Sun's UltraSPARC T1 (formerly code named Niagara) [54] is an 8-core CMP, supporting up to four threads per core. This architecture targets workloads with high thread-level parallelism such as web server applications. Intel's Core Duo processor [42], a dual-core architecture, has versions for desktop, laptop and mobile applications. Orienting game/multimedia applications,

Sony, Toshiba and IBM (STI) [46] designed Cell processor. It incorporates a dual-threaded two-way-issue Power architecture and eight synergistic processing elements. Broadcom's BCM1480 [13], consisting of four Broadcom SB-1 MIPS64 CPUs, targets the next-generation computing, storage and networking applications. These CMP chips are clearly signaling the growing popularity of CMP architectures.

## 1.2 Network-on-Chip: Interconnection of Future CMPs

Most current CMPs employ conventional interconnects such as buses and crossbars for connecting processing cores. Buses, however, suffer from the resource contention issue. When the number of nodes on a bus increases, performance may degrade due to excessive conflicts. Therefore, buses are not considered appropriate for systems of more than 10 nodes [9]. Crossbars, although performing well with a reasonably large number of cores, become not favorable when the size of CMPs increases, due to their high costs.

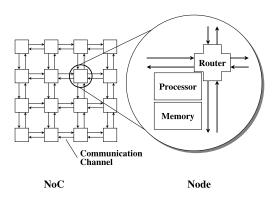

A segmented network fabric, namely, the Network-on-Chip (NoC) [26, 10], is emerging as a solution to chip-level communications. The structure of an NoC resembles that of a traditional macro network. That is, an NoC is composed of on-chip routers and communication links. Each processing core is attached a router, which interfaces it to the entire network through neighboring routers. The data to be exchanged among on-chip processing cores (homogeneous or heterogeneous) are transmitted along routers and communication links. As in a traditional macro network, the transmitted data is assembled into packets. Each packet includes both the header field (containing destination information and etc.) and the actual data.

The adoption of NoC architecture is driven by its predictability, scalability, and parallelism. From the physical design point of view, NoCs can be built at the early design stage, and their speed and power can be estimated as well, because of the regular, well controlled structure. NoC-based systems can also properly accommodate multiple asynchronous clocking through network protocols. From the perspective of microarchitecture, NoC-based systems are easy to expand by adding more routers, links and processing cores. The contention problem of centralized interconnects such as buses is alleviated in an NoC, as all the links in an NoC can operate simultaneously for transmitting different messages. Further, according to the computer community, "From a system design viewpoint, with the advent of multi-core processor systems, a network is a natural architectural choice. An NoC can provide separation between computation and communication, support modularity and IP reuse via standard interfaces, handle synchronization issues, serve as a platform for system test, and, hence, increase engineering productivity." [67] TeraFlop [40], a research CMP chip proposed by Intel, consists of 80 cores and connects these cores through a mesh-based NoC. Several CMP chips from academia, for example, RAW [94] and TRIPS [81] processors, also employ NoCs as their main communication fabric. In this thesis, our focus is on next-generation NoC-based CMP architectures.

#### 1.3 Non-Uniform Cache Architecture: Memory Subsystem of CMPs

Besides the interconnection, memory subsystem is another critical factor for the success of CMP systems. With multiple cores residing on a single die, CMPs require higher memory bandwidth than traditional processors. Consequently, they usually need to incorporate large on-chip (level-2) L2 and/or (level-3) L3 caches. For example, Sun's Ultrasparc T1 contains 3MB of on-chip L2 cache, and Intel's Dual Core Itanium 2 includes 2.5MB of on-die L2 cache and 24MB of on-die L3 cache. When the number of processing cores on a CMP increases, the demand for memory bandwidth also increases, leading to even larger on-chip L2/L3 caches [38].

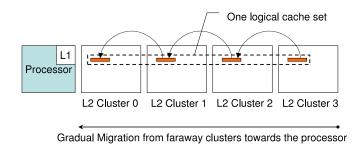

Traditional memory hierarchy design assumes each cache level has a constant access latency. However, the large size of on-chip L2 caches and the increasing wire delay make the L2 cache access latency not a constant any more. Instead, the latency is dependent on the distance between the accessing processor and the requested cache line. To employ this variance in L2 cache access latencies for improving L2 performance, Kim et al designed Non-Uniform Cache Architecture (NUCA) [48]. NUCA partitions the L2 cache into multiple individually addressable banks and connects these banks using Network-on-Chip. Cache banks exhibit different access latencies, which are determined by the relative locations to the processor. Data migration is employed in NUCA to move frequently accessed cache lines closer to the processor.

Prior NUCA designs for CMPs include a purely shared L2 cache [8], a purely private L2 cache [52] and a set of alternatives between purely shared and purely private caches [39, 22, 106, 7, 17]. Basically, all of these studies focus on minimizing the average L2 hit latency and/or maximizing the effective on-chip L2 capacity (i.e., minimizing the off-chip accesses), with an attempt to achieve an overall L2 performance enhancement.

#### 1.4 Thesis Scope

This thesis focuses on optimizations targeting NoC-based CMPs. Specifically, we target two critical components of CMPs: interconnection (Network-on-Chip) and memory subsystem (shared NUCA-based L2).

Regarding Network-on-Chip, we focus on reducing the power consumption without affecting performance excessively. Prior studies [10, 100] indicate that, although an NoC architecture provides high communication bandwidth, it consumes a significant portion of the overall chip power due to the amount of NoC components (routers and links) and the communication

data volume. For example, in the case of the MIT RAW processor, the NoC connecting 16 onchip tiles consumes 36% of the entire chip power, with each router consuming 40% of the per tile power [100, 94]. This observation motivates for research targeting the NoC power management.

Most prior NoC power management schemes are hardware based [90, 76]. That is, they adjust unused NoC components or NoC components under low utilization into low power modes based on the history utilization information. In contrast, in this thesis, we propose three compiler-directed approaches for reducing NoC power consumption. The first two approaches analyze the communication pattern of a parallel application and insert explicit network power control commands at proper points in the parallel code. The optimized parallel code will set NoC components to appropriate power modes at suitable time points during execution. The first approach we propose [57] assumes only two power modes (power-on and power off) and inserts proactive communication link showdown and activation commands. In comparison, our second approach [19] analyzes the critical paths within a parallel code in order to assign a suitable voltage level for each communication link. The third approach proposed [58] is profile-driven. Based on communication traces, the compiler reroutes messages by clustering messages into a small subset of communication links. The goal of this approach is to increase the idle periods of communication links and thus enhance the effectiveness of a pure hardware-based link shutdown scheme.

CMPs, with multiple cores on a single chip, impose a continuously increasing demand for memory bandwidth. Without sufficient memory bandwidth, different cores will compete with each other on using the limited set of pins and this might invalidate potential advantages of CMPs. In a CMP-based execution scenario, the latency of accessing off-chip memories is an order of magnitude higher than that of accessing on-chip memories. Therefore, the design of an

efficient on-chip cache system is crucial for achieving the potential performance of CMPs. The second part of this thesis focuses on the performance of the shared level-2 (L2) NUCA for CMPs. In this category, two micro-architectural schemes are proposed in this thesis. The first approach proposed employs the three-dimensional (3D) integration technology [27, 63] to design the high performance NUCA for CMPs, because the 3D technology decreases the lengths of cross-chip wires dramatically. The existing NUCA design [48, 8] is adapted to the 3D scenario. Our second approach focuses on a migration-based NUCA design for CMPs. This approach proposes two types of data migrations: eviction-triggered migration and access-triggered migration, aiming at finding a proper physical position for each cache line such that the average L2 access latency is minimized.

This thesis is organized as follows. Chapter 2 discusses three compiler-directed schemes for reducing NoC power consumption. We introduce the architecture abstraction and the NoC power model, explain the proposal details, and show the experimental results. In Chapter 3, a 3D NUCA architecture and a migration-based NUCA design for CMPs are presented. Further, we provide the details of these two schemes and the associated simulation results in this chapter. Finally, Chapter 4 concludes this thesis, and provides points for future research.

# Chapter 2

# **Compiler-Directed Power Management for Network-on-Chip**

#### 2.1 Background

As the power consumption of interconnection networks is becoming an important concern [94, 81], we have witnessed several efforts devoted to optimizing the NoC energy consumption. We classify these related works into three categories: hardware-based, compiler-based, and task mapping.

The hardware-based NoC energy optimizations usually depend on adjusting link and buffer power modes according to NoC utilization. Based on the technique of voltage/frequency scalable links proposed by Kim and Horowitz [50], Shang et al [82] evaluated a history-based dynamic voltage scaling (DVS) scheme for communication links. The hardware is enhanced to lower down the voltage of the communication links in low utilization. Kim et al [49] designed a link shutdown scheme that minimized the number of power-on links while maintaining the connectivity of the network. They proposed an adaptive routing algorithm, and compared their scheme against a link voltage scaling approach. Soteriou and Peh [90] explored the design space for communication link turn-on/off. In their scheme, the decisions of turning off communication links are also based on the past message traffic observed. Besides these works, several low power NoC circuit design techniques [76] are also proposed.

Within the area of low power design, many compiler optimizations that target the functional units, register files, or cache/memory hierarchies were proposed [16, 47, 73, 2, 62]. Considering the general domain of optimizing communication and locality of communicated data in distributed-memory message-passing architectures, representative locality-oriented studies include [53, 15, 6, 32]. The main idea behind these studies is to minimize the inter-processor data communication. Until now, much less attention is paid to compiler works for low power CMPs. Prior compiler works [55, 56, 66] on CMPs target mainly at extracting and employing parallelism. Two closely related works include [18] and [89], where [18] optimized the energy consumption of NoCs using compiler-directed communication link allocation, and [89] is a software-directed link DVS technique based on off-line profiling.

Besides hardware-based and compiler-based schemes, another approach to reducing the NoC energy consumption was based on task mapping. Shin and Kim [84] used genetic algorithms to determine task assignment, tile mapping, routing path allocation, task scheduling, and link speed assignment for applications running on NoC-based systems. Asica et al. [4] proposed another genetic algorithm that allowed users to specify a particular optimization goal, such as performance or energy consumption. Hu and Marculescu [37] proposed an algorithm that mapped a given set of IP blocks onto a generic regular NoC and constructed a deadlock-free routing function such that the total communication energy consumption was minimized.

In addition, regarding NoC energy optimization, Benini and De Micheli [10] also identified possible approaches for energy savings, including node-centric and network-centric techniques. Simunic and Boyd [86] later implemented several of these techniques using a closed-loop control model.

Our proposed approaches are different from all the prior efforts in that they are compiler-directed NoC power management. Specifically, they use compiler-based (automated) communication analysis to identify the active/idle or communication slack patterns for communication links, and insert explicit link power management calls, i.e., link turn on/off or setting link voltage levels in the application code. Or we use profiling information to restrict the routing paths so as to shutdown more communication links. To the best of our knowledge, these are the first study of using compiler support to manage interconnection network power. In comparison, the prior hardware-based network power optimizations, cannot be as effective as our approaches for loop-intensive applications running on small size networks.

#### 2.2 Architecture Abstraction

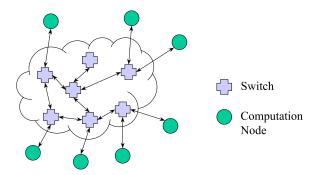

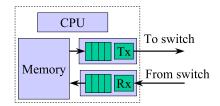

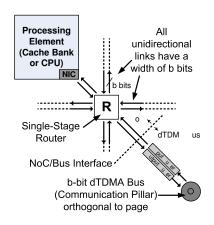

In the work aiming at managing the NoC power consumption, we assume that the application code is parallelized using message-passing directives. The resulting parallel program consists of a number of processes that are to be executed in parallel and communicate with each other through message passing. A message-passing based computing system (Figure 2.1) consists of a set of computing nodes ( $\mathcal{N}$ ) and a set of switches ( $\mathcal{S}$ ). Figure 2.2(a) shows the structure of a computing node ( $N_i \in \mathcal{N}$ ), which contains a processor, a memory module, an outgoing message port (out-port), and an incoming message port (in-port). The out-port and in-port of a computation node are connected to an in-port and out-port of a switch, respectively. Figure 2.2(b) shows the structure of a switch. Each switch ( $S_i \in \mathcal{S}$ ) has p in-ports and q out-ports. Each out-port of a switch is connected to an in-port of either another switch or a computing node; each in-port of a switch is connected to an out-port of either another switch or a computing node. A message sent by the application is first split into a set of fix-sized data packets. A

data packet flows into the switch through one of the p in-ports. The crossbar interconnect in the switch forwards this packet to an out-port of this switch based on the destination of this packet and the routing algorithm used by the network. From this out-port, the packet will be sent to an in-port of another switch, or the in-port of the destination computing node.

Fig. 2.1. A message-passing based parallel computing system consisting of computation nodes and a set of switches.

A packet received by an in-port is first stored in the buffer of this in-port. For a computation node, the in-port buffer can hold multiple packets. These packets in the buffer are first assembled into messages before being passed to the application. For a switch, however, an in-port buffer can hold only one packet at any given time. An in-port of a switch does not need a large buffer because the packet received by the in-port will be forwarded to an out-port immediately. The out-port that is trying to send a packet to an in-port is stalled if there is no free slot in the buffer of the targeted in-port. Each out-port has a FIFO (First-In-First-Out) buffer that can hold up to n packets.

(a) A computation node consisting of a CPU, a memory module, an in-port and an out-port.

(b) A switch with p (p=4) in-ports and q (q=4) out-ports. The buffer in each in-port can contain only one packet; the buffer in each out-port can contain up to n packets. The crossbar can forward packets from any in-port to any out-port.

Fig. 2.2. Internal structures of a computation node and a switch.

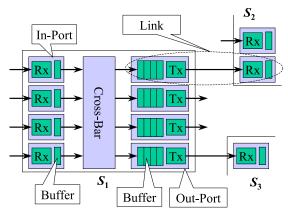

Fig. 2.3. A mesh-based network architecture.

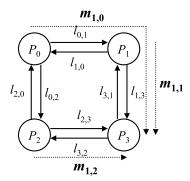

We focus on an  $M \times N$  (M rows, N columns) mesh architecture. Figure 2.3 shows an example mesh. The nodes in the  $M \times N$  mesh are numbered from 0 to MN-1. We use  $p_i$  to denote the  $i^{\text{th}}$  node in the mesh. A pair of nodes,  $p_i$  and  $p_j$ , are adjacent to each other if and only if the following condition holds:

$$|i \mod N - j \mod N| + ||i/N| - |j/N|| = 1.$$

Each pair of adjacent nodes,  $p_i$  and  $p_j$ , are connected by a pair of links,  $i \to j$  and  $j \to i$ . Link  $i \to j$   $(j \to i)$  transfers messages from  $p_i$   $(p_j)$  to  $p_j$   $(p_i)$ . We see from Figure 2.3 that each computation node is bond with a switch in this mesh architecture. Without misunderstanding, when we mention a node in this work, we mean a node consisting of a processor, a memory module, and a switch (router).

We assume the system runs a single embedded application at a given time. This application consists of a set of parallel processes (i.e., it is parallelized to be executed over the mesh nodes). Each node in the mesh executes at most one process. A process running on a node,  $p_i$ , can send messages to a process running on another node,  $p_j$ , through connection  $p_i \stackrel{*}{\to} p_j$ . If  $p_i$  and  $p_j$  are adjacent, connection  $p_i \stackrel{*}{\to} p_j$  contains only one link. On the other hand, if  $p_i$  and  $p_j$  are not adjacent,  $p_i \stackrel{*}{\to} p_j$  contains multiple links, that is, a "multi-hop" connection. The set of links involved in a connection is determined by the specific routing algorithm used. In this work, we assume a static (deterministic) X-Y routing algorithm [30]. In this algorithm, a message is first continuously passed in x-dimension and then in y-dimension until it reaches its destination.

Our approaches can be adapted to be used with other types of architectures.

## 2.3 Power Model

The increasing NoC energy consumption has motivated works on modeling NoC power consumption. Orion [101], an architectural-level power-performance simulator for interconnection networks, assesses different network architectures and the impact of different communication patterns on energy consumption. It enables the exploration for power-performance tradeoffs for interconnection network design. LUNA [31], a high-level power analysis framework for on-chip networks, gives the spatial and temporal power profile of the network by using link utilization as a high level power metric. Patel et al [70] have focused on the power constrained design of interconnection networks and proposed power models for routers and links in the network.

We use an interconnection network power model proposed in [31, 101], which can be represented as follows:

$$\begin{split} E_{network} &= & E_{link} + E_{switch} \\ &= & E_{link} + E_{crossbar} + E_{arbitration} + E_{buffer}, \end{split}$$

This means that the links and switches are the two main energy consuming components in an interconnection network. The energy consumed by the switches can be further classified into the energy consumption of crossbar, arbitration logic, and buffers. In this work for managing the network power, we focus only on the link energy consumption and model it in detail using the approach described in [90], which is to be elaborated in later analysis. The energy optimizations for the switches can be found in [49, 70, 100].

The energy consumed by the link circuitry turns out to be a significant portion of the total network energy consumption, which is pointed out by many previous studies [21, 82, 90]. In [21], the authors provide the on-chip link/router power numbers, showing that in many cases the link power consumption is larger than that of the router. The off-chip communication links consume an even higher portion of the total network power budget [90]. Therefore, one can expect significant power savings through optimizing the power consumption of the communication links.

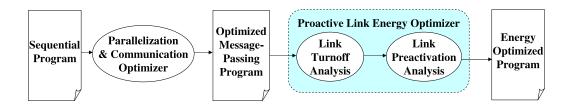

# 2.4 Compiler-Directed Proactive Link Turnoff and Activation

Figure 2.4 illustrates our first proposal for optimizing power consumption of NoCs. The proposed compiler algorithm (proactive link energy optimizer) analyzes the communication pattern of parallel applications, and decides which links to shut down/activate and when to shut down/activate. Based on the decisions, the algorithm modifies the original parallel codes by inserting link turnoff and pre-activation instructions at proper positions and generates an energy optimized parallel program. Please note that the focus of this work is on the proactive link energy optimizer in stead of application parallelization and communication optimization.

Fig. 2.4. High level view of proactive link energy optimization.

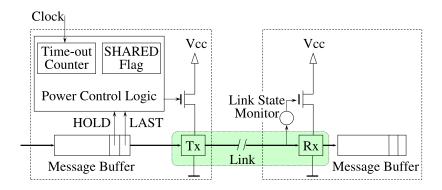

#### 2.4.1 Hardware Support for Link Turnoff and Activation

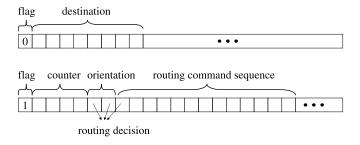

Figure 2.5 depicts the structure of a link and associated switch components that supports link shutdown and activation. A time-out counter in the sender node monitors the link utilization by decreasing its value at each clock tick when the link is not in use (once the link is used, the counter is reset to the maximum value). When the value reaches 0, link components (Tx and Rx) are turned off to conserve energy. Power control logic inside the sender node is responsible for link activation as well. When the link reactivates, a small link state monitor in the receiver node detects it and turns on Rx.

To support compiler-directed link turnoff and activation, we extend both the hardware design and the message format. A 1-bit "SHARED" flag is added into power control logic. We use this flag to indicate whether multiple connections share this link. When SHARED is set to 0 (not shared), the associated link can be turned off by a passing message. Each message extends by adding two one-bit link control flags: "HOLD" and "LAST". Setting flag LAST to 1 indicates that the sending node will not send messages for a relatively long period of time after sending this message. Therefore, the links involved for transferring this message can turn off to conserve energy if SHARED is 0. The link turnoff in this situation is regardless of the time-out counter value. However, if SHARED is 1, indicating other messages need this link, a message with flag LAST as 1 cannot turn off the link. Setting flag HOLD of a message to 1 indicates that the sender will use the connection again in the near future. Thus, sending a message with HOLD = 1 sets SHARED flags of all links passed by the message to 1, in order to prevent other nodes from turning off these links. A link with SHARED = 1 still turns off when the time-out counter reaches zero. When a link is reactivated from the power-down mode, its SHARED

flag is initialized to 0. Table 2.1 summarizes how the flags of a message affect the state of a communication link.

Fig. 2.5. The architecture supporting link shutdown and activation. Output buffer, Tx, Rx, and input buffer can turn off to conserve energy. HOLD and LAST are flags in the message header.

Using these control flags, we can control the states of links along the path from source node to destination node. This mechanism is especially important when the source and destination nodes of a given message are not adjacent to each other (when we have only the nearest-neighbor type of communication as in the case of stencil computations [80], the calculation of these flags can be significantly simplified). By making use of flag LAST, a program can turn off idle links earlier than a pure time-out based hardware mechanism would. Similarly, by utilizing flag HOLD in the message and SHARED associated with each link, the program can prevent a node from turning off links still needed by other nodes, and thus reduces potential performance/energy penalties.

Table 2.1. Controlling link state by using flags HOLD and LAST of a message and flag SHARED of the link. X: don't care; Reset: reset the time-out counter to the maximum value; —: the state (value) is not changed. Whenever there is a message coming and its targeting link is power-off, this link will reactivate.

| Messag | _    |        | Current State State After Message To |      |                     | Transmission |     |

|--------|------|--------|--------------------------------------|------|---------------------|--------------|-----|

| HOLD   | LAST | SHARED | Counter                              | Link | SHARED Counter Link |              |     |

| 0      | 0    | X      | X                                    | On   | -                   | Reset        | On  |

| 0      | 1    | 0      | X                                    | On   | -                   | X            | Off |

| 0      | 1    | 1      | X                                    | On   | -                   | -            | On  |

| 1      | 0    | X      | X                                    | On   | 1                   | Reset        | On  |

## 2.4.2 Link Turnoff

Targeting loop-intensive, message-passing based parallelized embedded programs, the task of our compiler algorithm is to set flags HOLD and LAST properly for each message-sending operation inside the program. The input program is already parallelized and optimized using techniques such as [34, 98, 103]. For ease of discussion, we assume that the program contains only one loop nest  $\mathcal{L}$ . For a message-sending command "send $_k(p, m)$ " (the  $k^{\text{th}}$  message-sending command m to processor p), if flag LAST message m is set to 1, links used to transfer message m turn off once m has been delivered. Besides, setting flag HOLD of message m to 1 prevents links passed by message m from being turned off by other nodes. Flags HOLD and LAST do not affect the correctness of the program, however, by setting their values properly, one can intelligently shut down the communication links without waiting until the time-out counter reaches 0.

The below example illustrates the code transformation performed by our compiler:

```

\label{eq:for_def} \text{for } \vec{I} = \vec{L} \text{ to } \vec{U} \; \{ \\ & \dots \\ \\ \text{if } (\vec{I} \in H_{k,i}) \; m.HOLD = 1; \\ \\ \text{...} \qquad \qquad \text{else } m.HOLD = 0; \\ \\ \text{send}_k(p(\vec{I}), m); \implies \qquad \text{if } (\vec{I} \in G_{k,i}) \; m.LAST = 1; \\ \\ \text{...} \qquad \qquad \text{else } m.LAST = 0; \\ \\ \text{send}_k(p(\vec{I}), m); \\ \\ \dots \\ \}

```

In this abstract code fragment, i is the ID of the node executing this code fragment,  $\vec{L}$  and  $\vec{U}$  are the lower and upper bound vectors for the loop nest, and  $\vec{I}$  is the iteration vector. At iteration  $\vec{I}$ , "send( $p(\vec{I})$ , m)" sends message m to the target node  $p(\vec{I})$ .  $H_{k,i}$  is the set of loop iterations where "send $_k(p(\vec{I}), m)$ " sends messages with HOLD= 1. Similarly,  $G_{k,i}$  is the set of loop iterations where "send $_k(p(\vec{I}), m)$ " sends messages with LAST= 1. The compiler computes iteration sets  $H_{k,i}$  and  $G_{k,i}$  for each message instruction executed on each node. In this work, we assume that both  $H_{k,i}$  and  $G_{k,i}$  can be expressed in Presburger formulas.

In stead of finding optimal  $H_{k,i}$  and  $G_{k,i}$ , which is very hard if not impossible, we consider a heuristic. Before presenting the details, we define several auxiliary functions:

• connection(i, j): the set of links used in the connection from node  $p_i$  to  $p_j$ . This function is determined by the used routing algorithm.

<sup>&</sup>lt;sup>2</sup>Vector  $\vec{I}$  keeps the loop indices from the outermost position to the innermost position.  $\vec{L}$  and  $\vec{U}$  are also defined as vectors and each contains an entry for each loop index, again from the outer most position to the inner most position.

- $targets(i, \vec{I})$ : the set of nodes to which node  $p_i$  sends messages at iteration  $\vec{I}$  of loop nest  $\mathcal{L}$ .

- $links(i, \vec{I})$ : the set of links used by node  $p_i$  at iteration  $\vec{I}$  of loop nest  $\mathcal{L}$ . This function can be computed as:

$$links(i, \vec{I}) = \bigcup_{j \in targets(i, \vec{I})} connection(i, j).$$

•  $use(i, \vec{I}, \vec{\delta})$ : the set of links used by node  $p_i$  during the period from iteration  $\vec{I}$  to  $\vec{I} + \vec{\delta}$  of loop nest  $\mathcal{L}$ .  $\vec{\delta}$  is the threshold, which is determined by the power consumption of a link in different states and the energy penalty for turning on a power-off link. The time for executing all the loop iterations enclosed by range  $[\vec{I}, \vec{I} + \vec{\delta}]$  is equal to T, the shortest idle period during which the energy saving by turning off the link can amortize the reactivation penalty. This function can be computed as:

$$use(i, \vec{I}, \vec{\delta}) = \bigcup_{\vec{I} = \vec{I'}}^{\vec{I} + \vec{\delta}} links(i, \vec{J}), \text{ where } \vec{I'} \text{ is the next iteration following } \vec{I}.$$

Based on the auxiliary functions, we give  $H_{k,i}$  and  $G_{k,i}$  for command "send $_k(p(\vec{I}),m)$ ":

$$H_{k,i} \ = \ \{\vec{I} \mid |connection(i,p(\vec{I}))| > 1 \ \land \ connection(i,p(\vec{I})) \subseteq use(i,\vec{I},\vec{\delta})\};$$

$$G_{k.i} = \{ \vec{I} \mid connection(i, p(\vec{I})) \cap use(i, \vec{I}, \vec{\delta}) = \phi \}.$$

The explanation for set  $G_{k,i}$  is straightforward — flag LAST of message m is set to 1 if all the links for transferring m will not be used by source node i in the near future, i.e., during the

iterations  $\vec{l}$  through  $\vec{l} + \vec{\delta}$ . Explaining set  $H_{k,\hat{l}}$ , however, is a little involved. flag HOLD of message m is set to 1 only when both of the following criteria are satisfied: (1) transferring m requires multiple hops, and (2) links used for transferring m will be used by the source node of m in the near future, i.e., during the loop iterations  $\vec{l}$  through  $\vec{l} + \vec{\delta}$ . The rationale behind these two criteria includes two parts. First, a connection connecting two communicating nodes is likely to share some links with another connection with another pair of nodes. If a node sends messages again along one of the connections soon, we do not want any link in this connection turned off by another node. A message with HOLD = 1 marks all the links along its way from the source node to the target node as "shared" (by setting SHARED flags of these links to 1) so that these links will not be mistakenly turned off. Second, we do not set flags HOLD to 1 for messages whose source and target nodes are neighbors. The reason is that, if a link used by two adjacent nodes is shared by a connection between two non-adjacent nodes, flag SHARED of this link will be set by the latter connection; if the link used by two adjacent nodes not shared by any other connections, keeping SHARED of this link at 0 allows us turn off the link immediately when we are sure that the source node will not use it for a certain period of time.

For a typical message-based parallel program, most communications take place between adjacent nodes. The compiler based scheme focuses on turning off idle links not shared by multiple connections promptly since the compiler can predict the behavior of these links accurately. As shared links has more complex behavior, which is harder for the compiler to predict, we do not turn off shared links in the compiler algorithm.

#### 2.4.3 Link Pre-activation

A power-off communication link must be turned on (i.e., reactivated) before it can be used. Reactivation incurs both performance and energy penalties. We cannot avoid the energy cost due to reactivation, however, the performance penalty, however, can be hidden by *preactivation*,. That is, we can turn on a power-off link a certain number of cycles before it is actually needed. The compiler performs pre-activation by inserting pre-activation instructions into the application program.

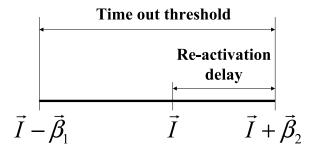

We first define  $attach(i) = \{l_1, l_2, ..., l_n\}$  as the set of links that connect node  $p_i$  with its neighbors. Since node  $p_i$  cannot directly control links not belonging to attach(i), in this work, node  $p_i$  only pre-activates links in its own attach(i) set. For ease of discussion, we define  $Q_{j,i}$  is the set of iterations (executed on node i) using link  $l_j$ . The set of iterations in which we pre-activate link  $l_j$  is:

$$A_{j,i} = \{\vec{I} \mid [\vec{I} - \vec{\beta}_1, \vec{I} + \vec{\beta}_2] \cap Q_{j,i} = \phi\},\$$

where  $\vec{\beta}_1$  and  $\vec{\beta}_2$  are two constant vectors.

Figure 2.6 explains the meaning of  $\vec{\beta}_1$  and  $\vec{\beta}_2$ . Specifically, the overall execution time for loop iterations within  $[\vec{I} - \vec{\beta}_1, \vec{I} + \vec{\beta}_2]$  is equal to  $T_D$ , the time-out period of the links; and, the overall execution time for the loop iterations within  $[\vec{I}, \vec{I} + \vec{\beta}_2]$  is equal to  $T_P$ , the delay due to reactivating a turned off link. In this work, we express set  $A_{j,i}$  in Presburger formulas. The below example shows the link pre-activation code inserted by our compiler:

```

\begin{split} &\text{for } \vec{I} = \vec{L} \text{ to } \vec{U} \; \{ \\ &\text{ if } (\vec{I} \in A_{1,i}) \text{ pre-activate link } l_1; \\ &\text{ for } \vec{I} = \vec{L} \text{ to } \vec{U} \; \{ \\ &\text{ if } (\vec{I} \in A_{2,i}) \text{ pre-activate link } l_2; \\ &\cdots \\ &\text{ send}_k(p(\vec{I}), m); \Longrightarrow &\text{ if } (\vec{I} \in A_{n,i}) \text{ pre-activate link } l_n; \\ &\cdots \\ &\text{ } \\ &\text{

```

Fig. 2.6. Both  $\vec{\beta}_1$  and  $\vec{\beta}_2$  are constant vectors. The overall execution time for loop iterations within  $[\vec{I} - \vec{\beta}_1, \vec{I} + \vec{\beta}_2]$  is equal to the time-out period of links; the overall execution time the loop iterations within  $[\vec{I}, \vec{I} + \vec{\beta}_2]$  is equal to the delay due to activating a power-off link.

Pre-activation is in a sense similar to prefetching [64, 71], a commonly-used latency-hiding mechanism for cache memories. In prefetching, data/instructions are brought into cache memory before needed, in an attempt to hide memory access latency. Similarly, in pre-activation, a communication link is activated (actually reactivated) before it is needed to hide the associated

reactivation latency. We want to reiterate at this point that a wrong placement of the link shutdown or pre-activation commands by the compiler does *not* affect program correctness. It can only cause extra performance and/or power penalties.

## 2.4.4 Experiments

In this section, we present the experimental evaluation of our compiler-based, proactive approach for managing network power. We first introduce the experimental setup and then show experimental results.

We employed the link power model in [90]. Links consume constant power regardless of the utilization due to link signaling features. That is, even when a link is not transmitting data, it consumes the same power,  $P_{on}$ . When a link is turned off, its power consumption is assumed to  $P_{off}$ . When a link is reactivated from power-off state to power-on state, it incurs an energy penalty  $E_P$  during the transition period  $T_P$ . As in [90], the power during this transition period is equal to that in power-on state. Therefore, the total link energy consumption  $E_{link}$  can be expressed as:

$$E_{link} = \sum_{i=1}^{N} (P_{on} \cdot T_{on_i} + P_{off} \cdot T_{off_i} + n_i \cdot E_P),$$

where  $T_{on_i}$  and  $T_{off_i}$  are, respectively, the lengths of total power-on and power-off time periods for link i,  $n_i$  is the number of times link i has been reactivated, and N is the total number of links in the mesh network. In other words, the total energy consumption of links is obtained by aggregating the energy consumption of all the links in the network. Each link's energy contains energies spent in power-on state, power-off state, and the power-off to power-on transition

period. Based on the assumption of  $P_{off}=0$  as in [90, 49] , the expression above becomes:

$$E_{link} = \sum_{i=1}^{N} (P_{on} \cdot T_{on_i} + n_i \cdot E_P).$$

Our simulation framework is a SimpleScalar [5] based execution engine. Multiple simulation processes communicate with each other through a network simulation process. The network simulation process captures all the data communications across the network during the whole execution time, simulates the turn-on/off behavior of each link, and then calculates the overall link energy consumption. The network simulator is adapted from a high-level network power analysis framework, LUNA [31], which has been validated against Orion [101], a cycle-accurate network simulator.

As mentioned earlier, this approach targets loop-intensive applications. The benchmark codes used in our study are extracted from Spec and Perfect Club benchmarks. We give important characteristics of these codes in Table 2.2. Note that "jacobi", "lu", "mxm", and "red-black SOR" are frequently used codes in embedded multimedia processing. We hand-parallelized these codes. All the arrays in the benchmarks are decomposed into 9 parts  $(3 \times 3)$  and distributed over the corresponding processors in the  $3 \times 3$  mesh. The computation-to-processor assignment is performed using the owner-computes rule [79]. The last column of Table 2.2 gives the link energy consumption under the pure hardware-based link power management scheme. As mentioned earlier, in our experiments, we normalize all the energy results with respect to these hardware optimized values.

Table 2.3 gives the default values of important parameters used in our simulation. The power values of links is obtained from the power estimates for an on-chip router and its links

Table 2.2. Benchmark codes.

|               | Input      | Number of | Volume of | Link          |

|---------------|------------|-----------|-----------|---------------|

| Name          | array size | messages  | messages  | energy        |

| eflux         | 25.2MB     | 7546      | 220.6KB   | $330.6 \mu J$ |

| jacobi        | 180MB      | 18960     | 151.7KB   | $737.6 \mu J$ |

| lu            | 1.4MB      | 431233    | 280.8MB   | 232.8mJ       |

| mxm           | 1.1MB      | 178200    | 142.6MB   | 149.1mJ       |

| red-black SOR | 90MB       | 18884     | 94.2KB    | 722.4 $\mu$ J |

| tomcatv       | 25.2MB     | 14890     | 357.7KB   | $582.0 \mu J$ |

| tsf           | 112MB      | 18884     | 150.7KB   | $734.2 \mu J$ |

$(0.07\mu\text{m}, 1\text{GHz})$  in [21]. We also present results when varying the values of some parameters. For most experiments, we assume a  $3 \times 3$  two-dimensional mesh network.

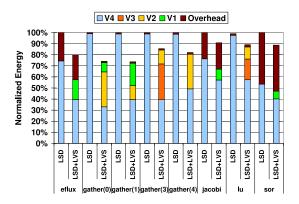

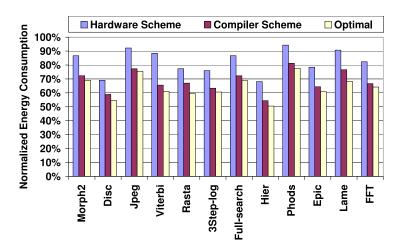

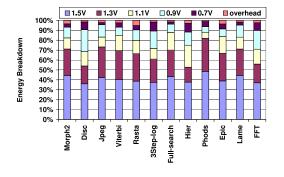

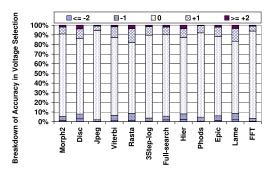

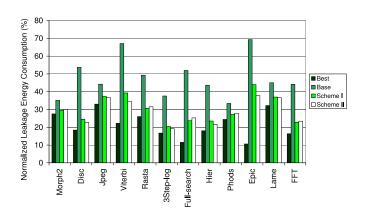

Figure 2.7 shows the normalized link energy consumption values for the proposed compiler-based approach and the hardware-based approach. Each bar is broken into two components: "Link Power-on" and "Link Reactivation". "Link Power-on" represents the link energy consumed in the link power-on states, while "Link Reactivation" is the energy penalty for link reactivations. Each benchmark contains two bars, "HW" and "SW", which correspond to the hardware-based approach and the compiler-based approach, respectively. The results of "SW" are normalized with respect to the corresponding "HW" results.

Our main observation from this bar-chart is that the compiler-based scheme saves more energy than the hardware-based scheme for all the seven benchmarks. The reason is that the compiler can shut down a communication link proactively. First, when the compiler decides to turn off a link, the link does not need to wait for some time (e.g.,  $T_D$  in the hardware-based approach). Thus, it can obtain further energy savings over the hardware-based approach. Note that, during this waiting period in the hardware scheme, the links still consume power. Second, since

Table 2.3. Default system configuration parameters.

| Link frequency                                | 1GHz        |

|-----------------------------------------------|-------------|

| Power of the links for one on-chip switch     | 0.1446W     |

| Link reactivation delay $(T_P)$               | 1000 cycles |

| Link reactivation energy $(E_p)$              | 36.2nJ      |

| Link turnoff threshold for the compiler $(T)$ | $T_{P}$     |

| Processor frequency                           | 1GHz        |

| Packet header size (flits)                    | 3           |

| Flit size (bits)                              | 39          |

| Buffer size (flits)                           | 64          |

Fig. 2.7. Normalized link energy consumption. HW: hardware-based approach; SW: our compiler-based approach.

Fig. 2.8. Performance penalty of the hardware-based approach (over the case when no power optimization is performed).

the compiler is proactive instead of reactive, it can assess the benefits of a link turnoff more accurately. In contrast, the time-out based hardware approach cannot make sure that a link turnoff is really beneficial from the energy perspective. Consequently, sometimes, in the hardware-based link turnoff case, the energy spent for reactivating a link cannot be amortized by the energy saved through turning off this link. As a result, we see an average 18.3% link energy saving obtained by the compiler-based approach over the hardware-based approach. For benchmarks "lu" and "mxm", hardware-based and compiler-based approaches give similar power savings, because these two benchmarks feature frequent communications and large exchanged data volumes. Both approaches cannot execute many link turnoffs.

While our compiler-based scheme performs better than the pure hardware-based one from the power consumption angle, we also need to consider performance for a fair evaluation. We found in our experiments that, as expected, the compiler scheme does not cause any observable performance degradation. This is because it can pre-activate a link which is in the power-off state before it is actually needed. The hardware scheme, on the other hand, does incur some performance penalty, as illustrated by the bar-chart in Figure 2.8. The average communication latency increase it brings is 6.6%. Our base case hardware approach does not incorporate an adaptive routing algorithm when a packet requires a power-off link. This could be one reason why we observe this latency penalty for the hardware-based approach. However, even in [90] that exploits a fully adaptive routing algorithm Opt-Y, the hardware approach incurs an average network latency penalty of 3.5% under the same link reactivation delay. Therefore, we can conclude that the compiler-based scheme is preferable over the hardware based scheme from the performance angle as well. This is particularly true for embedded on-chip networks, where adaptive routing is not typically employed due to its high energy costs [37].

We next perform sensitivity studies by changing the default mesh size and the input data size. Figure 2.9 illustrates the results with different mesh sizes. Only results for benchmark "jacobi" are presented because the trends observed with other benchmarks are very similar. We see that, with different mesh sizes, link energy behavior is quite stable. One can expect our approach to be successful even with large meshes. Results with different data sizes are in Figure 2.10. Besides this default size, denoted as 1X, we made experiments with data sizes X/4, X/2, 2X, and 4X. In this figure, the link energy values achieved by the compiler-based approach are still normalized to that of the hardware scheme. We see that the relative energy savings achieved by the compiler-based approach over the hardware scheme are quite consistent.

Fig. 2.9. The impact of mesh size (benchmark: jacobi).

Fig. 2.10. The impact of data size.

# 2.5 Compiler-Directed Voltage Scaling on Communication Links

## 2.5.1 Motivation

With voltage scalable communication links inside NoCs, there exist chances to scale down the link voltage in a in a performance sensitive manner. Figure 2.11 depicts two example scenarios. In the first scenario (Figure 2.11(a)), a pair of processors in different NoC nodes communicate with each other using non-blocking send and blocking receive operations. Note that the amounts of data sent between them are different. Consequently, the communication from processor 2 to processor 1 can be performed more slowly than that from processor 1 to processor 2. One can potentially scale down the voltage and frequency on the communication channel from processor 2 to processor 1, thereby reducing power. To prevent any performance penalty, the scaling factor should be determined based on the difference between the magnitudes of the communication volumes. In the second scenario (Figure 2.11(b)), a pair of processors first send data to each other and subsequently perform some computation. Let us assume that, while the data volumes in the two communications are the same, the amount of computation performed by processor 2 is much larger than that performed by processor 1. As a result, one can scale down the voltage/frequency on the communication channel from processor 1 to processor 2. These two scenarios illustrate that the opportunities to scale down voltages can come from the differences between the communication volumes on channels and/or from the differences between the computation volumes on NoC nodes; and both of these variances can be exploited through voltage scaling to reduce NoC power consumption without significantly affecting performance. In this work, we do not apply voltage scaling to processors; our focus is on NoC communication links.

```

//On processor 1

//On processor 2

for i = 0 to N {

for i = 0 to N {

send(2, A[i][0..1024]); >

\sim send(1, B[i][0..256]);

receive(2, buffer); ▲

ightharpoonup receive(1, buffer);

}

(a)

//On processor 1

//On processor 2

for i = 0 to N {

for i = 0 to N {

send(2, A[i][0..256]);

send(1, B[i][0..256]);

short computation(...)

long computation(...)

receive(2, buffer);

* receive(1, buffer);

(b)

```

Fig. 2.11. Two example scenarios.

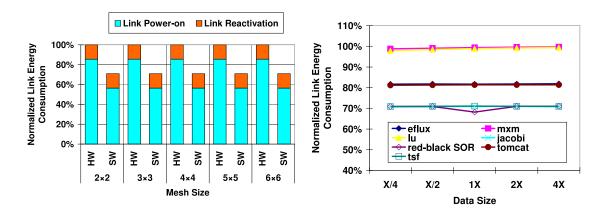

Fig. 2.12. High level view of compiler-directed channel voltage scaling.

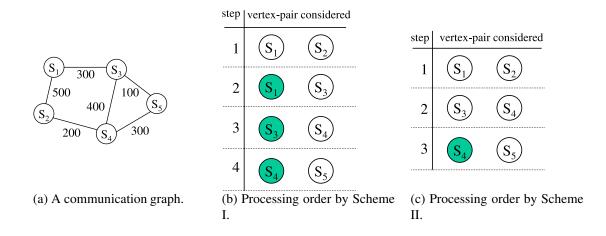

The voltage/frequency scaling approach proposed in this section has three major components. The first component analyze the input code, builds a graph called the *Interprocess Communication Graph (IPCG)*, which captures the communication behavior of the parallel application at hand. The second component, a voltage scaling algorithm, apply critical path analysis to this graph, identifies the voltage scaling opportunities, and determines the channel frequencies and voltages. The last component modifies the input code to insert explicit voltage scaling instructions. Figure 2.12 shows the high level view of our approach. We assume that the input application code has already been parallelized (either manually or through a compiler) for message-passing communication, and inter-processor communications have been optimized using known techniques such as message vectorization and message coalescing [98]. We also that the process-to-node mapping has already been performed.

The rest of this section is structured as follows. The next section presents our graph-based representation. Section 2.5.3 illustrates our algorithm that analyzes the graph and identifies the opportunities for voltage scaling. Section 2.5.4 discusses the necessary code modifications. An experimental evaluation of our approach is presented in Section 2.5.5.

Let us assume, without loss of generality, that a communication channel can work at m different voltage levels (and corresponding frequencies), namely  $v_1, v_2, ..., v_m$ , such that  $v_1 > v_2 > ... > v_m$ . We further assume that it provides data rate  $\lambda$  when working at the highest voltage  $v_1$  and the maximum frequency. The maximum data rate that can be provided at voltage  $v_i$  is assumed to be  $k_i\lambda$ , where  $0 < k_i \le 1$ . We refer to  $k_i$  as the *scaling factor* for voltage  $v_i$ . Thus,  $k_1 = 1$ . When a communication channel works at higher voltage, it provides higher data rate, and consumes more per-bit energy and dissipates more heat. The upper bound of the performance of a given application can be achieved by operating all the communication channels

used by this application at the highest voltage level available. However, this can be an overkill for many applications. For these applications, some communication channels can be operated at lower voltages to reduce energy consumption while not affecting the overall performance significantly. Our goal is to find the the lowest voltage level for each communication channel used by a given application such that the overall performance degradation incurred is within a given bound, as compared to the performance achieved by operating all the communication channels in NoC at the highest available voltage level. To achieve this goal, we need to answer two important questions: (1) which communication channels are non-critical, and (2) to which extent their speeds (and thus voltages) can be reduced without exceeding a preset performance penalty bound.

### 2.5.2 Inter-Process Communication Graph

In this section, we introduce the *Inter-Process Communication Graph (IPCG)*, an abstract representation that captures the communication behavior of a message-passing based parallel program in a concise manner. In order to simplify our analysis, we make the following assumptions about the application code being analyzed:

• An application process uses "send(p, m)" to send message m to process p, and uses instruction "receive(p, m)" to receive message m from process p. For each send or receive instruction, the value p and the size of message, m, can be determined at compilation time.

$<sup>^{3}</sup>$ We can handle the cases where the process id (p) in a send/receive instruction is expressed as a function of the id of the process which executes that send/receive instruction.

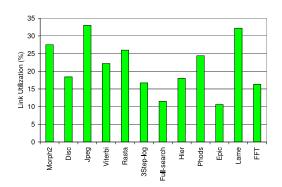

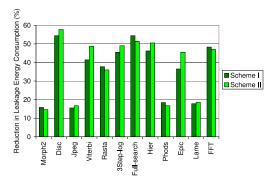

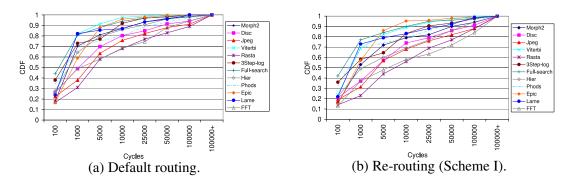

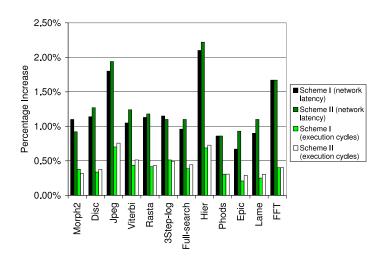

- The message send/receive relationships can be statically captured at compilation time.