## The Pennsylvania State University

The Graduate School

Department of Physics

# IMPROVING THE QUALITY OF CVD GRAPHENE BASED DEVICES AND TRANSPORT STUDIES OF FEW-LAYER WSE<sub>2</sub>

A Dissertation in

Physics

by

Junjie Wang

© 2015 Junjie Wang

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

December 2015

The dissertation of Junjie Wang was reviewed and approved\* by the following:

Jun Zhu

**Associate Professor of Physics**

Dissertation Advisor, Chair of Committee

Eric Hudson

**Associate Professor of Physics**

Theresa Mayer

Distinguished Professor of Electrical Engineering

Mauricio Terrones

Professor of Physics

**Professor of Chemistry**

Professor of Materials Science and Engineering

Nitin Samarth Professor of Physics George A. and Margaret M. Downsbrough Professor Head of the Department of Physics

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

This dissertation consists of two main topics: a) advances on the synthesis and quality of chemical vapor deposited graphene and devices; b) electrical and thermoelectrical transport studies of semiconducting transition metal dichalcogenides (TMDC), in particular few-layer WSe<sub>2</sub>.

Chapter 1 introduces the band structures of graphene and TMDC, as well as the novel physics and potential applications of both materials.

Chapter 2 describes the chemical vapor deposition (CVD) synthesis of graphene on copper using gaseous precursors of methane and hydrogen. Experimenting with the etching of carbon by hydrogen gas during and post growth, we demonstrate successful suppression of multilayer graphene growth, which is a common problem of the field. Next, we show that incorporating a diluted SC-2 cleaning step into the transfer process of CVD grown graphene removes metallic contaminations effectively and leads to a significant improvement of carrier mobility from several thousand cm<sup>2</sup>/Vs to 18,000 cm<sup>2</sup>/Vs at room temperature. These studies contribute to the improvement of graphene-based devices towards practical applications.

Chapter 3 focuses on the characterization of various TMDC materials including  $MoS_2$ ,  $WS_2$ , and  $WSe_2$  using microscopy and spectroscopy. We obtain the crystal structure of  $WSe_2$  using high-resolution transmission electron microscopy (TEM) and X-Ray diffraction (XRD). The layer number-dependent intensity ratio of two Raman modes (2LA and  $A_{1g}$ ) is studied and used to identify the layer number in few-layer  $WS_2$ . The size of the direct band gap (monolayer) and indirect band gap (few-layer to bulk) of

WSe<sub>2</sub> is obtained from photoluminescence (PL) spectroscopy. In monolayer WSe<sub>2</sub>, the width of the A-exciton emission peak decreases with decreasing temperature and saturates at low temperatures to around 15 meV, demonstrating good sample quality. PL spectra of ion irradiated WS<sub>2</sub> reveal additional emissions attributed to defect-bound excitons. Various atomic force microscopy (AFM) based imaging techniques, such as topographic AFM, Kelvin probe force microscopy (KPFM), and scanning thermal microscopy (SThM) are employed to study the morphology, work function and thermal conductivity of few-layer WSe<sub>2</sub> and WS<sub>x</sub>Se<sub>2-x</sub> alloys. These studies provide valuable information on the physical properties of the TMDC materials.

Chapter 4 focuses on the electrical transport properties of few-layer WSe<sub>2</sub> field-effect transistors. We study the gate-dependent conductance of the transistor in the subthreshold regime and demonstrate that the resistance of the Schottky barrier contacts dominates the two-terminal resistance. The transmission mechanism through the contact is found to be thermionic field emission (TFE), which arises from a large amount of impurity states inside the band gap. Applying the TFE model, we self-consistently determine the density of the impurity states to be approximately  $1\sim2\times10^{13}$  cm<sup>2</sup>/eV. We determine these impurity states are due to internal contributions rather than originating from the substrate by comparing devices fabricated on different substrates. The large number of impurity states leads to high mobility-edge carrier density ( $\sim1.1\times10^{13}$  /cm<sup>2</sup> in our devices) and low carrier mobility ( $\sim200$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> in our devices), Our studies shed light on the electrical transport properties of TMDC materials and highlight the material quality challenge of the field.

Chapter 5 presents preliminary thermoelectric transport study of few-layer WSe<sub>2</sub>. Using micro-patterned thermometer and heaters, we obtain preliminary results on the Seebeck coefficient of a 5-layer WSe<sub>2</sub> device. The magnitude of the Seebeck coefficient increases as the Fermi level is increased towards the conduction band edge and exceeds 200  $\mu$ V/K at high carrier densities.

Chapter 6 summarizes the studies discussed in this dissertation.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                           | X    |

|---------------------------------------------------------------------------|------|

| LIST OF TABLES                                                            | xxi  |

| ACKNOWLEDGEMENTS                                                          | xxii |

| Chapter 1: Introduction                                                   | 1    |

| 1.1 Graphene                                                              | 2    |

| 1.1.1 Lattice structure                                                   | 2    |

| 1.1.2 Electronic band structure                                           | 3    |

| 1.1.3 Novel physics and potential applications                            | 5    |

| 1.2 Semiconducting transition metal dichalcogenides (TMDC)                | 6    |

| 1.2.1 Lattice structure                                                   | 6    |

| 1.2.2 Electronic band structure                                           | 8    |

| 1.2.3 Novel physics and potential applications                            | 11   |

| Chapter 2: The synthesis and characterization of graphene                 | 13   |

| 2.1 Graphene characterizations                                            | 14   |

| 2.1.1 Raman spectroscopy                                                  | 14   |

| 2.1.1a Raman scattering theory                                            | 14   |

| 2.1.1b Raman spectra of graphene                                          | 16   |

| 2.1.2 Scanning electron microscopy (SEM) of graphene                      | 19   |

| 2.2 Graphene synthesis via low-pressure chemical vapor deposition (LPCVD) | 19   |

| 2.2.1 Continuous-CVD synthesis                                                         | 21 |

|----------------------------------------------------------------------------------------|----|

| 2.2.2 Pulsed-CVD synthesis                                                             | 25 |

| 2.3 Fabrication of CVD-graphene field effect transistors (GFETs)                       | 31 |

| 2.4 Electrical characterization of GFETs                                               | 36 |

| 2.4.1 Two-terminal electrical measurement setup                                        | 36 |

| 2.4.2 Charged-impurity scattering theory                                               | 39 |

| 2.4.3 Discussion on electron-hole asymmetry at high carrier densities                  | 42 |

| 2.4.4 Electrical test results of GETs                                                  | 44 |

| Chapter 3: Properties of mono- to few-layer TMDC and compounds                         | 47 |

| 3.1 TMDC synthesis                                                                     | 47 |

| 3.2 TMDC crystal quality characterizations                                             | 48 |

| 3.2.1 Transmission electron microscopy (TEM) characterization                          | 48 |

| 3.2.2 X-ray diffraction (XRD) characterization                                         | 50 |

| 3.2.3 Raman spectroscopy characterization                                              | 51 |

| 3.2.4 Photoluminescence spectroscopy (PL) characterization                             | 54 |

| 3.2.5 Discussion on PL spectroscopy of defective TMDC monolayers                       | 57 |

| 3.3 Atomic force microscopy (AFM) and AFM-based characterizations                      | 59 |

| 3.3.1 Topography characterization by AFM                                               | 59 |

| 3.3.2 Workfunction study by Kelvin Probe Force Microscopy (KPFM)                       | 62 |

| 3.3.3 Thermal conductivity study by scanning thermal microscopy                        |    |

| (SThM)                                                                                 | 68 |

| Chapter 4: Electrical transport in few-layer WSe <sub>2</sub> field effect transistors | 72 |

| 4.1 Introduction to charge transport mechanisms at metal/semiconductor         |  |

|--------------------------------------------------------------------------------|--|

| interface                                                                      |  |

| 4.1.1 Formation of Schottky barrier and Fermi level pinning                    |  |

| 4.1.2 Charge transport mechanisms at metal/semiconductor interface             |  |

| 4.2 Device fabrication and measurement techniques                              |  |

| 4.2.1 Device fabrication procedures                                            |  |

| 4.2.2 Electrical transport measurement techniques                              |  |

| 4.3 Electrical transport measurement results                                   |  |

| 4.3.1 General electrical transport features of MX <sub>2</sub> transistors     |  |

| 4.3.1a Hysteresis elimination                                                  |  |

| 4.3.1b Vacuum annealing effect                                                 |  |

| 4.3.2 Discussion on sheet resistance vs contact resistance of WSe <sub>2</sub> |  |

| transistors                                                                    |  |

| 4.3.3 Metal-insulator transition (MIT) in WSe <sub>2</sub> transistors         |  |

| 4.3.4 Electrical transport study of conduction behavior in the                 |  |

| subthreshold regime                                                            |  |

| 4.4 Summaries                                                                  |  |

| Chapter 5: Thermoelectric transport properties of few-layer WSe <sub>2</sub>   |  |

| 5.1 Introduction to thermoelectric materials and basic theory                  |  |

| 5.2 Preliminary thermoelectric transport measurements                          |  |

| 5.2.1 Two-terminal electrical measurement results                              |  |

| 5.2.2 Preliminary Seebeck coefficient measurements                             |  |

| 5.2.2a Measurement techniques                                                  |  |

| 5.2.2b Preliminary Seebeck coefficient results | 124 |

|------------------------------------------------|-----|

| 5.3 Summaries                                  | 125 |

| Chapter 6: Conclusions                         | 126 |

| Appendix A: Lithography recipes                | 128 |

| Appendix B: AFM-based techniques               | 136 |

| Bibliography                                   | 143 |

# LIST OF FIGURES

| Figure | 1-1. Schematics of (a) lattice structure of monolayer graphene, (b)                |    |

|--------|------------------------------------------------------------------------------------|----|

|        | Brillouin zone, and (c) k-space near the K or K' point                             | 2  |

| Figure | 1-2. Electronic band structure of monolayer graphene. Adapted from Fig. 3          |    |

|        | of Ref. [9]                                                                        | 5  |

| Figure | 1-3. Figure 1-3. Schematics of (a) lattice structure, (b) unit cell, and (c)       |    |

|        | Brillouin zone of monolayer MX <sub>2</sub> .                                      | 7  |

| Figure | 1-4. Schematic of 2H MX <sub>2</sub> structure.                                    | 8  |

| Figure | 1-5. (a) Electronic band structure and total and partial density of states of      |    |

|        | monolayer WSe <sub>2</sub> . Adapted from Fig. 7 of Ref. [29]. (b) Electronic band |    |

|        | structure of bulk WSe <sub>2</sub> . Adapted from Fig. 13 of Ref. [29]             | 9  |

| Figure | 1-6. Valence band splitting and coupling between the spin and valley               |    |

|        | degrees of freedom in monolayer TMDC.                                              | 10 |

| Figure | 2-1. Schematic diagram of Raman scattering process.                                | 15 |

| Figure | 2-2. Raman spectrum from a defective monolayer graphene. 514 nm                    |    |

|        | excitation laser line.                                                             | 16 |

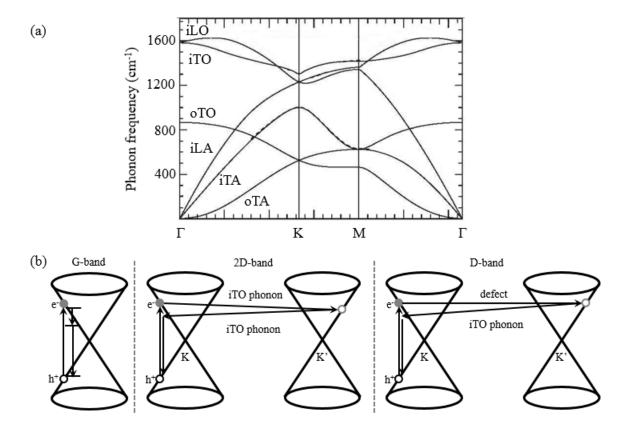

| Figure | 2-3. (a) DFT calculated phonon dispersion of monolayer graphene.                   |    |

|        | Adapted from Fig. 1 of Ref. [61]. (b) Resonant scattering process for G-           |    |

|        | band (left), 2D-band (middle), and D-band in graphene Raman                        | 17 |

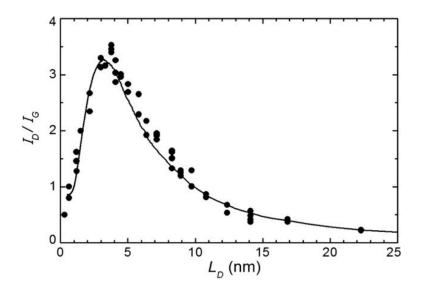

| Figure | 2-4. $I_D/I_G$ vs the average spacing $L_D$ for monolayer graphene. Adapted    |    |

|--------|--------------------------------------------------------------------------------|----|

|        | from Fig. 4 of Ref. [55]                                                       | 18 |

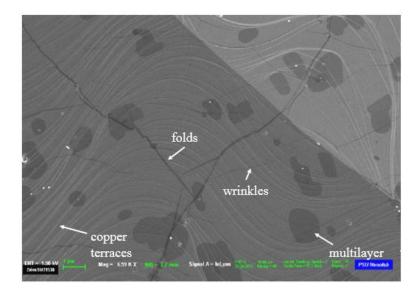

| Figure | 2-5. A typical SEM image of graphene on copper grown by a standard             |    |

|        | CVD method. Common features such as graphene folds, wrinkles, and              |    |

|        | multilayer islands, as well as copper terraces are indicated by arrows         | 19 |

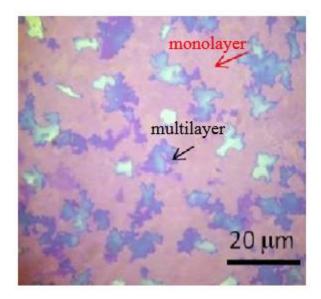

| Figure | 2-6. An optical image of CVD graphene transferred on SiO2/Si substrates        |    |

|        | from Ni. Adapted from Fig. 4 of Ref. [66]                                      | 20 |

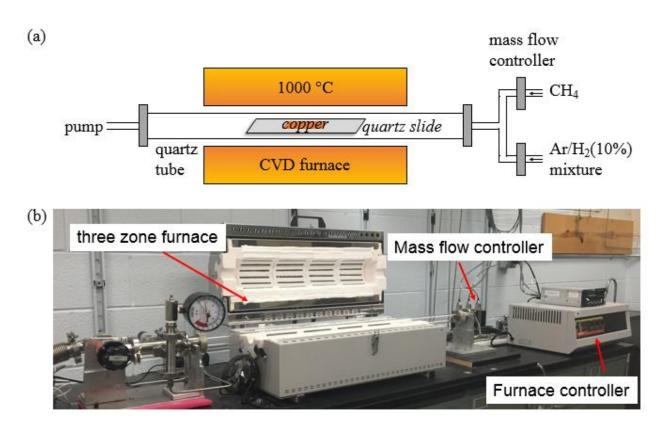

| Figure | 2-7. (a) Schematics and (b) an optical picture of the CVD system used in       |    |

|        | our laboratory                                                                 | 22 |

| Figure | 2-8. Growth profile of the tube furnace during the CVD process. The            |    |

|        | system pressure and flows of methane and $Ar/H_2(10\%)$ are also indicated     |    |

|        | on the diagram                                                                 | 23 |

| Figure | 2-9. SEM images of graphene on copper from continuous CVD growth               |    |

|        | with total methane flow of 100 s.c.c. (left) and 200 s.c.c. (right). The white |    |

|        | arrow points at copper surface that is not covered by graphene yet             | 24 |

| Figure | 2-10. Schematics of methane flow during the graphene growth process at         |    |

|        | 1000 °C for continuous (top) and pulsed (bottom) CVD methods                   | 25 |

| Figure | 2-11 Schematic illustrations of a)&b) the formation of multilayer graphene     |    |

|        | patches near a defect site on copper during the continuous-CVD process,        |    |

|        | and c)&d) suppression mechanism in the pulsed-CVD process. Adapted             |    |

|        | from Fig. 4 of Ref. [69]                                                       | 26 |

| Figure 2-12. SEM images from three pulsed-CVD graphene synthesizes. From (a)                      |    |

|---------------------------------------------------------------------------------------------------|----|

| to (c), the growth condition $t_1/t_2$ and MLG coverage are: $2min/2min$ ,                        |    |

| 15.7%; 1min/2min, 8.2%; and 0.5min/2.5min, 3.7%, respectively. For all                            |    |

| three growth, methane and Ar/H <sub>2</sub> (10%) flow rates are fixed at t $f_{\rm CH4}=10$      |    |

| s.c.c.m. and $f_{\rm H2} = 200$ s.c.c.m. with a total amount 200. s.c.c. methane                  | 27 |

| Figure 2-13. An optical image of pulsed-CVD graphene transferred on                               |    |

| SiO <sub>2</sub> (290nm)/Si substrate. No MLG patches are visually observed. Inset                |    |

| shows an SEM image of graphene from the same growth batch                                         | 28 |

| Figure 2-14. (a) Schematics of the modified CVD process with the post-growth                      |    |

| etching step. (b) An SEM image of multilayer-free graphene on copper                              | 30 |

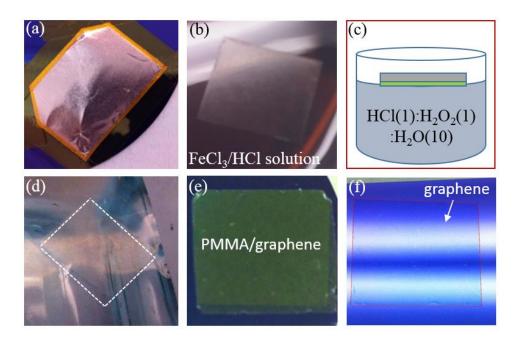

| Figure 2-15. Polymer-assisted transfer process for CVD graphene                                   | 31 |

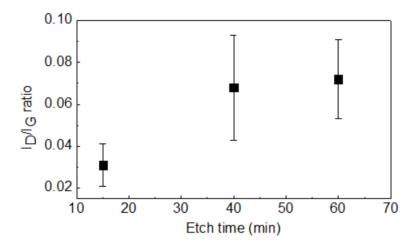

| Figure 2-16. I <sub>D</sub> /I <sub>G</sub> from monolayer regions of CVD graphene transferred on |    |

| SiO <sub>2</sub> /Si substrate with 15min, 40min, and 60min Cu etch time during the               |    |

| transfer process.                                                                                 | 32 |

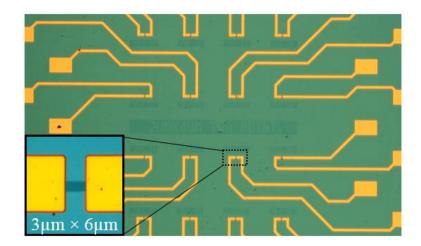

| Figure 2-17. An optical image of GFET arrays with 16 two-terminal transistors.                    |    |

| Inset is an SEM (false colored) zoom-in of the graphene channel. Image                            |    |

| courtesy of Dr. Bei Wang.                                                                         | 35 |

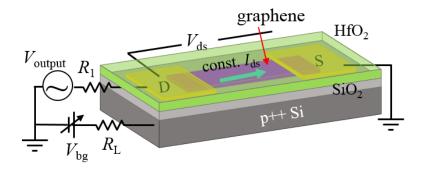

| Figure 2-18. Schematics of the two-terminal GFET structure and the electrical                     |    |

| measurement configuration using a constant current excitation method                              | 36 |

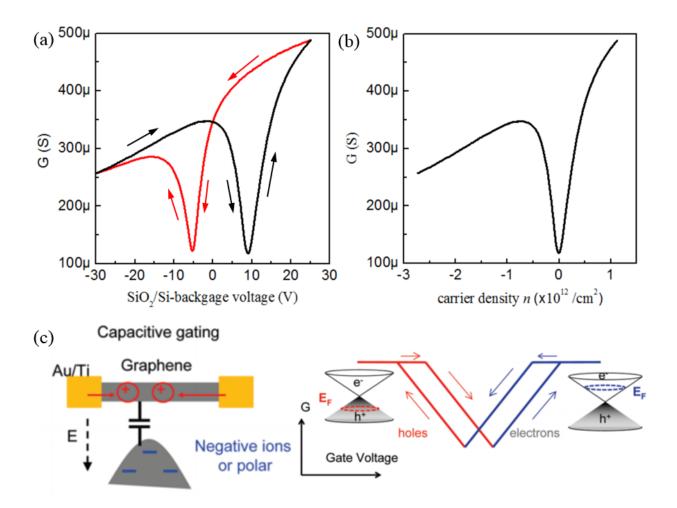

| Figure 2-19. (a) A typical hysteretic transfer curve of GFET. (b) The same                        |    |

| forward Vbg-sweep conductance curve in (a) plotted as a function of                               |    |

|        | carrier density. (c) Schematics of the capacitive gating model and the                      |    |

|--------|---------------------------------------------------------------------------------------------|----|

|        | resulting hysteresis direction. Adapted from Ref. [73]                                      | 38 |

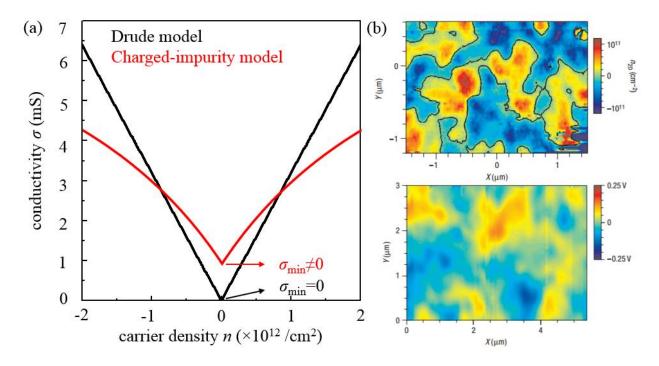

| Figure | 2-20. (a) Graphene sheet conductance vs carrier density from the Drude                      |    |

|        | model (black line) and the charged-impurity model incorporating short-                      |    |

|        | range scattering (red curve). (b) A color map of the spatial density                        |    |

|        | variation in graphene flake (top) and a surface potential map of the bare                   |    |

|        | silicon oxide surface near the graphene flake in the top graph. Adapted                     |    |

|        | from Fig. 3 of Ref. [75]                                                                    | 40 |

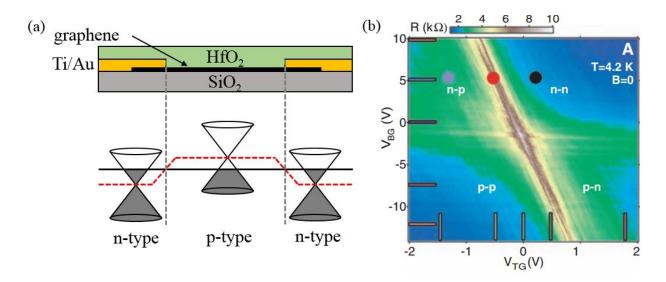

| Figure | 2-21. (a) Schematics of the p-n junction formation at negative backgate                     |    |

|        | voltages. (b) A color map of graphene p-n junction resistance. Adapted                      |    |

|        | from Fig. 2 of Ref. [80].                                                                   | 43 |

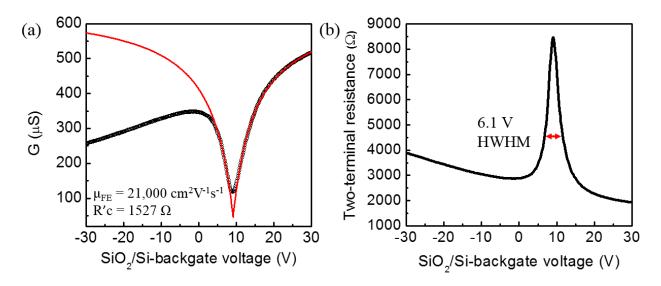

| Figure | 2-22. (a) An example of applying Eq. (2.9) to a $G(V_{bg})$ curve. $\mu_{FE}=21,000$        |    |

|        | cm <sup>2</sup> /Vs and Rc'=1527 $\Omega$ . (b) Same curve in (a) plotted in resistance for |    |

|        | measurement of the FWHM. The narrow 6.1 V width further attests to the                      |    |

|        | high mobility obtained in (a)                                                               | 44 |

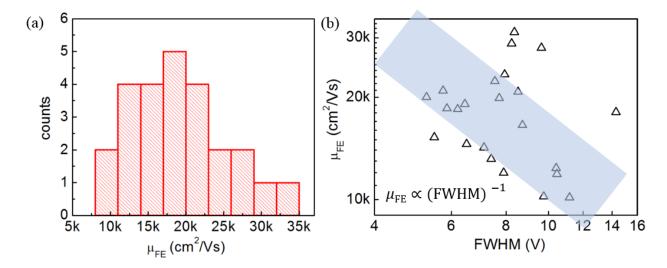

| Figure | 2-23. (a) Histogram distribution of field effect mobility $\mu_{FE}$ obtained from          |    |

|        | a total of 25 GFETs. (b) Log-log plot of $\mu_{FE}$ vs FWHM                                 | 45 |

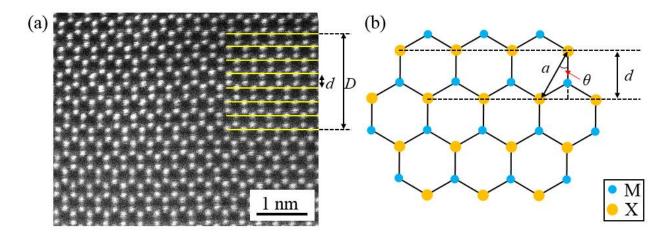

| Figure | 3-1. (a) High-resolution HAADF TEM image of a CVT-grown FSU-WSe <sub>2</sub>                |    |

|        | crystal and imaged along the [110] plane of both W and Se atoms. The                        |    |

|        | hexagonal lattice confirms the 2H crystal structure. Image courtesy of                      |    |

|        | Daniel Rhodes. (b) Schematics showing the relation between in-plane                         |    |

|        | lattice constant and spacing d i.e. $d = a \times \cos(\theta)$                             | 49 |

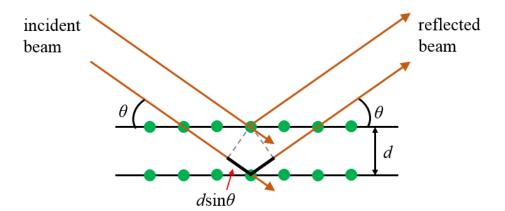

| Figure 3-2. Schematics of x-ray diffraction process                                               | 50 |

|---------------------------------------------------------------------------------------------------|----|

| Figure 3-3. XRD spectrum of a CVT-grown PSU-WSe <sub>2</sub> crystal measured with the            |    |

| $K\alpha$ line of copper. The peaks are indexed by Miller indices. The in-plane                   |    |

| and out-of-plane lattice constants are a=3.28 Å and c=12.95 Å. Image                              |    |

| courtesy of Minh An Nguyen.                                                                       | 51 |

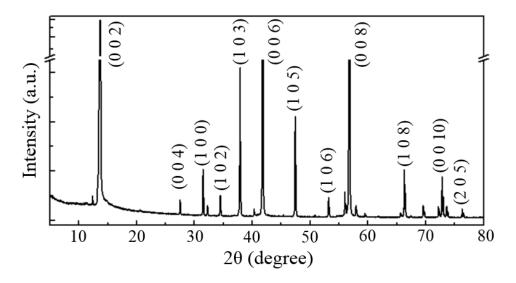

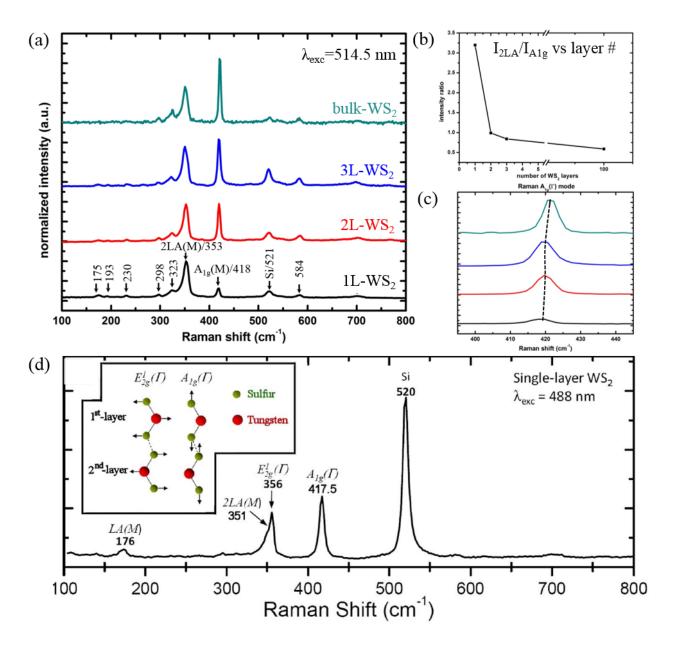

| Figure 3-4. (a) Raman spectra of exfoliated mono-, bi-, tri-layer and bulk PSU-                   |    |

| $WS_2$ on $SiO_2/Si$ substrate. 514.5 nm excitation laser line. (b) $I_{2LA}/I_{A1g}\ vs$         |    |

| layer number. (c) Blue shift in $A_{1g}(\Gamma)$ peak position with increasing layer              |    |

| number. (d) Raman spectrum of a CVD-grown single layer WS2 obtained                               |    |

| using 488 nm laser excitation. Inset shows the lattice vibrations for $E_{2g}(\Gamma)$            |    |

| and $A_{1g}(\Gamma)$ modes. Adapted from Fig. 1 of Ref. [89]                                      | 52 |

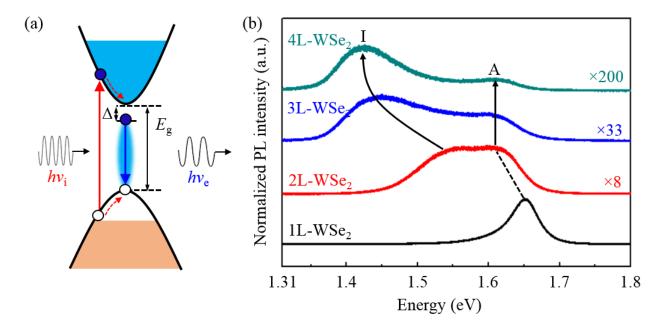

| Figure 3-5. (a) Schematics of PL emission process. (b) PL spectra of exfoliated 1-                |    |

| to 4-layer FSU-WSe <sub>2</sub> on SiO <sub>2</sub> /Si substrate. 488 nm laser excitation. Image |    |

| courtesy of Simin Feng.                                                                           | 55 |

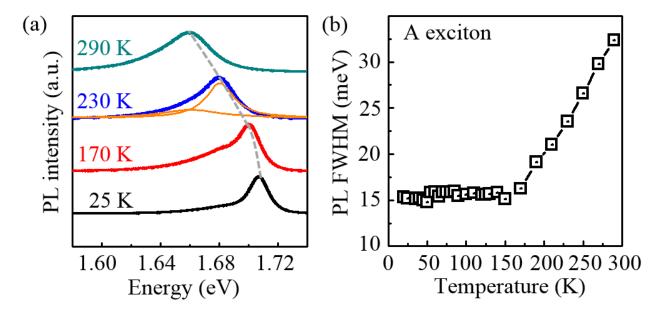

| Figure 3-6. (a) PL spectra of exfoliated monolayer FSU-WSe <sub>2</sub> on SiO <sub>2</sub> /Si   |    |

| substrate at selected temperatures from 25K to 290K. The position of the                          |    |

| A exciton peak is indicated by the dashed line. Fits to the 230K trace are                        |    |

| shown underneath the data. (b) Temperature dependence of the FWHM of                              |    |

| the A-exciton peak. The low-temperature width of 15 meV indicates the                             |    |

| high crystal quality                                                                              | 56 |

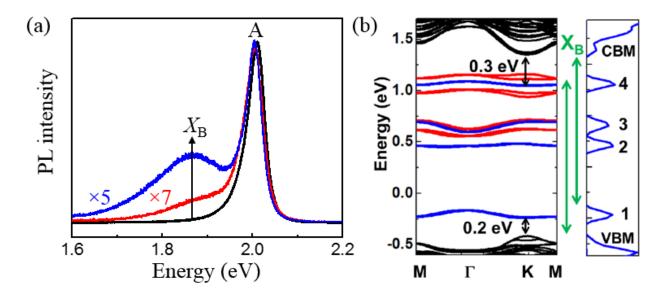

| Figure 3-7. (a) PL spectra of exfoliated pristine (black curve) and defective (red                |    |

| and blue curves) PSU-WS <sub>2</sub> monolayers. 488 nm laser excitation. (b)                     |    |

| Calculated electronic band structure of monolayer MoS <sub>2</sub> in the presence of                   |    |

|---------------------------------------------------------------------------------------------------------|----|

| di-S vacancies. Right panel: Total density of states of the monolayer $MoS_2$                           |    |

| with S vacancies in the presence of N <sub>2</sub> . Adapted from Fig. 5 of Ref. [101]                  | 58 |

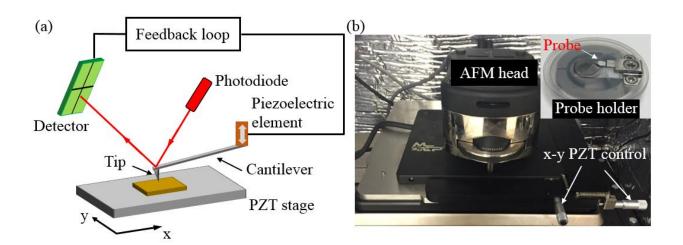

| Figure 3-8. Schematic diagram of the AFM measurement setup. (b) An optical                              |    |

| picture of our AFM instrument                                                                           | 60 |

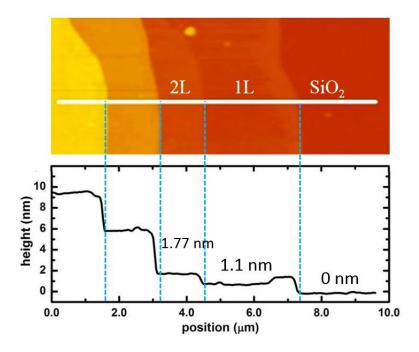

| Figure 3-9. Top: Tapping mode AFM height map of an exfoliated PSU-WS <sub>2</sub> on                    |    |

| SiO <sub>2</sub> /Si with regions of identified layer numbers. Bottom: Height profile                   |    |

| along the while line in the height map                                                                  | 61 |

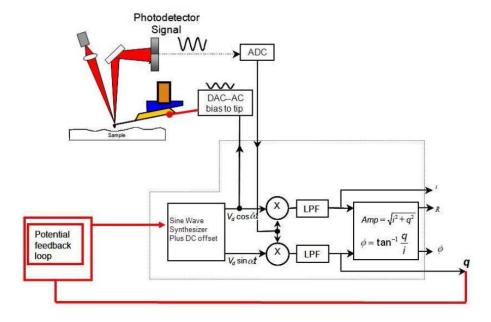

| Figure 3-10. Schematic diagram of the KPFM measurement configuration.                                   |    |

| Adapted from Fig. 10.1 of Ref. [102].                                                                   | 63 |

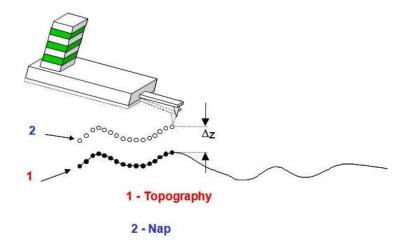

| Figure 3-11. Schematic diagram of the Nap mode scan. Adapted from Fig. 10.2 of                          |    |

| Ref. [102]                                                                                              | 65 |

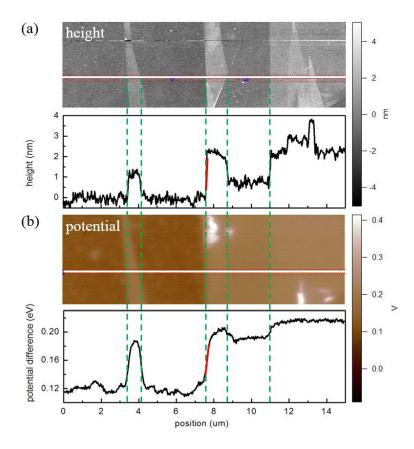

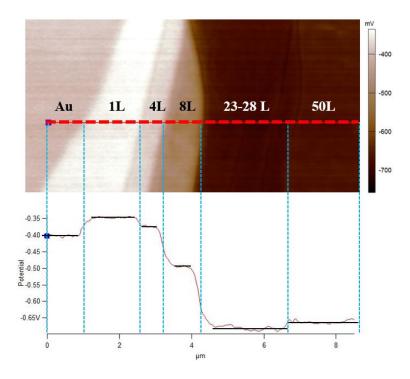

| Figure 3-12. (a) KPFM height map of an exfoliated graphene on Au/Si and a                               |    |

| height profile along the white line. (b) KPFM potential map of the same                                 |    |

| region in (a) and the potential profile along the same line                                             | 66 |

| Figure 3-13. KPFM potential map of exfoliated UT-WSe <sub>2</sub> on Au/Si substrate with               |    |

| regions of identified layer number. The bottom graph is the potential                                   |    |

| profile along the red line in the potential map. Image courtesy of Jacob                                |    |

| Shevrin.                                                                                                | 67 |

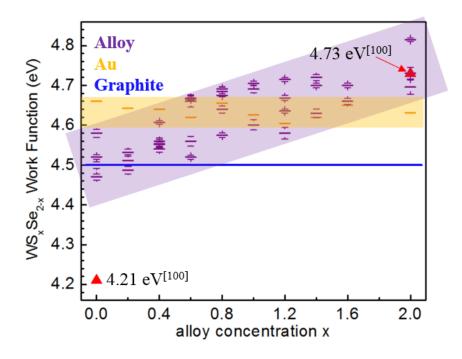

| Figure 3-14. Workfunction evolution of PSU-WS <sub>x</sub> Se <sub>2-x</sub> alloy as a function of the |    |

| alloy concentration x                                                                                   | 68 |

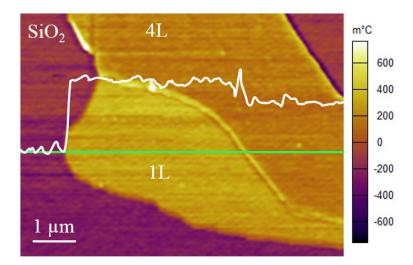

| Figure | 3-15. SThM temperature map of an exfoliated UT-WSe <sub>2</sub> flake on SiO <sub>2</sub> /Si |    |

|--------|-----------------------------------------------------------------------------------------------|----|

|        | and is measured using active mode scan. The temperature on the graph is                       |    |

|        | linearly proportional to the real temperature by an unknown factor. Higher                    |    |

|        | temperature corresponds to lower thermal conductivity                                         | 70 |

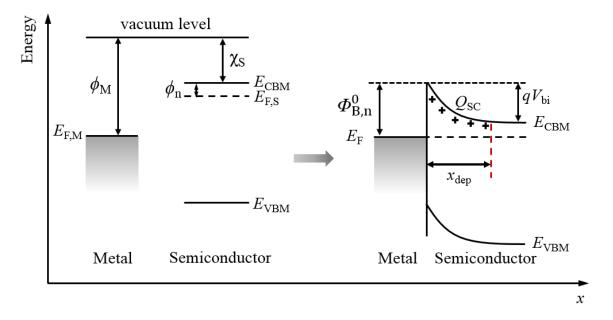

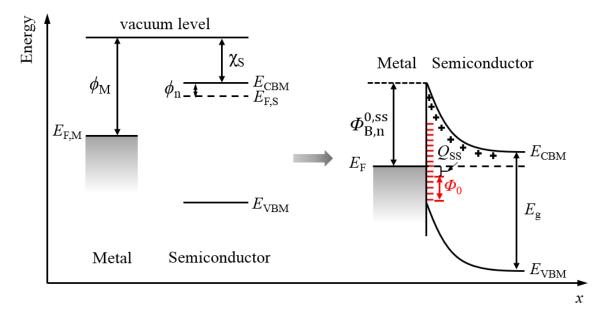

| Figure | 4-1.Schematic band diagram of the Schottky barrier formation at the                           |    |

|        | metal/semiconductor interface for ideal condition                                             | 75 |

| Figure | 4-2. Schematic band diagram of the Schottky barrier formation in the                          |    |

|        | presence of surface states                                                                    | 77 |

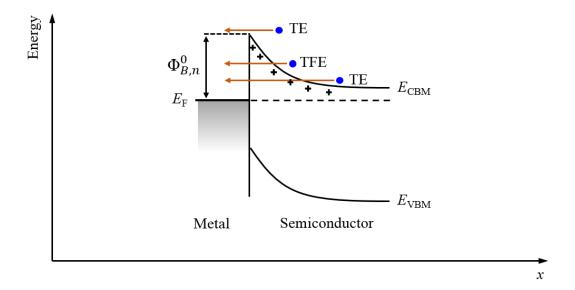

| Figure | 4-3. Schematics of three carrier transport process at the                                     |    |

|        | metal/semiconductor interface, i.e. thermionic emission (TE), thermionic                      |    |

|        | field emission (TFE), and field emission (FE)                                                 | 78 |

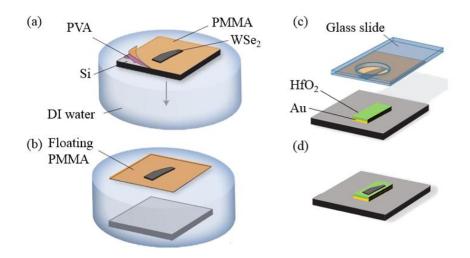

| Figure | 4-4. PMMA/PVA-assisted transfer process. Adapted and modified from                            |    |

|        | Fig. 1 of Ref. [114].                                                                         | 82 |

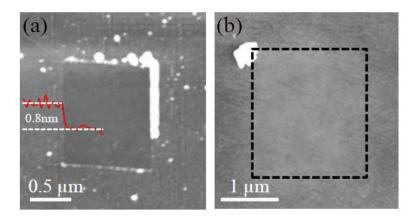

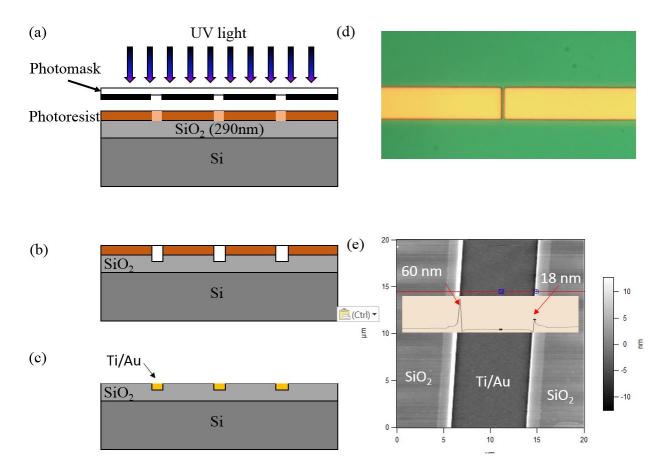

| Figure | 4-5. (a) AFM tapping mode image shows resist accumulation at the                              |    |

|        | borders of a square area scanned by the tip in contact mode prior to the                      |    |

|        | acquisition of this image. The line cut reveals a resist layer thickness of                   |    |

|        | 0.8 nm. (b) Another AFM tapping mode image shows a clean surface after                        |    |

|        | low-energy Ar <sup>+</sup> bombardment.                                                       | 86 |

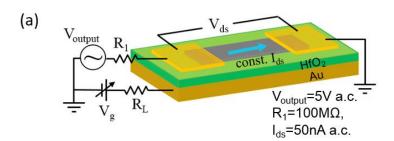

| Figure | 4-6. Schematics of electrical measurement setup for (a) constant current                      |    |

|        | excitation and (b) constant bias excitation.                                                  | 87 |

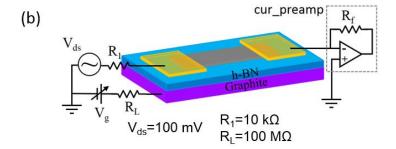

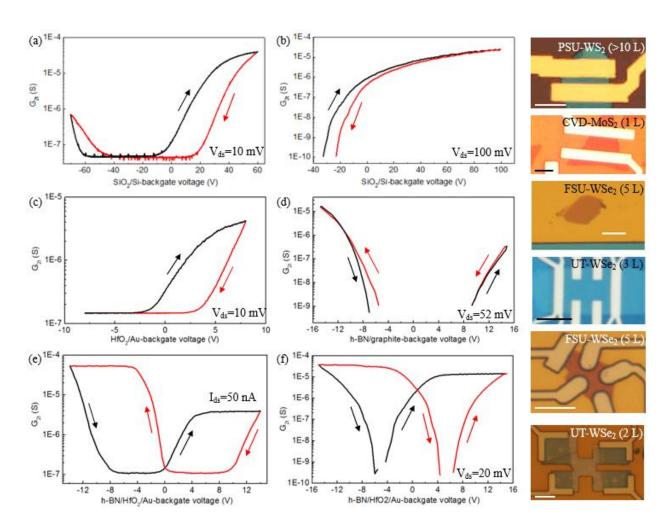

| Figure | 4-7. Representative two-terminal gate-dependent conductance curves                             |    |

|--------|------------------------------------------------------------------------------------------------|----|

|        | shows common transport characteristics including ambipolar conduction                          |    |

|        | with e-h symmetry and hysteretic transfer                                                      | 89 |

| Figure | 4-8. "p+-", "p++" and "p" pulse patterns used in pulsing-gate                                  |    |

|        | measurements                                                                                   | 91 |

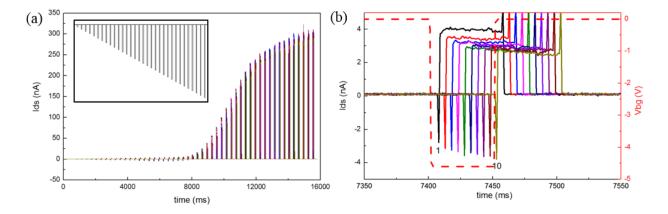

| Figure | 4-9. (a) Example of source-drain current response $I_{\rm ds}$ in pulsed-gating                |    |

|        | measurements. Inset shows the gate pulse pattern used. (b) A zoom-in plot                      |    |

|        | of Ids for $V_{\text{bg}} = -4.5 \text{ V}$                                                    | 92 |

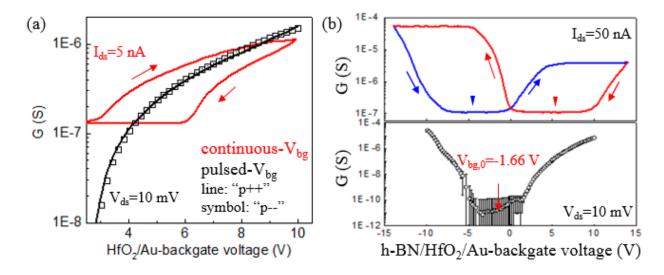

| Figure | 4-10. Comparison of $G(V_{\rm bg})$ measured using the continuous and pulsed-                  |    |

|        | gating techniques from (a) a 3-layer MoS <sub>2</sub> transistor and (b) a 5-layer             |    |

|        | FSU-WSe <sub>2</sub> transistor.                                                               | 93 |

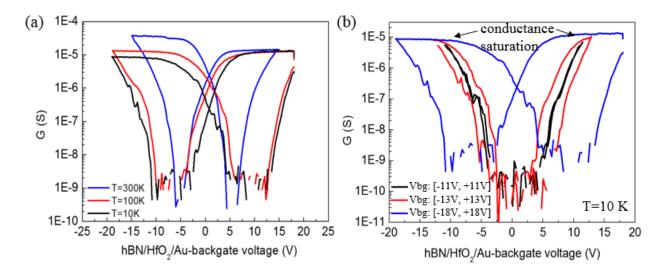

| Figure | 4-11. (a) Hysteretic $G(V_{bg})$ at $T = 300 \mathrm{K}$ , 100K, and 10K. (b) $G(V_{bg})$      |    |

|        | measured with different gate sweeping ranges at 10K.                                           | 94 |

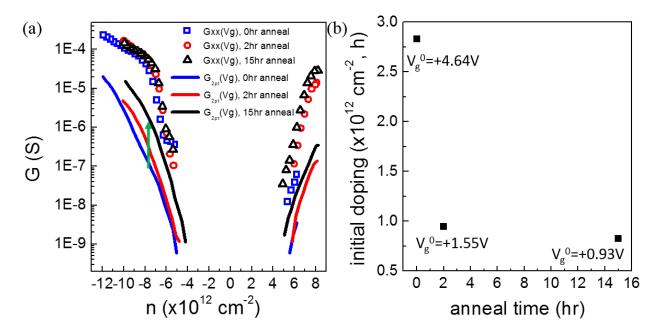

| Figure | 4-12. (a) Two-terminal and four-terminal $G(V_{\text{bg}})$ from a 3-layer UT-WSe <sub>2</sub> |    |

|        | transistor at 300K after 0hr, 2hr, and 15hr accumulated vacuum annealing.                      |    |

|        | (b) Initial doping level vs the accumulated vacuum annealing time                              | 96 |

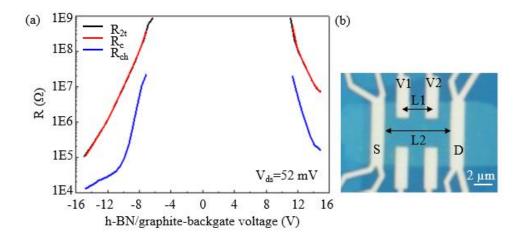

| Figure | 4-13. (a) Comparison of total, contact, and channel resistant from a 3-layer                   |    |

|        | UT-WSe <sub>2</sub> transistor. (b) An optical image of the device                             | 97 |

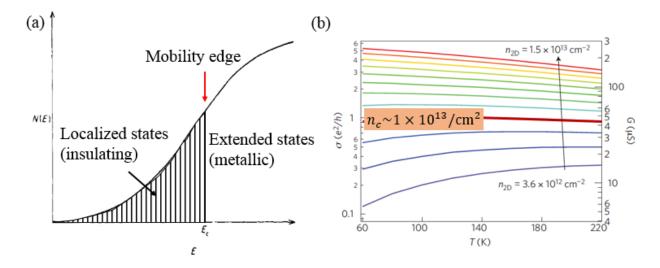

| Figure | 4-14. (a) Density of states $N(E)$ in a material with disorders showing the                    |    |

|        | mobility edge Ec. Adapted from Fig. 1 of Ref. [126]. (b) Temperature                           |    |

| dependence of the MoS <sub>2</sub> sheet conductance shows the presence of MIT.                   |     |

|---------------------------------------------------------------------------------------------------|-----|

| Adapted from Fig. 3 of Ref. [106].                                                                | 100 |

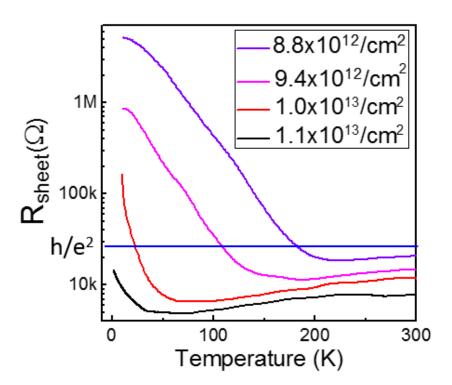

| Figure 4-15. Temperature dependence of sheet resistance from the 3-layer UT-                      |     |

| WSe <sub>2</sub> transistor at different carrier densities.                                       | 101 |

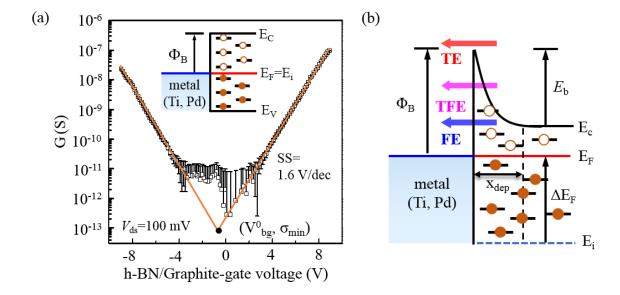

| Figure 4-16. (a) Two-terminal $G(V_{bg})$ for a 3-layer FSU-WSe <sub>2</sub> transistor on h-BN   |     |

| in a semi-log plot. The absence of hysteresis indicates trap-free interface.                      |     |

| Fits to log $G$ vs $V_{\rm bg}$ yield SS of 1.6 V/dec for both electron and hole. The             |     |

| charge neutrality point occurs at $V_{\rm bg}^0 = -0.58$ V and $G_0 = 8.7 \times 10^{-14}$ S, the |     |

| band diagram at which is shown in the inset. (b) Band diagram near the                            |     |

| metal contact in the case of electron doping                                                      | 102 |

| Figure 4-17. Schematics of two parallel-plate capacitors connected in series                      | 104 |

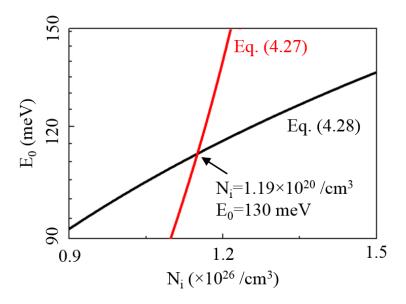

| Figure 4-18. An example of the self-consistent determination of $N_i$ and $E_0$                   | 107 |

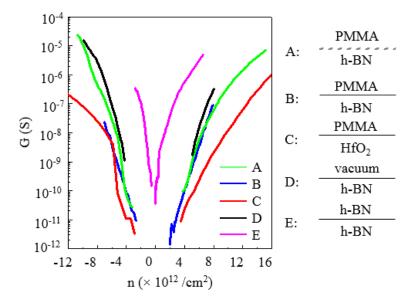

| Figure 4-19. Comparison of devices in different dielectric environment. Two-                      |     |

| terminal conductance $G$ vs carrier density $n$ for devices 5L-A, 3L-B, 5L-C,                     |     |

| 3L-D and 4L-E. Schematics indicate the dielectric layers adjacent to the                          |     |

| WSe <sub>2</sub> sheet. After accounting for the gating efficiencies, the SS slopes are           |     |

| very similar over a large range of subgap energies despite the large                              |     |

| differences in substrate surface chemistry.                                                       | 109 |

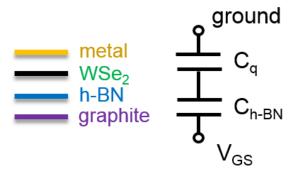

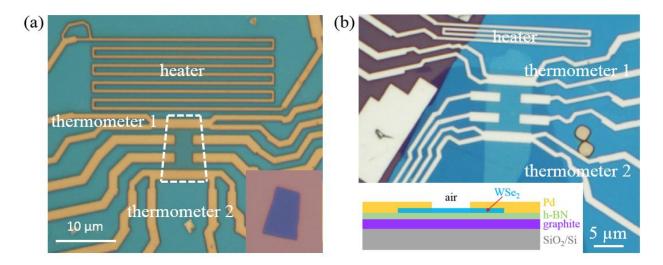

| Figure 5-1. (a) An optical image of a 5-layer FSU-WSe <sub>2</sub> TE-FET. The inset shows        |     |

| an optical image of the WSe <sub>2</sub> sheet. (b) An optical image of a 3-layer UT-             |     |

|        | WSe <sub>2</sub> TE-FET. The inset shows a schematic cross-section view of the                                                                                                                                                                                                                                       |     |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | device structure.                                                                                                                                                                                                                                                                                                    | 114 |

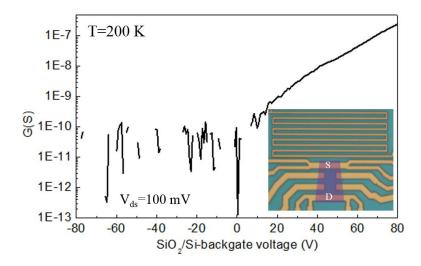

| Figure | 5-2. Two-terminal $G(V_{bg})$ at 200K. The inset shows an optical image of the device.                                                                                                                                                                                                                               | 115 |

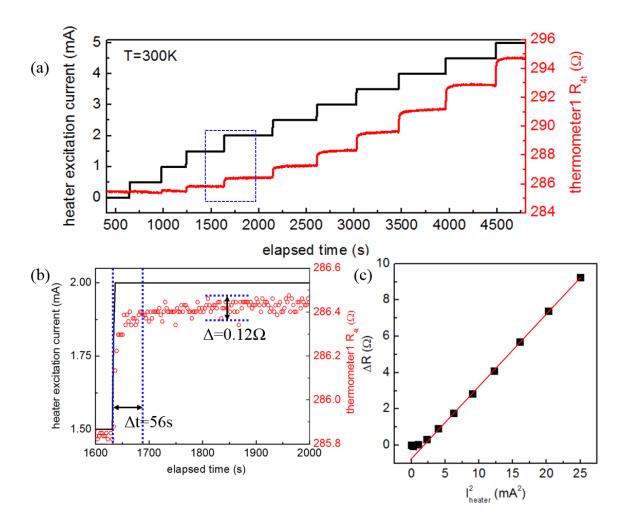

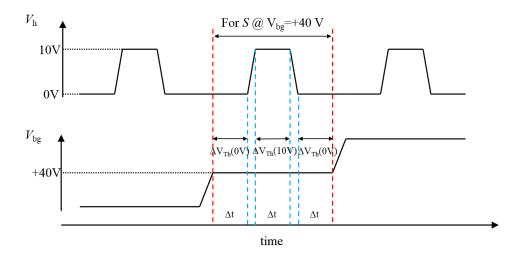

|        | 5-3. (a) Heater excitation current $I_{heater}$ and the corresponding thermometer resistance as a function of the elapsed time. (b) Zoom-in of the circled region in (a). The peak-to-peak resistance fluctuation is 0.12 $\Omega$ . The rise time to a steady resistance reading is $\sim$ 56s. (c) The thermometer |     |

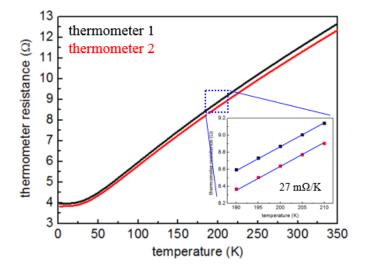

|        | resistance change as a function of I <sub>heater</sub> square shows a linear relation  5-4. Temperature calibration of the Pd thermometer resistance. Inset is a                                                                                                                                                     | 116 |

|        | zoom-in plot around T=200K showing good linear dependence within ±10K range                                                                                                                                                                                                                                          | 117 |

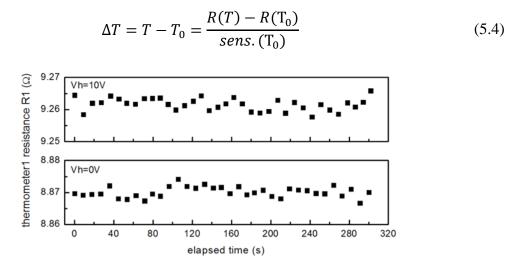

| Figure | 5-5. Thermometer 1 resistance stability check at V <sub>h</sub> =0V and 10V. The base temperature is 200K.                                                                                                                                                                                                           | 118 |

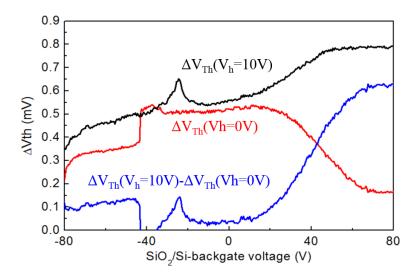

|        | 5-6. Thermoelectric voltage $\Delta V_{\text{Th}}$ vs $V_{\text{bg}}$ for $V_{\text{h}}$ =0V (red curve) and 10V black curve). The blue curve is obtained by subtracting the red curve from the black.                                                                                                               | 119 |

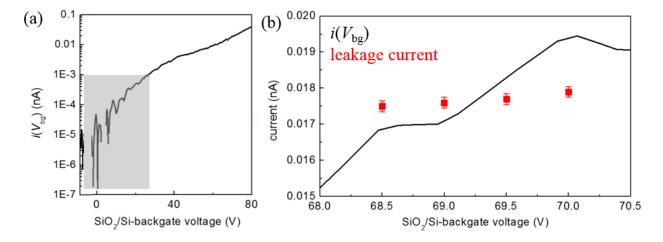

|        | 5-7. (a) $i(V_{bg})$ vs Vbg obtained using Eq. (5.5). (b) Zoom-in for $V_{bg}$ from +69.0V to +70,5V. The discrete red symbols are leakage current measured by parking $V_{bg}$ at selected voltages.                                                                                                                | 120 |

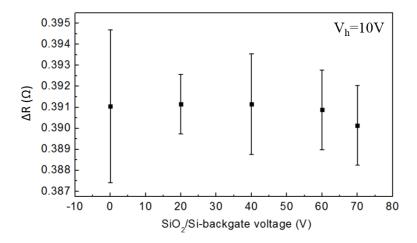

| Figure 5-8. Thermometer resistance change $\Delta R$ vs $V_{bg}$ at 10V heater excitation             |     |

|-------------------------------------------------------------------------------------------------------|-----|

| voltage. 200K base temperature                                                                        | 121 |

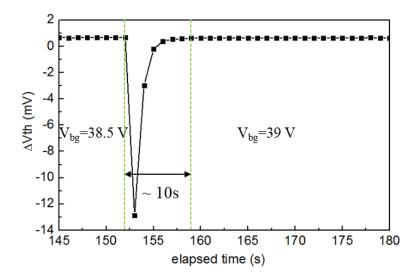

| Figure 5-9. Thermoelectric voltage $\Delta V_{\text{Th}}$ vs time as Vbg is stepped from +38.5V       |     |

| to +39V. It takes about 10s for $\Delta V_{\text{Th}}$ to become steady                               | 122 |

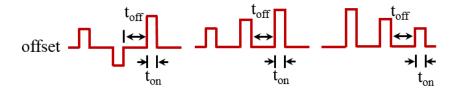

| Figure 5-10. Schematics of the Seebeck coefficient measurement protocols for                          |     |

| future experiments. $\Delta V_{\text{Th}}$ is only taken at parked $V_{\text{bg}}$                    | 123 |

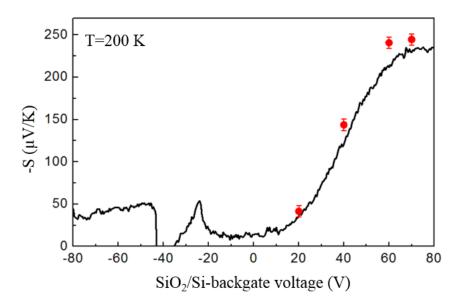

| Figure 5-11. Seebeck coefficient $S$ vs $V_{\rm bg}$ at T=200K. The black curve is obtained           |     |

| using $\Delta V_{\text{Th}}$ from continuous $V_{\text{bg}}$ sweep, and the red symbols are generated |     |

| using $\Delta V_{\mathrm{Th}}$ measured at parked $V_{\mathrm{bg}}$                                   | 124 |

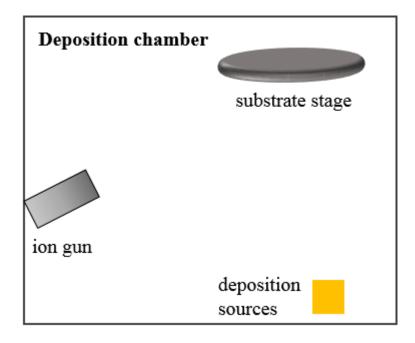

| Figure A-1. Schematics of the Lab-18 deposition chamber with an integrated ion                        |     |

| gun                                                                                                   | 128 |

| Figure A-2. Fabrication process of the embedded local backgates                                       | 131 |

| Figure A-3. ALD recipe program for HfO₂ growth at 110 ℃                                               | 133 |

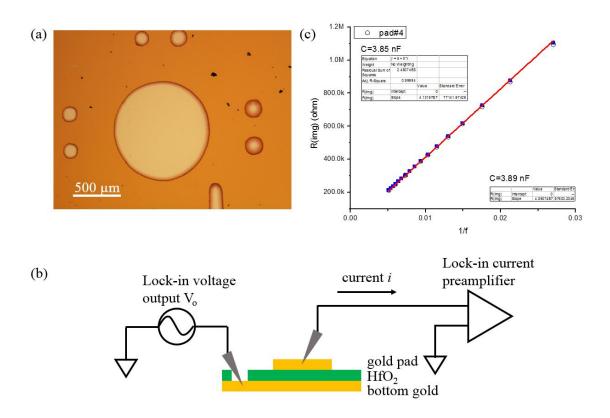

| Figure A-4. Capacitance measurements for ALD-grown HfO <sub>2</sub>                                   | 134 |

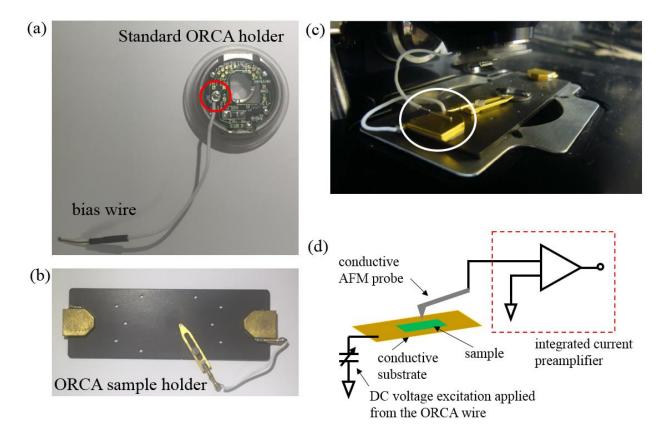

| Figure B-1. Optical images and schematics for KPFM measurements. (c) Image                            |     |

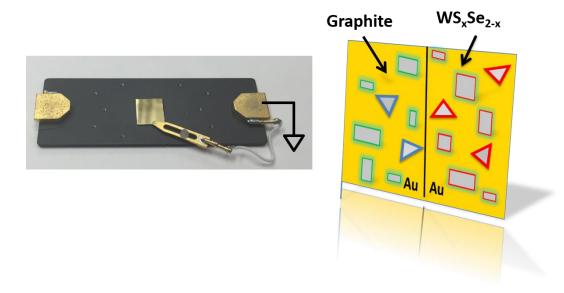

| courtesy of Asylum Research.                                                                          | 137 |

| Figure B-2. An optical image of a sample mounted on the KPFM sample holder                            |     |

| and Schematics of sample preparation                                                                  | 140 |

# LIST OF TABLES

| Table 1-1 Experimental and theoretical gap sizes of monolayer and 2H-bulk TMDC |    |

|--------------------------------------------------------------------------------|----|

|                                                                                | 10 |

#### **ACKNOWLEDGEMENTS**

I would like to express my deepest respect and most sincere gratitude to my advisor Dr. Jun Zhu for her patient education and guidance during my doctoral studies at Penn State. It was her insight in physics and mentoring that guided me through the difficult times in my graduate research over the past five years. She has made a great influence on me with her enthusiasm in physics and rigorous attitude towards science. I also feel grateful to my committee members: Dr. Mauricio Terrones, Dr. Eric Hudson and Dr. Theresa Mayer for their help on my Ph.D. dissertatioin.

Many of the experiments that were accomplished in this thesis are the results of help from group members and collaborations with different research groups. My sincere thanks to Minh An Nguyen, Daniel Rhodes, Jiaqiang Yan, from whom I obtained the TMDC crystals. I feel grateful to Dr. Bei Wang who taught me the synthesis of CVD graphene and device fabrication techniques when I joined Jun's group. I thank Jing Li for sharing with me many of the device fabrication techniques and helping me in solving problems in many electrical measurements. I thank Simin Feng for helping me with the Raman and Photoluminescence measurements.

I would also like to express my thanks to the staffs at the Nanofabrication Laboratory of Penn State for their help in the fabrication of devices in this dissertation.

Finally, I would like to thank my parents and grandparents for their love, support, and confidence in me. I dedicate my dissertation to them.

To my beloved parents and grandparents

谨以此论文献给我敬爱的父母和祖父母

## **Chapter 1**

## Introduction

Scientific research in two-dimensional (2D) materials have been developing at a fast pace ever since the first experimental discovery of single-layer graphene in 2004.[1-3] Due to the confinement of charge carriers and phonons, 2D materials possess novel physical properties and show great application potentials. Although active experimental explorations have only been slightly more than 10 years, theoretical studies of the 2D materials can trace back to more than 50 years ago. For example, the electronic band structure of graphene was first proposed by P. R. Wallace in 1947[4].

Formed by a layer of carbon atoms, monolayer graphene can be viewed as the base material of  $sp^2$ -hybridization based carbon nanomaterials, such as zero-dimensional fullerenes, one-dimensional carbon nanotubes, and three-dimensional graphite. Many excellent experiments have demonstrated graphene as an ideal platform for fundamental studies and a wonder material with superior material properties.[5-7] Recently, research in 2D materials have gone beyond graphene with new atomically thin materials being synthesized and explored, among which semiconducting transition metal dichalcogenides (TMDC), which have a common chemical formula  $MX_2$  (M=Mo, W; S=S, Se, and Te), have received intense scientific attentions. While monolayer graphene is a zero-gap material, semiconducting TMCD possesses a band gap of 1  $\sim$  2 eV depending on the actual composition, and shows interesting electronic, optical, and valleytronic properties.[8] Therefore, graphene and the semiconducting TMDC are usually viewed as the metal and semiconductor building blocks in the family of 2D materials.

This chapter makes an introduction to both materials on topics including the crystal and electronic band structures, as well as some of the novel physics and potential applications.

### 1.1 Graphene

#### 1.1.1 Lattice structure

Monolayer graphene consists of a layer of carbon atoms that are arranged in a hexagonal lattice plane. Within the lattice plane, the bonds between two nearest-neighbor carbon atoms are formed from  $sp^2$  hybrid orbitals. When multiple monolayer graphene sheets are stacked through van der Waals interactions, they form one of the most common carbon materials, i.e. graphite.

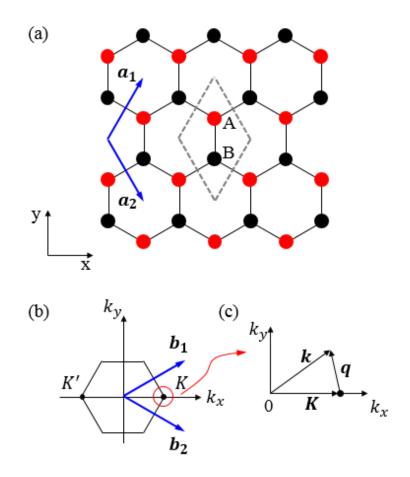

Figure 1-1. Schematics of (a) lattice structure of monolayer graphene, (b) Brillouin zone, and (c) k-space near the K or K' point.

Figure 1-1(a) is a schematic drawing of the lattice structure for a single-layer graphene. There are two sublattices, represented by the red and black symbols, and they are labeled as A and B carbon sites. There are two carbon atoms in each unit cell. The nearest-neighbor carbon-carbon bond length is  $a_{CC} = 1.42$  Å.  $a_1$  and  $a_2$  are the unit cell vectors and are given by

$$a_1 = \left(\frac{a}{2}, \frac{\sqrt{3}a}{2}\right), \quad a_2 = \left(\frac{a}{2}, -\frac{\sqrt{3}a}{2}\right)$$

(1.1)

where  $a = |a_1| = |a_2| = \sqrt{3}a_{CC}$  is the graphene lattice constant.

The corresponding reciprocal lattice vectors  $b_1$  and  $b_2$  are given by

$$\boldsymbol{b_1} = \left(\frac{2\pi}{a}, \frac{2\pi}{\sqrt{3}a}\right), \qquad \boldsymbol{b_2} = \left(\frac{2\pi}{a}, -\frac{2\pi}{\sqrt{3}a}\right) \tag{1.2}$$

Figure 1-1(b) plots the hexagonal Brillouin zone of monolayer graphene based on the two reciprocal lattice vectors. While there are six corners in the Brillouin zone, only two of them are nonequivalent and they are labeled as K and K' points. Their coordinates in the k-space are

$$K = \left(\frac{4\pi}{3a}, 0\right), \qquad K' = \left(-\frac{4\pi}{3a}, 0\right) \tag{1.3}$$

As will be discussed next, it is the unusual electronic band structure at the six corners of the Brillouin zone that makes graphene an amazing material.

#### 1.1.2 Electronic band structure

The electronic band structure of monolayer graphene  $E(\mathbf{k})$  is deduced from tight-binding approximation by considering one  $2p_z$  orbital from the two carbon atoms in one unit cell. An analytical expression of  $E(\mathbf{k})$  can be obtained by solving a secular equation

$$det(H_1 - ES_1) = 0 (1.4)$$

where  $H_1$  and  $S_1$  are the transfer and overlap integral matrices, respectively.  $E(\mathbf{k})$  is then given by

$$E_{\pm}(\mathbf{k}) = \frac{\epsilon_{2p} \pm \gamma_0 |f(\mathbf{k})|}{1 \mp s_0 |f(\mathbf{k})|}$$

(1.5)

$$f(\mathbf{k}) = e^{ik_y a/\sqrt{3}} + 2e^{-ik_y a/2\sqrt{3}}\cos(k_x a/2)$$

(1.6)

Here  $E_+$  and  $E_-$  represent the two energy bands above and below the Fermi level, respectively.  $E_+$  is also known as  $\pi^*$  band and  $E_-$  as  $\pi$  band.  $\epsilon_{2p}$  is energy of the  $2p_z$  orbital,  $\gamma_0$  and  $s_0$  are the nearest-neighbor transfer and overlap integrals, respectively.  $f(\mathbf{k})$  describes the hopping between A and B atoms and serves as an indicator of the coupling strength between the two sublattices. Exactly at the K and K' points,  $f(\mathbf{k}) = 0$ , indicating there is no coupling between the two sublattices.

Around the K(K') point, as shown in Fig. 1-1(c), the k vector can be expresses as

$$\mathbf{k} = \mathbf{K} + \mathbf{q} \tag{1.7}$$

where q is a small vector measured from the K(K') point. Substituting Eq. (1.7) into Eqs. (1.5) and (1.6), the energy dispersion relation around the K(K') can be expressed as

$$E_{\pm}(\mathbf{q}) - \epsilon_{2p} \approx \pm \hbar |\mathbf{q}| v_F \tag{1.8}$$

and

$$v_F = \frac{\sqrt{3}\gamma_0 a}{2\hbar} \tag{1.9}$$

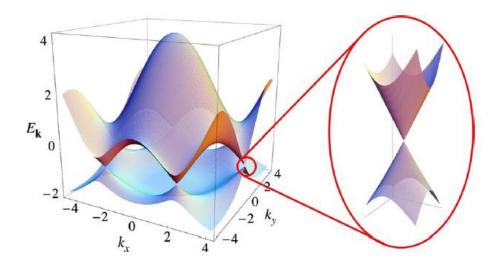

is the Fermi velocity, whose value is experimentally determined to be  $1.0 \sim 1.1 \times 10^6$  m/s in the linear dispersion regime.[9] Because Eq. (1.8) takes the same form of massless Dirac equation, the K(K') point is also known as the Dirac point. Figure 1-2 shows a calculated 3D representation of the electronic band structure and the linear dispersion near the K(K') point.

Figure 1-2. Electronic band structure of monolayer graphene. Adapted from Fig. 3 of Ref. [9]

## 1.1.3 Novel physics and potential applications

Over the past decade, graphene has been demonstrated as a unique two-dimensional electron gas system (2DEGs) where novel physics have been theoretically predicted and/or experimentally observed, such as half integer quantum hall effect (QHE)[3, 10], Klein tunneling[11], quantum spin hall effect[12], spin polarized edge states[13], etc.

Besides being an ideal material for fundamental research, graphene also shows great potential in a variety of applications due to its excellent electronic, optical, thermal, and mechanical properties. Graphene is a superior conductor with extremely high carrier mobility (e.g., exceeding  $2 \times 10^5$  cm<sup>2</sup>/Vs at room temperature[6]) and ability of sustaining ultrahigh current density (on the order of  $10^8$  A/cm<sup>2</sup>[14]). It has a high optical transmittance for visible lights with an absorptance of 2.3% per layer[15]. With a room-temperature thermal conductivity of ~ 5,000 W/mK[16], graphene is the most thermally conductive material up to date. Graphene also shows superior mechanical strength with a Young's modulus of 1 tesla pascals[17], which is the strongest material ever measured. Besides these intrinsic properties, graphene can also be

chemically functionalized to extend its application potentials, such as through hydrogenation[18], fluorination[19-21], etc.

The application potential of graphene has been demonstrated in many areas including electronics, optics, optoelectronics, etc. A common graphene-based electronic structure involves using graphene as the conduction channel in field effect transistors (FETs). So far, various functions have been realized by integrating graphene FETs, such as radio frequency transistors[22], biosensors[23], etc. Due to its excellent electrical, optical and mechanical properties, graphene has been demonstrated as an ideal material for flexible and transparent electrodes[24], which is very promising in replacing the currently widely used indium tin oxide (ITO)[25]. When graphene is functionalized with fluorine atoms, i.e. fluorographene, the original sp<sup>2</sup> carbon-carbon bonds transform into sp<sup>3</sup> hybridizations. This opens up a large band gap (~ 3.8 eV[26]) in fluorographene, which is now the world's thinnest insulating material[27].

## 1.2 Semiconducting transition metal dichalcogenides (TMDC)

#### 1.2.1 Lattice structure

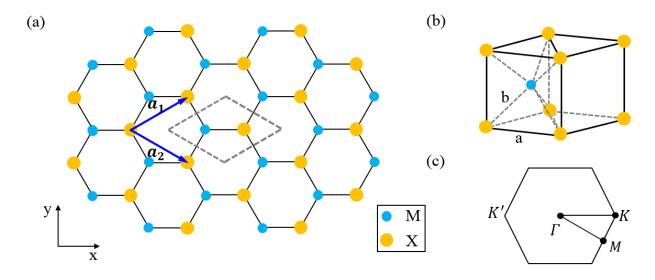

Transition metal dichalcogenides (TMDC) is another class of layered materials with strong covalent intra-layer bonds and weak inter-layer van der Waals interactions. It has the chemical formula MX<sub>2</sub>, where M is the transition metal W and Mo, and X is the group-IV chalcogenides S, Se, and Te. Monolayer MX<sub>2</sub> consists of an M layer sandwiched between two X layers. Figure 1-3(a) is a top view schematics of the monolayer lattice structure exhibiting a hexagonal pattern. Here, the top and bottom layer X atoms overlap at the same position. Each primitive unit cell contains one M atom and two X atoms as is outlined by the dashed grey lines.

Figure 1-3. Schematics of (a) lattice structure, (b) unit cell, and (c) Brillouin zone of monolayer MX<sub>2</sub>.

A three-dimensional (3D) view of the unit cell is shown by Fig. 1-3(b) where the M and X atoms are arranged in a trigonal prism coordination. *a* is the in-plane lattice constant. b is the bond length between the nearest-neighbor M and X atoms.

$a_1$  and  $a_2$  are the unit cell vectors and are given by

$$a_1 = \left(\frac{\sqrt{3}a}{2}, \frac{a}{2}\right), \qquad a_2 = \left(\frac{\sqrt{3}a}{2}, -\frac{a}{2}\right)$$

(1.10)

where  $|a_1| = |a_2| = a$  is the in-plane lattice constant.

The corresponding reciprocal lattice vectors  $\boldsymbol{b_1}$  and  $\boldsymbol{b_2}$  are then given by

$$\boldsymbol{b_1} = \left(\frac{2\pi}{\sqrt{3}a}, \frac{2\pi}{a}\right), \qquad \boldsymbol{b_2} = \left(\frac{2\pi}{\sqrt{3a}}, -\frac{2\pi}{a}\right) \tag{1.11}$$

Same as graphene, the Brillouin zone of monolayer  $MX_2$  is also hexagonal with two inequivalent K and K' points. When multiple layers are stacked to form 3D crystals, the bulk property can be quite different depending on the stacking orders and coordination of the transition metal atoms. There are three polytypes: a hexagonal 2H form, a rhombohedral 3R

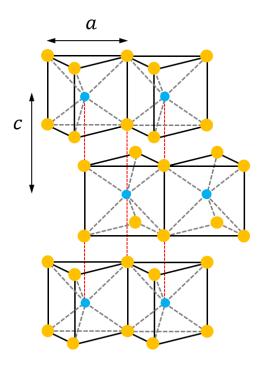

form, and a 1T form.[28] The stacking order of the 2H-phase is shown in Figure 1-4, where one unit cell consists of two monolayers.

Figure 1-4. Schematics of 2H-TMDC structure.

In this dissertation, our work on the TMDC material are based on crystals with the 2H structures.

#### 1.2.2 Electronic band structure

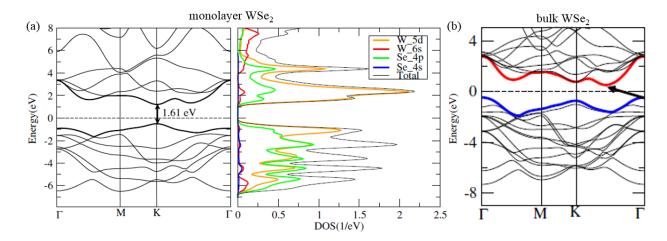

The electronic band structures of monolayer (1H) and 2H-bulk TMDC have been systematically studied by Kumar *et al.*[29] using first principles calculation. For monolayer TMDC, the energy bands that are close to the Fermi level are primarily formed by the metal d orbitals. For example, Figure 1-5(a) shows a calculated electronic band structure and the corresponding partial and total density of states (DoS) of monolayer WSe<sub>2</sub> from Ref. [29].

Energy states close to the Fermi level are predominantly contributed by the W\_5d orbital states, while the Se orbital states only make up a small portion of the total energy states.

Figure 1-5. (a) Electronic band structure and total and partial density of states of monolayer WSe<sub>2</sub>. Adapted from Fig. 7 of Ref. [29]. (b) Electronic band structure of bulk WSe<sub>2</sub>. Adapted from Fig. 13 of Ref. [29].

In the monolayer limit,  $MX_2$  band gap is direct with the conduction and valence band extrema appear at the K(K') point, as shown by the monolayer  $WSe_2$  example in Fig.1-5(a). As the layer number increases, the band gap becomes indirect due to inter-layer interactions.[29] The conduction band minimum is shifted to somewhere between the  $\Gamma$  and K points, while the valence band maximum is found at the  $\Gamma$  point, as shown in Fig. 1-5(b). Table 1-2 lists the band gaps of different  $MX_2$  for both monolayer and 2H-bulk forms. Gap sizes from theoretical calculations are labeled with (cal.), and the experimentally measured ones are labeled with (exp.).

| Table 1-1 Experimental | and theoretical band | gap sizes of monola | yer and 2H-bulk TMDC. |

|------------------------|----------------------|---------------------|-----------------------|

|                        |                      |                     |                       |

| TMDC     | $E_{g,1L}\left( eV\right)$  | $E_{g,bulk}$ (eV)           |

|----------|-----------------------------|-----------------------------|

| $MoS_2$  | 1.8 <sup>[30]</sup> (exp.)  | 1.23 <sup>[31]</sup> (exp.) |

|          | 1.78 <sup>[32]</sup> (cal.) | $1.29^{[33]}$ (exp.)        |

| $MoSe_2$ | 1.49 <sup>[32]</sup> (cal.) | $1.09^{[31]}$ (exp.)        |

|          |                             | $1.1^{[33]}$ (exp.)         |

| $MoTe_2$ | 1.13 <sup>[32]</sup> (cal.) | $1.0^{[33]}$ (exp.)         |

| $WS_2$   | 1.93 <sup>[32]</sup> (cal.) | $1.35^{[33]}$ (exp.)        |

| $WSe_2$  | 1.61 <sup>[29]</sup> (cal.) | $1.20^{[33]}$ (exp.)        |

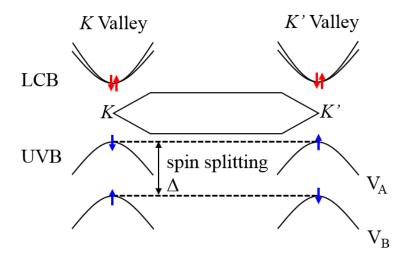

Due to a strong spin-orbit coupling of the heavy transition metal atoms, there are splitting in both the valence and conduction bands of monolayer TMDC.[29, 34] The conduction band splitting is in the meV range, while that of the valence band is in general a few hundred meV, e.g. 0.148 eV (MoS<sub>2</sub>), 0.430 eV(MoSe<sub>2</sub>), 0.430 eV(WS<sub>2</sub>), and 0.466 eV(WSe<sub>2</sub>).[35]

Figure 1-6. Valence band splitting and coupling between the spin and valley degrees of freedom in monolayer TMDC.

Another important property of monolayer TMDC is the coupling between spin and valley degrees of freedom. Due to the valence band splitting and inversion symmetry breaking, energy states at these two valleys are no longer the same even though they occupy the same energy levels.[36] Hence, the spin distribution at the K and K valleys are opposite, as is schematically shown in Fig. 1-6.

With these interesting features, TMDC has become an important 2D material for fundamental research and potential applications, which will be discussed next.

#### 1.2.3 Novel physics and potential applications

Many interesting physics in the TMDC systems are associated with their spin and valley properties. Valley-dependent optical selection rules have been theoretically proposed in monolayer MoS<sub>2</sub> and other MX<sub>2</sub> monolayers.[36] Control of valley polarizations, i.e. selective population of one valley, has been experimentally realized in monolayer MoS<sub>2</sub> through optical pumping with circularly polarized light.[37, 38] Using the same method, an anomalous Hall effect, i.e. valley Hall effect, is observed in monolayer MoS<sub>2</sub> transistors where the sign of Hall voltage depends on the helicity of excitation light, which determines the valley polarization.[38] It has also been predicted in Ref. [36] that the Berry-phase-driven spin Hall effect coexists with the valley Hall effect in monolayer MX<sub>2</sub> systems for both electrons and holes.

Besides being an excellent laboratory for the exploration of interesting and novel physics, TMDC has also shown great application potentials in electronics, optoelectronics, and spin-valleytronics. Large current on/off ratio exceeding  $10^7$  has been demonstrated in monolayer MoS<sub>2</sub> transistors[39], and a further increase to >  $10^{10}$  is predicted.[40] Electronic circuits with logic operation functions have been demonstrated based on mono- and bilayer MoS<sub>2</sub>.[41, 42]

Utilizing the visible-range direct bandgap property, monolayer TMDC has been demonstrated as a promising material in photovoltaics and photodetectors.[43, 44] Another advantage of the TMDC is its potential as a thermoelectric material with enhanced figure-of-merit. An ultralow cross-plane thermal conductivity (~ 0.05 W/mK) has been reported in disordered thin WSe<sub>2</sub> films.[45] With proper engineering to enhance the Seebeck coefficient and electrical conductivity, TMDC-based thermoelectric materials with superior performance may be realized in the future.

## Chapter 2

## The synthesis and characterization of graphene

Graphene has demonstrated itself as a 'miracle material' in both scientific research and potential applications due to its excellent electrical, thermal, optical and mechanical properties.[5, 6, 15] Monolayer graphene was first extracted from bulk graphite crystals into a free-standing form using a mechanical exfoliation technique in 2004.[1] Ever since then, this technique has been widely used in laboratories to produce graphene sheets with the highest quality. However, the lateral sizes of these graphene sheets are usually limited to a few micron to a few tens of microns, while the location of their appearance is random. Such inconvenience hardly poses a problem for laboratory research, but becomes a serious issue for future industrial applications. In this respect, chemical vapor deposition (CVD) has been demonstrated to be promising for graphene production in a large-scale and cost-effective way.[24] This technique involves using transition metal films, such as Cu, Ni, Ru, Pt, Co, Pd, and Re, as the growth substrates for graphene formation.[46-52] During a typical CVD process, hydrocarbon precursors are decomposed at the transition metal surface into carbon radicals in a hot reactor. These carbon radicals then arrange themselves into hexagonal patterns and form graphene sheets of various thickness. A third way of synthesizing graphene is through the sublimating of Si atoms at SiC wafer surface.[53]

This chapter focuses on the CVD synthesis of graphene on copper and electrical tests of graphene field effect transistors (GFETs). It first makes an introduction to two characterization techniques, i.e. Raman spectroscopy and scanning electron microscopy (SEM), which are commonly used in characterizing graphene (Section 2.1). Then, in section 2.2, we discuss three CVD methods used in graphene synthesis and the suppression of multilayer growth. Section 2.3

describes GFET fabrication procedures. Electrical test results of the GFETs are discussed in Section 2.4.

## 2.1 Graphene characterizations

Raman spectroscopy is widely used in graphene studies providing important information, such as defects density[54, 55], layer number identification[56], and electron-phonon interactions[57, 58]. SEM is another useful tool for direct imaging of the surface morphology of the synthesized the graphene. In this dissertation, we primarily use SEM to find MLG coverage percentage to correlate with different growth conditions to achieve the goal of complete MLG suppression.

## 2.1.1 Raman spectroscopy

## 2.1.1a Raman scattering theory

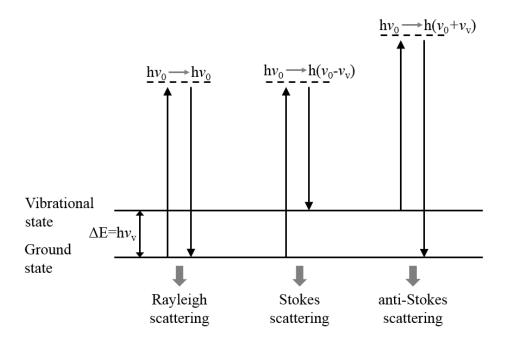

Raman scattering describes an interaction process where incident photons are inelastically scattered from an atom or a molecule through the interaction with an excitation, such as phonons, molecular energy level transitions, etc.[59] After the atom or molecule absorbs the incident photon energy  $h\nu_0$ , they are first excited to a virtual energy state and then relaxes back to the initial energy state through emitting another photon.

Figure 2-1. Schematic diagram of Raman scattering process.

Depending on the energy difference  $\Delta E$  between the scattered and incident photons, there are three scattering processes, as shown in Fig. 2-1.  $hv_v$  is the energy difference between the first vibrational state and the ground state. If the initial or final energy state of the atom or molecule does not couple to other excitation energy besides the incident photons, the emitted photon will have the same energy as the incident photon. This process is called Rayleigh scattering and is the dominant process. The Stokes and anti-Stokes scattering processes result in the emitted photons with energies lower and higher than the incident photon energy  $hv_0$  by  $hv_v$ , respectively. However, their occurrence probability is very low (approximately 1 in 10 million) except in the case of resonant scattering, where the incident photon energy matches an electronic transition energy. In graphene, the resonant Raman scattering condition is met, which generates strong Raman response as will discussed next.

# 2.1.1b Raman spectra of graphene

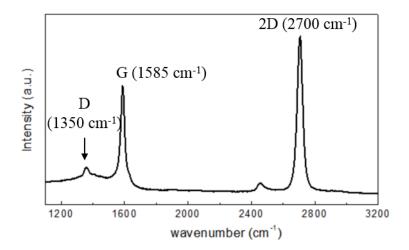

Figure 2-2. Raman spectrum from a defective monolayer graphene. 514 nm excitation laser line.

Raman spectroscopy probes the graphene phonon modes via inelastic scattering of the incident laser excitation.[60] In a Raman spectrum of pristine monolayer graphene, there are two prominent peaks around 1585 cm<sup>-1</sup> and 2700 cm<sup>-1</sup>, which are called G band and 2D band, respectively. When defects are present in the lattice, a disorder-induced D-band appears around 1350 cm<sup>-1</sup>. Figure 2-2 is a Raman spectrum from a defective CVD graphene monolayer showing all three Raman peaks.

Figure 2-3. (a) DFT calculated phonon dispersion of monolayer graphene. Adapted from Fig. 1 of Ref. [61] (b) Resonant scattering process for G-band (left), 2D-band (middle), and D-band in graphene Raman.

The origin of the three Raman-active modes can be well understood by correlating their peak positions with the phonon dispersion of monolayer graphene. Since each unit cell has two carbon atoms, monolayer graphene possesses three acoustic phonon modes and three optical phonon modes. Figure 2-3(a) shows the phonon dispersion of graphene from density-function theory (DFT) calculation.[61] The Raman scattering process for the G-band is a first-order scattering process involving the zone-center degenerate phonons ( $\Gamma$ ) iTO and iLO. iTO is the in-plane optical phonon mode and iLO is the in-plane longitudinal optical phonon mode. The 2D-band, on the other hand, arises from a second-order scattering process involving two iTO phonons near the K point. The D-band also originates from a second-order scattering process but can only be

activated in the presence of at least one defect point. Figure 2-3(b) illustrates the first and second order scattering processes associated with the three graphene Raman modes.

Figure 2-4.  $I_D/I_G$  vs the average spacing  $L_D$  for monolayer graphene. Adapted from Fig. 4 of Ref. [55].

Raman spectroscopy has also been demonstrated as an important and useful tool in the studies defects in graphene.[54, 55, 62] A Raman-based quantitative model for the density of defects in graphene has been reported by Lucchese *et al.*[55]. They correlated the Raman intensity ratio between the defect-inducted D-band and the G-band, i.e.  $I_D/I_G$ , with the average defect spacing  $L_D$  obtained from scanning tunneling microscopy (STM) measurements, and found that  $I_D/I_G$  does not follow a monotonic relation with  $L_D$  but rather reaches a maximum value around  $L_D$  =4 nm, which corresponds to a defect density ~ 0.2%. In the less defective regime, i.e.  $L_D$  >4 nm,  $I_D/I_G$  increases in a non-linear fashion as  $L_D$  decreases. After crossing the saddle point, it then sharply decreases to below 1. Figure 2-4 shows the  $I_D/I_G$  vs  $L_D$  relation from Ref. [55].

# 2.1.2 Scanning electron microscopy (SEM) of graphene

Figure 2-5. A typical SEM image of graphene on copper grown by a standard CVD method. Common features such as graphene folds, wrinkles, and multilayer islands, as well as copper terraces are indicated by arrows.

SEM is employed in characterizing the surface morphology of as-grown CVD graphene on copper substrates. Through quantitative analysis on the SEM images using an open-source software ImageJ, we are able to determine the MLG size and coverage in as-grown graphene films. Figure 2-5 is an SEM image of graphene on Cu showing features such as multilayer graphene islands, graphene folds and wrinkles, as well as copper terraces, in addition to the monolayer background. The large regions with different contrast correspond to different copper domains.

## 2.2 Graphene synthesis via low-pressure chemical vapor deposition (LPCVD)

Among the many transition metal substrates, polycrystalline Ni and Cu films are the two most studied for CVD graphene synthesis.[46, 63, 64] Due to a large difference in carbon

solubility, graphene growth on Ni and Cu occur via two different mechanisms. Because of a large carbon solubility and high carbon diffusivity[65], graphene growth on Ni happens in two steps, i.e. precipitation and segregation of carbon atoms.[64] First, hydrocarbon molecules are decomposed at the Ni surface followed by diffusion into the body and forming Ni-C solid solutions. This step happens at high temperatures and is usually controlled to last for a short time such that the amount of carbon atoms stored in Ni is limited. Then, as the reactor temperature decreases, carbon atoms segregate from Ni due to a reducing solubility and form graphene films. The thickness of the graphene film is shown to depend on the cooling rate. It has been demonstrated in Ref. [64] that large-area graphene films of several layers can be synthesized with a controlled cooling rate. Figure 2-6 shows an optical image of CVD graphene transferred to SiO<sub>2</sub>/Si substrates after synthesis using Ni.[66] The light pink areas are monolayer graphene as pointed by the red arrow. The additional irregular-shaped patches with colors varying from light purple to gold are thick graphene patches.

Figure 2-6. An optical image of CVD graphene transferred on SiO2/Si substrates from Ni. Adapted from Fig. 4 of Ref. [66]

Contrary to nickel and other transition metals, copper has a much lower carbon solubility which enables large-area monolayer graphene growth.[46] During the CVD process, hydrocarbon precursors decompose into carbon radicals at Cu surface in a hot reactor. Instead of diffusing into the Cu body, the majority of the atoms directly form small monolayer graphene islands at different nucleation sites and then expand laterally. At the same time, a small portion of the carbon atoms get stored at defect sites in the Cu substrate via diffusion where the carbon solubility is large. As soon as all individual monolayer islands coalesce and fully cover the catalytic Cu surface, decomposition of the hydrocarbon molecules ceases. Without further supply of carbon atoms, the growth process stops even if there is still ample hydrocarbon molecules. Hence, the growth of graphene on Cu is a self-limiting process and the majority of the graphene film is monolayer. In a standard CVD process, the hydrocarbon precursor is supplied continuously. In this dissertation, we refer to it as continuous-CVD. As already shown by the SEM image in Fig. 2-5, the synthesized monolayer graphene film is usually accompanied by multilayer islands at random locations. The multilayer formation mechanism is related to the additional carbon atoms stored at Cu defect sites and will be discussed in detail later in this section. One of the initial motivations behind the work discussed in this chapter is to achieve multilayer-free graphene growth for the consideration of using CVD graphene for real applications, which have a high requirement on the uniformity of the synthesized graphene films.

#### 2.2.1 Continuous-CVD synthesis

In our group, we first adopt a low-pressure continuous-CVD method using copper as the growth substrate following Ref. [46]. Figure 2-7(a) shows a schematic drawing of the CVD system. We use are thin copper foils with thickness of 25 µm and purity of 99.8% that are

purchased from Alfa Aesar. Methane and Ar/ $H_2$  (9:1) are used as precursors. Their flow rates are controlled by the mass flow controllers (MFC) located at the upstream of the system. A mechanical pump at the downstream can reduce the reactor pressure to  $\sim 1T$  during growth. Figure 2-7(b) shows the real CVD system.

Figure 2-7. (a) Schematics and (b) an optical picture of the CVD system used in our laboratory.

Before starting the growth process, a small piece of copper foil is soaked in diluted hydrochloric acid (1 parts 97% HCl and 3 parts DI water) for ~ 5 min. This step removes native oxide layer from the Cu surface. Then it is rinsed with large amount of DI water to wash off any acid residues before blown dry by nitrogen gas. The cleaned Cu foil piece is placed on a quartz slide and inserted into the quartz tube inside a horizontal furnace (HZS 12/600, Carbolite). The

CVD system is first pumped for  $\sim 10$  minutes to evacuate air inside all the tubes. Then the pump is turned off and the system is filled back with Ar/H<sub>2</sub> to atmospheric pressure. After that, the exhaust valve is opened to allow a continuous flow Ar/H<sub>2</sub> through the growth tube at 200 s.c.c.m. for at least 30 minutes to purge out any residual air.

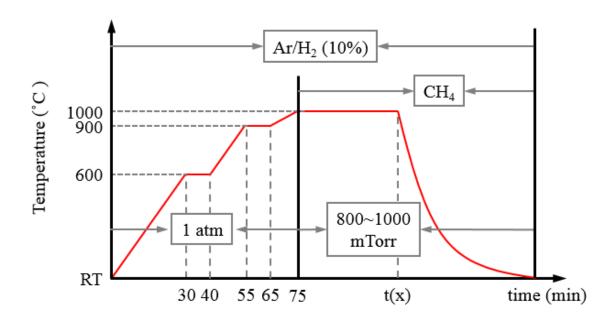

Figure 2-8 shows the growth profile in our LPCVD process. Ar/H<sub>2</sub> flows through the growth tube continuously and constantly during the whole CVD process. Before reaching 1000  $\,^{\circ}$ C, the pump is at off state and system pressure is at 1 atm. The furnace temperature is first raised to 600  $\,^{\circ}$ C at a rate of 20  $\,^{\circ}$ C/min followed by a 10 min dwell time. This step further removes the native copper oxide through a redox reaction with hydrogen. Then the temperature is elevated to 900  $\,^{\circ}$ C at a rate of 20  $\,^{\circ}$ C/min followed by a 10 min dwell time. This is the copper foil annealing stage. After that, the reactor temperature is raised to the growth temperature of 1000  $\,^{\circ}$ C, at a rate of 10  $\,^{\circ}$ C/min. Once the reactor is at 1000  $\,^{\circ}$ C, the pump is turned on to bring pressure in the growth tube to 800  $\,^{\circ}$  1000 mTorr. Then methane is introduced for graphene growth. The growth stage at 1000  $\,^{\circ}$ C usually last for 10  $\,^{\circ}$ 20 minutes depending on the flow rate of methane. After that, the furnace temperature is gradually reduced back to room temperature.

Figure 2-8. Growth profile of the tube furnace during the CVD process. The system pressure and flows of methane and  $Ar/H_2(10\%)$  are also indicated on the diagram.

In our early growth recipe, we use the continuous CVD method with the methane flow rate varies between 5 s.c.c.m. to 30 s.c.c.m. We find a total methane flow of 200 s.c.c. is sufficient for graphene to fully cover the Cu surface in our CVD system. Figure 2-9 shows two SEM images of graphene on copper for methane flow of 100 s.c.c. (10 s.c.c.m. flow rate for 10 min, left) and 200 s.c.c. (10 s.c.c.m flow rate for 20 min, right). As can be seen, 100 s.c.c. methane flow is not enough for individual graphene islands to coalesce and leaves gaps in between. At 200 s.c.c. methane flow, a continuous film is formed. Because graphene growth on Cu is a self-limiting process, there is no need to flow methane more than 200 s.c.c.

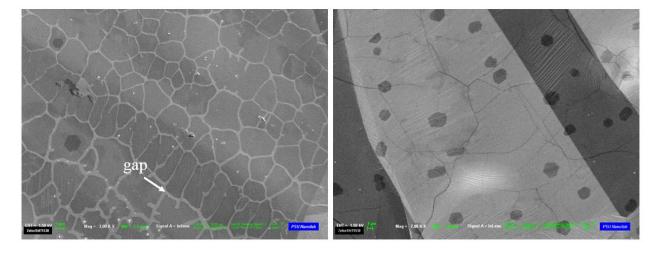

Figure 2-9. SEM images of graphene on copper from continuous CVD growth with total methane flow of 100 s.c.c. (left) and 200 s.c.c. (right). The white arrow points at copper surface that is not covered by graphene yet.

In general, we find graphene synthesized from the continuous-CVD method usually contains about 10% ~ 20% multilayers. Raman spectra from the monolayer regions show small D-band

intensity with the  $I_D/I_G$  ratio less than 0.1. Carrier mobilities of graphene field effect transistors show a distribution centered around 5,000 cm<sup>2</sup>/Vs.[67]

## 2.2.2 Pulsed-CVD synthesis

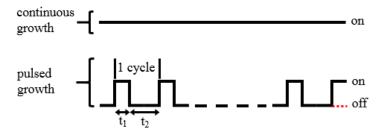

Later, the dual role of hydrogen in CVD graphene synthesis is revealed by Vlassiouk et al.[68]. According to their experimental study, hydrogen serves as an activator of the surface bound carbon and as an etching reagent for carbon atoms. This motivates us into modifying the continuous growth recipe to take advantage the etching ability of  $H_2$  at high temperature, i.e.  $1000 \, \text{C}$ , to prevent the occurrence of the multilayer patches. Inspired by another paper by  $Han \, et \, al.$ [69], where they show the suppression of MLG patches can be achieved by introducing the methane in a pulsed fashion, i.e. pulsed-CVD method, we experiment with this idea and work out a recipe for our own CVD system.

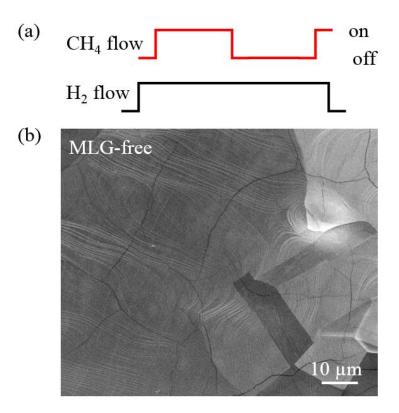

Figure 2-10. Schematics of methane flow during the graphene growth process at 1000 °C for continuous (top) and pulsed (bottom) CVD methods.

First, we define the growth parameters for the pulsed-CVD method. Figure 2-10 schematically compares the flow patterns of the methane for the two methods. Unlike the continuous-CVD growth, methane is alternatively turned on and off during the pulsed-CVD process. Hence, we break the whole growth process at 1000 °C into a number of cycles. Each

cycle contains a  $t_1$  growth period followed by a  $t_2$  etching period. During the growth period, methane is applied at a flow rate of  $f_{CH4}$ . Then it is cut off in the following etching period leaving only Ar/H<sub>2</sub> flowing though the reactor. It should be noted that the Ar/H<sub>2</sub>(10%) is constantly applied during the growth process for both continuous- and pulsed-CVD methods. Its flow rate is denoted by  $f_{H2}$ . As will be shown later, we obtain complete suppression of the multilayer islands over a large area (hundreds of  $\mu$ m in lateral sizes) with optimized growth conditions, i.e.  $f_{CH4}$ ,  $f_{H2}$ ,  $t_1$  and  $t_2$ .

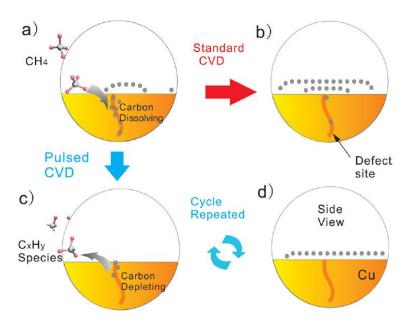

Figure 2-11 Schematic illustrations of a)&b) the formation of multilayer graphene patches near a defect site on copper during the continuous-CVD process, and c)&d) suppression mechanism in the pulsed-CVD process. Adapted from Fig. 4 of Ref. [69].

Next, we discuss the origin of the MLG formation and the suppression mechanism in pulsed-CVD method following Ref. [69]. Because the polycrystalline copper substrates (99.8% purity) always contain certain amount of defects that have large carbon solubility, carbon atoms can

diffuse into these defect sites, as shown in Fig. 2-11(a). Then, in the continuous CVD process, these carbon atoms diffuse to the copper surface and form additional graphene patches as the reactor cools down (Fig. 2-11(b)). As discussed above, H<sub>2</sub> can react with carbon atoms such as those at the growth front of the graphene lattice and the ones stored at the copper defect sites, through forming C<sub>x</sub>H<sub>y</sub> species. Hence, by cutting off the methane for a short period of time in cycles, the H<sub>2</sub> molecules can deplete the carbon atoms in the defect sites. If the depletion is complete, there should be no more carbon supplies for the multilayer to form. This is illustrated in Fig. 2-11(c) and (d). Another way to suppress the MLG growth is to use ultra-high purity (99.999%) copper substrates.

Figure 2-12. SEM images from three pulsed-CVD graphene synthesizes. From (a) to (c), the growth condition  $t_1/t_2$  and MLG coverage are: 2min/2min, 15.7%; 1min/2min, 8.2%; and 0.5min/2.5min, 3.7%, respectively. For all three growth, methane and Ar/H<sub>2</sub>(10%) flow rates are fixed at t  $f_{CH4} = 10$  s.c.c.m. and  $f_{H2} = 200$  s.c.c.m. with a total amount 200. s.c.c. methane.

As there are four growth parameters that can be controlled during the pulsed-CVD process, we first show results from growth tests where the methane and Ar/H<sub>2</sub>(10%) flow rates are fixed at  $f_{\text{CH4}} = 10\,$  s.c.c.m. and  $f_{\text{H2}} = 200\,$  s.c.c.m.. Figure 2-12 show typical SEM images from three combination of  $t_1/t_2$ , i.e. (a) 2min/2min, (b) 1min/2min, and (c) 0.5min/2min. Statistical results of

the MLG average sizes and coverage percentages from multiple SEM images for each growth are: (a)  $(0.62\pm0.58)~\mu\text{m}^2$ ,  $(15.7\pm2.4)~\%$ ; (b)  $(0.79\pm0.68)~\mu\text{m}^2$ ,  $(8.2\pm2.1)~\%$ ; (c)  $(0.37\pm0.37)~\mu\text{m}^2$ ,  $(3.7\pm1.1)~\%$ . The total amount of methane applied is kept at 200 s.c.c. for all three growth conditions. As can be seen from the graphs and statistical results, both the average size and coverage of MLG patches progressively reduce with shorter  $t_1$  and longer  $t_2$ . We also experiment with the flow rate of methane by keeping  $t_1$  and  $t_2$  constant.

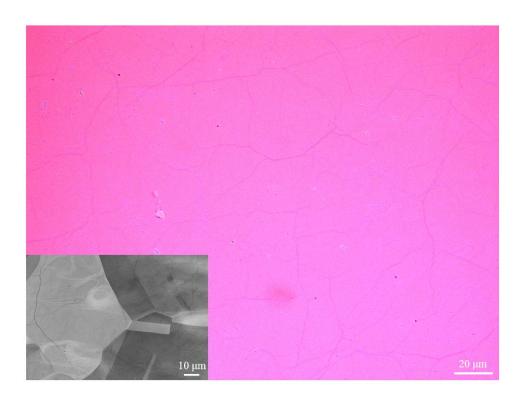

Figure 2-13. An optical image of pulsed-CVD graphene transferred on  $SiO_2(290nm)/Si$  substrate. No MLG patches are visually observed. Inset shows an SEM image of graphene from the same growth batch.

After many trials, we are able to produce MLG-free monolayer graphene films using a growth recipe of  $t_1 = 30$  s,  $t_1 = 60$  s,  $f_{\text{CH4}} = 5$  s.c.c.m.,  $f_{\text{H2}} = 200$  s.c.c.m. and 80 growth cycles. Figure 2-13 is an optical image of the pulse-CVD graphene transferred onto

$SiO_2(290nm)/Si$  substrate. The color contrast of the graphene film is uniform and no MLG patches are found visually. The size of the graphene film is 180  $\mu m \times 250 \mu m$ . The inset shows an SEM image of graphene on copper from the same growth batch at a smaller scale. No MLG patches are observed either.