## The Pennsylvania State University

The Graduate School

College of Engineering

# PHYSICS, FABRICATION AND CHARACTERIZATION OF III-V MULTI-GATE FETS FOR LOW POWER ELECTRONICS

A Dissertation in

**Electrical Engineering**

by

Arun V. Thathachary

© 2015 Arun V. Thathachary

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

December 2015

The dissertation of Arun V. Thathachary was reviewed and approved\* by the following:

Suman Datta

Professor of Electrical Engineering and Computer Science

Dissertation Advisor

Co-Chair of Committee

Theresa Mayer Professor of Electrical Engineering and Computer Science Associate Dean for research and innovation, College of Engineering Co-Chair of Committee

Nitin Samarth Professor of Physics George A. and Margaret M. Downsbrough Department Head

Weihua Guan Assistant Professor of Electrical Engineering and Computer Science

Roman Engel-Herbert Assistant Professor of Materials Science and Engineering

Kultegin Aydin Professor of Electrical Engineering and Computer Science Department Head

<sup>\*</sup>Signatures are on file in the Graduate School

#### **ABSTRACT**

With transistor technology close to its limits for power constrained scaling and the simultaneous emergence of mobile devices as the dominant driver for new scaling, a pathway to significant reduction in transistor operating voltage to 0.5V or lower is urgently sought. This however implies a fundamental paradigm shift away from mature Silicon technology. III-V compound semiconductors hold great promise in this regard due to their vastly superior electron transport properties making them prime candidates to replace Silicon in the n-channel transistor. Among the plethora of binary and ternary compounds available in the III-V space, In<sub>x</sub>Ga<sub>1-x</sub>As alloys have attracted significant interest due to their excellent electron mobility, ideally placed bandgap and mature growth technology. Simultaneously, electrostatic control mandates multigate transistor designs such as the FinFET at extremely scaled nodes.

This dissertation describes the experimental realization of III-V FinFETs incorporating In<sub>x</sub>Ga<sub>1-x</sub>As heterostructure channels for high performance, low power logic applications. The chapters that follow present experimental demonstrations, simulations and analysis on the following aspects (a) motivation and key figures of merit driving material selection and design; (b) dielectric integration schemes for high-k metal-gate stack (HKMG) realization on In<sub>x</sub>Ga<sub>1-x</sub>As, including surface clean and passivation techniques developed for high quality interfaces; (c) novel techniques for transport (mobility) characterization in nanoscale multi-gate FET architectures with experimental demonstration on In<sub>0.7</sub>Ga<sub>0.3</sub>As nanowires; (d) Indium composition and quantum confined channel design for In<sub>x</sub>Ga<sub>1-x</sub>As FinFETs and (e) InAs heterostructure designs for high performance FinFETs. Each chapter also contains detailed benchmarking of results against state of the art demonstrations in Silicon and III-V material systems. The dissertation concludes by assessing the feasibility of In<sub>x</sub>Ga<sub>1-x</sub>As FinFET devices as n-channel Silicon replacement for low power logic technology scaling.

# TABLE OF CONTENTS

| List of Figures                                                                                                              | vi   |

|------------------------------------------------------------------------------------------------------------------------------|------|

| List of Tables                                                                                                               | xii  |

| Acknowledgements                                                                                                             | xiii |

| Chapter 1 In <sub>x</sub> Ga <sub>1-x</sub> As channels in the context of low power logic technology                         | 1    |

| I. Motivation                                                                                                                | 3    |

| Current in nanoscale MOSFETs                                                                                                 |      |

| Quantum capacitance bottleneck                                                                                               |      |

| II. Layer structure design and characterization                                                                              |      |

| III. FinFET device architecture                                                                                              |      |

| Chapter 2 High-k dielectric gate stack integration on In <sub>x</sub> Ga <sub>1-x</sub> As                                   | 13   |

| Chapter 2 Tright is dicretaine gate states integration on m <sub>x</sub> out- <sub>x</sub> , is                              |      |

| I. MOS capacitor fabrication and characterization: Thermal ALD                                                               | 14   |

| II. Low power plasma surface clean and passivation                                                                           |      |

| Bi-layer vs. single layer dielectric gate stack                                                                              |      |

| III. Conclusions                                                                                                             |      |

|                                                                                                                              |      |

| Chapter 3 Characterization of electronic transport in nanoscale multi-gate FETs                                              | 27   |

| I. Introduction                                                                                                              | 27   |

| II. Test structure design and fabrication                                                                                    |      |

| Device metrology and material characterization                                                                               |      |

| III. Results and discussion                                                                                                  |      |

| Device characterization                                                                                                      |      |

| Equivalent circuit model and mobility extraction                                                                             |      |

| Validation of measured results                                                                                               |      |

| Identifying the cause for mobility degradation                                                                               |      |

| IV. Ballistic transport in nanoscale $In_xGa_{1-x}As$ structures                                                             |      |

| V. Conclusions                                                                                                               |      |

| Chapter 4 Channel architecture and composition engineering for high performance In <sub>x</sub> Ga <sub>1-x</sub> As FinFETs |      |

| I. Channel architecture, device design and fabrication                                                                       | 47   |

| II. Results and discussion                                                                                                   |      |

| Multi-fin split CV measurements                                                                                              |      |

| Long channel FinFET performance                                                                                              |      |

|                                                                                                                              |      |

| Short channel FinFET performance                                                                                             |      |

| Benchmarking                                                                                                                 |      |

| Projected short channel performance                                                                                          |      |

| III. Conclusions                                                                                                             | 61   |

| Chapter 5 High performance InAs heterostructure FinFETs    | 63 |

|------------------------------------------------------------|----|

| I. Motivation                                              | 63 |

| II. Device design and fabrication                          |    |

| Bandstructure effects                                      |    |

| III. Results and discussion                                |    |

| Long channel performance                                   |    |

| Short channel benchmarking                                 |    |

| IV. Conclusions                                            |    |

| Chapter 6 Conclusions and future work                      | 75 |

| I. Summary and conclusions                                 | 75 |

| Impact of confinement on transport : confined phonon modes | 80 |

| II. Future work: High aspect ratio InAs channel FinFETs    | 81 |

| Bibliography                                               | 86 |

| Appendix Process flow for III-V FinFET fabrication         | 96 |

| E-beam litho markers + S/D pads                            |    |

| Mesa isolation                                             |    |

| Gate recess etch                                           |    |

| Fin Definition                                             |    |

| Gate Stack: High-k deposition                              |    |

| Gate electrode definition                                  |    |

# LIST OF FIGURES

| Figure 1-1. Scaling trends of CPUs showing saturation in the clock frequency and an upper limit to power dissipation (source: [6])                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1-2. Schematic showing the potential performance gain from inserting high electron mobility III-V channel materials. Comparable drive currents may be achieved at 0.5V supply voltage.                                                                                   |

| Figure 1-3. Bulk electron and hole mobilities for III-V compound semiconductors plotted as a function of bandgap (from [3]). Ternary alloys of InGaAs have high electron mobility with a suitably high bandgap to enable scalable III-V logic technology4                       |

| Figure 1-4. Schematic representation of the top of the barrier injection model for nanoscale MOSFETs indicating the virtual source point                                                                                                                                        |

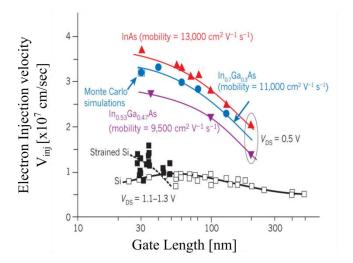

| Figure 1-5. Injection velocity as a function of gate length measured from planar III-V HEMT devices [4]                                                                                                                                                                         |

| Figure 1-6. Equivalent circuit representation of quantum effects in the inversion charge.  Low effective mass in III-V semiconductors results in more pronounced quantum effects.                                                                                               |

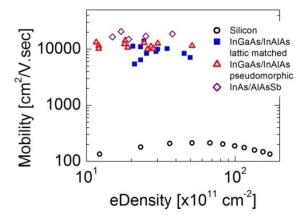

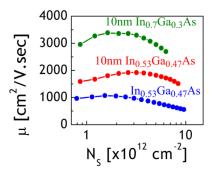

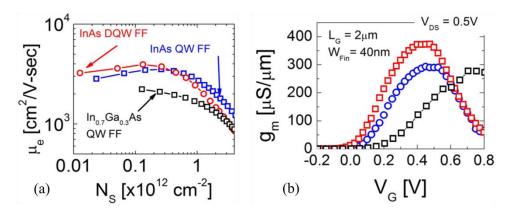

| Figure 1-7. Electron mobility μ versus sheet electron density n <sub>S</sub> in n-channel Si FETs and III-V QWFETs: Si MOSFETs, InGaAs/AlGaAs HFETs [12,13], lattice-matched InGaAs/InAlAs QWFETs [14,15], pseudomorphic InGaAs/InAlAs QWFETs [16,17], InAs/AlSb QWFETs [18,19] |

| Figure 1-8. Schematic showing generic layer structure of quantum well channels investigated in this work                                                                                                                                                                        |

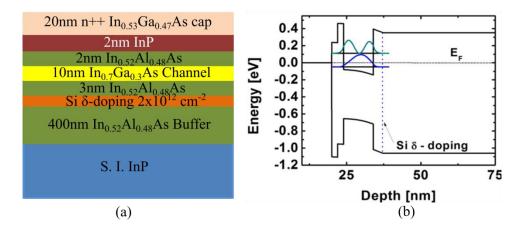

| Figure 1-9. (a) Device layer structure showing the remote $\delta$ -doping layer and (b) band diagram indicating the first two sub-bands and the Fermi level                                                                                                                    |

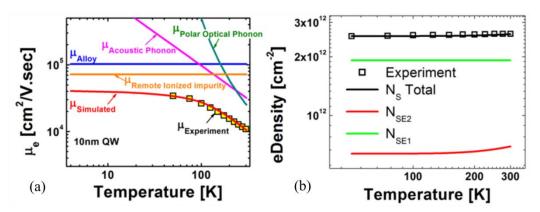

| Figure 1-10. (a) Hall mobility measured as a function of temperature (symbols). Solid lines show fit obtained using a relaxation time approximation based scattering analysis. (b) Carrier density contribution from the first two sub-bands                                    |

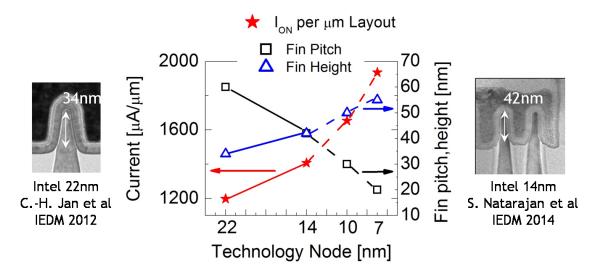

| Figure 1-11. Scaling trends of drive current, fin width and fin height from 22nm node onwards. Values for the 10 and 7nm nodes are projected assuming simplistic scaling by 0.7x in dimensions per generation                                                                   |

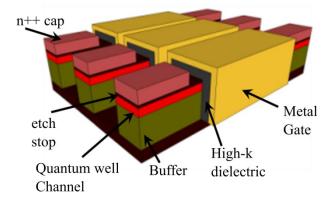

| Figure 1-12. Representative schematic showing the architecture of the quantum well FinFET devices fabricated in this work                                                                                                                                                       |

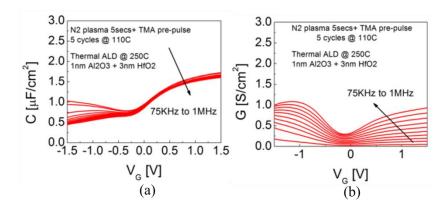

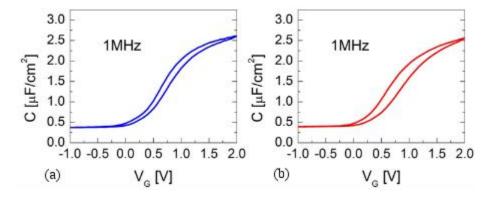

| Figure 2-1. Experimental measured capacitance (a) and conductance (b) data for a 1nm Al <sub>2</sub> O <sub>3</sub> /3nm HfO <sub>2</sub> stack grown by thermal ALD15                                                                                                          |

| Figure 2-2. Measured capacitance (a) and conductance (b) data shown for MOS capacitor with bi-layer gate stack and low temperature (110C) plasma nitride surface passivation                                                                                                                                                                                                                                                                                                                                                                                                                                                        | í        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

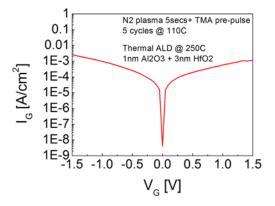

| Figure 2-3. Gate leakage measured for MOS capacitor shown in figure 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ,        |

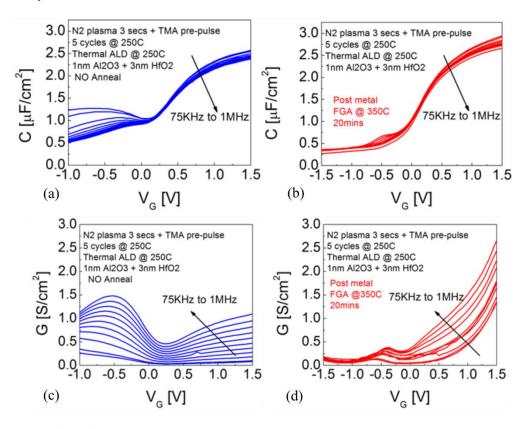

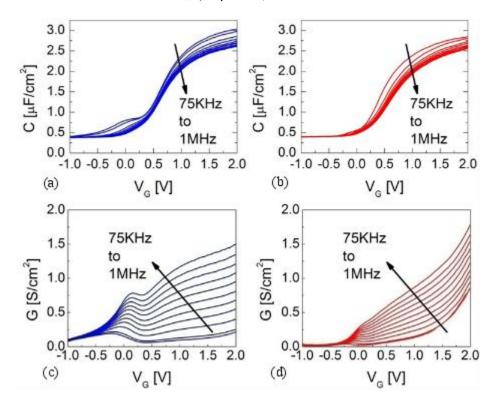

| Figure 2-4. Effect of FGA on bi-layer dielectric gate stack with high temperature plasma nitrogen clean and passivation. (a) and (b) show capacitance data before and after FGA while (c) and (d) show the corresponding conductance data                                                                                                                                                                                                                                                                                                                                                                                           | 3        |

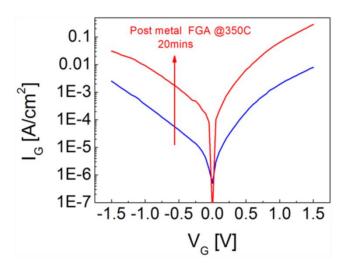

| Figure 2-5. Gate leakage comparison before and after FGA for bi-layer dielectric gate stack.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | )        |

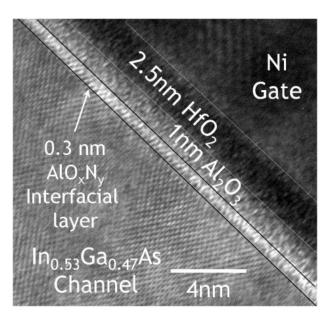

| Figure 2-6. Cross-section transmission electron micrograph of the bi-layer dielectric gate stack with 250°C plasma nitride surface passivation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )        |

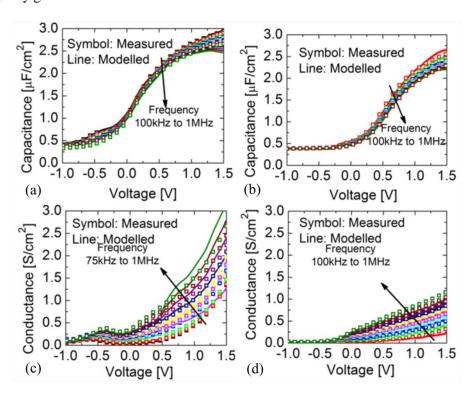

| Figure 2-7. (a) and (b) show measured capacitance data (symbols) while (c) and (d) show measured conductance data (symbols) for bi-layer 1nm Al <sub>2</sub> O <sub>3</sub> /3nm HfO <sub>2</sub> and 4nm HfO <sub>2</sub> only stacks. Solid lines indicate fit from equivalent circuit model                                                                                                                                                                                                                                                                                                                                      | L        |

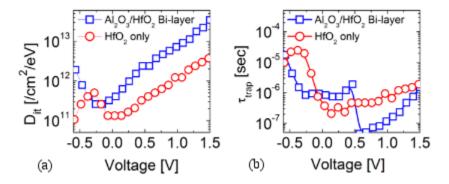

| Figure 2-8. (a) Extracted D <sub>IT</sub> profiles and (b) estimated trap time constant for bi-layer and HfO <sub>2</sub> only gate stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>.</u> |

| Figure 2-9. (a) and (b) show measured capacitance data for pre-gate metal and post-gate metal forming gas anneals. (c) and (d) show the corresponding conductance data.  Devices comprise of 4nm HfO <sub>2</sub> only gate stack with AlO <sub>x</sub> N <sub>y</sub> passivation                                                                                                                                                                                                                                                                                                                                                  | 3        |

| Figure 2-10. Measured hysteresis of (a) pre-gate metal and (b) post-gate metal FGA24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ļ        |

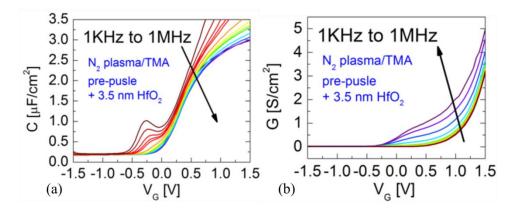

| Figure 2-11. (a) Capacitance and (b) conductance data for 3.5nm HfO <sub>2</sub> only gate stack with 250°C plasma nitride surface passivation and FGA with frequency sweep down to 1KHz.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1        |

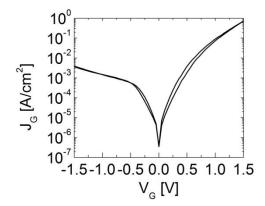

| Figure 2-12. Gate leakage current measured for 3.5nm HfO <sub>2</sub> only gate stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | į        |

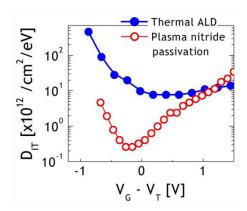

| Figure 2-13. Extracted DIT profiles for thermal ALD and plasma nitride surface passivated gate stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | į        |

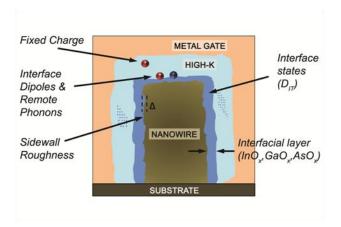

| Figure 3-1. Schematic representation of various extrinsic scattering mechanisms that affect transport in multi-gate NWFET structures on III-V substrates                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ;        |

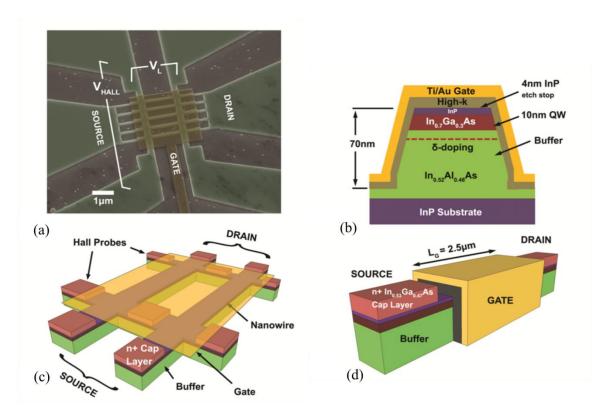

| Figure 3-2. (a) SEM of multi-gate, In <sub>0.7</sub> Ga <sub>0.3</sub> As NWFET with an array of five NWs of width 40nm. Additional probe electrodes are integrated to form a Hall bridge structure. Hall voltage (V <sub>H</sub> ) and longitudinal (V <sub>L</sub> ) voltage are measured as shown. (b) Schematic cross-section of the NW showing the layer structure of the substrate. (c) Schematic showing two representative NWs and the structure of the probe underneath the gate. The heavily doped n+ cap layer is retained on the probe electrode in the regions between the NWs and (d) perspective view of single NW31 |          |

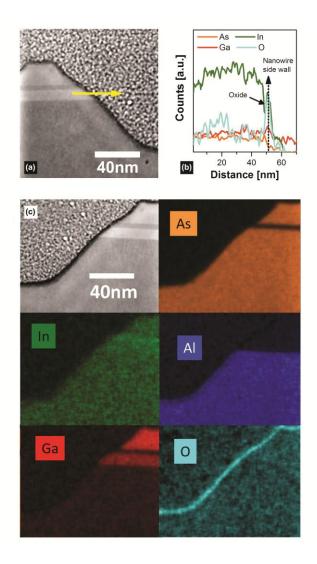

| Figure 3-3. Characterization of the top down patterned nanowire subsequent to plasma etching: (a) STEM image indicating location of EELS line scan and (b) EELS line scan showing possible formation of indium oxide interfacial layer. (c) EELS elemental map of NW cross-section confirming that top-down etch yields high quality, defect-free NW structure, while also highlighting the formation of native oxide layer on side walls.                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

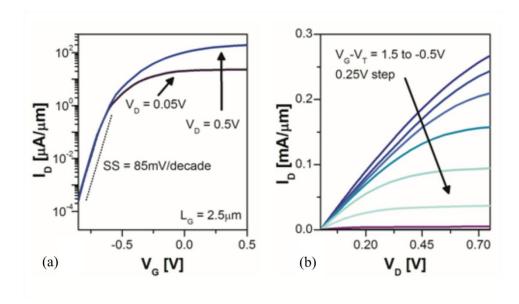

| Figure 3-4. (a) Transfer characteristics $(I_D-V_G)$ of the multi-gate NWFET based Hall structure, with NW width of 40nm, showing good sub-threshold behavior. (b) Output characteristics $(I_D-V_D)$ of the same device                                                                                                                                                                                                                                                                                                                  |

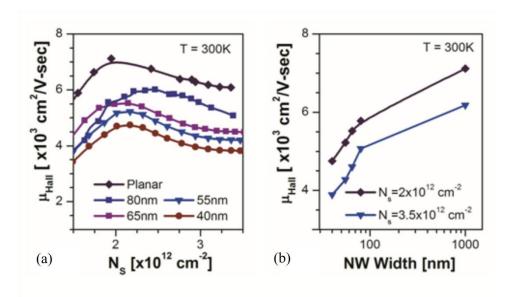

| Figure 3-5. Experimentally measured Hall electron mobility for multi-gate NWFET of Figure 3-2 as a function of carrier concentration for different NW widths. (b) Mobility shows a monotonic roll-off with reducing NW dimensions. Peak mobility is observed at a carrier concentration of 2x10 <sup>12</sup> cm <sup>-2</sup> for all NW widths                                                                                                                                                                                          |

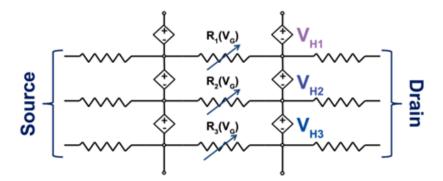

| Figure 3-6. Equivalent circuit model for interpretation of measured results                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

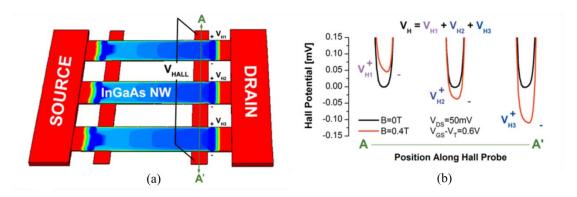

| Figure 3-7. Improving measurement accuracy: (a) simulated electrostatic potential through the NW array. (b) Simulated Hall potential profile plotted as a function of position along the Hall probe. The results show that each NW contributes a small Hall potential to the total V <sub>H</sub> , which is measured across the device                                                                                                                                                                                                   |

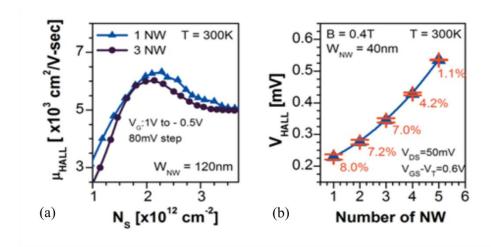

| Figure 3-8. (a) Measured Hall mobility as a function of carrier concentration showing excellent agreement between single NW and NW array device. Results confirm the equivalent circuit based interpretation of Fig. 3-6. (b) Simulated Hall voltage as a function of NW number showing an increase in measured Hall voltage with number of NWs. Due to the averaging effect of the array, the error of the measured Hall voltage reduces as number of NWs increases. Error is less than 1% when the number of NWs is increased beyond 5. |

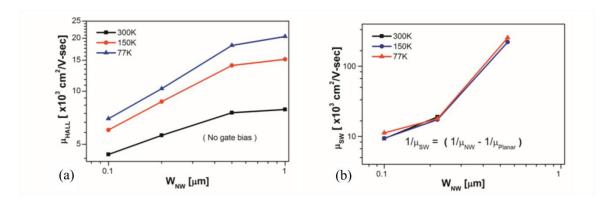

| Figure 3-9. (a) Temperature dependent, un-gated Hall measurements showing mobility degradation as the InGaAs quantum well is patterned into NWs with width reducing from 1 µm (planar) down to 100nm. (b) Additional scattering extracted using Mathiessen's rule. This component is found to be independent of temperature clearly indicating that the scattering arises from roughness due to the side walls                                                                                                                            |

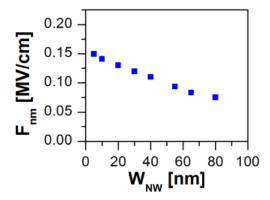

| Figure 3-10. Calculated overlap integral values $F_{nm}$ as a function of NW width at $N_S = 2x10^{12}$ . The effective electric field from the potential fluctuations of the sidewall roughness increases monotonically with reducing NW width                                                                                                                                                                                                                                                                                           |

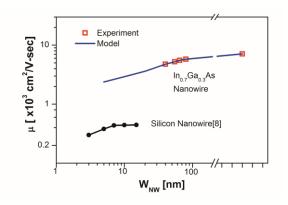

| Figure 3-11. Projection of mobility for 10nm NW width. The side-wall roughness scattering model is calibrated to the measured data. The gated Hall measurement results clearly indicate a mobility roll-off with decreasing nanowire width.  Comparison of mobility between InGaAs and silicon NWs indicates over 10× higher mobility for InGaAs at a NW width of 10nm                                                                                                                                                                    |

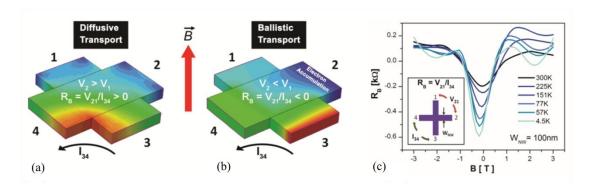

| Figure 3-12. (a) Simulated potential distribution profile for a Hall cross structure in the diffusive regime. As current flows from contact 3 to 4 a positive bend resistance is                                                                                                                                                                                                                                                                                                                                                          |

|      | measured. (b) Potential distribution in the ballistic regime. Electrons from contact 4 travel past the junction without scattering and start accumulating in contact 2 reversing the polarity of $V_{21}$ giving $R_B < 0$ . (c) Measured bend resistance as a function of magnetic field and temperature for $In_{0.7}Ga_{0.3}As$ NW based Hall cross structure. $R_B < 0$ is observed at room temperature confirming ballistic transport at room temperature. | 46 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

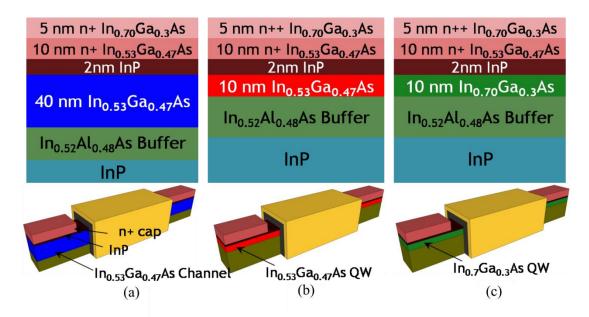

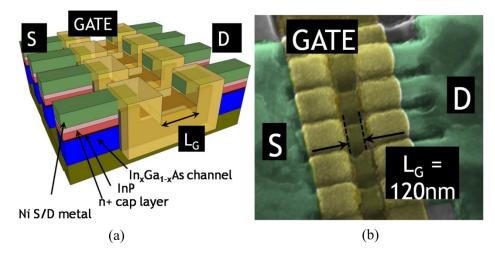

| Fig  | ure 4-1. Schematic showing the layer structure for devices A,B and C investigated in this work. all substrates are finally patterned into FinFET structures as shown in the bottom panel.                                                                                                                                                                                                                                                                       | 49 |

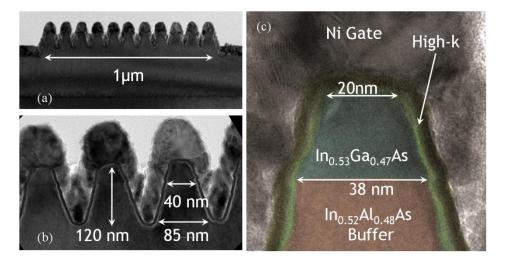

| Figi | ure 4-2. Cross-section transmission electron micrographs (TEM) showing (a) tight fin pitch with 10 fins/µm layout width (b) magnified image showing critical dimensions achieved with side wall slope of 75° (c) magnified false color image highlighting the high-k dielectric and metal gate.                                                                                                                                                                 | 49 |

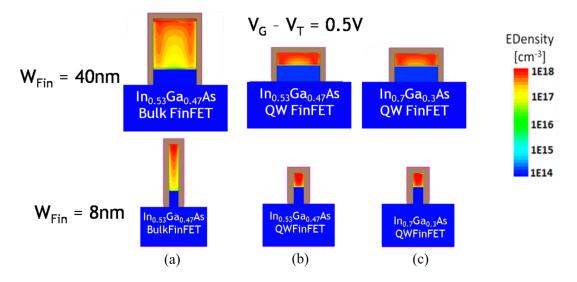

| Figi | ure 4-3. Two dimensional Schrodinger-Poisson simulations show inherent volume inversion in the thin quantum well devices. Similar volume inversion densities in the thick InGaAs channel is achieved only at a highly scaled fin width of 8nm                                                                                                                                                                                                                   | 50 |

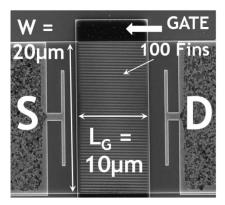

| Figi | ure 4-4. SEM of a long channel multi-fin device for measuring split-CV fin capacitance.                                                                                                                                                                                                                                                                                                                                                                         | 51 |

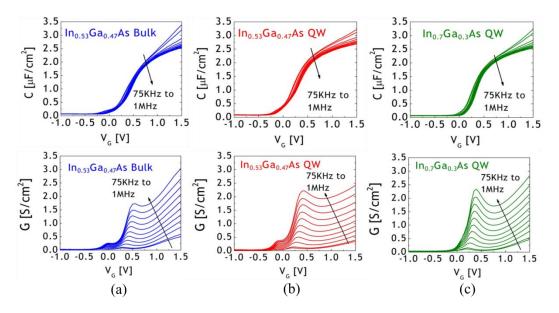

| Figi | ure 4-5. Measured multi-fin split CV capacitance (top panel) and conductance (bottom panel) for the thick In <sub>0.53</sub> Ga <sub>0.47</sub> As, thin In <sub>0.53</sub> Ga <sub>0.47</sub> As and In <sub>0.7</sub> Ga <sub>0.3</sub> As quantum wells in (a), (b) and (c) respectively.                                                                                                                                                                    | 52 |

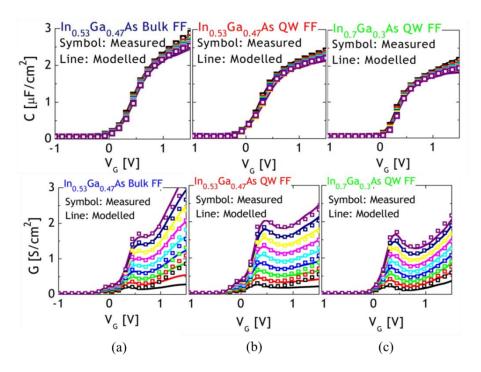

| Figi | ure 4-6. Fit obtained between experimental capacitance and conductance data modeled using the equivalent circuit method                                                                                                                                                                                                                                                                                                                                         | 52 |

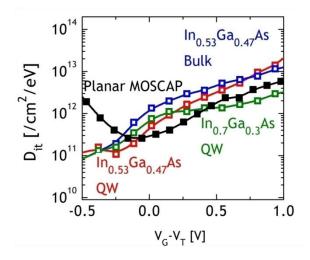

| Figi | ure 4-7. Extracted interface state density (D <sub>it</sub> ) profile for the three multi-fin devices is shown and compared to planar MOS capacitor D <sub>it</sub> profiles                                                                                                                                                                                                                                                                                    | 53 |

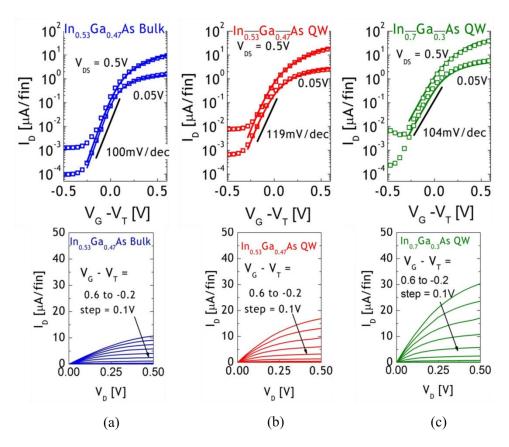

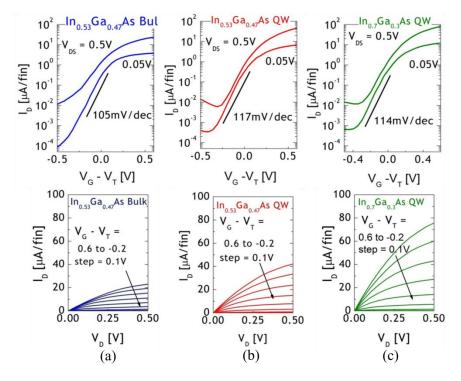

| Figi | ure 4-8. (a), (b) and (c) show measured long channel transfer characteristics (top panel) and output characteristics (bottom panel) for substrates A, B and C respectively.                                                                                                                                                                                                                                                                                     | 54 |

| Fig  | ure 4-9. Experimentally extracted field effect mobility for long channel FinFET devices                                                                                                                                                                                                                                                                                                                                                                         | 55 |

| Figi | ure 4-10. (a) Schematic showing the structure of the short channel multi-fin FET device. (b) Top view SEM of fabricated device                                                                                                                                                                                                                                                                                                                                  | 56 |

| Fig  | ure 4-11. (a), (b) and (c) show measured transfer characteristics (top panel) and output characteristics (bottom panel) for the substrates A, B and C respectively                                                                                                                                                                                                                                                                                              | 57 |

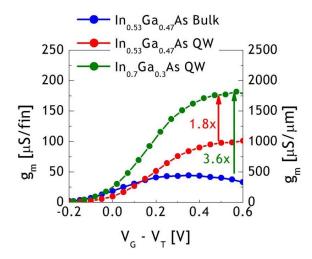

| Fig  | ure 4-12. Experimentally extracted transconductance (g <sub>m</sub> ) for the three short channel devices vs. gate overdrive.                                                                                                                                                                                                                                                                                                                                   | 58 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

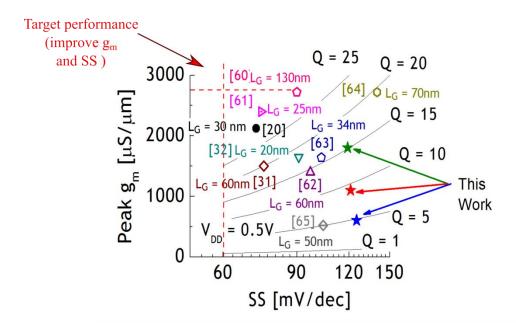

| Figure 4-13. Benchmarking plot showcasing the transconductance (g <sub>m</sub> ) for the three short channel devices as a function of sub-threshold slope (SS).                                                                                                              | 59 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

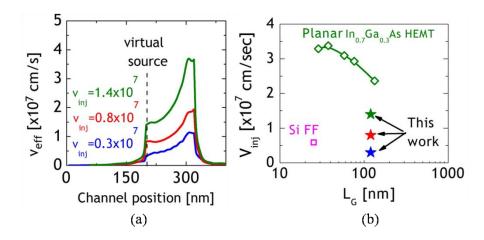

| Figure 4-14. (a) Velocity profiles along the channel for the three short channel devices extracted using calibrated TCAD simulations. (b) Benchmarking of the injection velocity against state of the art silicon and In <sub>0.7</sub> Ga <sub>0.3</sub> As HEMT devices[4] | 60 |

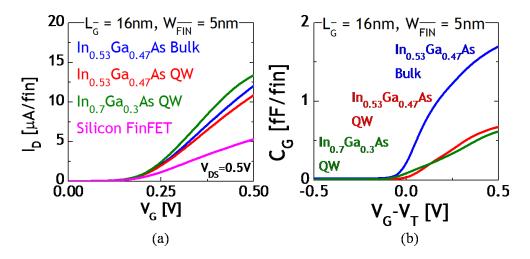

| Figure 4-15. Projected performance for 7nm node FinFET at 0.5V supply voltage showing (a) drive currents and capacitance per fin for the three substrates                                                                                                                    | 61 |

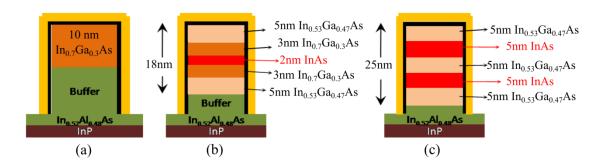

| Figure 5-1. Cross-section schematic of the three FinFET structures highlighting the single and dual InAs quantum wells.                                                                                                                                                      | 64 |

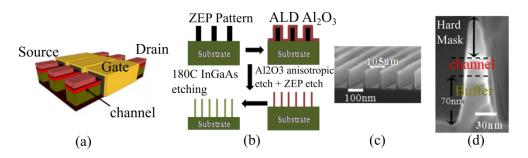

| Figure 5-2. (a) Schematic of fabricated FinFET devices (b) Process flow outlining the spacer technique for patterning fins (c) cross-section SEM of etched fins and (d) cross-section SEM of etched fin shown with residual hard mask                                        | 65 |

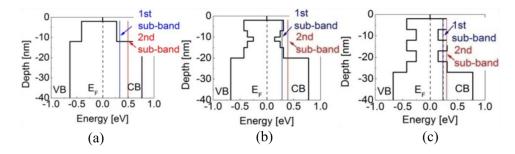

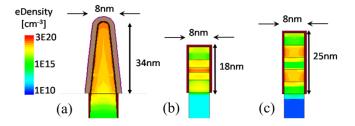

| Figure 5-3. One dimensional Schrodinger-Poisson simulations using nextnano showing reducing sub-band spacing going from the (a) InGaAs QW to the (b) single and (c) dual QW substrates.                                                                                      | 66 |

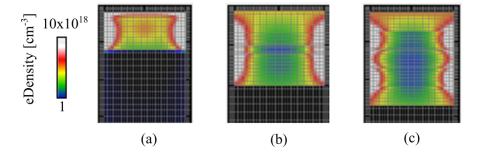

| Figure 5-4. Two dimensional Schrodinger-Poisson simulations using nextnano showing higher inversion charge concentration near the InAs regions in the single and dual quantum well structures.                                                                               | 66 |

| Table 5-1. Effective perimeter of FinFET devices based on weighted average of carrier distributions                                                                                                                                                                          | 67 |

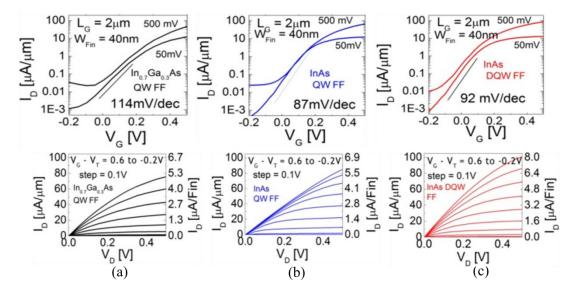

| Figure 5-5. Transfer characteristics (top panel) and output characteristics (bottom panel) are shown for FinFETs on the three substrates from figure 5-1 in column (a), (b) and (c) respectively.                                                                            | 68 |

| Figure 5-6. (a) Long channel FinFET mobility extracted using inverse modeling in Sentaurus TCAD after calibration to experimental long channel transfer characteristics. (b) Long channel FinFET transconductance.                                                           | 69 |

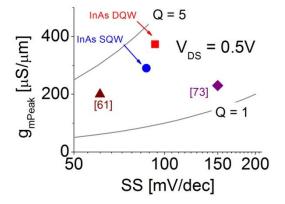

| Figure 5-7. Benchmarking of experimental long channel FinFET g <sub>m</sub> against published long channel In <sub>x</sub> Ga <sub>1-x</sub> As/InAs devices [61,73].                                                                                                        | 69 |

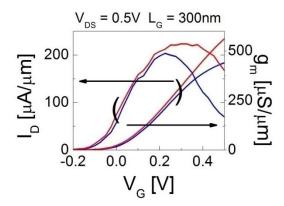

| Figure 5-8. Short channel ( $L_G = 300$ nm) transfer characteristics shown for single (blue solid line) and dual (red solid line) FinFET devices. Right axis shows corresponding transconductance.                                                                           | 70 |

| Figure 5-9. Fin cross-sections showing electron density profiles simulated at $V_G$ = 0.5V ( $I_{OFF}$ = 100nA/ $\mu$ m) for scaled 8nm devices, (a) Si FinFET (b) InAs single QW FinFET and (c) InAs DQW FinFET.                                                            | 71 |

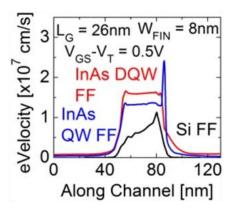

| Figure 5-10. Electron velocity profiles for FinFETs projected at 22nm node using Sentaurus TCAD. Transport parameters are calibrated to experimental short channel devices                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

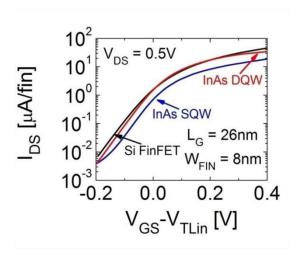

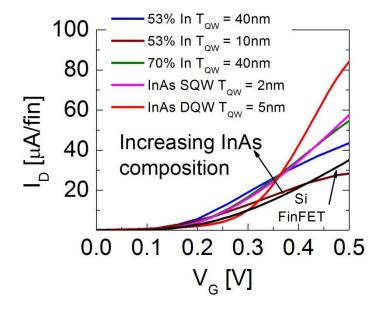

| Figure 5-11. Transfer characteristics (current per fin) of InAs SQW and DQW devices benchmarked against 22nm Si FinFET technology                                                                                                                                                                  |

| Table 5- 1 Benchmarking of projected short channel performance (at 22nm node) with state of the art 22nm silicon technology. InAs dual QW FinFET devices show promising on-current                                                                                                                 |

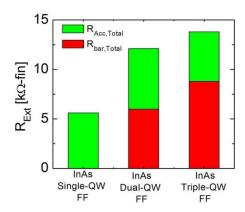

| Figure 6-1. External resistance for InAs QW FinFETs with raised source/drain architectures rises rapidly with stacking of InAs QW                                                                                                                                                                  |

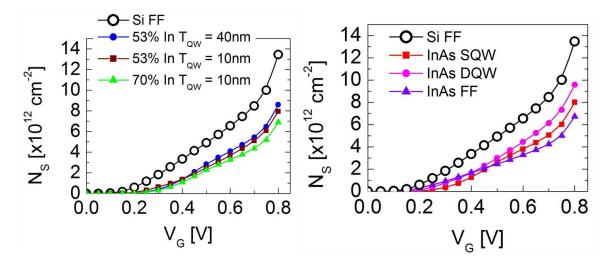

| Figure 6-2. Charge density estimated using two dimensional Poisson-Schrodinger simulations for different III-V architectures explored in this work. The higher DoS in silicon results in almost 2x higher charge.                                                                                  |

| Figure 6-3. TCAD simulation of scaled devices comparing projected performance with 22nm Silicon FinFETs [20]                                                                                                                                                                                       |

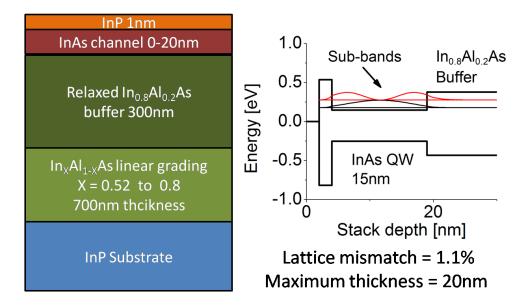

| Figure 6-4. Linear grading of In <sub>x</sub> Al <sub>1-x</sub> As buffer to accommodate thick pseudomorphic InAs channel (0-20nm). The lattice mismatch still limits maximum thickness in order to accommodate strain. Shown on the right is the corresponding band diagram82                     |

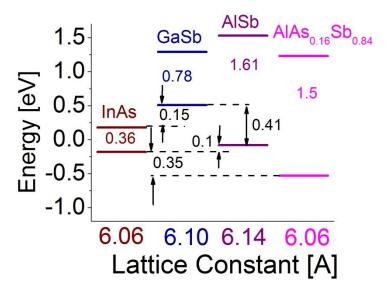

| Figure 6-5. Band gaps and alignment of various Sb based buffer layers relative to InAs83                                                                                                                                                                                                           |

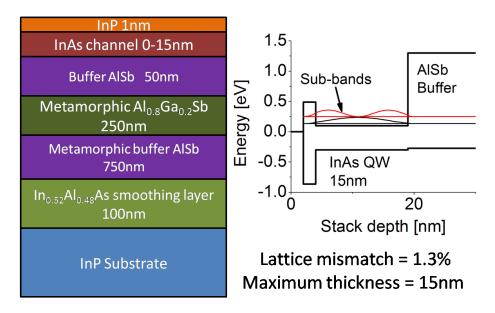

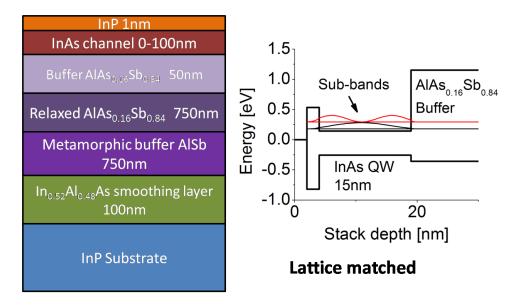

| Figure 6-6. A thick AlSb metamorphic buffer growth on InP/InAlAs can provide a closely lattice matched system to InAs along with large conduction band offsets required for electron confinement. Shown on the right is the corresponding band diagram                                             |

| Figure 6-7. Thick metamorphic AlSb growth followed by the growth of thick relaxed AlAsSb can provide a perfectly lattice matched buffer layer which also satisfies the criteria of large conduction band offset (good electron confinement). Shown on the right is the corresponding band diagram. |

# LIST OF TABLES

| Table 5- 1 Benchmarking of projected short channel performance (at 22nm node) with |    |

|------------------------------------------------------------------------------------|----|

| state of the art 22nm silicon technology. InAs dual QW FinFET devices show         |    |

| promising on-current.                                                              | 73 |

#### ACKNOWLEDGEMENTS

I am indebted to all the people who have made my graduate studies a great experience and this dissertation possible. I would like to express my heartfelt gratitude to all of them.

First I would like to express my sincere gratitude to my advisor Prof. Suman Datta for giving me the opportunity to work on compound semiconductor devices. His guidance and motivation have kept me on edge and ensured I continue to grow intellectually and personally. I am very grateful for the sense of responsibility and commitment he has instilled in me.

I am also grateful to our sponsor, Samsung Electronics Co. Ltd. for funding this dissertation work. I would like to thank our collaborators Mirco Cantoro, K. K Bhuwalka, Y-C Heo, S. Maeda and the entire team from Samsung Logic technology development for their technical inputs and the many fruitful discussions we have had through the course of this dissertation. I would also like to thank my committee members Dr. Theresa Mayer, Dr. Nitin Samarth, Dr. Roman Engel-Herbert and Dr. Weihua Guan for reading

I would like to convey my special thanks and appreciation to the staff in the nanofabrication facility at Penn State, especially Guy Lavallee, Chad Eichfeld, Michael Labella, Bill Drawl, Bangzhi Liu and Jaime Reish for their help with training me at the Penn State Nanofab, as well as technical discussions on device fabrication and extensive process development during the course of my doctoral study.

I sincerely thank the Department of Electrical Engineering in selecting me for the Melvin P. Bloom Memorial Outstanding Doctoral Research Award 2015. I again thank my advisor Prof. Suman Datta for nominating me for this award.

Special thanks to my colleague and collaborator on the Samsung projects, Nidhi Agrawal. Her support with extensive simulations and data extractions have made keeping pace with the project and this dissertation possible. I would also like to thank Mike Barth and Matt Hollander

for their support in the clean room and the characterization labs. The many long late hours we have spent together fabricating devices in the nanofab is something I will remember for a long time. I also thank Rahul Pandey for the many fruitful discussions we have had and the entire Datta group for a great graduate experience.

No graduate student can complete a dissertation without support and a life outside the lab. I am very grateful for the great group of friends I have had the good fortune of knowing especially Nidhi Agrawal, Kadappan, Vishesh, Vivek, Amruta and Divya. Their presence, support and encouragement have enriched me many folds personally and professionally. The many fun hours we spent together like family is something I will cherish forever.

Finally, I owe a debt I cannot repay to my family. I thank my parents, V. T. Ranganathan and Sowmithri Ranganathan, for always leading by example and raising me with a strong sense of love, integrity, courage and resilience. They prepared me for facing the trials and tribulations of life. I will always remember my father's encouraging words and advice when I needed it the most. His gentle wisdom will remain my guiding beacon. I am also grateful to my sister Supriya for her constant words of encouragement and support. Last but not least, I am eternally grateful to my mother who has always stood by me and believed in me. But for her untold sacrifices I would not have come this far in life. I dedicate this thesis to my family and to the loving memory of my father.

## Chapter 1

## In<sub>x</sub>Ga<sub>1-x</sub>As channels in the context of low power logic technology

The metal oxide semiconductor field effect transistor or MOSFET has remained the workhorse of the electronics industry due to its almost miraculous property of increased performance with shrinking size. This simple rule has led to the staggering success of Moore's law, now in its 50th year, and continues to propel the microelectronics industry forward while ushering the world into an era of ubiquitous computing.

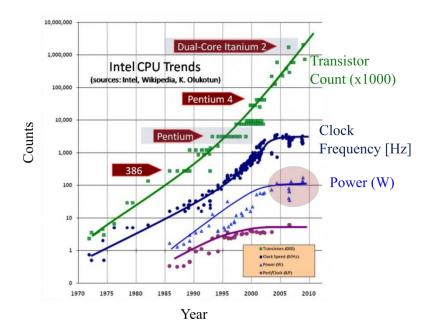

In the context of integrated circuits, the MOSFET is used as a switch where its primary function is to switch between two logic states, viz. "0" (OFF) and "1" (ON). Further, with the imperative to make them smaller, faster and cheaper, the primary metrics driving the design of this switch are the area (footprint), switching speed and the energy dissipated during the switching operation [1-5]. Additionally, current integrated circuits employ MOSFETs implemented in a complementary fashion with n and p-channel transistors (based on the mobile charge carrier type) to enable complementary MOS (CMOS) technology. With the progression of Moore's law, the MOSFET has followed a geometric scaling rule enabling exponential gains in performance with every new generation. Increasing transistor density per chip and rising frequencies of operation led to dramatic increase in performance. This however also resulted in considerably high power dissipation and current designs strive to limit the power at 100W and frequencies of 2-3GHz, as seen in figure 1-1. Thus integrated electronics entered an era of power constrained scaling.

Further, with consumer trends and commerce rapidly embracing mobile technology, the electronics industry is predominantly focused on mobile computing platforms, fueling the ever

increasing demand for ultra-low power computing technology. Development of this next generation low power technology will enable a plethora of new products such as ultra-small form

Figure 1-1. Scaling trends of CPUs showing saturation in the clock frequency and an upper limit to power dissipation (source: [6]).

factor tablets, more powerful smart phones and wearable computing devices that can interface to bio-sensors while potentially drawing power from energy harvesters. It is also critically important to emerging technologies such as the Internet of Things (IoT).

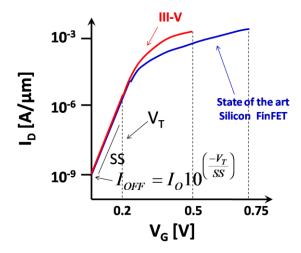

A key requirement to achieve power constrained scaling is to reduce the supply voltage as the dynamic power scales geometrically with supply voltage. This places several stringent and competing requirements on the performance metrics of the transistor such as high drive-current at reduced supply voltage, low leakage current ( $I_{OFF}$ ), high  $I_{ON}/I_{OFF}$  ratio and good sub-threshold slope with well controlled drain induced barrier lowering[2,3]. At reduced supply voltages silicon CMOS is limited by reduced drive currents. Enabling such low power integrated electronics therefore requires a new generation of nanoscale digital-logic transistors capable of operating at voltages of 500mV or lower; a very significant reduction from the present day values of close to 0.75V. One of the fundamental roadblocks preventing this is the non-scalability of threshold

voltage (V<sub>T</sub>) of the transistor as off-state leakage current trades off exponentially with V<sub>T</sub>, as seen in figure 1-2. Therefore implementing a considerable reduction in supply voltage requires a paradigm shift in the design approach of the transistor which has traditionally relied on mature Silicon technology. In this context, interest in group III-V compound semiconductors has grown rapidly within the last decade. These materials have higher electron mobilities as compared to silicon which can be exploited to provide a viable path to reduced supply voltage operation as shown in figure 1-2.

Figure 1-2. Schematic showing the potential performance gain from inserting high electron mobility III-V channel materials. Comparable drive currents may be achieved at 0.5V supply voltage.

#### I. Motivation

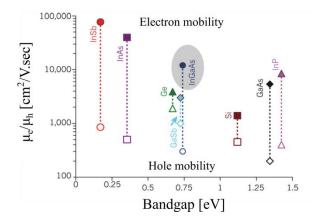

III-V semiconductors possess excellent transport properties in addition to spanning a wide range of bandgaps as seen in figure 1-3. It is further possible to engineer the properties of the material by creating ternary and even quaternary alloys of various binary compounds. Ternary  $In_xGa_{1-x}As$  alloys with varying percentage of Indium have high electron mobility making them attractive replacements for the n-channel Silicon transistor. Additionally, a suitable bandgap between 0.35eV (InAs) and 0.75eV (lattice matched  $In_{0.53}Ga_{0.47}As/InP$ ) may be achieved. A

reasonable bandgap is critical to scaling the technology [3]. Large bandgaps prevent threshold voltage from scaling due to the absence of suitable work function metals and simultaneously, very small bandgaps can be detrimental to off-state leakage arising from both over the barrier (thermionic) and band-to-band tunneling currents. Room temperature bulk electron mobilities in excess of 10,000 cm<sup>2</sup>/V.sec have been measured for high quality lattice matched InGaAs substrates[4].

Figure 1-3. Bulk electron and hole mobilities for III-V compound semiconductors plotted as a function of bandgap (from [3]). Ternary alloys of InGaAs have high electron mobility with a suitably high bandgap to enable scalable III-V logic technology.

#### **Current in nanoscale MOSFETs**

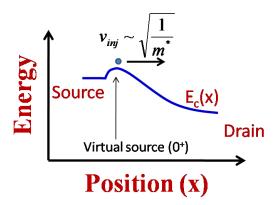

For nanoscale MOSFETs, significant fraction of the current can propagate in a ballistic fashion from source to drain. At extremely scaled dimensions, a simplistic one dimensional scattering based transport model given by the Lundstrom-Natori model [7-8], captures the essential physics as depicted in figure 1-4. In this model the current is controlled by the inversion charge density and effective injection velocity at the top of the barrier near the source-channel junction, referred to as the virtual source.

Figure 1-4. Schematic representation of the top of the barrier injection model for nanoscale MOSFETs indicating the virtual source point.

The current in the MOSFET is then given as

$$I_{ON} = WC_{ox}v_{ini}(V_{DD} - V_T)$$

Here,  $\upsilon_{inj}$  (also called  $\upsilon_{eff}$ ) is the effective velocity of electrons at the top of the source which is

given as

$$\frac{1}{v_{ini}} = \frac{1}{v_{Bal}} + \frac{1}{\mu_{ab}E(0^+)} \quad ; v_{Bal} = \sqrt{\frac{2kT}{\pi m^*}}$$

Here,  $\mu_{ch}$  refers to the channel mobility. Higher  $\mu_{ch}$  allows the effective injection velocity  $v_{inj}$  to approach the ballistic limit denoted as  $v_{Bal}$ . It is important to note here that both the mobility as well as the ballistic injection velocity depend inversely on the channel effective mass. Thus introducing low effective mass materials will directly impact the injection velocity and hence oncurrent of the MOSFET.

Figure 1-5 summarizes injection velocity  $(\upsilon_{inj})$  for III-V semiconductors in comparison to silicon. It can be observed that the lower effective mass InGaAs channels provide significantly higher (2-3x) injection velocity at 0.5V supply as compared to silicon at close to 1V supply voltage. Additionally it is important that  $\upsilon_{inj}$  is extracted and compared at the same DIBL conditions as this has a direct impact on the barrier height at the virtual source. Although at first it

appears as if III-V devices have a clear advantage over Silicon in transport properties, it is important to look at the corresponding charge density at which  $\upsilon_{inj}$  is extracted in these systems. Injection velocity is a function of the inversion charge density which is in turn determined by the gate bias (see reference 13 in [4]). It is observed that the injection velocity goes through a peak as a function of the gate voltage. The initial increase is due to the fact that the  $\upsilon_{Bal}$  term in the injection velocity equation above is in fact weighted by Fermi functions (see [7]) dictated by the gate bias. The eventual decline however is to be expected due to factors such as surface roughness which reduces the diffusive term. Since the overall  $\upsilon_{inj}$  is determined by the smaller of the two quantities, the diffusive term now dictates the velocity. But then it is important again to note that this trend changes for gate lengths smaller than 40nm. For example the 30nm gate length HEMT device exhibits a monotonic roll off in  $\upsilon_{inj}$  as a function of gate bias.

Figure 1-5. Injection velocity as a function of gate length measured from planar III-V HEMT devices [4].

#### Quantum capacitance bottleneck

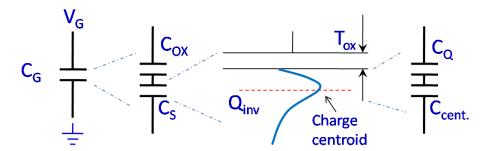

An important consequence of introducing low effective mass channels however, is the emergence of the quantum capacitance[9-11]. Most of the electrons participating in transport in III-V semiconductors reside in the  $\Gamma$ -valley. Due to the spherical symmetry at the bottom of the  $\Gamma$ -valley there is a simple correlation between the transport and density of states (DoS) effective mass. Due to the low effective mass in these semiconductors, low DoS can limit the inversion charge. This is further exacerbated in the case of quantization where the conduction band splits into sub-bands with each having a constant two dimensional DoS given by  $\frac{m_{\ell^*}}{\pi \hbar^2}$  where the index i refers to the i<sup>th</sup> sub-band. Quantization may be introduced by confinement druing heterostructure growth. It can also arise from band bending close to the gate oxide-semiconductor interface which is dictated by electrostatics in the on-state. As a consequence of these quantum effects the semiconductor capacitance reduces which in turn lowers the total gate capacitance at inversion. Figure 1-6 shows the two components of semiconductor capacitance which have to be taken into account in the quantum capacitance limit, viz., the quantum capacitance arising from the finite 2-D DoS and the centroid capacitance which arises from the shape of the inversion layer charge distribution[11].

Figure 1-6. Equivalent circuit representation of quantum effects in the inversion charge. Low effective mass in III-V semiconductors results in more pronounced quantum effects.

Implementing highly scaled transistors dictates the need for ultra-thin quantum well (QW) structures to preserve the electrostatic integrity. However as outlined above this strong confinement leads to the quantum capacitance limit (QCL). High drive current requirement dictates that the new material system needs to provide high mobility at a reasonably high inversion charge density. Figure 1-7 shows the measured field effect mobility for various schottky gated In<sub>x</sub>Ga<sub>1-x</sub>As quantum well transistors as a function of the charge density in comparison to silicon MOSFETs. InGaAs provides considerably higher mobility (40x to 50x) at inversion charge density on the order of  $5x10^{12}$  cm<sup>-2</sup>, making it ideally suited for exploratory studies.

Figure 1-7. Electron mobility  $\mu$  versus sheet electron density  $n_S$  in n-channel Si FETs and III-V QWFETs: Si MOSFETs, InGaAs/AlGaAs HFETs [12,13], lattice-matched InGaAs/InAlAs QWFETs [14,15], pseudomorphic InGaAs/InAlAs QWFETs [16,17], InAs/AlSb QWFETs [18,19].

#### II. Layer structure design and characterization

The general representative channel structure used throughout this dissertation work is shown figure 1-8. The device layer structure comprises of an  $In_xGa_{1-x}As$  channel with varying Indium (In) percentage (x) grown pseudomorphically on a high bandgap  $In_{0.52}Al_{0.48}As$  buffer layer. The wafers are grown by IQE inc. on 3-inch semi-insulating InP wafers using molecular

beam epitaxy (MBE). Subsequent chapters explore the trade-offs inherent in engineering the channel in order to achieve higher performance.

Figure 1-8. Schematic showing generic layer structure of quantum well channels investigated in this work.

Figure 1-9 (a) shows a particular example of layer structure used in this work. The channel comprises a 10nm In<sub>0.7</sub> Ga<sub>0.3</sub>As quantum well (QW) grown pseudomorphically on the In<sub>0.52</sub>Al<sub>0.48</sub>As buffer. The structure contains a silicon delta-doping layer to supply electrons to the channel and facilitate hall mobility measurements for characterizing the growth. A 20nm thick, heavily n-type doped (2x10<sup>19</sup> cm<sup>-3</sup>) In<sub>0.53</sub>Ga<sub>0.47</sub>As cap layer is grown in-situ to allow low resistance ohmic contact formation. The 2nm undoped InP layer serves as an etch stop layer during the recess etch of the heavily doped cap required to define the channel during device fabrication. Figure 1-9 (b) shows the corresponding band diagram obtained from self consistent 1-D Schrodinger-Poisson calculations using nextnano simulations.

Figure 1-9. (a) Device layer structure showing the remote  $\delta$ -doping layer and (b) band diagram indicating the first two sub-bands and the Fermi level.

The presence of a delta-doping layer allows for easy characterization of the channel properties and growth quality through hall measurements. Figure 1-10 shows the temperature dependent hall measurement data for the  $In_{0.7}$   $Ga_{0.3}As$  QW with room temperature mobility measured at  $10,000 cm^2/V.sec$ . Among the various scattering mechanisms modeled and quantified, polar optical phonon mechanism dominates at room temperature.

Figure 1-10. (a) Hall mobility measured as a function of temperature (symbols). Solid lines show fit obtained using a relaxation time approximation based scattering analysis. (b) Carrier density contribution from the first two sub-bands.

#### III. FinFET device architecture

Silicon CMOS technology scaling into the 22nm node and beyond requires advance multi-gate device architectures as planar devices do not provide the necessary short channel electrostatic control[20]. Several different architectures from silicon-on-insulator (SOI), double gate, tri-gate/FinFET to gate all around devices (GAA) have been demonstrated [20-22]. However in order to maintain feasibility from a manufacturing stand point industries have chosen to implement the 3-D tri-gate transistor or FinFET [20]. Figure 1-11 shows scaling trends for 22nm and 14nm technology nodes. Additionally, drive currents for present generation devices (14nm) are normalized to the layout width. With each successive generation, the fin pitch scales down while fin height scales up and thus FinFET architectures enable a new class of scaling where drive currents can approach close to 2mA/μm (normalized to layout width) at scaled nodes; values that are not attainable with traditional planar scaling.

Figure 1-11. Scaling trends of drive current, fin width and fin height from 22nm node onwards. Values for the 10 and 7nm nodes are projected assuming simplistic scaling by 0.7x in dimensions per generation.

Thus in order to assess the feasibility of any new material system, it is essential to characterize and evaluate performance in multi-gate architectures. Results presented in this

dissertation focus exclusively on the FinFET architecture as shown in the representative schematic of figure 1-12 for all experimental device demonstrations as well as simulations outlined in subsequent chapters. All devices are fabricated on layer structures grown by MBE on semi-insulating InP substrates as described in the previous section.

Figure 1-12. Representative schematic showing the architecture of the quantum well FinFET devices fabricated in this work.

## Chapter 2

# High-k dielectric gate stack integration on In<sub>x</sub>Ga<sub>1-x</sub>As

Replacing silicon in the channel of the transistor is fraught with several difficult technical challenges. One of the most fundamental challenges, at the heart of transistor design, is the gate-stack which forms the control terminal of the device. While transistors have traditionally employed a Si/SiO<sub>2</sub> interface, the gate stack in modern transistors comprises of a very intricate atomic level interface between the channel semiconductor (silicon/non-silicon) material and high-k (high permittivity) dielectric based insulator. This is further followed by the deposition of a stack of metals which form the electrode. Different metals are used for the n-channel and p-channel devices in order to tune the workfunction suitably and achieve the desired threshold voltage for the device.

Demonstrating a high quality gate interface is necessary in order to achieve good electrostatic control and shut off the transistor. This is critical especially in low bandgap III-V semiconductors where it is necessary to control sub-threshold leakage current while simultaneously increasing on-current by exploiting higher electron mobilities. The quality of the high-k interface directly impacts the off-state leakage current and in-turn determines the viability of III-V materials as a new technology. Traditional MOSFETs which employ a Si/SiO<sub>2</sub> interface have several intrinsic advantages such as low interface state (trap) density, excellent thermodynamic stability and large band offsets to Silicon along with maturity of the technology[23].

However, demonstrating a high quality trap-state-free interface on non-silicon semiconductor materials such as III-V compound semiconductors with high-k dielectric is an

extremely challenging problem[24-26]. III-V semiconductor surfaces in general exhibit more complicated reconstructions compared to Silicon. Further, GaAs surfaces suffer from gap states arising primarily from As-As dimers which have anti-bonding states in the bandgap just below the conduction band. However moving from GaAs to InGaAs and finally InAs, the bandgap reduces with lowering of the conduction band while the As-As anti-bonding states remain at the same energy. This could potentially provide some reprieve from the Fermi level pinning problem. However with changing group III composition, the interface states problem arises again this time due to uncoordinated group III (In/Ga) atoms and dangling bonds. Thus it is necessary to simultaneously suppress the formation of uncoordinated group III bonds as well As-As dimer states increasing the complexity of dielectric integration to InGaAs.

#### I. MOS capacitor fabrication and characterization: Thermal ALD

The first experimental demonstration of high-k dielectric integration on GaAs substrates implemented an Al<sub>2</sub>O<sub>3</sub> layer grown using thermal atomic layer deposition[26] followed closely by studies with HfO<sub>2</sub> as well[27], due to their suitable band offsets and interface stability[28]. It was found that pulsing of the tri-methyl aluminum (TMA) precursor had a self-cleaning effect on the GaAs surface, by reducing the native oxides. Despite the demonstration of working FETs, the quality of surface passivation achieved was insufficient to demonstrate a scalable technology. However as indicated in the previous section by moving to higher Indium composition it might be possible to overcome limitations from Fermi level pinning to some extent due to the changing surface reconstruction and reduced impact of As-As dimers. In order to investigate this possibility MOS capacitors (MOSCAPs) were fabricated on In<sub>0.53</sub>Ga<sub>0.47</sub>As (InP substrate). Samples were degreased in boiling Acetone and IPA followed by a 3 minute dip in 10:1 buffered HF acid (BOE). An Al<sub>2</sub>O<sub>3</sub> passivation layer followed by HfO<sub>2</sub> layer was grown in order to scale the

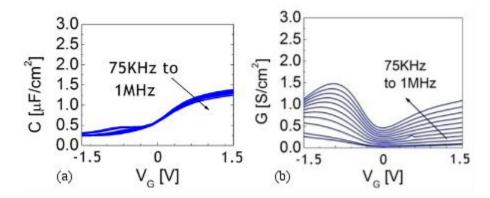

effective oxide thickness (EOT). EOT =  $T_{High-K}*\epsilon_{Si}/\epsilon_{High-k}$ , shows the equivalent thickness of SiO<sub>2</sub> required for the same capacitance density. Figure 2-1 shows experimental capacitance (CV) and conductance (GV) data for a bi-layer stack comprising 1nm Al<sub>2</sub>O<sub>3</sub>/3nm HfO<sub>2</sub> integrated on n-type In<sub>0.53</sub>Ga<sub>0.47</sub>As (Si-doping;  $5x10^{17}$  cm<sup>-3</sup>) by thermal ALD. Platinum gate metal was deposited by ebeam evaporation followed by forming gas anneal (FGA) at  $350^{\circ}$ C for 20mins.

Figure 2-1. Experimental measured capacitance (a) and conductance (b) data for a 1nm  $Al_2O_3/3nm$  HfO<sub>2</sub> stack grown by thermal ALD.

The maximum capacitance density achieved using this bi-layer stack is limited to  $1.4\mu F/cm^2$ . The large EOT is attributed to interfacial oxide growth during the anneal process caused by the presence of oxygen in the RTA furnace ambient. Additionally, large frequency dispersion is observed in the mid-gap and depletion regions. It should be noted further that the devices are characterized only down to a frequency of 75KHz. These results show that despite integrating  $Al_2O_3$  as the passivation layer, there is significant frequency dispersion. Further the addition of  $HfO_2$  did not result in scaled EOT.

## II. Low power plasma surface clean and passivation

In order to improve the quality of the surface passivation low power plasma treatment was explored. Experiments were done on the Kurt Lesker LX 150 plasma ALD tool in the Penn State

nanofab. Low power inductively coupled remote plasmas were generated by diluting Ar gas with various ratios of H<sub>2</sub> and N<sub>2</sub>. All samples were degreased in boiling Acetone and then rinsed in IPA, followed by a 3 minute 10:1 BOE clean prior to loading into the loadlock of the ALD tool. Preliminary experiments indicated that H<sub>2</sub> plasma has a detrimental impact on the InGaAs surface resulting in poor CV modulation and large frequency dispersion. Whereas the primary function of the plasma clean is to reduce the native oxide, the H<sub>2</sub> plasma was found to induce surface damage hampering the subsequent nucleation of the ALD grown high-k layers. This surface damage was found to be present at all substrate temperatures from 100°C to 250°C. Subsequently N<sub>2</sub> plasma was investigated as outlined by Chobapattana et al in [29]. However in this work we explore highly diluted concentrations (5-10%) in an Ar ambient. The presence of Ar gas also facilitates quick plasma ignition at low powers facilitating short plasma pulse exposures. First set of N<sub>2</sub> plasma exposure experiments were carried out at relatively low temperature of 110°C. Figure 2-2 shows the measured CV and GV characteristics for depletion-mode MOSCAPS fabricated with the above gate stack on n-type (Si-doping; 5x10<sup>17</sup>cm<sup>-3</sup>) In<sub>0.53</sub>Ga<sub>0.47</sub>As.

Figure 2-2. Measured capacitance (a) and conductance (b) data shown for MOS capacitor with bi-layer gate stack and low temperature (110C) plasma nitride surface passivation.

The surface is exposed to alternating pulses of N<sub>2</sub> plasma followed by TMA exposure. This was followed by thermal ALD growth of 1nmAl<sub>2</sub>O<sub>3</sub> and 3nm HfO<sub>2</sub>. Additionally the gate metal was changed to thermally evaporated Nickel instead of e-beam Platinum. Special ceramic

(Alumina) coated Tungsten boats were used for the Nickel evaporation. Results immediately indicated better CV modulation along with reasonable frequency dispersion. The samples were annealed in FGA at 350C for 20mins. In order to avoid the presence of Oxygen in the annealing ambient the samples are annealed in the ALD chamber itself post metallization. The samples are transferred into the ALD chamber through the high vacuum loadlock into a  $H_2$ /Ar ambient which prevents unwanted oxidation of the surface. However the maximum capacitance density obtained was only around  $1.5\mu$ F/cm<sup>2</sup> indicating that some native oxide still remains on the surface. This is also evidenced by the relatively large frequency dispersion in the mid-gap and depletion regions. Figure 2-3 shows the corresponding measured gate leakage current which is well controlled with the maximum current density value below  $10\text{mA/cm}^2$ .

Figure 2-3. Gate leakage measured for MOS capacitor shown in figure 2-2.

The above results indicated that the  $N_2$  plasma surface clean yielded reasonable CV characteristics thus providing a viable path for optimization. The reduced capacitance density and large frequency dispersion indicate the presence of residual native oxide and the absence of a pristine starting surface for nucleation of the high-k layers. In order to increase the effectiveness of the plasma clean one of the most critical parameters that needs to be modified is the substrate temperature. Various temperatures starting from  $110^{\circ}$ C upto  $250^{\circ}$ C were investigated for the  $N_2$

plasma clean. Temperatures higher that 250°C were not investigated in order to limit the thermal budget and cooling/cycling times required for subsequent ALD high-k growth which was optimized at 250°C. The plasma surface treatment was performed as outlined before with alternating pulses of N<sub>2</sub> plasma followed by TMA exposure. The TMA pulse is shut off for the first cycle of exposure and is then followed by 5 cycles of the N<sub>2</sub> plasma/TMA sequence. Samples are metalized with thermally evaporated Nickel. In order to investigate the impact of the FGA CV was measured before and after post metal FGA. Figure 2-4 shows the CV and GV characteristics for MOSCAPs fabricated with the above surface clean performed at 250°C followed by thermal ALD of 1nm Al<sub>2</sub>O<sub>3</sub> and 3nm HfO<sub>2</sub>. The panels on the left show the corresponding characteristics for the samples without the FGA and on the right after FGA respectively.

Figure 2-4. Effect of FGA on bi-layer dielectric gate stack with high temperature plasma nitrogen clean and passivation. (a) and (b) show capacitance data before and after FGA while (c) and (d) show the corresponding conductance data.

It is observed that the FGA has a significant impact on the frequency dispersion near mid-gap and depletion regions. Further the maximum capacitance density  $C_{max}$  also increases from 2.3 to  $2.65\mu F/cm^2$ . The key results obtained with the high temperature (250°C) plasma clean in this experiment include the stabilization of the interface and higher  $C_{max}$  with simultaneously lower frequency dispersion. The capacitance equivalent thickness (CET) and equivalent oxide thickness (EOT) are measured at 1.3nm and 1nm respectively (corresponding to  $C_{max}$  of 2.65  $\mu F/cm^2$ ). The difference between the two thicknesses results from the finite thickness of the inversion layer which results in quantum capacitance. It is critical to account for this thickness especially in low mass systems as highlighted in chapter 1. Figure 2-5 shows the comparison of the gate leakage currents with and without FGA. The leakage current is observed to increase by nearly two orders post FGA. However the maximum current density was still measured to be less than  $1A/cm^2$  which is the maximum tolerance allowed for high performance CMOS devices.

Figure 2-5. Gate leakage comparison before and after FGA for bi-layer dielectric gate stack.

In order to understand the nature of surface passivation and native oxide removal we further investigate the device using transmission electron microscopy. Figure 2-6 shows the cross-section TEM of the realized gate stack. It is observed that the alternating  $N_2$  plasma/TMA

sequence results in near complete removal of native oxide on the surface followed by growth of a 3A thick  $AlO_xN_y$  layer. This passivation layer also facilitates nucleation of the subsequent ALD oxide layers evidenced by the well controlled gate leakage which could be higher due to the presence of pinholes in the oxide layers and the  $Al_2O_3$  layer in turn is used to facilitate nucleation of the  $HfO_2$  layer.

Figure 2-6. Cross-section transmission electron micrograph of the bi-layer dielectric gate stack with 250°C plasma nitride surface passivation.

#### Bi-layer vs. single layer dielectric gate stack

In order to fully exploit the benefits of a high mobility semiconductor channel it is necessary to increase the capacitance density of the gate stack so that higher inversion charge may be realized in the channel. Since the on current is directly proportional to the gate capacitance as  $I_{ON} = \upsilon_{inj} C_G(V_G - V_T)$ , a larger gate capacitance has a direct impact on the device performance. Further, for highly scaled devices it is important to maintain good electrostatic control for which a large  $C_G$  ( $C_{ox}$ ) again helps to reduce the subthreshold swing (SS) which depends on the gate coupling ratio given as  $\eta = (1 + C_{dep}/C_{ox})$ . Higher Cox may be realized by

aggressively scaling the thickness of the high-k layers. However this will result in increased gate leakage. Instead, in our approach we migrate from the composite stack to a 4nm thick  $HfO_2$  only gate stack. The thickness of  $HfO_2$  is kept same as the composite gate stack in order to maintain the same order of gate leakage current. The passivation layer comprising of  $AlO_xN_y$  is retained and realized as described in the previous section. Figure 2-7 shows the comparison between the two resulting gate stacks. The panels on the left show CV and GV respectively for the composite  $(Al_2O_3/HfO_2)$  gate stack respectively whereas those on the right show the corresponding data for the  $HfO_2$  only gate stack.

Figure 2-7. (a) and (b) show measured capacitance data (symbols) while (c) and (d) show measured conductance data (symbols) for bi-layer 1nm Al<sub>2</sub>O<sub>3</sub>/3nm HfO<sub>2</sub> and 4nm HfO<sub>2</sub> only stacks. Solid lines indicate fit from equivalent circuit model.

It is immediately observable that the  $AlO_xN_y$  passivation +  $HfO_2$ -only gate stack shows superior frequency dispersion characteristics in the mid-gap and depletion regions without significant change in  $C_{max}$ . This is further evidenced from the conductance (GV) characteristics of

the devices. In order to compare and quantify the improvement in the passivation characteristics extract the interface state density ( $D_{\rm IT}$ ) for both the HfO<sub>2</sub>-only as well as composite gate stacks. This is extracted using the modified conductance technique described in [30] where both the CV and GV characteristics are simultaneously modeled while also accounting for the gate leakage currents. The corresponding fit is also shown in figure 2-7 where the symbols show measured data points and solid lines indicate the output of the model. Good fit is obtained giving confidence in the extraction technique. Figure 2-8 shows the resulting  $D_{\rm IT}$  and trap time constant profiles. It is observed that the HfO<sub>2</sub> only gate stack shows  $D_{\rm IT}$  density around  $1x10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> starting close to mid-gap up to the conduction band (0V - 1.5V), which is almost order of magnitude lower than the composite gate stack. However both gate stacks show an increase in  $D_{\rm IT}$  towards the conduction band and again from mid-gap onwards going into the lower half of the band gap.

Figure 2-8. (a) Extracted  $D_{IT}$  profiles and (b) estimated trap time constant for bi-layer and  $HfO_2$  only gate stacks.