## The Pennsylvania State University The Graduate School

## REUSE DISTANCE MODELS FOR ACCELERATING SCIENTIFIC COMPUTING WORKLOADS ON MULTICORE PROCESSORS

A Dissertation in Computer Science and Engineering by Jeonghyung Park

$\odot$  2015 Jeonghyung Park

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

The dissertation of Jeonghyung Park was reviewed and approved\* by the following:

Padma Raghavan

Associate Vice President for Research

Director of Institute for CyberScience

Distinguished Professor, Computer Science and Engineering

Dissertation Advisor, Chair of Committee

Mahmut Kandemir Professor, Computer Science and Engineering

Kamesh Madduri Assistant Professor, Computer Science and Engineering

Christopher Duffy Professor, Civil and Environmental Engineering

Raj Acharya Professor, Computer Science and Engineering Department Head, Computer Science and Engineering

<sup>\*</sup>Signatures are on file in the Graduate School.

#### **Abstract**

As the number of cores increase in chip multiprocessor microarchitecture (CMP) or multicores, we often observe performance degradation due to complex memory behavior on such systems. To mitigate such inefficiencies, we develop schemes that can be used to characterize and improve the memory behavior of a multicore node for scientific computing applications that require high performance.

We leverage the fact that such scientific computing applications often comprise code blocks that are repeated, leading to certain periodic properties. We conjecture that their periodic properties and their observable impacts on cache performance can be characterized in sufficient detail by simple ' $\alpha + \beta \sin(\theta)$ ' models. Additionally, starting from such a model of the observable reuse distances, we develop a predictive cache miss model, followed by appropriate extensions for predictive capability in the presence of interference.

We consider the utilization of our reuse distance and cache miss models for accelerating scientific workloads on multicore system. We use our cache miss model to determine a set of preferred applications to be co-scheduled with a given application to minimize performance degradation from interference. Further, we propose a reuse distance reducing ordering that improves the performance of Laplacian mesh smoothing. We reorder mesh vertices based on the initial quality for each node and its neighboring nodes so that we can improve both temporal and spatial localities. The reordering results show that 38.75% of performance improvement of Laplacian mesh smoothing can be obtained by our reuse distance reducing ordering when running on a single core. 75x of speedup is obtained when scaling up to 32 cores.

### **Table of Contents**

| List of                  | Figures                                                                          | vi  |

|--------------------------|----------------------------------------------------------------------------------|-----|

| List of                  | Tables                                                                           | xii |

| Ackno                    | wledgments                                                                       | xiv |

| Chapte<br>Inti           | er 1<br>oduction                                                                 | 1   |

| Chapte                   | er 2                                                                             |     |

| Bac                      | kground                                                                          | 5   |

| 2.1                      | Notations                                                                        | 5   |

| 2.2                      | Simple Periodic $\alpha + \beta \sin(2\pi t\phi)$ Functions and the Role of FFTs | 6   |

| 2.3                      | Reuse Distance Analysis for Characterizing Cache Interference                    | 7   |

| 2.4                      | Laplacian Mesh Smoothing                                                         | 8   |

| 2.5                      | Mesh Reordering for Improving Mesh Smoothing Performance                         | 10  |

| Chapte                   | er 3                                                                             |     |

| $\operatorname{Re}\iota$ | se Distance and Cache Miss Models                                                | 12  |

| 3.1                      | Modeling Cache Performance in an HPC application using $\alpha$ +                |     |

|                          | $\beta \sin(2\pi t \phi)$ function                                               | 12  |

|                          | 3.1.1 Methodology                                                                | 13  |

|                          | 3.1.2 Predictive Models                                                          | 14  |

| 3.2                      | Experimental Results                                                             | 17  |

|                          | 3.2.1 Experimental Setup                                                         | 18  |

|                          | 3.2.2 Verification: Predicting Cache Misses from Models of Reuse                 |     |

|                          | Distance, i.e., $\overline{C}_{A_i} = k_1 R_{A_i}$                               | 19  |

|         | 3.2.3                         | Verification: Predicting Cache Misses from Models of Reuse Distance, i.e., $\overline{C}_{A_i} = k_1 R_{A_i}$ in Real Architecture System | 21         |

|---------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.3     | Summ                          | lary                                                                                                                                      | 21         |

| CI.     | 4                             |                                                                                                                                           |            |

| Chapte  |                               | e Miss Models be Predictive in the face of Interference?                                                                                  | 26         |

| 4.1     |                               | ling Interference in Co-scheduled HPC Applications Using $\alpha+$                                                                        | 20         |

| 4.1     |                               | $(2\pi t\phi)$ function                                                                                                                   | 26         |

|         | $\frac{\beta \sin(2)}{4.1.1}$ | Methodology                                                                                                                               | 27         |

|         | 4.1.2                         | Predictive Models                                                                                                                         | 27         |

| 4.2     |                               | imental Results                                                                                                                           | 31         |

| 1.2     | 4.2.1                         | Experimental Setup                                                                                                                        | 31         |

|         | 4.2.2                         | Verification: Predicting Reuse Distances in the Presence of                                                                               | 91         |

|         | 1.2.2                         | Interference, i.e., $\overline{R}_{(A_i A_i)} = c_1 R_{A_i} + c_2 R_{A_i} + c_3$                                                          | 31         |

|         | 4.2.3                         | Verification: Predicting Cache Misses from Reuse Distance                                                                                 | 01         |

|         | 1.2.0                         | in the Presence of Interference, i.e., $\overline{C}_{(A_i A_i)} = k_1 \overline{R}_{(A_i A_i)}$                                          | 36         |

| 4.3     | Summ                          | tary                                                                                                                                      | 38         |

|         |                               |                                                                                                                                           |            |

| Chapt   |                               |                                                                                                                                           |            |

| Acc     | celerati                      | ing Scientific Workloads using Reuse Distances and                                                                                        |            |

|         |                               | Cache Miss Models                                                                                                                         | 42         |

| 5.1     |                               | neduling using Ranking Results of our Predictive Cache Miss                                                                               |            |

|         | Model                         | s under Interference                                                                                                                      | 42         |

|         | 5.1.1                         | Experimental Results                                                                                                                      | 44         |

|         | 5.1.2                         | Summary of Co-scheduling                                                                                                                  | 44         |

| 5.2     |                               | Distance Reducing Ordering for Laplacian Mesh Smoothing .                                                                                 | 48         |

|         | 5.2.1                         | Factors Affecting Temporal and Spatial Locality                                                                                           | 49         |

|         | 5.2.2                         | Toward a Reuse Distance Reducing Ordering                                                                                                 | 50         |

|         | 5.2.3                         | Experimental Results                                                                                                                      | 54         |

|         |                               | 5.2.3.1 Experimental Setup                                                                                                                | 54         |

|         |                               | 5.2.3.2 Performance: Execution Time and Reduced Reuse                                                                                     |            |

|         |                               | Distance                                                                                                                                  | 55         |

|         |                               | 5.2.3.3 Cache Performance                                                                                                                 |            |

|         | 1                             | 5.2.3.4 Performance Scalability                                                                                                           | 59         |

|         | 5.2.4                         | Summary of Reuse Distance Reducing Ordering                                                                                               | 61         |

| Chapte  | er 6                          |                                                                                                                                           |            |

| -       |                               | ns and Future Work                                                                                                                        | 70         |

| D'! !'  | 1                             |                                                                                                                                           | <b>=</b> 0 |

| Bibliog | graphy                        |                                                                                                                                           | <b>7</b> 3 |

## **List of Figures**

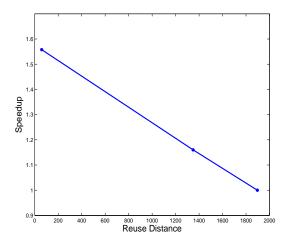

| 1.1 | Speedups obtained from difference reuse distances for irregular mesh smoothing application. As the reuse distances increased, less performance gainings are achieved                                                                   | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

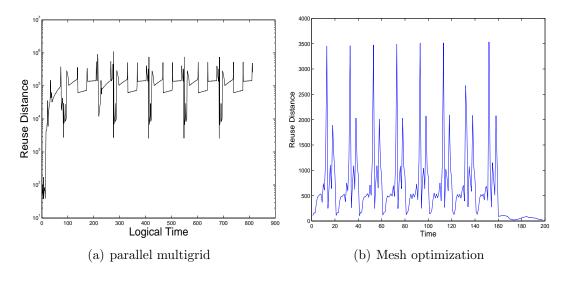

| 1.2 | The reuse distance profile for the multigid (MG) application (a). A certain periodic behavior is observable. The reuse distance profile for the mesh optimization application discussed in Chapter 6 also shows a periodic pattern (b) | 3  |

| 2.1 | Time variance data trace for 100 elements generated by a function $y = 2 + \sin(2\pi t \times 10)$ and its frequency domain data converted by                                                                                          | _  |

| 2.2 | FFT                                                                                                                                                                                                                                    | 7  |

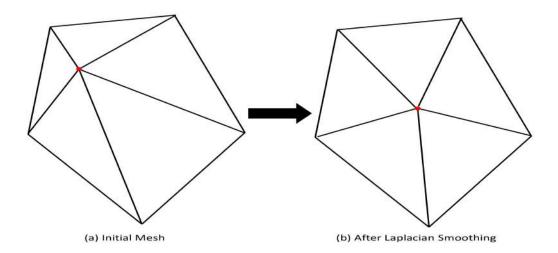

| 2.2 | Laplacian smoothing performed on initial mesh. The vertex position inside the mesh was changed                                                                                                                                         | 9  |

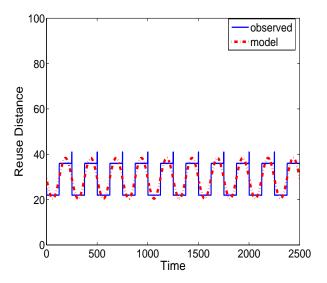

| 3.1 | Observed reuse distance profile(solid line) and its sine function model(dash-dot line) for $CodeP(30, 10)$ application                                                                                                                 | 15 |

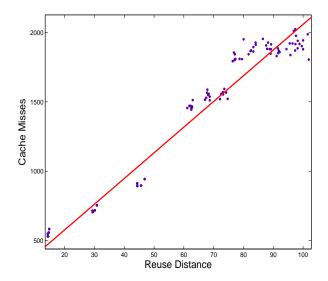

| 3.2 | Correlation between reuse distance and cache misses for a multi-<br>core with 2KB cache. Consider for example, cache misses of 1,500<br>corresponding to a reuse distance of 60, 24 times the reuse distance                           |    |

|     | value                                                                                                                                                                                                                                  | 16 |

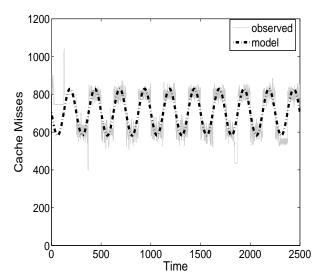

| 3.3 | Observed cache miss profile (solid line) and its sine function model (dash                                                                                                                                                             | -  |

|     | dot line) for $CodeP(30, 10)$ application running on a system with                                                                                                                                                                     | 17 |

|     | cache size 2KB                                                                                                                                                                                                                         | 17 |

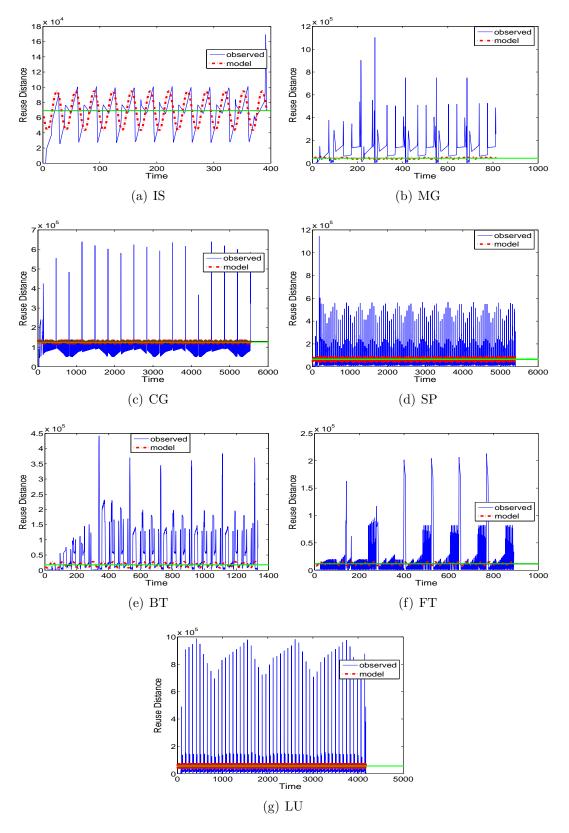

| 3.4 | Observed reuse distance profiles $OR_{A_i}$ and their reuse distance mod-                                                                |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | els $R_{A_i} = FFT(OR_{A_i})$ for (a) $IS(A_1)$ , (b) $MG(A_2)$ , (c) $CG(A_3)$ , (d)                                                    |    |

|     | $SP(A_4)$ , (e) $BT(A_5)$ , (f) $FT(A_6)$ , and (g) $LU(A_7)$ . Average reuse                                                            |    |

|     | distances shown as lines for IS, MG, CG, SP, BT, FT, and LU are                                                                          |    |

|     | 69118.3, 44028.6, 127999.9, 65328.8, 17937.1, 11799.5, and 57141.8                                                                       |    |

|     | when observed and 69177.06, 43994.78, 126719.9, 65395.64, 17948.9,                                                                       |    |

|     | 11807.8, and 57196.2, respectively, when modeled. Errors are very                                                                        |    |

|     | low at 0.00085%, 0.00076%, 0.01%, 0.001%, 0.00066%, 0.00071%,                                                                            |    |

|     | and 0.00095% for IS, MG, CG, SP, BT, FT, and CG, respectively.                                                                           | 23 |

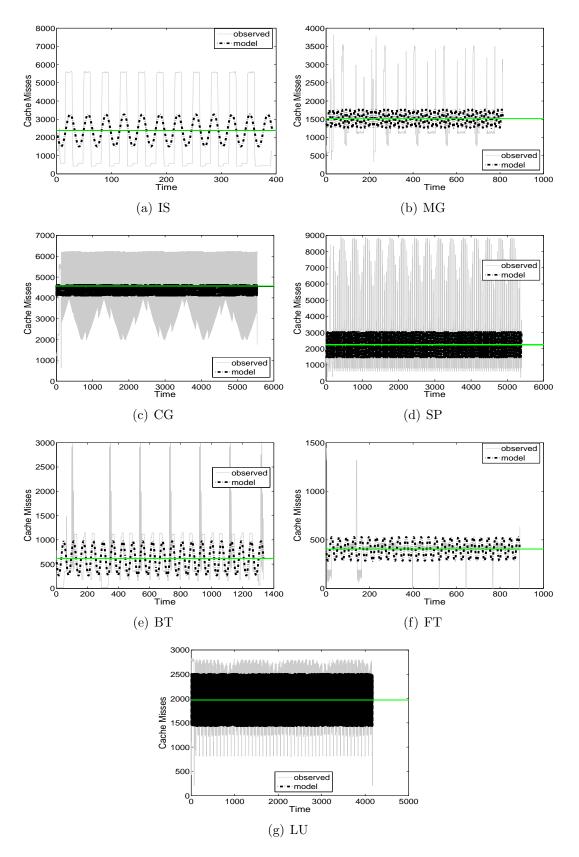

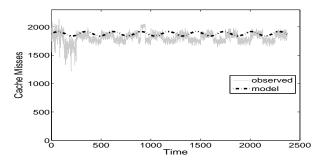

| 3.5 | Observed cache miss profiles $OC_{A_i}$ and their cache miss models                                                                      | 20 |

| 5.5 | $\overline{C}_{A_i} = 0.03445 R_{A_i}$ for (a) IS( $A_1$ ), (b) MG( $A_2$ ), (c) CG( $A_3$ ), (d)                                        |    |

|     | $\operatorname{SP}(A_4)$ , (e) $\operatorname{BT}(A_5)$ , (f) $\operatorname{FT}(A_6)$ , and (g) $\operatorname{LU}(A_7)$ . The dominant |    |

|     | amplitudes are shown as lines for both observed and predicted $(\alpha)$                                                                 |    |

|     | values. Observe that these lines are nearly coincident indicating a                                                                      |    |

|     | high level of match between observed and predicted values                                                                                | 24 |

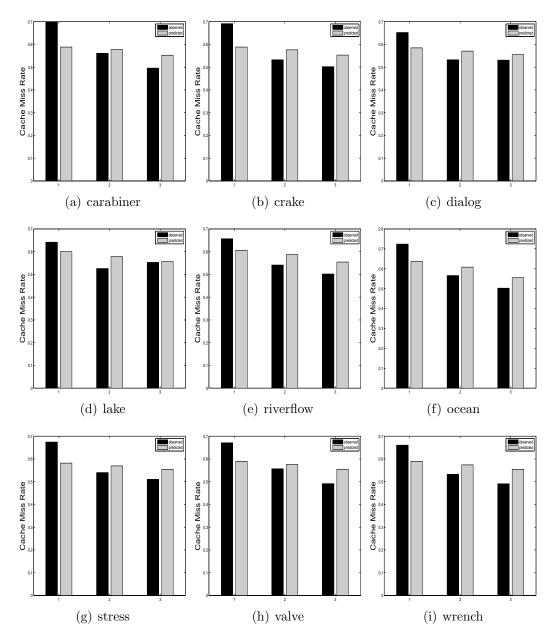

| 3.6 | Our predictive cache miss model results of Laplacian mesh smooth-                                                                        | 24 |

| 5.0 | ing for (a) carabiner, (b) crake, (c) dialog, (d) lake, (e) riverflow,                                                                   |    |

|     | (f) ocean, (g) stress, (h) valve, and (i) wrench meshes when ORI,                                                                        |    |

|     | BFS, and RDR ordering are applied. Overall prediction error rates                                                                        |    |

|     | are 5.36%                                                                                                                                | 25 |

|     | arc 9.00/0                                                                                                                               | 20 |

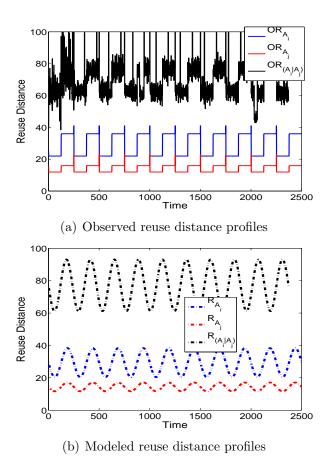

| 4.1 | Observed reuse distance profiles (a) for $CodeP(30, 10)$ , namely $A_i$ ,                                                                |    |

|     | for $CodeP(10, 10)$ , namely $A_j$ , and for $A_i$ in the presence of inter-                                                             |    |

|     | ference by $A_j$ . The corresponding modeled profiles are shown below                                                                    |    |

|     | in (b)                                                                                                                                   | 28 |

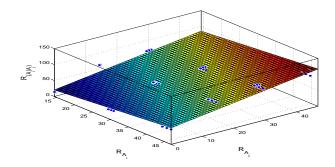

| 4.2 | Correlation between reuse distances for two applications and the                                                                         |    |

|     | interfered reuse distance in a given multicore system                                                                                    | 29 |

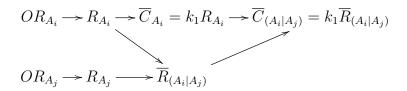

| 4.3 | Summary of our proposed approach to develop a predictive model                                                                           |    |

|     | of cache misses of application $A_i$ with interference by application                                                                    |    |

|     | $A_j$ when they are co-scheduled                                                                                                         | 29 |

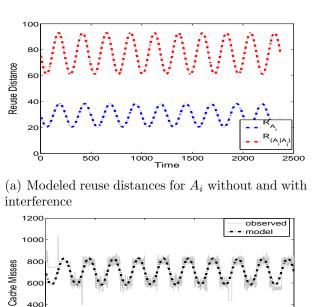

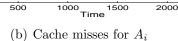

| 4.4 | $CodeP(30, 10)$ and $CodeP(10, 10)$ are used as $A_i$ and $A_j$ . Reuse                                                                  |    |

|     | distance models are shown in (a) for $R_{A_i}$ and $\overline{R}_{(A_i A_j)}$ , observed                                                 |    |

|     | cache misses $OC_{A_i}$ and modeled cache misses $\overline{C}_{A_i}$ are shown in                                                       |    |

|     | (b), and finally, when co-scheduled in the presence of interference,                                                                     |    |

|     | the observed cache misses $OC_{(A_i A_j)}$ and the modeled cache misses                                                                  |    |

|     | $\overline{C}_{(A_i A_i)} = k_1 \overline{R}_{(A_i A_i)}$ are shown in (c)                                                               | 30 |

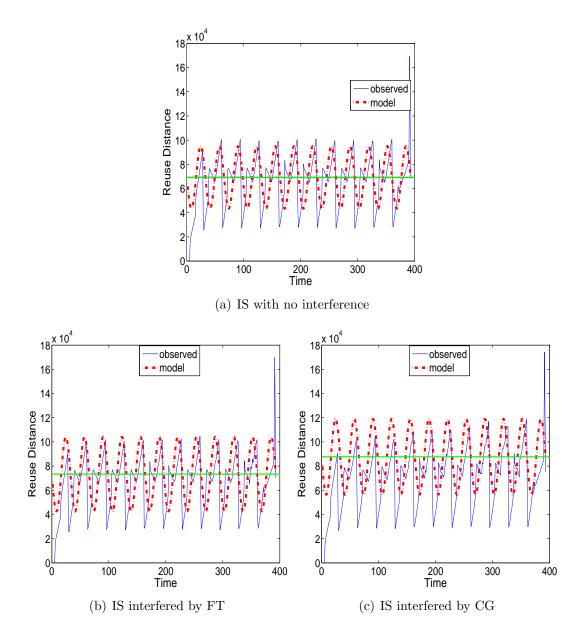

| 4.5  | Observed reuse distance profile $OR_{A_i}$ and the reuse distance model                                       |    |

|------|---------------------------------------------------------------------------------------------------------------|----|

|      | $R_{A_i} = FFT(OR_{A_i})$ for $IS(A_1)(a)$ . Observed reuse distance profiles                                 |    |

|      | $OR_{(A_i A_j)}$ and the reuse distance models $\overline{R}_{(A_i A_j)} = c_1 R_{A_i} + c_2 R_{A_j} +$       |    |

|      | $c_3$ , where $c_1 = 1.178$ , $c_2 = 0.1245$ , and $c_3 = -9593$ , in the presence                            |    |

|      | of interference from $FT(A_6)(b)$ and $CG(A_3)(c)$                                                            | 33 |

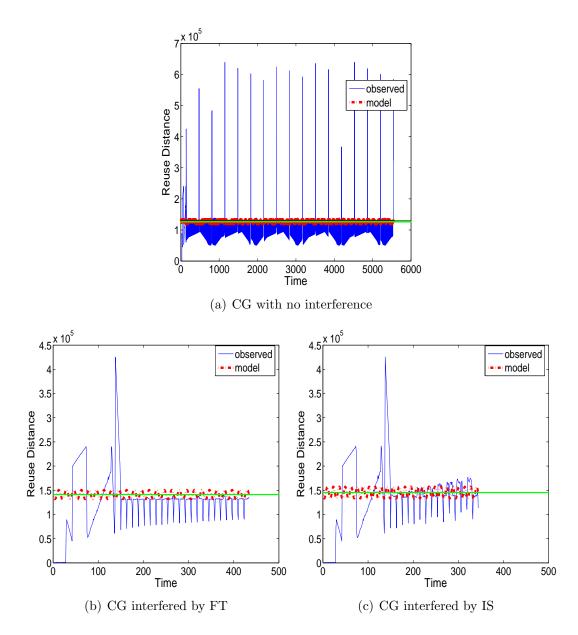

| 4.6  | Observed reuse distance profile $OR_{A_i}$ and the reuse distance model                                       |    |

|      | $R_{A_i} = FFT(OR_{A_i})$ for $CG(A_3)(a)$ . Observed reuse distance profiles                                 |    |

|      | $OR_{(A_i A_i)}$ and the reuse distance models $\overline{R}_{(A_i A_i)} = c_1 R_{A_i} + c_2 R_{A_i} +$       |    |

|      | $c_3$ , where $c_1 = 1.178$ , $c_2 = 0.1245$ , and $c_3 = -9593$ , in the presence                            |    |

|      | of interference from $FT(A_6)(b)$ and $IS(A_1)(c)$                                                            | 34 |

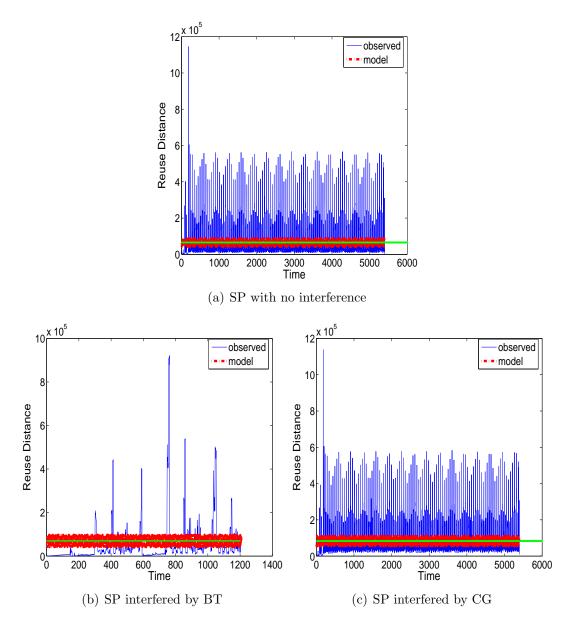

| 4.7  | Observed reuse distance profile $OR_{A_i}$ and the reuse distance model                                       |    |

|      | $R_{A_i} = FFT(OR_{A_i})$ for $SP(A_4)(a)$ . Observed reuse distance profiles                                 |    |

|      | $OR_{(A_i A_i)}$ and the reuse distance models $\overline{R}_{(A_i A_i)} = c_1R_{A_i} + c_2R_{A_i} +$         |    |

|      | $c_3$ , where $c_1 = 1.178$ , $c_2 = 0.1245$ , and $c_3 = -9593$ , in the presence                            |    |

|      | of interference from $BT(A_5)(b)$ and $CG(A_3)(c)$                                                            | 35 |

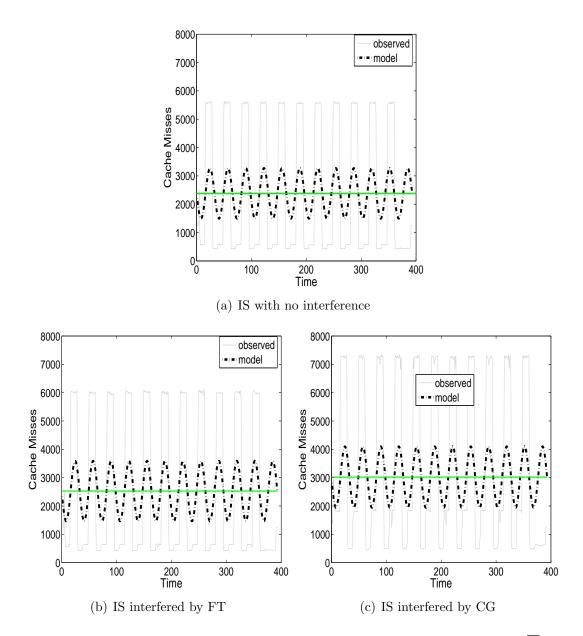

| 4.8  | Observed cache miss profile $OC_{A_i}$ and the cache miss model $\overline{C}_{A_i}$                          |    |

|      | $k_1 R_{A_i}$ , where $k_1 = 0.03445$ , for $IS(A_1)(a)$ . Observed cache miss                                |    |

|      | profiles $OC_{(A_i A_i)}$ and the cache miss models $\overline{C}_{(A_i A_i)} = k_1 \overline{R}_{(A_i A_i)}$ |    |

|      | in the presence of interference from $FT(A_6)$ (b) and $CG(A_3)$ (c)                                          | 38 |

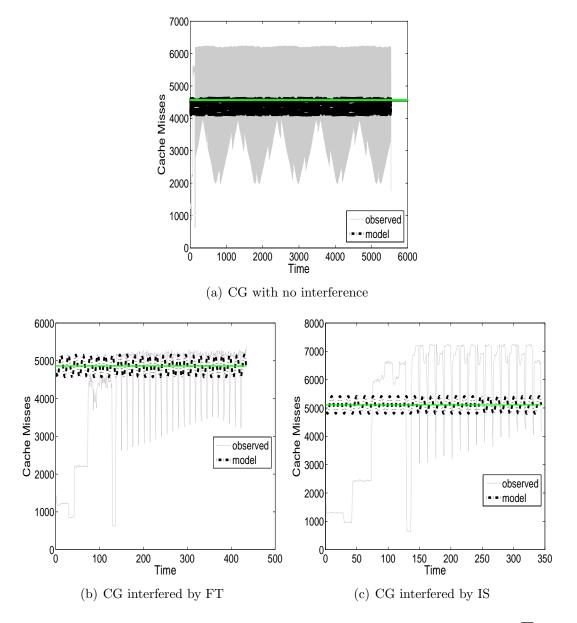

| 4.9  | Observed cache miss profile $OC_{A_i}$ and the cache miss model $\overline{C}_{A_i}$                          |    |

|      | $k_1 R_{A_i}$ , where $k_1 = 0.03445$ , for CG(A <sub>3</sub> )(a). Observed cache miss                       |    |

|      | profiles $OC_{(A_i A_j)}$ and the cache miss models $\overline{C}_{(A_i A_j)} = k_1 \overline{R}_{(A_i A_j)}$ |    |

|      | in the presence of interference from $FT(A_6)$ (b) and $IS(A_1)$ (c)                                          | 39 |

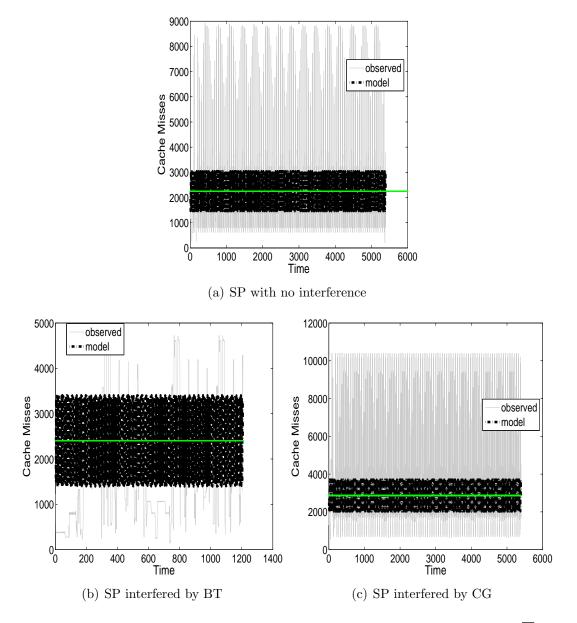

| 4.10 | Observed cache miss profile $OC_{A_i}$ and the cache miss model $C_{A_i}$                                     |    |

|      | $k_1 R_{A_i}$ , where $k_1 = 0.03445$ , for $SP(A_4)(a)$ . Observed cache miss                                |    |

|      | profiles $OC_{(A_i A_j)}$ and the cache miss models $C_{(A_i A_j)} = k_1 R_{(A_i A_j)}$                       |    |

|      | in the presence of interference from $BT(A_6)$ (b) and $CG(A_3)$ (c)                                          | 40 |

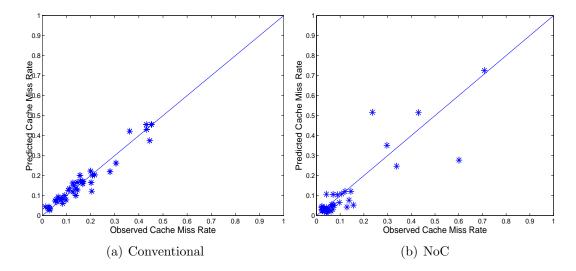

| 4.11 | Prediction results for our cache interference miss model on conven-                                           |    |

|      | tional computer architecture (a) and NoC architecture system (b).                                             |    |

|      | Overall prediction error rates are 3.13% for conventional architec-                                           |    |

|      | ture with a two level cache hierarchy system and 3.98% for NoC                                                |    |

|      | architecture                                                                                                  | 41 |

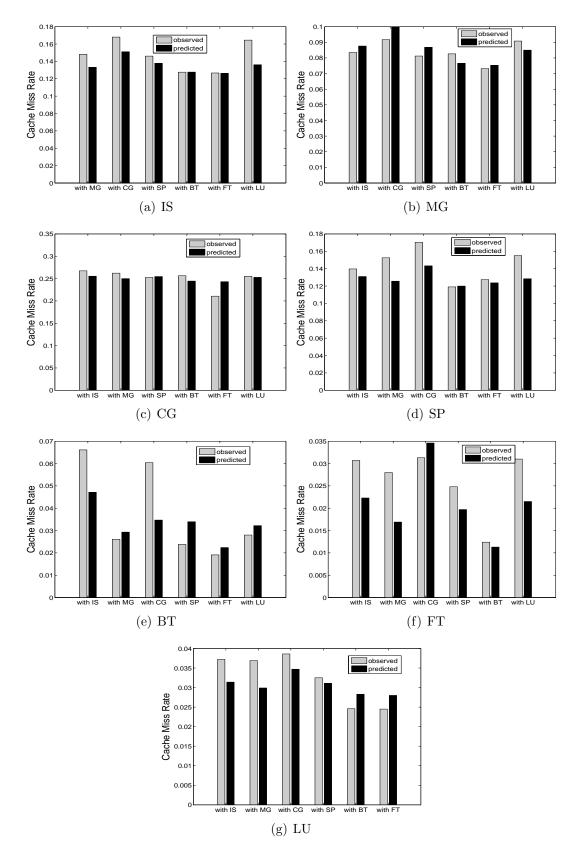

| 5.1        | Total execution times when four applications $A_1$ , $A_2$ , $A_3$ , and $A_4$ are co-scheduled. When applications are scheduled in a random |            |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------|

|            | way (a), we obtained the worst performance. When applications                                                                                |            |

|            | are co-scheduled with our ranking system (b), we first co-schedule                                                                           |            |

|            | applications $A_1$ and $A_2$ since the pair of $A_1$ and $A_2$ show the least                                                                |            |

|            | increase of cache misses. The best co-scheduling performance can                                                                             |            |

|            | be obtained through our ranking results of predictive cache miss                                                                             |            |

|            | models.                                                                                                                                      | 43         |

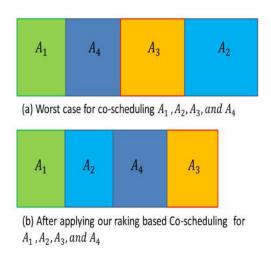

| 5.2        | Prediction results for our cache interference miss models for (a)IS,                                                                         | 10         |

| J.2        | (b)MG, (c)CG, (d)SP, (e)BT, (f)FT, and (g)LU. From the pre-                                                                                  |            |

|            | dicted cache miss rates, we rank the best pair application for each                                                                          |            |

|            | application to co-schedule each other                                                                                                        | 46         |

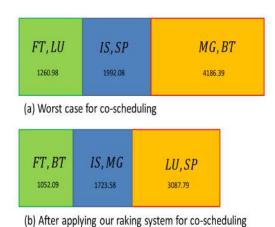

| 5.3        | Total execution times when six applications IS, MG, SP, BT, FT,                                                                              | 10         |

| 0.0        | and LU are co-scheduled. When applications are scheduled in a                                                                                |            |

|            | random way (a), we obtained the worst performance, 7439.45 sec.                                                                              |            |

|            | When applications are co-scheduled with our ranking system (b), we                                                                           |            |

|            | first co-schedule applications FT and BT since the pair of FT and                                                                            |            |

|            | BT show the least increase of cache misses. Next, we co-schedule                                                                             |            |

|            | applications IS and MG for obtaining the least increase of cache                                                                             |            |

|            | misses among the remaining applications. Improved co-scheduling                                                                              |            |

|            | performance can be obtained through our ranking results of predic-                                                                           |            |

|            | tive cache miss models, 5863.46 sec                                                                                                          | 47         |

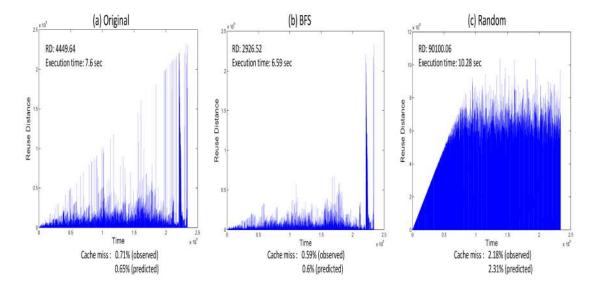

| 5.4        | Performance results for Laplacian mesh smoothing according to the                                                                            |            |

|            | difference reuse distances with (a) original mesh, (b) BFS ordered                                                                           |            |

|            | mesh, and (c) random ordered mesh                                                                                                            | 49         |

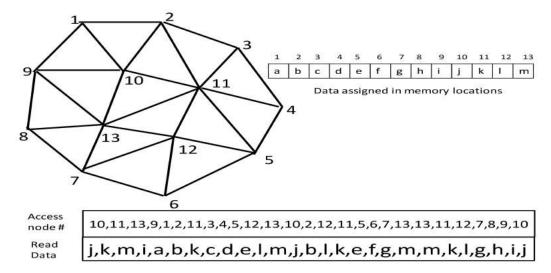

| 5.5        | Partial traces observed from node visiting for Laplacian mesh smooth-                                                                        |            |

|            | ing. (a) Traces for Laplacian mesh smoothing with original order-                                                                            |            |

|            | ing. (b) Traces for Laplacian mesh smoothing with BFS ordering.                                                                              |            |

|            | When the reuse distances for Laplacian mesh smoothing are reduced                                                                            |            |

|            | by BFS ordering, temporal and spatial localities are significantly                                                                           |            |

|            | improved                                                                                                                                     | 50         |

| 5.6        | Original Mesh that have have almost same qualities for each vertex.                                                                          |            |

|            | The node traces visited by Laplacian mesh smoothing are shown                                                                                | 51         |

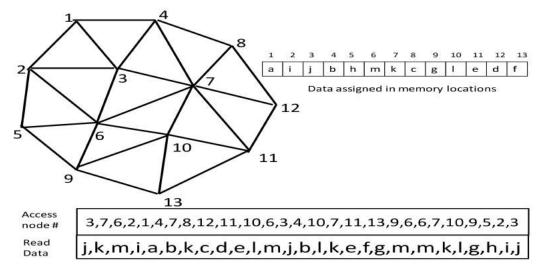

| 5.7        | BFS ordered Mesh. The node traces showing the visit of Laplacian                                                                             |            |

|            | mesh smoothing have higher spatial locality than original mesh                                                                               | 51         |

| 5.8        | Reordered mesh based on the qualities that each node has. The                                                                                |            |

|            | node traces observed from Laplacian mesh smoothing have higher                                                                               | <b>-</b> ~ |

| <b>-</b> ^ | spatial locality and higher temporal locality than original mesh                                                                             | 52         |

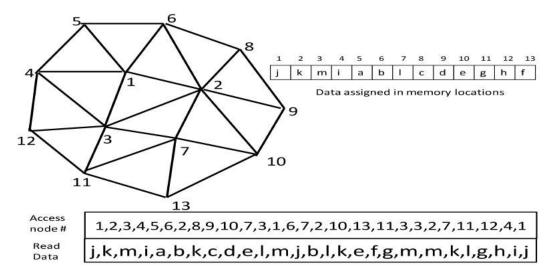

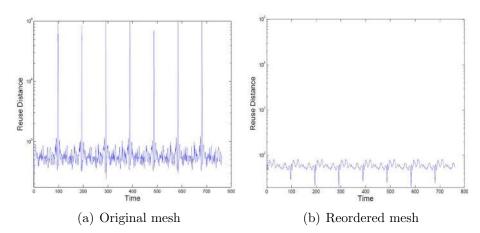

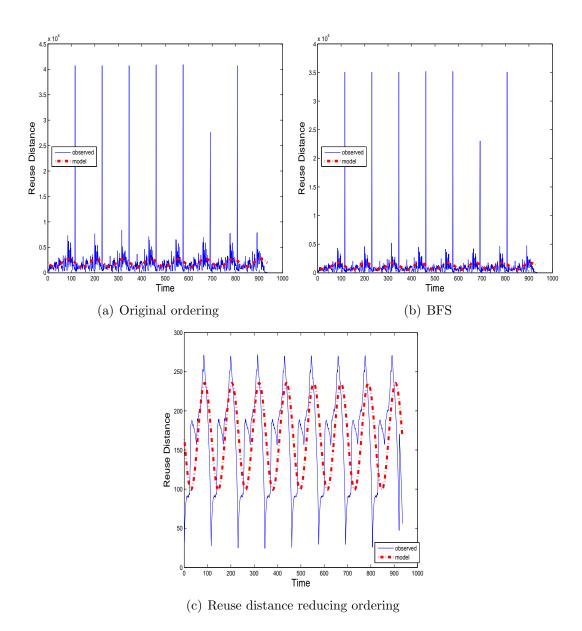

| 5.9        | Observed reuse distance profiles for original mesh (a) and reordered                                                                         |            |

|            | $\operatorname{mesh} (b).  \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                 | 53         |

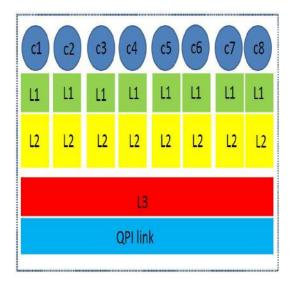

| 5.10 | High-level views of Intel Westmere-EX processor. Ovals denote to     |   |    |

|------|----------------------------------------------------------------------|---|----|

|      | cores and rectangles represent on-chip caches (L1, L2, and L3).      |   |    |

|      | The machine has four sockets, which are connected directly via 3.2   |   |    |

|      | GHz OPI links. Each socket has 8 cores with the inclusive cache      |   |    |

|      | hierarchy; 32K L1 private cache, 256K L2 private cache, and 24MB     |   |    |

|      | shared L3 cache are in the socket, highlighted using dashed box      |   | 55 |

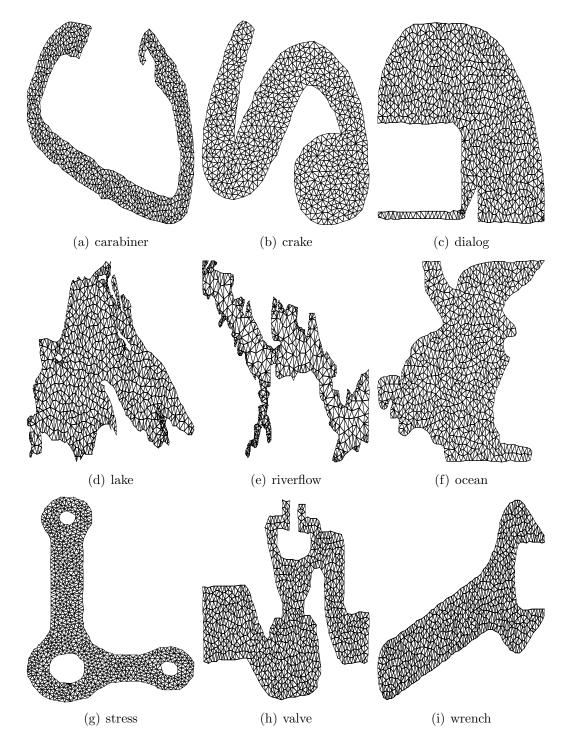

| 5.11 | 2D meshes generated by Triangle [1]. These meshes are coarser,       |   |    |

|      | representative versions of the meshes used in the experiments        |   | 56 |

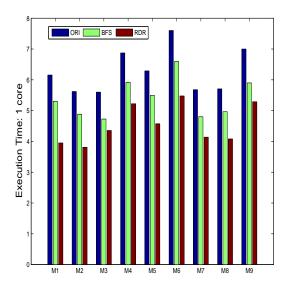

| 5.12 | Execution time results for Laplacian mesh smoothing when reuse       |   |    |

|      | distance reducing ordering was applied. Reuse distance reducing      |   |    |

|      | ordering is 38.57% faster than original ordering                     |   | 57 |

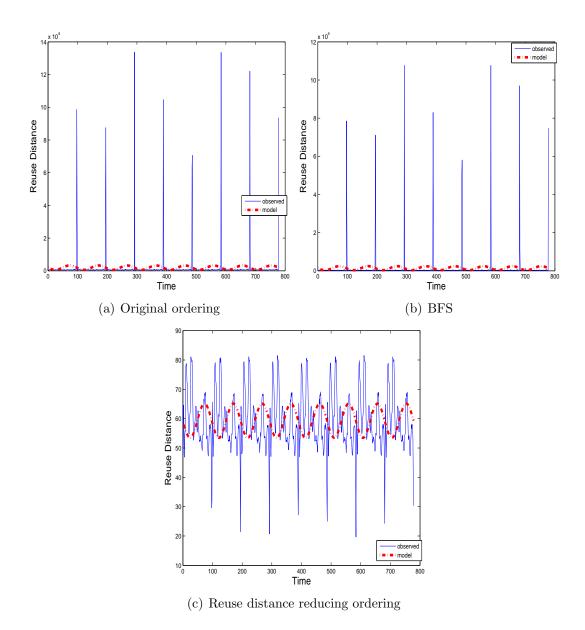

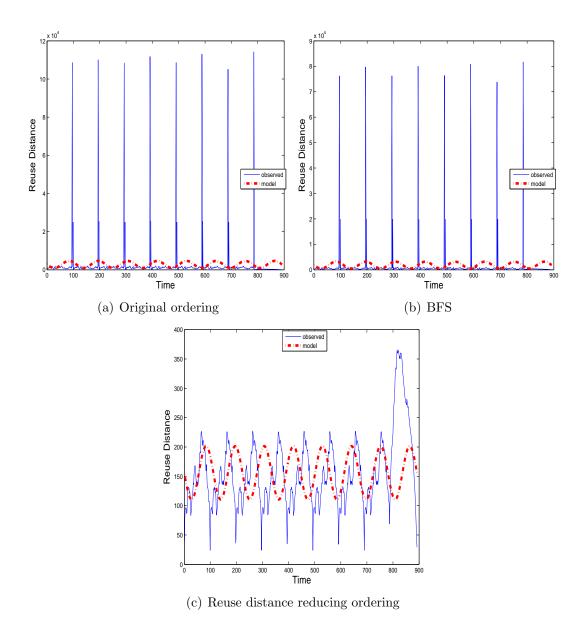

| 5.13 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with carabiner mesh         |   | 58 |

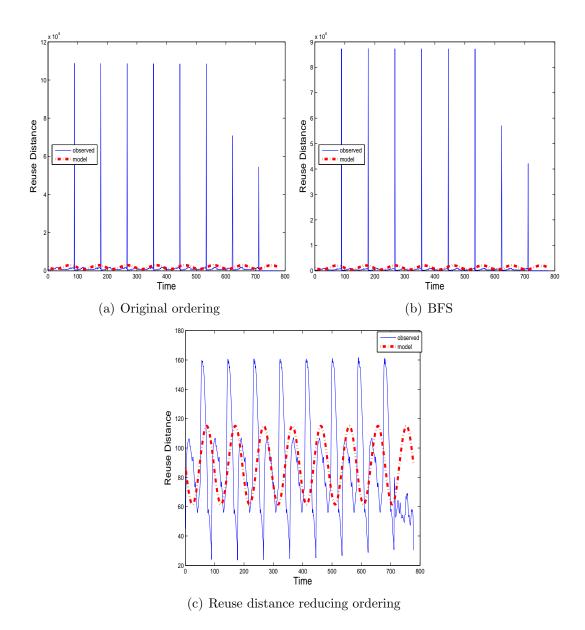

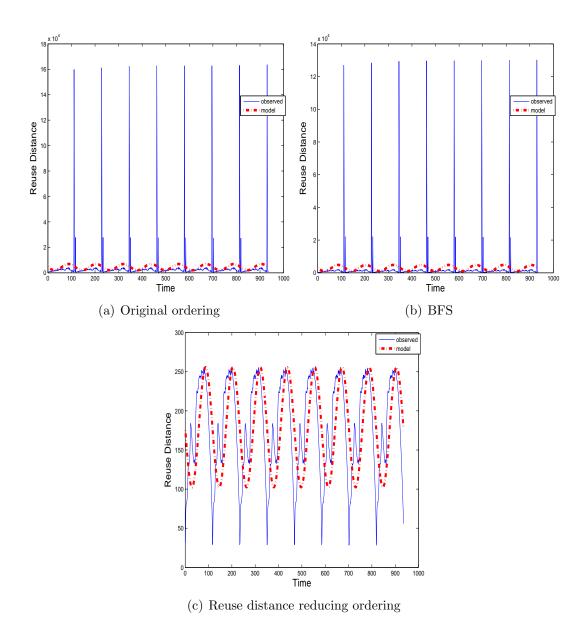

| 5.14 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with crake mesh             |   | 59 |

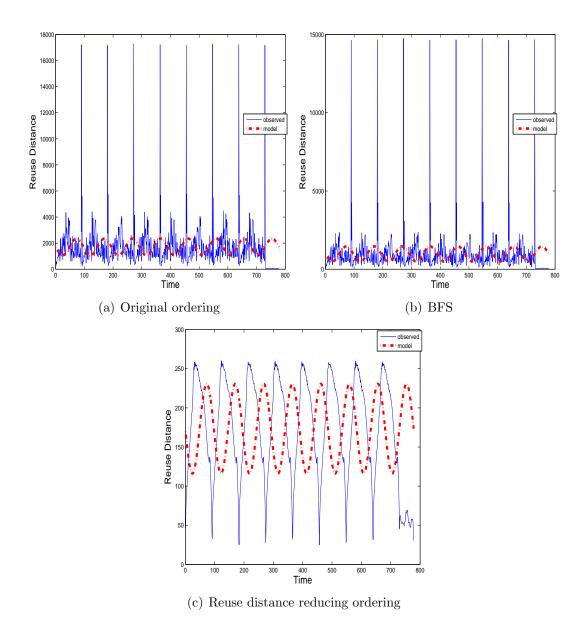

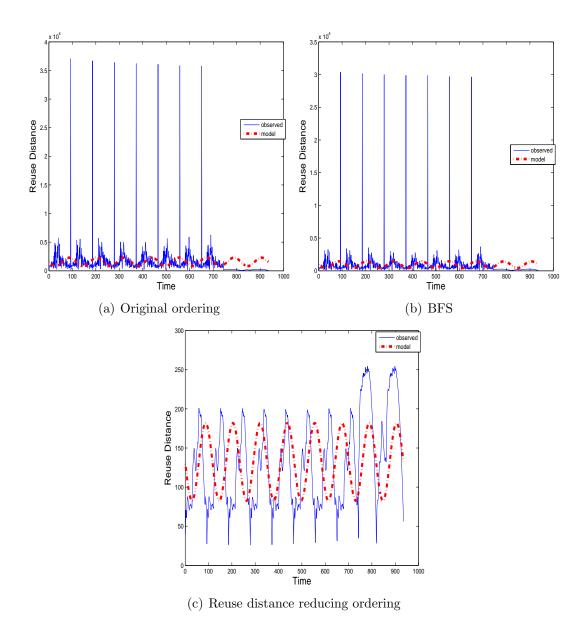

| 5.15 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with dialog mesh            |   | 60 |

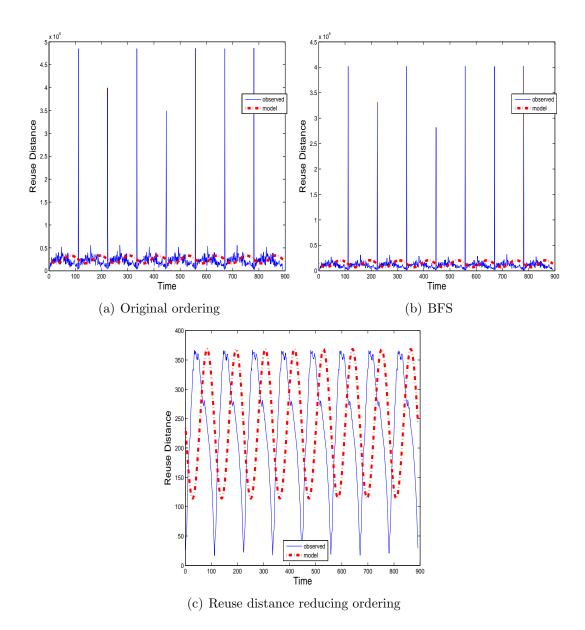

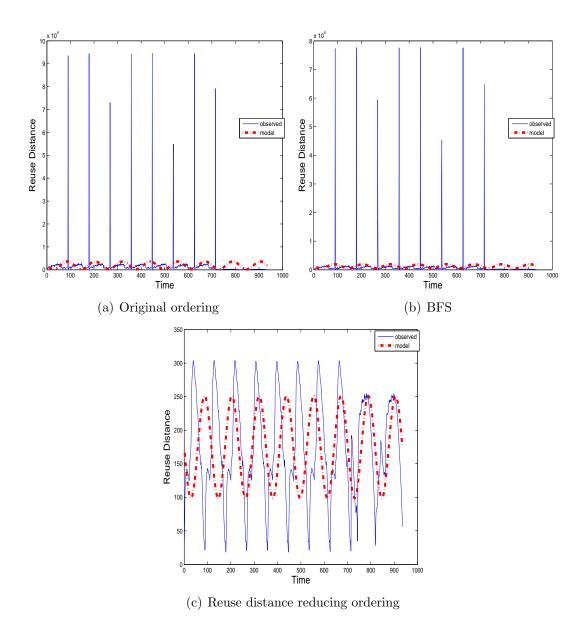

| 5.16 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with lake mesh              |   | 61 |

| 5.17 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with riverflow mesh         | • | 62 |

| 5.18 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with ocean mesh             | • | 63 |

| 5.19 | 1                                                                    |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with stress mesh            | • | 64 |

| 5.20 | 1                                                                    |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with valve mesh             | • | 65 |

| 5.21 | Observed reuse distance profiles and reuse distance models for (a)   |   |    |

|      | original ordering, (b) BFS ordering, and (c) reuse distance reducing |   |    |

|      | ordering of the Laplacian mesh smoothing with wrench mesh            | _ | 66 |

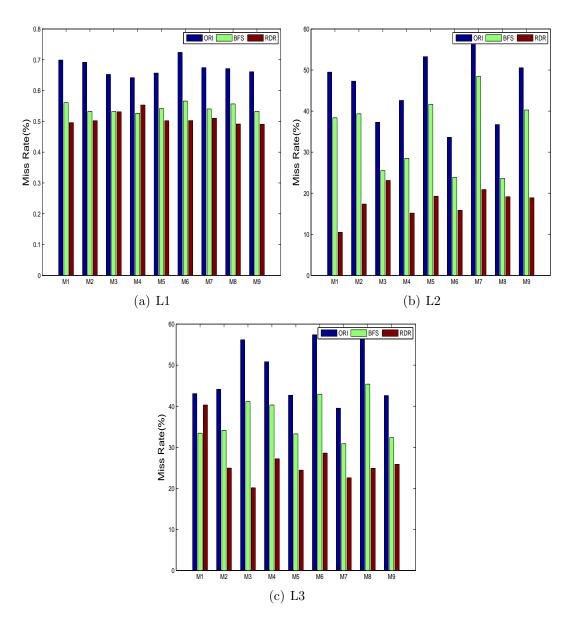

| 5.22 | Cache performance results when reuse distance reducing ordering         |    |

|------|-------------------------------------------------------------------------|----|

|      | was applied to Laplacian mesh smoothing for (a) L1, (b) L2, and         |    |

|      | (c) L3. Cache miss rates decreased from 0.67% to 0.5% for L1, from      |    |

|      | 44.7% to $17.3%$ for L2, and from $47.4%$ to $26.1%$ for L3 on average. | 68 |

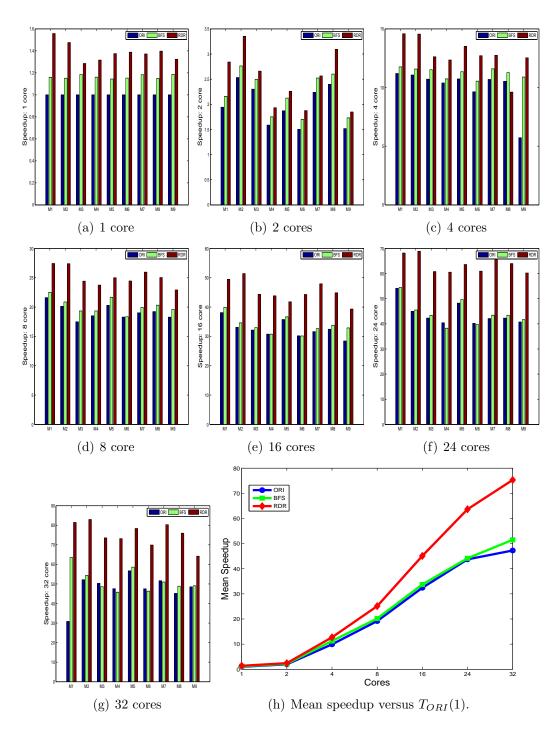

| 5.23 | Observed speedup relative to the serial ORI baseline. Reuse dis-        |    |

|      | tance reducing ordering (RDR) provides significant performance im-      |    |

|      | provement                                                               | 69 |

### **List of Tables**

| 3.1        | Set of applications used for our model verification                                                                                                                                                                                     | 19 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2<br>3.3 | Model parameters. $k_1$ is used in $\overline{C}_{A_i} = k_1 R_{A_i}$                                                                                                                                                                   | 19 |

| 3.4        | when they are run alone, with no interference                                                                                                                                                                                           | 20 |

|            | crake, dialog, lake, riverflow, ocean, stress, valve, and wrench meshes when original ordering and BFS ordering are applied                                                                                                             | 22 |

| 4.1        | Model parameters. $k_1$ is used in $\overline{C}_{A_i} = k_1 R_{A_i}$ , $\overline{C}_{(A_i A_j)} = k_1 \overline{R}_{(A_i A_j)}$ .                                                                                                     |    |

| 4.2        | Further, $c_1, c_2$ , and $c_3$ are used in $\overline{R}_{(A_i A_j)} = c_1 R_{A_i} + c_2 R_{A_j} + c_3$ Predicted reuse distances in the presence of interference using $\overline{R}_{(A_i A_j)} = c_1 R_{A_i} + c_2 R_{A_j} + c_3$ . | 31 |

| 7.2        | 1.178 $R_{A_i} + 0.1245R_{A_j} - 9593$ for each application when paired with one of the remaining six in order of increasing levels of interference.                                                                                    |    |

|            | The ranges of interfered reuse distances are also shown                                                                                                                                                                                 | 32 |

| 4.3        | Reuse distance models for $IS(A_1)$ , $CG(A_3)$ and $SP(A_4)$ in the presence of interference. Pairs shown in the reuse distance models represent the least and the most increased reuse distances for IS, CG,                          |    |

|            | and SP                                                                                                                                                                                                                                  | 32 |

| 4.4        | Predicted cache misses in the presence of interference using $\overline{C}_{(A_i A_j)} = 0.03445\overline{R}_{(A_i A_j)}$ for each application when paired with one of the re-                                                          |    |

|            | maining six in order of increasing levels of interference. The ranges of interfered cache misses are also shown                                                                                                                         | 36 |

| 4.5        | Cache miss models for $IS(A_1)$ , $CG(A_3)$ , and $SP(A_4)$ in the presence of interference. Pairs shown in the cache miss models represent the                                                                                         |    |

|            | least and the most increased cache misses for IS, CG, and SP                                                                                                                                                                            | 37 |

| 5.1        | Predicted ranking of applications for co-scheduling with IS, MG, CG, SP, BT, FT, and LU                                                                                                                                                 | 45 |

| 5.2        | Input Mesh Configuration                                                                                                                                                                                                                | 55 |

| 5.3 | Reuse distance models of Laplacian mesh smoothing for carabiner,        |    |

|-----|-------------------------------------------------------------------------|----|

|     | crake, dialog, lake, riverflow, ocean, stress, valve, and wrench meshes |    |

|     | when original ordering, BFS ordering and reuse distance reducing        |    |

|     | ordering are applied                                                    | 67 |

### Acknowledgments

This work was supported in part by the National Science Foundation through awards 1319448 and 1439058.

#### **Dedication**

I would like to thank my thesis advisor, Dr. Padma Raghavan, for her guidance, patience, and support she has shown me during my time here at Pennsylvania State University. I am grateful for the one-on-one time she has given and our conversations that have expanded my mind and opened to the gate for overcoming problems I met in my methodology. Without her support, I would have never made it. I thank my committee members, Dr. Mahmut Kandemir, Dr. Kamesh Madduri, and Dr. Christopher Duffy, for their insightful commentary on my work. Finally, I would like to thank my father and my mother. My father was strong role model that taught me the joy of research in computer science. My mother taught me the value of hard work. I am grateful for their indefinite support over the years.

|              | 1 |  |

|--------------|---|--|

| l<br>Chapter |   |  |

#### Introduction

Current trends call for core counts as high as  $60\sim90$  at a multicore node in the near future [2]. Consequently, it is desirable to apply greater parallelism to enable efficient utilization of processing power and memory resources [3,4]. However, the performance of irregular high performance computing applications (HPC) on such multicores tend to scale poorly. We observe that many irregular applications cause unexpected memory accesses and these become the bottleneck of performance scalability [5]. Further, when multiple applications are run concurrently on larger number of cores, they compete for shared resources such as on-chip caches, main memory, memory bandwidth, and the I/O bus. Such computing resource contention often have negative impacts on overall performance of applications. This degradation becomes even more pronounced in applications with higher performance computing requirements. To mitigate unexpected performance degradation for irregular high performance computing applications on multicores, understanding memory subsystem behavior is crucial. More specifically, efficient cache utilization for irregular applications must be considered in order to achieve performance scalability under a fixed problem size.

For resolving significant performance issues and tuning application's performance, we focus on memory behavior of on-chip caches and NUMA domains for shared memory, many-core systems. In current HPC systems, there is considerable variation between vendors, for instance, Intel and AMD chip designs range from 4 to 12 cores per die and have significant differences in cache design [6,7]. This variation makes it challenging to predict application's performance on these various

computer architecture systems without costly runs of applications. Further, for a performance prediction to be feasible it is required to be compact and efficient. Thus, we seek mathematical model driven approach to predict memory behavior of applications.

In this thesis, we consider the methodology for modeling memory behavior of HPC applications by using reuse distances. It is known that there exists a relationship between reuse distance and cache miss rates for applications on multicore systems [8]. Applications with lower reuse distances show better performance. Figure 1.1 shows the performance variation in regards of reuse distances. Once we develop the reuse distance models, we use it to optimize performance.

Figure 1.1: Speedups obtained from difference reuse distances for irregular mesh smoothing application. As the reuse distances increased, less performance gainings are achieved.

To mathematically model the memory behavior of HPC applications through reuse distances, we use the fact that many scientific applications show periodic behavior. Our main contributions are based on exploiting the fact that HPC applications often exhibit periodic behavior. This is primarily from the fact that in many HPC codes, code segments in basic blocks are performed repeatedly. We expect that their iterative computations will lead to certain periodic patterns in measures such as reuse distances and cache misses that we can model compactly for predictive purposes. As an example, the observed reuse distance profile is shown below in Figure 1.2(a) for parallel multigrid (MG). Mesh smoothing application considered in Chapter 5 also shows the periodic behavior in its observed reuse

distance profile shown in Figure 1.2(b). We would like to consider how the behavior of this and other applications can be modeled as a simple periodic function.

Figure 1.2: The reuse distance profile for the multigid (MG) application (a). A certain periodic behavior is observable. The reuse distance profile for the mesh optimization application discussed in Chapter 6 also shows a periodic pattern (b).

Our contributions in this thesis are not meant to faithfully reproduce the complicated time evolution patterns that can be observed of reuse distances and cache misses. Instead, our goal is to come up with concise, reduced-order models which can capture essential features of memory behavior including average reuse distances and average cache misses. We use the periodic patterns in their observable reuse distances to develop models for their memory behavior in terms of cache miss rates. Additionally, we develop a predictive cache miss model based on our conjecture that these periodic patterns will continue to persist even in the presence of interference in the shared caches when two applications are co-scheduled. Further, we will improve the performance of HPC application by using our predictive reuse distance and cache miss models.

We start by providing notation, background material on simple periodic functions and Laplacian mesh smoothing, related research on reuse distance and cache interference miss analysis, and mesh reordering schemes in Chapter 2. We provide our main contributions in Chapters 3, 4, and 5. Our main contributions in this thesis can be summarized as follows:

- Reuse Distance and Cache Miss Models. In Chapter 3, we propose a simple  $\alpha + \beta \sin(2\pi t\phi)$  model of reuse distance that can be obtained from observed values. We assume that a small set of data can be obtained to correlate, in general, reuse distance and cache misses for a given multicore. We propose how to develop a model for cache misses from the reuse distance model when an application runs by itself without interference.

- Predictive Cache Miss Models in the Presence of Interference. In Chapter 4, we propose models of cache misses under interference for any pair of applications. In our approach, all data needed to compute correlations can be obtained using synthetic code segments and without running actual applications. Actual runs are only needed to observe reuse distances for an application when it is running alone, thus, enhancing the potential value of our predictive model for informing co-scheduling. We verify our models for NAS benchmarks and we show that the error rate in our predictive models for cache misses when two applications interfere each other is on average 3.13%.

- Accelerating Scientific Workload Using Reuse Distance and Cache Miss Models. In Chapter 5, we show that how to utilize our reuse distance and cache miss models for improving performance. We first show that the predictive cache model can be used to generate rankings of a preferred partner for a given application to inform how application pairs could be co-scheduled for best performance. We then propose reuse distance reducing ordering for Laplacian mesh smoothing. This reordering scheme provides up to 38.75% of performance improvement for Laplacian mesh smoothing on a single core. When we scale up to 32 cores, 75x speedup with reuse distance ordering is obtained as compared with a serial baseline (with original ordering mesh). Predictive cache miss models developed in Chapter 3 were utilized to predict cache performance for Laplacian mesh smoothing when the reuse distance reducing ordering is applied. Prediction error rates for our predictive cache miss models were low at 5.36% on average.

Finally, we present concluding remarks and potential directions for future research in Chapter 6.

### **Background**

In this chapter, we present a brief review of the background material. We first introduce and define terms and notation that we will use in the remainder of this dissertation. Further, we provide a brief review of sine functions constructed by an Fast Fourier Transformation (FFT). Additionally, we present a review of related research about reuse distance analysis and characterization of cache interference. We then, provide a brief explanation of Laplacian mesh smoothing that is used for mesh quality improvement in irregular HPC applications. Finally, we discuss related works for mesh reordering to improve the mesh smoothing performance.

#### 2.1 Notations

We consider a set of n applications  $A_1, A_2, ... A_n$ , each of which may execute on its own on a multicore processor or execute with any one of the other applications, and thus as a pair of applications sharing and contending for memory resources. We assume that for an application  $A_i$  when it is running on a multicore, we can observe its memory accesses to calculate the reuse distance and cache miss rate for each access as they evolve over time. The reuse distance is defined as the number of memory references between two successive accesses to the same memory reference. The cache miss rate is defined as the number of misses that occur in a shared cache divided by the total number of cache accesses.

We use  $OR_{A_i}$ , and  $OC_{A_i}$  to denote these observed reuse distance and cache miss profiles, respectively, for the case when the application is running by itself,

i.e., without another co-scheduled application. Further, we expect to observe such sequences when  $A_i$  and  $A_j$  are co-scheduled together. In the co-scheduled case, because of interference, we expect the profiles to be different for each application compared to when it is run on its own. Further, we expect both applications to be impacted in different ways. To denote the observed reuse distances for application  $A_i$  because of interference by  $A_j$ , we use  $OR_{(A_i|A_j)}$ . Similarly, the observed cache misses for the interfered application  $A_i$  is denoted  $OC_{(A_i|A_j)}$ .

We will be developing modeled approximate representations of some of the observable measures as part of our main contributions in Chapter 3 and Chapter 4. We use  $R_{A_i}$  to denote the sine model for representing the periodic behavior in  $OR_{A_i}$ . We use symbols with an overline,  $\overline{C}_{A_i}$  to denote the model for predicting cache misses from  $R_{A_i}$ , the model of observed reuse distances. Similarly, the modeled reuse distance for  $A_i$  in the presence of interference by co-scheduled application  $A_j$  is denoted by  $\overline{R}_{(A_i|A_j)}$ . The modeled cache miss rate for  $A_i$  in the presence of interference by co-scheduled application  $A_j$  is denoted by  $\overline{C}_{(A_i|A_j)}$ .

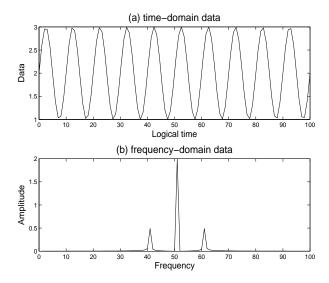

## 2.2 Simple Periodic $\alpha + \beta \sin(2\pi t \phi)$ Functions and the Role of FFTs

It is known that time-domain data that exhibit periodic behavior can be represented as a simple sine function in the form of  $\alpha + \beta \sin(2\pi t\phi)$ . If an observed sequence of a measure, such as the reuse distance, is known for example, through the trace of an application running on a multicore or from compiler or runtime analysis, then it is conceivable that if it has periodic behavior, it could be approximated by such a sine representation. In general, the process of determining the existence of periodicity in such data involves a suitable fast fourier transformation (FFT) [9].

Consider data with 100 elements in Figure 2.1(a) where a simple, regular, periodic behavior is clearly observable. Now an FFT can be applied to these data, to get an frequency-domain representation in terms of dominant magnitudes and their frequencies as shown in Figure 2.1(b). Observe that the two highest magnitudes are  $M_1 = 2$  and  $M_2 = 0.5$ ; further, they occur at frequencies  $I_1 = 0.5$

Figure 2.1: Time variance data trace for 100 elements generated by a function  $y = 2 + \sin(2\pi t \times 10)$  and its frequency domain data converted by FFT.

50, and  $I_2 = 60$  respectively. One way construct a sine function of the form  $\alpha + \beta \sin(2\pi t\phi)$  is to set  $\alpha = M_1$ ,  $\beta = M_2 \times 2$ , and  $\phi = abs(I_1 - I_2)$  to get  $2 + 1 \times \sin(2\pi t \times 10)$ . In this simple example, we recover the original form with accuracy. However, in general such a construction will give only an approximation. Further, the original data may be noisy and may have linear or non-linear trends that may need to be identified and removed before applying an FFT to characterize the periodic behavior. However, this basic approach is often appropriate with suitable variations to derive periodic function models from data in a wide variety of applications.

## 2.3 Reuse Distance Analysis for Characterizing Cache Interference

We now summarize how our results are loosely related to two prior streams of results on (i) reuse distance analysis and (ii) characterization of contention in the memory subsystem of CMPs/multicores when applications are co-scheduled. Further, we comment on how our contributions are significantly different than these earlier results.

Many researchers have applied reuse distance analysis to capture the cache performance of applications running on a single core system [10–12], and on multicore systems [13–16]. These results typically involve generating reuse distance histograms and using them to predict cache miss rates. However, these results do not take into account interference from co-scheduling of applications as we do in this paper.

More recently, as multiple applications are run simultaneously on CMPs/multicores, there is increasing interests in studying performance degradation effects due to shared resource contention. Zhuravlev et al. classify levels of cache contention in regard to increases in execution times [17]. Tang et al. used cache misses, memory bandwidth and prefetchers to indicate an application's contention characteristics [18] with further extensions in [15, 19, 20]. Additionally, Zhao et al. propose a two-phase regression approach involving cache misses and memory bandwidth [21]. These characterization results differ substantively from the results in this paper which provide closed form trigonometric function models of cache miss rates with interference from co-scheduling. Further, our models derive solely from the observable reuse distance profile of an application running alone.

The differentiating significance of our contributions in this paper is that we bring predictive capability through modeling for the specific class of scientific applications that are iterative, and thus, with periodicity in their memory access patterns. We observe that some others have also considered utilizing periodic behavior, although for very different applications such as identifying basic blocks [22] and reuse signatures [23].

#### 2.4 Laplacian Mesh Smoothing

Mesh smoothing application is performed to improve the quality of the mesh so that accurate PDE solution can be obtained within a short execution time [24]. In mesh smoothing procedure, we first compute the initial mesh quality for a given mesh and do mesh smoothing to improve the mesh quality [25]. After smoothing, we compute the mesh quality again and if the overall mesh quality reached a desirable level, then we stop smoothing.

We use edge-length ratio [26], i.e., the ratio of minimum and maximum length

edges, as a mesh quality metric for computing the mesh quality in this study. The mesh quality for each vertex can be represented as an average quality metric value of triangles that are attached on the vertex. The mesh quality for entire region of the mesh can be computed by averaging all mesh quality values obtained from each vertex. The range of edge-length ratio mesh quality values is  $0 \sim 1$ . If the quality value for a triangle is closed to 1, we can say the triangle has a good shape, i.e., closed to equilateral triangle that we desire. The goal of mesh smoothing application will be maximizing the average quality values for each vertex.

For improving the quality of the mesh, we perform Laplacian smoothing to replace a vertex position using neighbored vertices coordinates. Suppose there is a vertex v we want to move and N neighbored vertices surrounding the vertex. If we represent the position for  $i^{th}$  neighbored vertex as  $p_i$ , the new position for  $\bar{p}_v$  will be

$$\overline{p}_v = \frac{1}{N} \sum_{i=1}^{N} p_i.$$

Figure 2.2 shows the initial mesh and the output mesh of Laplacian smoothing.

Figure 2.2: Laplacian smoothing performed on initial mesh. The vertex position inside the mesh was changed.

We would like to improve the performance of the Laplacian mesh smoothing by reordering the initial mesh. Each vertex will be reordered based on the initial mesh quality for each vertex and details will be described in Chapter 6.

#### Algorithm 1 Algorithm for Laplacian Mesh Smoothing

```

1: procedure Laplacian Smoothing(V, T)

2:

V \leftarrow \text{mesh vertex data}

T \leftarrow \text{mesh triangle data}

3:

quality = 0

4:

for i \leftarrow 1, V do

5:

6:

compute initial mesh quality for V[i]

quality = quality + q_{V[i]}

7:

end for

8:

Initial quality = \frac{1}{V}quality

9:

while Final quality < goal quality do

10:

for i \leftarrow 1, V do

11:

Laplacian Smoothing

12:

end for

13:

quality = 0

14:

for i \leftarrow 1, V do

15:

16:

compute final mesh quality for V[i]

17:

quality = quality + q_{V[i]}

18:

end for

Final quality = \frac{1}{V} quality

19:

end while

20:

21: end procedure

```

### 2.5 Mesh Reordering for Improving Mesh Smoothing Performance

Several researchers suggested mesh reordering scheme for improving mesh smoothing application performance. For example, Strout [27] and Hovland et al. [28] developed a Feasible Newton mesh optimization algorithm and benchmark. Their algorithm and benchmark employed both data and iteration reordering in order to improve cache performance. One finding of their research was that reordering of the input data can increase or decrease the number of iterations taken by the inexact Newton method and can affect its success or failure [29]. The reordering applied was a reordering of the vertices and elements in the mesh by applying a breadth-first search and reversing the order in which the vertices were visited. When data and iteration ordering were performed on the relevant hypergraphs, the reorderings were found to significantly decrease the number of cache misses in

all phases of code execution and resulted in significantly faster code [28]. However, less amount of reuse distance reducing were observed with their reordering schemes compared to our proposed reordering scheme. Experimental evaluation will show these results in Chapter 6. Shontz and Knupp [30] considered mesh vertex reordering techniques to reduce the total time required to improve the mesh quality. Vertex ordering was performed for the first iteration (static) and every iterations (dynamic). To reduce extra reordering time for dynamic cases, Park et al. [31] considered a priori vertex reordering which performs the vertex reordering only once when mesh smoothing is started. Unlike this study, we consider cache performance when a reordering technique is applied to mesh smoothing. We can gain the performance improvement since we reduce the reuse distances for mesh smoothing applications and the reduced reuse distance can improve cache performance [32].

Chapter 3

# Reuse Distance and Cache Miss Models

In this chapter, we develop a methodology to predict the cache miss rates from reuse distance models for HPC applications. We use the fact that our HPC applications often show periodic patterns in their memory behavior. We will show that the periodic behavior can be utilized to characterize the cache performance using reuse distances when it is running alone. This predictive cache miss models are tested for actual applications represented by NAS benchmarks. Experimental evaluation for our predictive cache miss models will be provided. Finally, we provide the summary of this chapter.

## 3.1 Modeling Cache Performance in an HPC application using $\alpha + \beta \sin(2\pi t \phi)$ function

In this section, we develop  $\alpha + \beta \sin(2\pi t\phi)$  models that seek to characterize periodic behavior that we expect is observable in regard to reuse distance and cache miss profiles of HPC applications. Starting from a brief description of our overall methodology, we develop reuse distance and cache miss models to predict and utilize cache miss rates in an application when it is running alone, i.e., without interference.

#### 3.1.1 Methodology

Our approach is based on studying the relationship between reuse distance and cache miss rates using a simple synthetic benchmark that we call CodeP which is described in later paragraphs. CodeP would be run on multicore system and data will be generated to find correlations on that particular system between miss rates and reuse distances. These data and regression analysis will be used to estimate values of parameters in the models that we propose later in this section. Our main conjecture is that even though these parameters are obtained using synthetic code data, they would also be equally valid for actual high performance data applications. This conjecture is tested later in Section 3.2. Below we provide the details of our synthetic benchmark and how the data are collected.

CodeP Synthetic Benchmark We would like to define a logical time unit to map to a series of discrete events. Let t be the logical time that corresponds to N memory references. Then, the reuse distance for time t is the average reuse distance observed in N memory accesses. Similarly, the number of cache misses for time t is given by the total number of cache misses observed in N memory accesses. Cache miss rates can be computed by dividing cache misses for time t by N. In this study, we use N = 20,000.

We develop a synthetic benchmark with built-in periodic behavior of memory accesses. It provides time-dependent data of measures such as the reuse distances and cache misses that we use to illustrate and develop our main contribution in Section 3.1. We call it CodeP and it generates R unique memory references that are repeated F number of times for a reuse distance equal to R and a set of observations of length  $F \times R$ .

The  $F \times R$  memory references generated by CodeP should be higher than the value of N that we use for memory references corresponding to a logical time interval of length t. To generate observations using CodeP, multiple runs will be made for different values of F and R such that  $F \times R$  is much bigger than N by factors of 10 or more. These observations will be used for regression of analysis to estimate parameters for  $\alpha + \beta \sin(2\pi t\phi)$  models.

#### Algorithm 2 CodeP

```

1: procedure CodeP(R, F)

2:

R \leftarrow \text{length of unique memory reference}

F \leftarrow \text{number of repetitions}

3:

for i \leftarrow 1, F do

4:

for j \leftarrow 1, R do

5:

access memory[j]

6:

end for

7:

end for

8:

9: end procedure

```

#### 3.1.2 Predictive Models

We start by developing a model based on observed values of reuse distances when a single application runs on a multicore without any interference. Next, we consider how this model could be used to derive a model for predicting cache misses.

In the rest of this section, we use simple illustrative examples based on CodeP, our synthetic benchmark. Further, we consider instances with small reuse distances in the range of  $10 \sim 50$ , and small frequencies in the range of  $10 \sim 100$  matched with the gem5 simulation of a conventional two level cache hierarchy with a very small 2KB cache. To estimate the parameters for the models that we will develop in next section, we use multiple runs of CodeP and their observed cache misses to generate the data set that we will use to estimate correlation.

$R_{A_i}$ : A Model for Reuse Distance from Observations for Application  $A_i$ . We now characterize periodic behavior in observed reuse distance profiles as an  $\alpha + \beta \sin(2\pi t\phi)$  model.

Consider an observed reuse distance profile  $OR_{A_i}$  for codeP(30, 10) as shown in Figure 3.1 by a solid line with a step-like shape. By applying an FFT to  $OR_{A_i}$ , we can obtain an frequency-domain representation in terms of dominant magnitudes and their frequencies:  $FFT(OR_{A_i}) = (M_1^R, M_2^R, I_1^R, I_2^R)$ . We can now construct a model  $R_{A_i}$  as follows:

$$R_{A_i} = M_1^R + M_2^R \times 2\sin(2\pi t \times abs(I_1^R - I_2^R)). \tag{3.1}$$

Here in the  $\alpha + \beta \sin(2\pi t\phi)$  notation,  $\alpha = M_1^R$  represents the average reuse distances

Figure 3.1: Observed reuse distance profile(solid line) and its sine function model(dash-dot line) for CodeP(30, 10) application.

observed in  $OR_{A_i}$ , and  $\beta = M_2^R$  represents the deviation of the reuse distance from the average reuse distance value while  $\phi = abs(I_1^R - I_2^R)$  is the frequency. For the observed data shown by the solid line in Figure 3.1, this method yields the model  $R_{A_i} = 29.39 + 8.94 \sin(2\pi t \times 10)$ , which is also shown in Figure 3.1 as a dash-dot line. Note that from our model, the average reuse distance is 29.39 which is within 0.02% error of the actual reuse distance of 30 from CodeP(30, 10). Further, observe that although the model does not capture the corners in Figure 3.1 of the original data, we conjecture that it may be sufficiently accurate to bring predictive ability for co-scheduling applications.

$\overline{C}_{A_i}$ : A Predictive Model for Cache Misses derived from  $R_{A_i}$ . Given an observed cache miss profile  $OC_{A_i}$  of application  $A_i$ , we could develop its corresponding model  $C_{A_i}$  as we had developed  $R_{A_i}$  from the observed  $OR_{A_i}$ . However, this would require the trace data observed by running application  $A_i$  on a given multicore. To limit such experimental runs and corresponding observations, we would like in general to be able to derive a predictive model for cache misses  $\overline{C}_{A_i}$  using only the  $R_{A_i}$  model of its reuse distance. Additionally, we would need a small set of "training data" to characterize how reuse distances correspond to cache misses for a given multicore. If this method is successful, then we could easily derive predictive models for cache miss rates for an application on a given

multicore starting from only its reuse distance profile. Further, in some cases, the reuse distance profile of an application can be derived through our analysis. In such cases, no observations are needed with the application to predict its cache behavior, thus adding to predictive capabilities.

For illustrative purposes, consider data that show average cache miss rates corresponding to average reuse distances from a gem5 simulation of a multicore with two level caches of very small size at 2KB. Figure 3.2 shows these data as points and the linear model from regression between reuse distance and cache misses as a line.

Figure 3.2: Correlation between reuse distance and cache misses for a multicore with 2KB cache. Consider for example, cache misses of 1,500 corresponding to a reuse distance of 60, 24 times the reuse distance value.

Consider the reuse distance model that we derived earlier for CodeP(30, 10), namely  $R_{A_i} = 29.39 + 8.94 \sin(2\pi t \times 10)$ . We conjecture that the miss rates will correspond to the average reuse distances when scaled by a factor of 24 from Figure 3.2, and we expect that the dominant frequencies for both reuse distance and cache misses to be the same to give  $\overline{C}_{A_i} = 705.69 + 107.28 \sin(2\pi t \times 10)$ . Although  $\overline{C}_{A_i}$  is a profile, we can easily recover the cache miss and rates. Recall that t corresponds to N memory references, we use N = 20,000, i.e., now the average cache miss rates is given by 705.69/20,000 ( $\alpha/N$ ) at 3.53%. This approach is illustrated for CodeP(30,10) in Figure 3.3, where the dash-dot line is the predicted

$\overline{C}_{A_i}$  and the actual observed misses  $OC_{A_i}$  are shown by a solid line.

Figure 3.3: Observed cache miss profile (solid line) and its sine function model(dash-dot line) for CodeP(30, 10) application running on a system with cache size 2KB.

**Summary.** Our predictive models are developed for an application  $A_i$  using only its observed reuse distance combined with certain model parameter estimates obtained by regression analysis of observed reuse distances and cache misses for its synthetic CodeP. Observed cache miss rates including  $OC_{A_i}$  are used solely to evaluate the quality of corresponding models, namely  $\overline{C}_{A_i}$ .

We have presented our key ideas in terms of very simple  $\alpha + \beta \sin(2\pi t\phi)$  models. However, we expect that our method can be easily generalized to produce more complex representations of periodic functions when appropriate.

#### 3.2 Experimental Results

In this section, we examine the predictive capabilities of our models and evaluate model accuracy. We start with a description of our experimental setup. We then verify our models for predicting cache miss rates when an application is running alone, i.e., with no interference.

#### 3.2.1 Experimental Setup

System and Simulation. We used the gem5 simulation framework [33] to collect detailed reuse distances, cache misses, and interference statistics for evaluating our  $\alpha + \beta \sin(2\pi t\phi)$  models. We test two different types of computer system architectures.

We simulated a conventional computer architecture system that has a two level cache hierarchy. L1 cache was set up as private and L2 cache and all lower level memory hierarchy components were set up as shared. The L1 cache size is 32KB for instruction cache, 32KB for data cache and L2 cache size is 512KB for unified cache of both instruction and data. All caches have a 64-byte line size and utilize an LRU replacement policy. Private L1 caches are 8-way set associative and shared L2 cache has 16-way set associativity.

We also considered a Network-on-Chip (NoC) architecture to test the validity of our predictive cache miss models for S-NUCA. The network topology was set up as a mesh with 4 mesh rows. A private 32KB L1 data cache, a private 32KB instruction cache and a shared 512KB L2 cache were set up for NoC architecture simulation. The associativity for L1 and L2 are 8 and 16 respectively.

**Test Suite.** Seven HPC applications are selected from the NAS Parallel Benchmark suite [34] for testing our methodology, namely, Conjugate Gradient (CG), Multigrid (MG), Integer Sort (IS), Lower Upper diagonal (LU), Scalar Pentadiagonal (SP), Block Tri-diagonal (BT), and Fast fourier Transform (FT), with class A workloads. The descriptions for each application are as follow:

- Conjugate Gradient (GC) Computes an estimation of the smallest eigenvalue of a large sparse symmetric positive-definite matrix.

- Multigrid (MG) Solves a three-dimensional discrete Poisson equation.

- Integer Sort (IS) Sorts the particles to the appropriate place in a particle method application.

- Lower Upper Diagonal (LU) Solves a regular sparse LU triangular system using a symmetric successive over-relaxation method.

- Scalar Penta-diagonal (SP) Solves a nonlinear PDE using scalar pentadiagonal kernel.

- Block Tri-diagonal (BT) Solves a nonlinear PDE using block tridiagonal kernel.

- Fast Fourier Transform (FT) Solves a three-dimensional PDE using discrete fast Fourier Transform.

Labels assigned for each application are shown in Table 3.1.

| Benchmark | IS    | MG    | CG    | SP    | BT    | FT    | LU    |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| Label     | $A_1$ | $A_2$ | $A_3$ | $A_4$ | $A_5$ | $A_6$ | $A_7$ |

Table 3.1: Set of applications used for our model verification.

**Model Parameter Estimation.** We need to estimate values of parameter  $k_1$  in for the cache miss model of the form  $\overline{C}_{A_i} = k_1 R_{A_i}$  without interference. We use multiple runs of CodeP to first obtain the dataset that is then used to fit a line using regression as discussed in Section 3.1.

$$\frac{k_1}{0.03445}$$

Table 3.2: Model parameters.  $k_1$  is used in  $\overline{C}_{A_i} = k_1 R_{A_i}$ .

## 3.2.2 Verification: Predicting Cache Misses from Models of Reuse Distance, i.e., $\overline{C}_{A_i} = k_1 R_{A_i}$ .

We first test our predictive cache miss model when there is no interference during the execution of a given application. Table 3.3 shows our reuse distance and cache miss models for all applications. Figure 3.4(a), 3.4(b), 3.4(c), 3.4(d), 3.4(e), 3.4(f), and 3.4(g) show the details of reuse distance model results when compared to the observed reuse distance profiles for  $IS(A_1)$ ,  $MG(A_2)$ ,  $CG(A_3)$ ,  $SP(A_4)$ ,  $BT(A_5)$ ,  $FT(A_6)$ , and  $LU(A_7)$ . Our modeled average reuse distances match to observed values with errors of 0.0008%, 0.00076%, 0.01%, 0.001%, 0.00066%, 0.00071%,

| $\alpha + \beta \sin(2\pi t\phi)$ Models |            |          |        |

|------------------------------------------|------------|----------|--------|

| Reuse Distance $(10^3)$                  |            |          |        |

|                                          | $\alpha$   | β        | $\phi$ |

| $R_{IS}$                                 | 69.177     | 25.747   | 12     |

| $R_{MG}$                                 | 43.994     | 7.392    | 42     |

| $R_{CG}$                                 | 126.719    | 7.628    | 853    |

| $R_{SP}$                                 | 65.395     | 22.974   | 208    |

| $R_{BT}$                                 | 17.948     | 10.302   | 21     |

| $R_{FT}$                                 | 11.807     | 3.581    | 26     |

| $R_{LU}$                                 | 57.196     | 15.683   | 669    |

|                                          | Cache Miss |          |        |

|                                          | $\alpha$   | $\beta$  | $\phi$ |

| $\overline{C}_{IS}$                      | 2383.15    | 887.75   | 12     |

| $\overline{C}_{MG}$                      | 1515.62    | 254.683  | 42     |

| $\overline{C}_{CG}$                      | 4365.5     | 262.8156 | 853    |

| $\overline{C}_{SP}$                      | 2252.88    | 791.46   | 208    |

| $\overline{C}_{BT}$                      | 618.34     | 354.93   | 21     |

| $\overline{C}_{FT}$                      | 406.78     | 123.35   | 26     |

| $\overline{C}_{LU}$                      | 1970.41    | 540.303  | 669    |

Table 3.3: Reuse distance models derived from FFT conversion of observed reuse distance profiles,  $R_{A_i} = FFT(OR_{A_i})$ , and cache miss models derived from  $\overline{C}_{A_i} = k_1 R_{A_i}$ , where  $k_1 = 0.03445$ , for all applications when they are run alone, with no interference.

and 0.00095%, respectively for IS, MG, CG, SP, BT, FT, and LU, thus, verifying them as being highly accurate.