### The Pennsylvania State University

The Graduate School

College of Engineering

### ZNO THIN FILM ELECTRONICS FOR MORE THAN DISPLAYS

A Dissertation in

**Electrical Engineering**

by

Jose Israel Ramirez

© 2015 Jose Israel Ramirez

Submitted in Partial Fulfillment

of the Requirements

for the Degree of

Doctor of Philosophy

August 2015

The dissertation of Jose Israel Ramirez was reviewed and approved\* by the following:

Thomas N. Jackson Robert E. Kirby Chair Professor of Electrical Engineering Dissertation Adviser Chair of Committee

Suman Datta Professor of Electrical Engineering

Susan Trolier-McKinstry

Professor of Electrical Engineering and Ceramic Science and Engineering

Mark W. Horn Associate Professor of Engineering Science and Mechanics

Kultegin Aydin Professor of Electrical Engineering Department Head

<sup>\*</sup>Signatures are on file in the Graduate School.

### **Abstract**

Zinc oxide thin film transistors (TFTs) are investigated in this work for large-area electronic applications outside of display technology. A constant pressure, constant flow, showerhead, plasma-enhanced atomic layer deposition (PEALD) process has been developed to fabricate high mobility TFTs and circuits on rigid and flexible substrates at 200 °C. ZnO films and resulting devices prepared by PEALD and pulsed laser deposition (PLD) have been compared. Both PEALD and PLD ZnO films result in densely packed, polycrystalline ZnO thin films that were used to make high performance devices. PEALD ZnO TFTs deposited at 300 °C have a field-effect mobility of ~ 40 cm²/V-s (and > 20 cm²/V-S deposited at 200 °C). PLD ZnO TFTs, annealed at 400 °C, have a field-effect mobility of > 60 cm²/V-s (and up to 100 cm²/V-s).

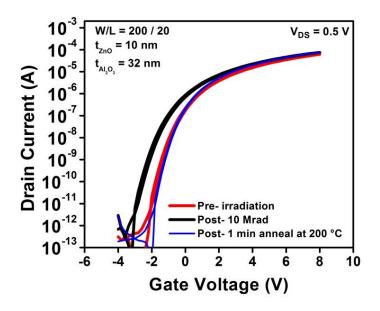

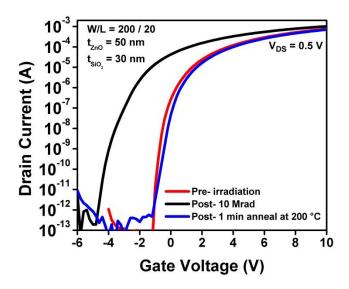

Devices, prepared by either technique, show high gamma-ray radiation tolerance of up to  $100 \, \text{Mrad}(\text{SiO}_2)$  with only a small radiation-induced threshold voltage shift ( $V_T \sim -1.5 \, \text{V}$ ). Electrical biasing during irradiation showed no enhanced radiation-induced effects. The study of the radiation effects as a function of material stack thicknesses revealed the majority of the radiation-induced charge collection happens at the semiconductor-passivation interface. A simple sheet-charge model at that interface can describe the radiation-induced charge in ZnO TFTs.

By taking advantage of the substrate-agnostic process provided by PEALD, due to its low-temperature and excellent conformal coatings, ZnO electronics were monolithically integrated with thin-film complex oxides. Application-based examples where ZnO electronics provide added functionality to complex oxide-based devices are presented. In particular, the integration

of arrayed lead zirconate titanate (Pb(Zr, Ti)O<sub>3</sub> or PZT) thin films with ZnO electronics for microelectromechanical systems (MEMs) and deformable mirrors is demonstrated. ZnO switches can provide voltage to PZT capacitors with fast charging and slow discharging time constants. Finally, to circumvent fabrication challenges on predetermined complex shapes, like curved mirror optics, a technique to transfer electronics from a rigid substrate to a flexible substrate is used. This technique allows various thin films, regardless of their deposition temperature, to be transferred to flexible substrates.

Finally, ultra-low power operation of ZnO TFT gas sensors was demonstrated. The ZnO ozone sensors were optimized to operate with excellent electrical stability in ambient conditions, without using elevated temperatures, while still providing good gas sensitivity. This was achieved by using a post-deposition anneal and by partially passivating the contact regions while leaving the semiconductor sensing area open to the ambient. A novel technique to reset the gas sensor using periodic pulsing of a UV light over the sensor results in less than 25 milliseconds recovery time. A pathway to achieve gas selectivity by using organic thin-film layers as filters deposited over the gas sensors tis demonstrated. The ZnO ozone sensor TFTs and the UV light operate at room temperature with an average power below 1  $\mu$ W.

# Table of Contents

| List of Figures                                                                  | vii |

|----------------------------------------------------------------------------------|-----|

| Acknowledgements                                                                 | xv  |

| Chapter 1                                                                        | 1   |

| 1.1 Introduction and Background                                                  | 1   |

| Chapter 2                                                                        | 7   |

| 2.1 Thin Film Deposition Processes for Oxide Semiconductors                      | 7   |

| 2.2 Showerhead Plasma-Enhanced Atomic Layer Deposition                           | 9   |

| 2.2.1 Showerhead PEALD Thin Film Properties and Devices                          | 15  |

| 2.2.2 Typical ZnO Thin Film Transistors                                          | 25  |

| 2.3 Pulsed Laser Deposition                                                      | 27  |

| 2.3.1 ZnO Thin Film Transistors with Active layer Deposited by PLD               | 29  |

| 2.4 Materials Comparison of PEALD and PLD ZnO Thin Films                         | 31  |

| Chapter 3                                                                        | 40  |

| 3.1 Radiation-Hard ZnO TFTs                                                      | 40  |

| 3.1.1 ZnO Device Structures under Radiation Test                                 | 42  |

| 3.1.2 Accounting for Non-idealities in ZnO devices for Accurate Parameterization | 43  |

| 3.2 <sup>60</sup> Co Irradiation of Electrically Unbiased ZnO TFTs               | 44  |

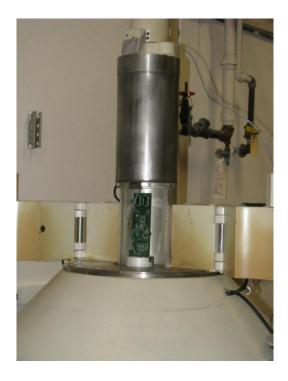

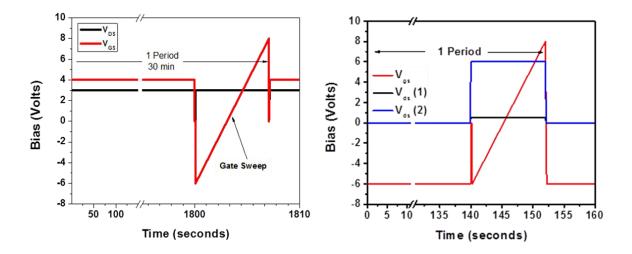

| 3.3 Hardware and Software Setup for In-Situ Radiation Testing                    | 47  |

| 3.4 Electrically Biased and <sup>60</sup> Co Irradiated ZnO TFTs                 | 50  |

| 3.5 Measurement Artifacts during In-Situ Irradiation                             | 53  |

| 3.6 Wider Irradiation Dose Range                                                 | 57  |

| 3.7 Physical Location of Radiation-Induced Changes in ZnO TFTs                   |     |

| Chapter 4                                                                        | 67  |

| 4.1 Integration of ZnO Electronics with Complex Oxides Thin Films                | 67  |

| 4. 2 Integrating AZO Thin Films with BST Thin Films on Alumina Substrates        | 69  |

| 4.2.1 Al-doped ZnO Thin Films Deposited by Atomic Layer Deposition (ALD)         | 70  |

| 4.3 Integrating ZnO Thin Film Transistors with PZT Thin Films                         | 74        |

|---------------------------------------------------------------------------------------|-----------|

| 4.3.1 Addressing Many PZT Elements in a Row-Column Scheme                             | 75        |

| 4.3.2 Co-Processing ZnO TFTs and PZT Capacitors                                       | 76        |

| 4.3.3 Integration of ZnO Ring Oscillators to Actuate PZT Cantilevers                  | 81        |

| 4.3.3.1 ZnO Ring Oscillator Circuit Simulation, Design and Layout                     | 81        |

| 4.4 Integrated ZnO-PZT Thin Films for Adaptive Optics X-ray Telescopes                | 87        |

| 4.4.1 Mask Design of ZnO TFTs Controlling PZT Actuators for Adaptive Optics           | 91        |

| 4.4.2 Adaptive Optics Array with integrated Electrostatic Discharge (ESD) Input Prote | ection 94 |

| 4.4.3 Integrating ZnO Electronics on Curved Mirrors                                   | 101       |

| Chapter 5                                                                             | 106       |

| 5.1 Ultra-Low Power ZnO Ozone Sensors Using Pulsed UV Light                           | 106       |

| 5.2 Electrical Stability of ZnO TFT Gas Sensors                                       | 107       |

| 5.3 Ozone Sensing Test Setup                                                          | 113       |

| 5.4 Ozone Gas Sensor Recovery using UV Light                                          | 114       |

| 5.5 Towards Gas Selectivity                                                           | 117       |

| Chapter 6                                                                             | 119       |

| 6.1 Conclusions                                                                       | 119       |

| 6.2 Future Work                                                                       | 120       |

| Appendix A: List of Symbols                                                           | 125       |

| Appendix B: Elements and Element Compounds                                            | 126       |

| Appendix C: Abbreviations                                                             | 127       |

| References                                                                            | 128       |

# **List of Figures**

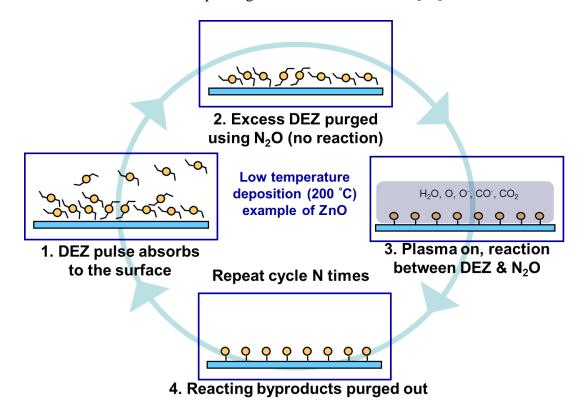

| Figure 1. An example of a plasma-enhanced atomic layer deposition (PEALD) cycle to deposit ZnO using diethylzinc (DEZ) as the zinc precursor and a weak oxidant (N <sub>2</sub> O in this example) as both oxidizer (when the plasma is tuned-on) and purge gas                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

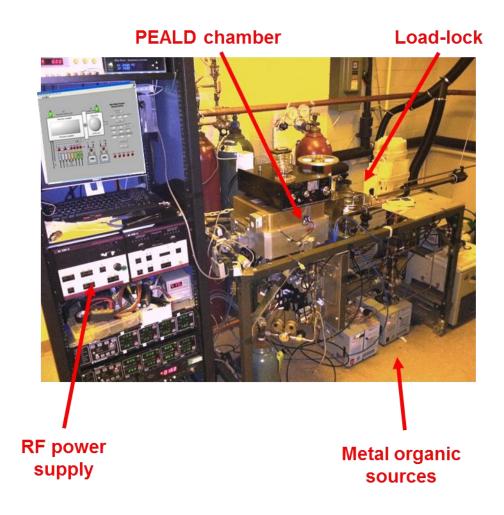

| Figure 2. A picture of the showerhead PEALD deposition system with a load-lock chamber. The load-lock chamber was added to the system to minimize moisture in the deposition chamber. A custom-made LabView program was developed to control various deposition parameters 12                                                 |

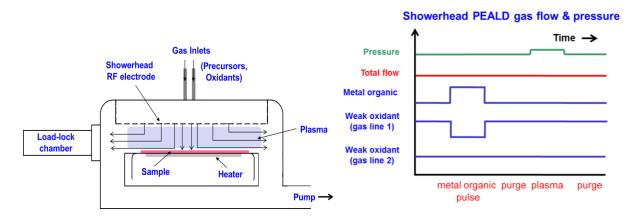

| Figure 3 (left) Modified Applied Materials P5000 chamber used as a PEALD chamber. The system can handle substrates up to 20 cm; (right) schematic of the pressure and gas flow as a function of time used to operate the showerhead deposition system                                                                         |

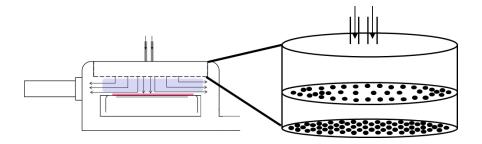

| Figure 4. A detailed schematic of the plenums in the showerhead. The showerhead consists of two plenums with spatially asymmetric holes in the innermost showerhead and spatially equidistant holes in the showerhead dispensing the gas to the sample                                                                        |

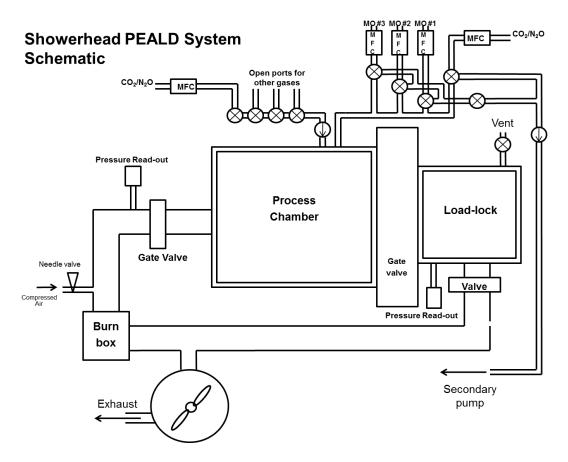

| Figure 5. A schematic of the showerhead PEALD system including the gas handling. The gas handling operates in a run/vent mode (either gases are introduced to the chamber or taken to the secondary pump).                                                                                                                    |

| Figure 6. Typical deposition parameters for optimized thin films deposited using the showerhead PEALD system                                                                                                                                                                                                                  |

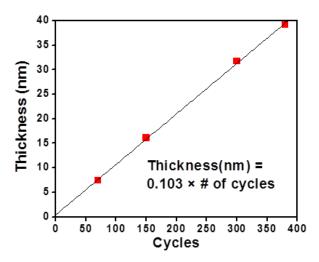

| Figure 7. Deposition rate of PEALD Al <sub>2</sub> O <sub>3</sub> using TMA precursor and CO <sub>2</sub> plasma at 200 °C. The deposition rate was found to be 0.103 nm per cycle                                                                                                                                            |

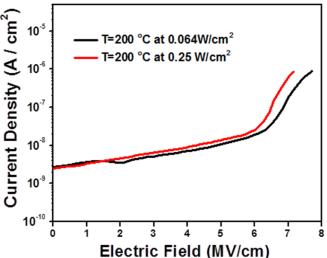

| Figure 8. (left) Deposition rate and refractive index for PEALD Al <sub>2</sub> O <sub>3</sub> are fairly insensitive to deposition parameters; (right) leakage current density as a function of applied field for Al <sub>2</sub> O <sub>3</sub> metal-insulator-metal structures deposited at two different power densities |

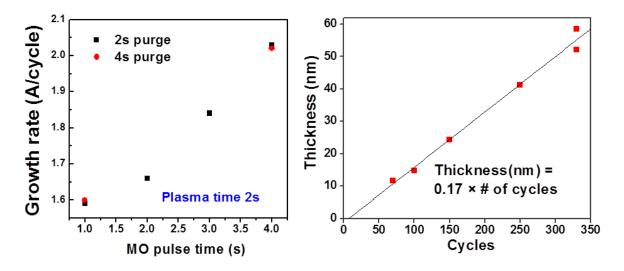

| Figure 9. Deposition rate of PEALD ZnO using DEZ precursor at 200 °C. (left) PEALD ZnO growth rate as a function of DEZ pulse time, the other parameters were fixed. (right) ZnO deposition rate is 0.17 nm per cycle and depended on the deposition parameters                                                               |

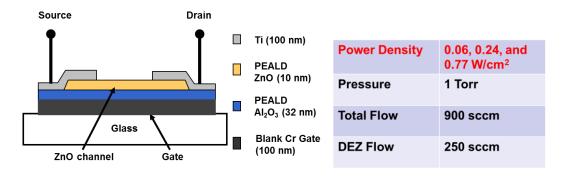

| Figure 10. (left) Unpatterned bottom-gate ZnO TFT cross-sectional schematic. This structure was used for rapid device fabrication; (right) Summary of deposition parameters used to deposit ZnO thin films                                                                                                                    |

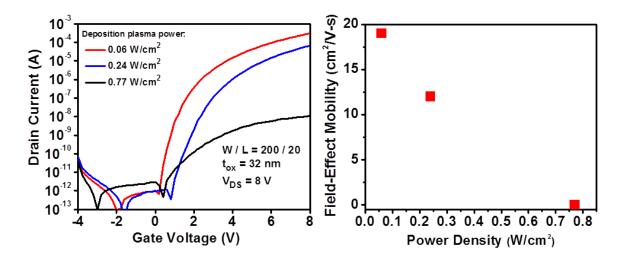

| Figure 11. (left) Linear region ( $V_{DS} = 0.5V$ ) $I_{DS}$ versus $V_{GS}$ for ZnO films deposited at different plasma power densities; (right) extracted linear-region field-effect mobility as a function of                                                                                                              |

| deposition power density. Low deposition power density for ZnO films yields higher electrical performance.                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

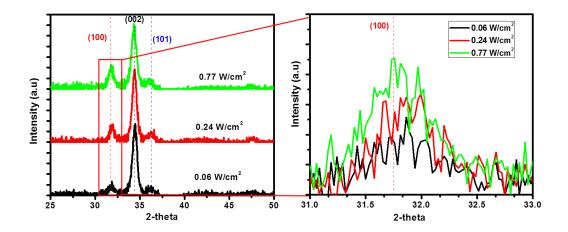

| Figure 12. 2-theta X-ray diffraction scan of PEALD ZnO thin films deposited at various plasma power densities according to Figure 10 (right) parameters. As the deposition power density decreases, the 100 peak diminishes with respect to the 002 peak                                                                                                                                                                                                                                                 |

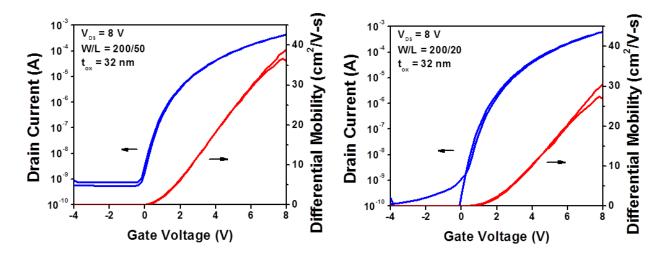

| Figure 13. (left) Saturation region ( $V_{DS} = 8$ V) $I_{DS}$ versus $V_{GS}$ for a ZnO TFT with the Al <sub>2</sub> O <sub>3</sub> gate dielectric deposited at 200 °C and the active layer deposited at 280 °C. The peak field-effect mobility was ~31 cm <sup>2</sup> /V-s. (right) $I_{DS}$ versus $V_{GS}$ for a ZnO TFT with, both, the Al <sub>2</sub> O <sub>3</sub> gate dielectric and the ZnO active layer deposited at 300 °C. The peak field-effect mobility was ~39 cm <sup>2</sup> /V-s. |

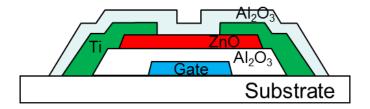

| Figure 14. Cross-sectional schematic of a patterned gate PEALD ZnO TFTs with Al <sub>2</sub> O <sub>3</sub> and ZnO as gate dielectric and active layer, respectively. The ZnO TFTs are completed with an ALD-based Al <sub>2</sub> O <sub>3</sub> passivation layer                                                                                                                                                                                                                                     |

| Figure 15. (left) Linear region ( $V_{DS}=0.5V$ ) $I_{DS}$ versus $V_{GS}$ for an ALD $Al_2O_3$ passivated ZnC TFT (W / L = 200 $\mu$ m / 20 $\mu$ m) with field-effect mobility over 20 cm <sup>2</sup> /V-s; (right) $I_{DS}$ versus $V_{DS}$ characteristics for several values of $V_{GS}$ .                                                                                                                                                                                                         |

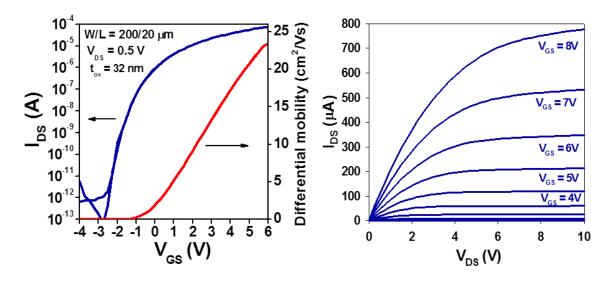

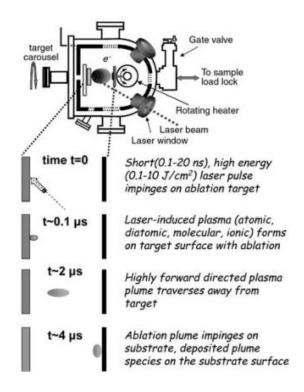

| Figure 16. Schematic of a PLD chamber and a schematic of the deposition process. Schematic taken from [51].                                                                                                                                                                                                                                                                                                                                                                                              |

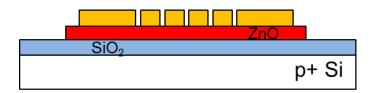

| Figure 17. Cross-sectional schematic of a blanket gate PLD ZnO TFTs with SiO <sub>2</sub> and ZnO as gate dielectric and active layer, respectively                                                                                                                                                                                                                                                                                                                                                      |

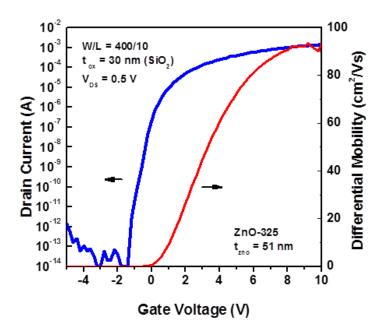

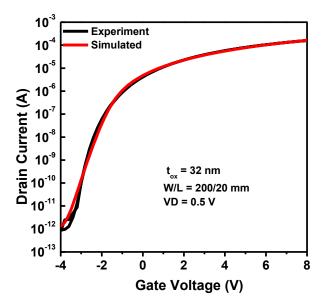

| Figure 18. Linear region ( $V_{DS}=0.5V$ ) $I_{DS}$ versus $V_{GS}$ for a PLD ZnO TFT (W / L = 200 $\mu$ m / 20 $\mu$ m) with a PECVD deposited SiO <sub>2</sub> gate dielectric. In this device the field-effect mobility is 90 cm <sup>2</sup> /V-s. The field-effect mobility measured in these devices ranged from 60-110 cm <sup>2</sup> /V-s 31                                                                                                                                                    |

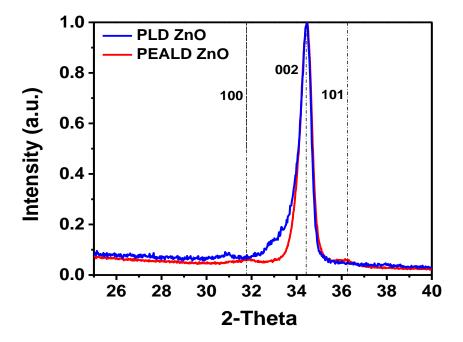

| Figure 19. Grazing incidence XRD of ZnO thin films (50 nm) deposited by PLD and PEALD both show highly textured films with (002) orientation and similar coherence length suggesting similar grain size. The coherence length for PEALD and PLD ZnO films is estimated, using Scherrer's equation, to be ~7 nm and ~7.2 nm, respectively                                                                                                                                                                 |

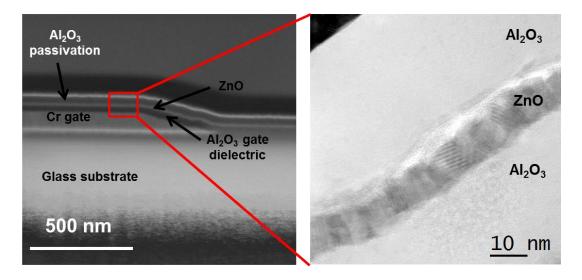

| Figure 20. (left) Scanning electron microscope (SEM) image of a PEALD ZnO TFT; (right) transmission electron microscope (TEM) over the channel region of the TFT. PEALD ZnO TFTs shows a densely packed polycrystalline structure with grain size of the order of the thickness (~10 nm)                                                                                                                                                                                                                 |

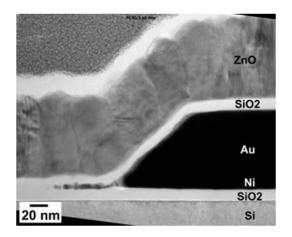

| Figure 21. Transmission electron microscope (TEM) of PLD ZnO TFT. The ZnO thin film shows a densely packed polycrystalline structure with grain size in the order of 20-40 nm 35                                                                                                                                                                                                                                                                                                                         |

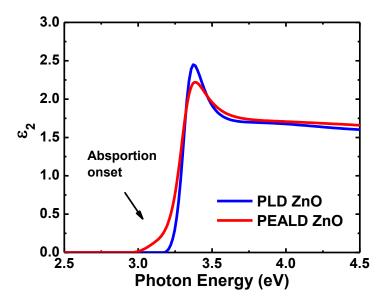

| Figure 22. Absorption coefficient extracted by parameterization using spectroscopic ellipsometry. PEALD ZnO films have a slower absorption onset than PLD ZnO films suggesting a broader tail-state distribution for PEALD ZnO films                                                                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

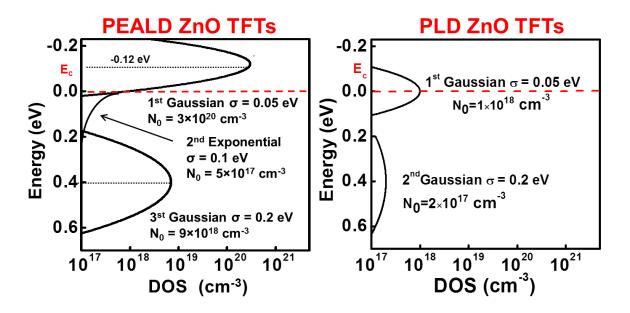

| Figure 23. Trap distributions used to fit the experimental data to model ZnO TFTs with active layers prepared by both PEALD and PLD                                                                                                                                                                               |

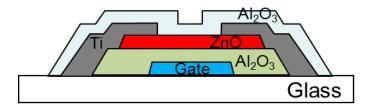

| Figure 24. Bottom-gate PEALD ZnO TFT schematic cross-section. The TFT uses a 100-nm Cr gate, 32-nm PEALD Al <sub>2</sub> O <sub>3</sub> gate dielectric, 10-nm PEALD ZnO active channel, Ti source-drain contacts, and 30-nm ALD Al <sub>2</sub> O <sub>3</sub> passivation layer fabricated on a glass substrate |

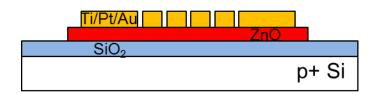

| Figure 25. Bottom gate PLD ZnO TFT schematic cross-section. The TFT uses a 30-nm PECVD SiO <sub>2</sub> gate dielectric, 50-nm PLD ZnO active channel, and Ti/Au source-drain contacts on Si as substrate and gate                                                                                                |

| Figure 26. Linear region ( $V_{DS} = 0.5 \text{ V}$ ) $I_D$ versus $V_{GS}$ for a PEALD ZnO TFT before irradiation, after 10 Mrad(SiO <sub>2</sub> ) $^{60}$ Co gamma ray irradiation, and after irradiation and a 200 $^{\circ}$ C, 1 min anneal in air                                                          |

| Figure 27. Linear region ( $V_{DS} = 0.5 \text{ V}$ ) $I_D$ versus $V_{GS}$ for a PLD ZnO TFT before irradiation, after 10 Mrad(SiO <sub>2</sub> ) $^{60}$ Co gamma ray irradiation, and after irradiation and a 200 $^{\circ}$ C, 1 min anneal in air                                                            |

| Figure 28. Comparison of device characteristics for PEALD and PLD ZnO TFTs before and after 10 Mrad(SiO <sub>2</sub> ) gamma ray irradiation                                                                                                                                                                      |

| Figure 29. (left) In-situ bias sample fixture with integrated thermocouple. (right) Sample fixture loaded in <sup>60</sup> Co gamma cell                                                                                                                                                                          |

| Figure 30. Measurement setup for in-situ measurement of ZnO TFTs modified for increased multiplexing capabilities                                                                                                                                                                                                 |

| Figure 31. The original timing diagram shown on the left is from the prior period of performance and limited to a sampling rate of about 30 minutes. The timing diagram on the right depicts the system improvements with sampling rates of about 2 minutes and multiple drain bias configurations.               |

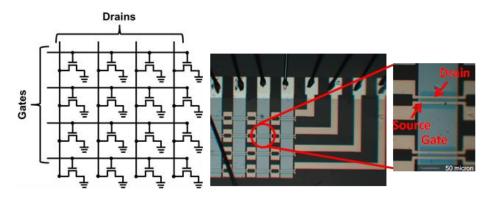

| Figure 32. Circuit schematic and optical micrograph of the 4x4 array of PEALD ZnO TFTs used in electrical bias and radiation measurements.                                                                                                                                                                        |

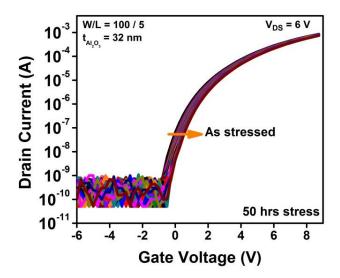

| Figure 33. A group of $I_D$ versus $V_{GS}$ curves in saturation region ( $V_{DS} = 6$ ) for a PEALD ZnO TFT stressed for 50 hours. A $\Delta V_{ON}$ of +0.5 V and a $\Delta V_T$ +0.2 V was observed                                                                                                            |

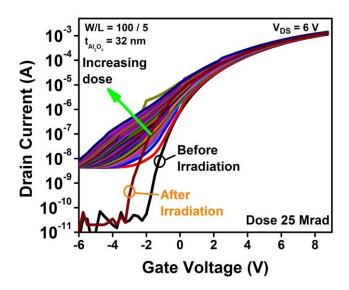

| Figure 34. A group of $I_D$ versus $V_{GS}$ curves in saturation region ( $V_{DS}=6$ V) for a PEALD ZnO TFT electrically stressed and exposed to a cumulative dose of 25 Mrad(SiO <sub>2</sub> ), equivalent to 50 hours. After 25 Mrad(SiO <sub>2</sub> ) a $\Delta V_{ON}$ of -1.1 V and a $\Delta V_T$ +0.6 V was observed                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

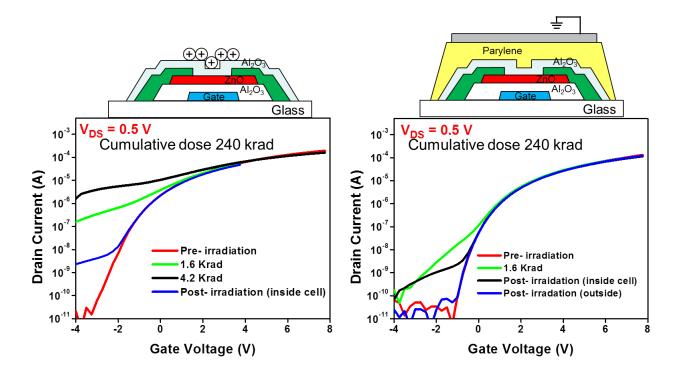

| Figure 35. (left) Bottom gate PEALD ZnO TFT (same structure as used in previous experiments) and $I_{DS}$ versus $V_{GS}$ ( $V_{DS} = 0.5$ V) showing a rapid increase in subthreshold current after only several krad dose. (right) The same TFT structure as used before but with an additional low-k dielectric and a conductive film over it connected to ground. $I_D$ versus $V_{GS}$ ( $V_{DS} = 0.5$ V) for a PEALD ZnO TFT with the top surface shielded. Both structures were exposed to 240 krad(SiO <sub>2</sub> ). Anomalies in the low current region are reduced with proper shielding |

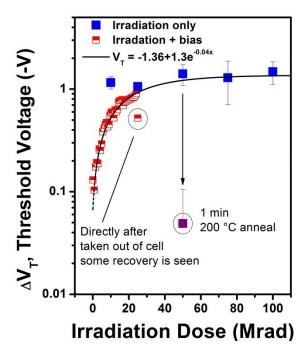

| Figure 36. Threshold voltage as function of irradiation dose for irradiation only and irradiation with electrical bias for doses to 100 Mrad(SiO <sub>2</sub> ). A 1 minute anneal at 200 °C nearly removes the radiation-induced V <sub>T</sub> shift                                                                                                                                                                                                                                                                                                                                                |

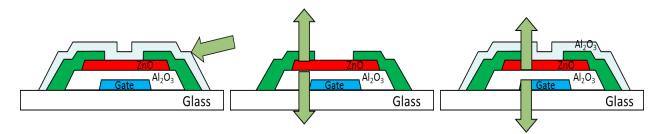

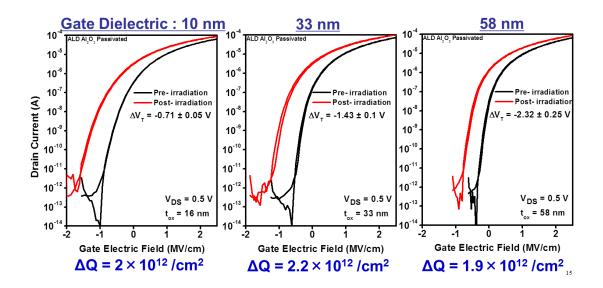

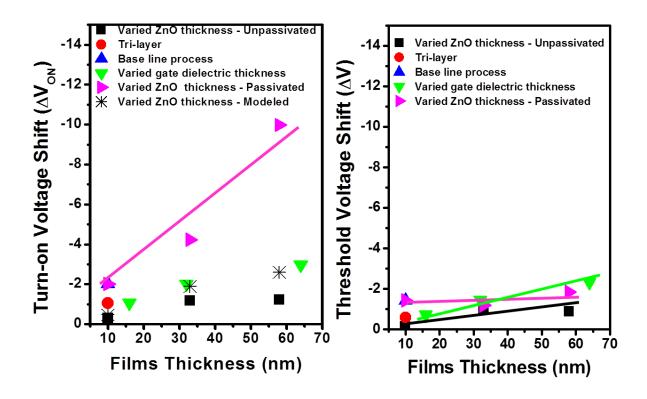

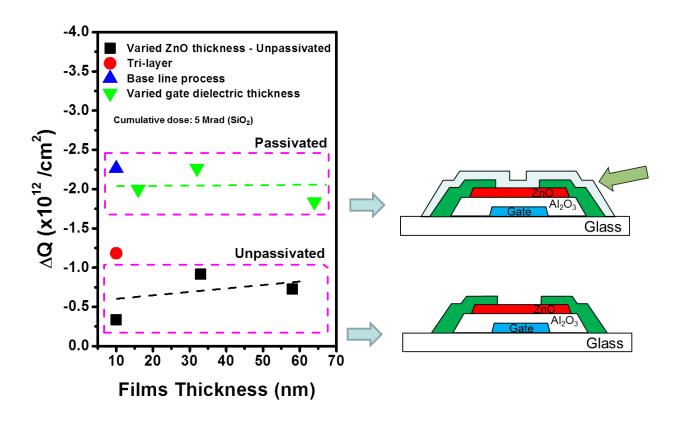

| Figure 37. Multiple device permutations were studied for PEALD ZnO TFTs to understand which interface was affected the most by irradiation                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

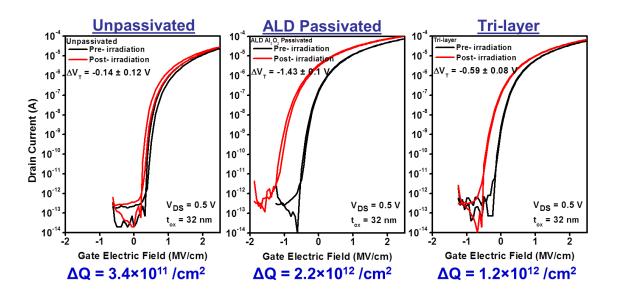

| Figure 38. PEALD ZnO TFTs with different passivation schemes. Passivation variations result in significant changes in radiation-induced charge                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

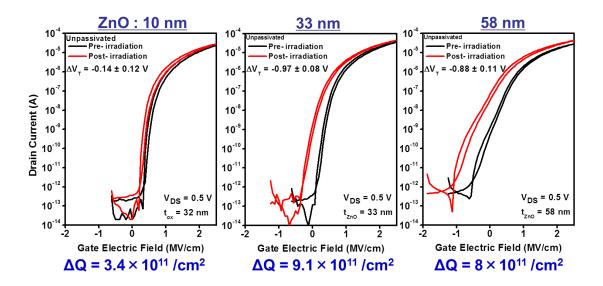

| Figure 39. PEALD ZnO TFTs with active channel thicknesses and no passivation. ZnO film thickness variations result in some variation of radiation-induced charge after 5 Mrad (SiO <sub>2</sub> ) 62                                                                                                                                                                                                                                                                                                                                                                                                  |

| Figure 40. PEALD ZnO TFTs with varying gate dielectric thickness, fixed active channel thickness, and same ALD passivation. Gate dielectric thickness variations result in negligible change in charge for 5 Mrad (SiO <sub>2</sub> ) dose                                                                                                                                                                                                                                                                                                                                                            |

| Figure 41. Summary of changes in $V_{ON}$ (left) and $V_{T}$ (right) as a function of process varients for TFTs exposed to 5 Mrad (SiO <sub>2</sub> ) of $^{60}$ Co gamma radiation                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 42. Summary of changes in charge showing passivation/ZnO interface is most critical. 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

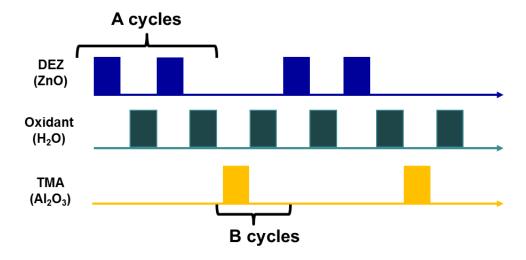

| Figure 43. Schematic of the deposition sequence used to deposit Al-doped ZnO by ALD 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

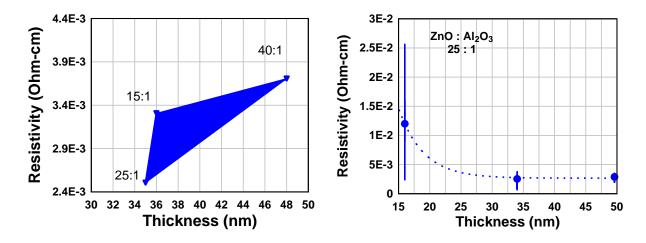

| Figure 44. (left) Lateral resistivity of Al-doped ZnO thin films as a function of ZnO: $Al_2O_3$ cycles; (right) at a fixed 25:1 ratio of ZnO: $Al_2O_3$ cycles, resistivity as a function of thickness was examined. Films over > 30 nm show the lowest resistivity                                                                                                                                                                                                                                                                                                                                  |

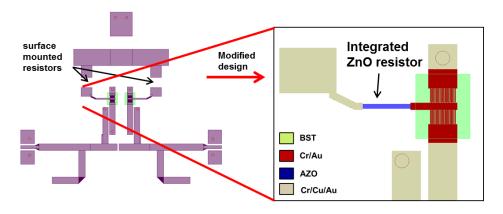

| Figure 45. BST-based two-pole tunable X-band filter with integrated Al-doped ZnO resistor 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

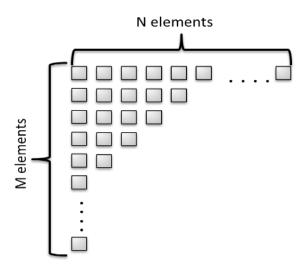

| Figure 46. Connections to M×N + 1 elements can be reduced to M+N+1 connections by using a transistor connected to each element                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

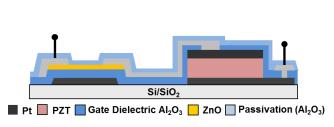

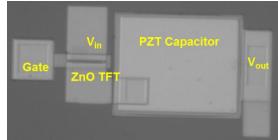

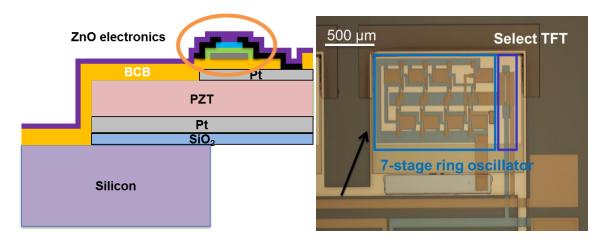

| Figure 47. (left) Cross-sectional schematic of a ZnO TFT monolithically integrated with a PZT capacitor; (right) Top-view, optical micrograph of the integrated ZnO TFT-PZT capacitor 77                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 48. Side-view SEM images comparing PZT sidewall damage for (left) unoptimized and (right) optimized dry etching conditions                                                                                                                                                                                               |

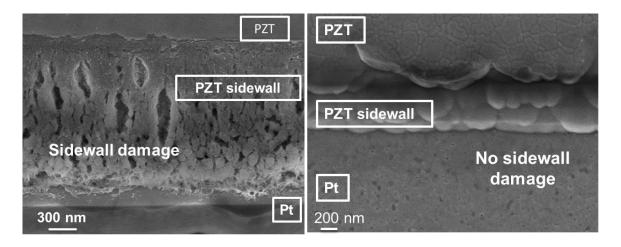

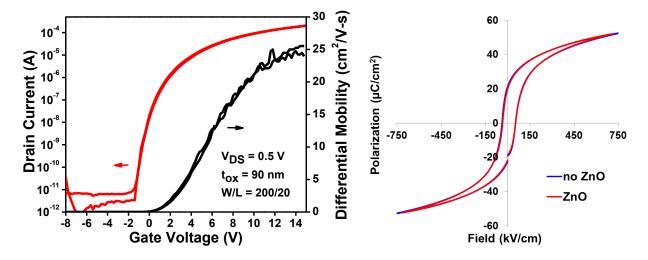

| Figure 49. (left) Linear region ( $V_{DS} = 0.5 \text{ V}$ ) $I_{DS}$ versus $V_{GS}$ of a discrete ZnO TFT with W/L = $200/20 \mu m$ co-fabricated with PZT capacitors; (right) polarization as a function of applied field (P-E) for PZT capacitors pre- and post- ZnO TFT fabrication show nearly identical characteristics. |

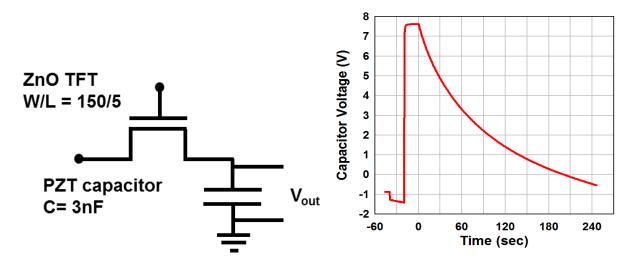

| Figure 50. (left) Schematic of ZnO TFT with a W/L ratio of 150/50 connected to a 3 nF PZT thin film capacitor; (right) The capacitor's voltage as a function of time after applying voltage through the ZnO TFT. A charging and discharging time constant of ~ 3 msecs and 70 secs was found, respectively.                     |

| Figure 51. Linear region (VDS = $0.5$ ) $I_{DS}$ versus $V_{GS}$ comparison of experimental and AIMSpice simulated ZnO TFT                                                                                                                                                                                                      |

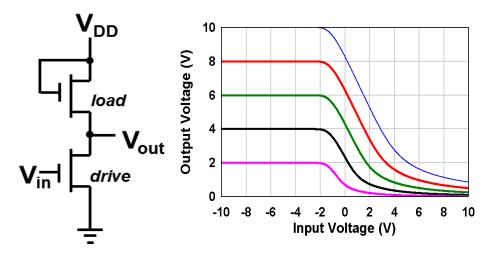

| Figure 52. (left) A circuit schematic for a saturated-load inverter. The simulated ZnO inverter has a $\beta_{ratio} \sim 12$ ; (right) logic transition curves at various supply voltages                                                                                                                                      |

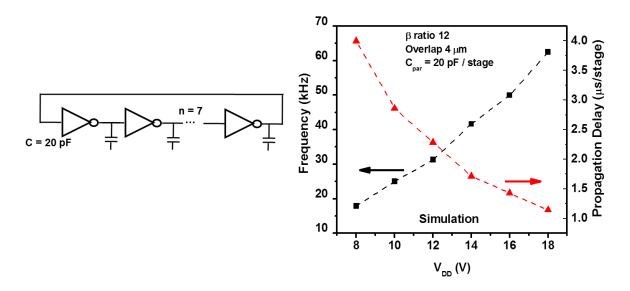

| Figure 53. (left) Circuit schematic of a simulated 7-stage ring oscillator with a capacitor on each stage to match the resonating frequency of the PZT cantilevers; (right) frequency as a function of supply voltage for the simulated ring oscillator                                                                         |

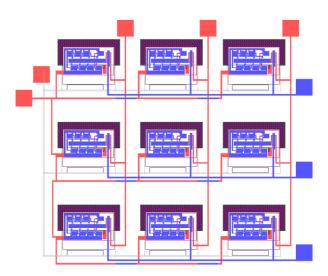

| Figure 54. Layout schematic of a 3×3 array of PZT cantilevers with ZnO ring-oscillators on top each cantilever.                                                                                                                                                                                                                 |

| Figure 55. (left) Cross-sectional schematic of PZT cantilevers on a Si substrates with ZnO electronics fabricated right on top of the cantilever. (right) Top-view optical micrograph of a 7-stage ring-oscillator with a select TFT in a 3x3 elements array                                                                    |

| Figure 56. Representative video frames of the deflection of a PZT cantilever integrated with the ZnO electronics                                                                                                                                                                                                                |

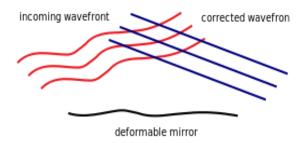

| Figure 57. Schematic of adaptive optics used to correct aberrations of an incoming wavefront. "Deformable mirror correction" Licensed under CC BY-SA 3.0 via Wikimedia Commons 87                                                                                                                                               |

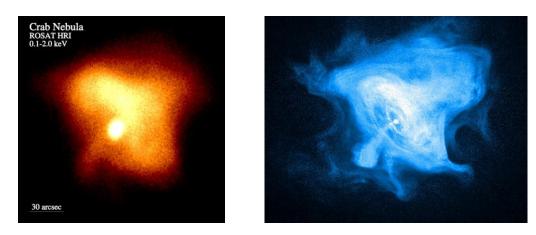

| Figure 58. X-ray images of the Crab Nebula from (left) ROSAT and (right) Chandra. (ROSAT Credit: S.L. Snowden, NASA/GSFC. Chandra Credit: NASA/CXC/SAO)                                                                                                                                                                         |

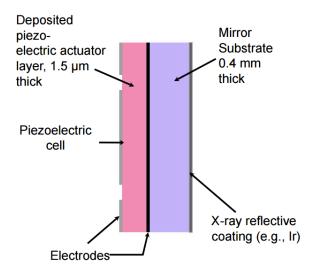

| Figure 59. A cross-sectional schematic of mirror with PZT piezoelectric cells to correct for incoming wavefront aberrations. Photo taken from "Integrated Control Electronics for                                                                                                                                               |

| Adjustable X-ray Optics" S. Trolier-McKinstry. Early State Technology Workshop, Astrophysics and Heliophysics                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

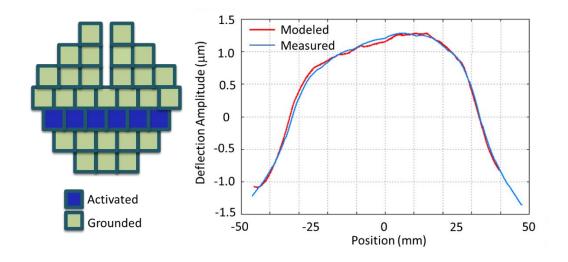

| Figure 60. (left) 33 PZT elements with separate connections. A voltage was applied to 6 actuators in a row. (right) Comparison of the experimental and modeled influence functions for 6 PZT actuators. Figures taken from reference [113]                                                                          |

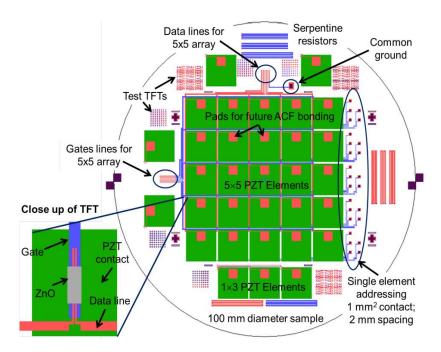

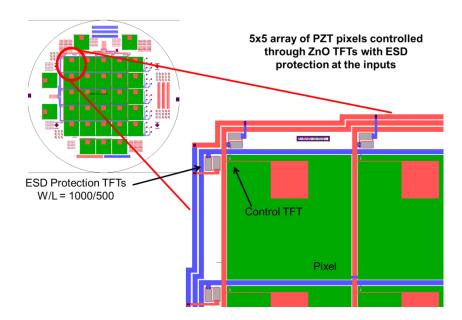

| Figure 61. A mask design for a 5×5 array of PZT elements with ZnO TFTs integrated to address the array in a row-column scheme                                                                                                                                                                                       |

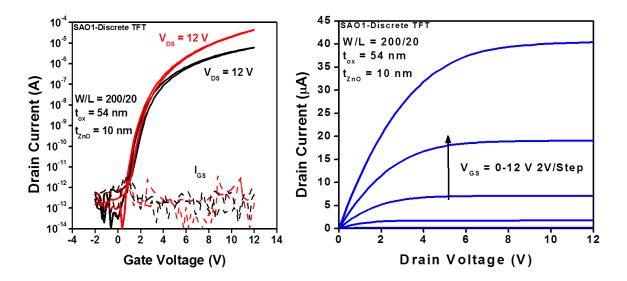

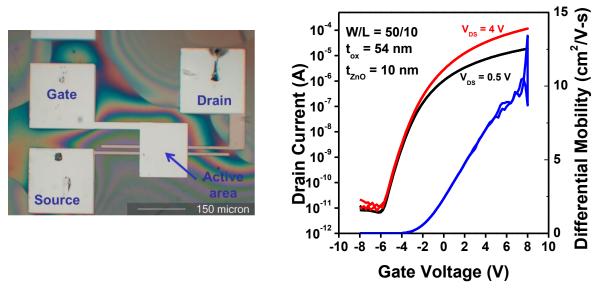

| Figure 62. (left) I <sub>DS</sub> versus V <sub>GS</sub> for a discrete ZnO TFT co-processed with PZT actuators for adaptive optics (right) I <sub>DS</sub> versus V <sub>DS</sub> for the same discrete ZnO TFT. The gate dielectric is 54 nm thick.                                                               |

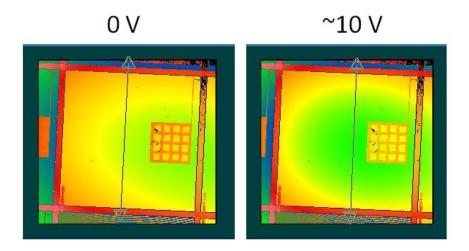

| Figure 63. (Left) An optical profilometer image of a 1-cm <sup>2</sup> pixel with no voltage applied to it (0 V); (right) the same pixel with an applied voltage of 10 V. There is a clear change in the shape of the pixel at 10 V, indicating that the PZT has been actuated. Color changes denote the deflection |

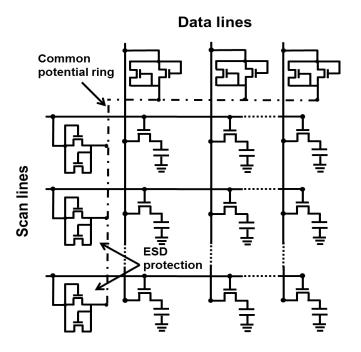

| Figure 64. ESD protected scan and data line input using diode-connected TFTs in parallel, connected to a common potential shorting ring                                                                                                                                                                             |

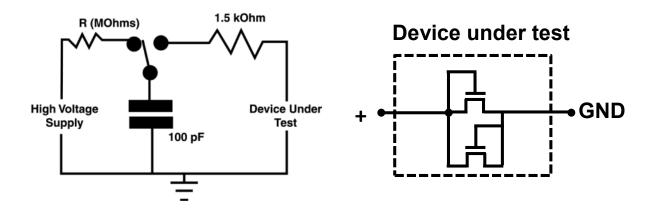

| Figure 65. (left) Typical Human Body Model (HBM) circuit (right) ESD protection circuit comprises of two diode-connected ZnO TFTs                                                                                                                                                                                   |

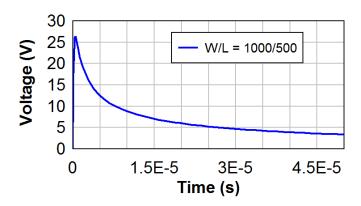

| Figure 66. Transient analysis simulation of two diode-connected TFT with W/L = 1000/500 with a peak voltage of 27 V for a 100 pF discharge.                                                                                                                                                                         |

| Figure 67. A modified PZT array mask design with ZnO-based ESD protection at the inputs of the select and data lines                                                                                                                                                                                                |

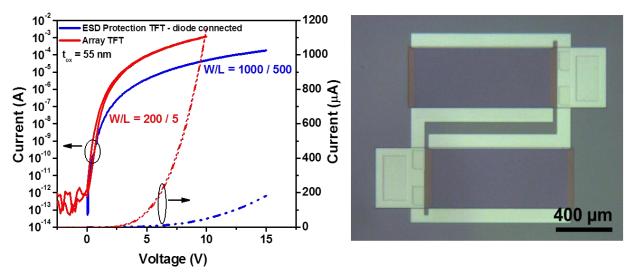

| Figure 68. (left) I-Vcharacteristics comparison a TFT in the array and a diode-connect TFT used for input protection against ESD events (right) Optical micrograph of a fabricated ESD-protection TFTs                                                                                                              |

| Figure 69. Transient measurement of two diode-connected ZnO TFT with W/L = 1000/500, in an HBM circuit, with a peak voltage of ~6 V for a 120 pF discharge                                                                                                                                                          |

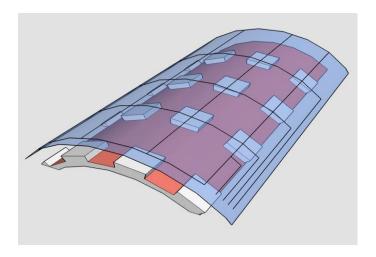

| Figure 70. Conceptualized schematic of PZT elements on a curved mirror segments with the ZnO electronics on a thin flexible substrate bonded onto the curved mirror                                                                                                                                                 |

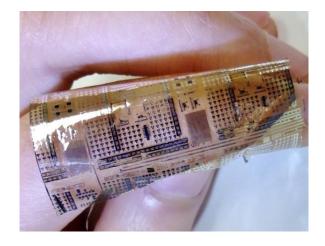

| Figure 71. ZnO TFTs fabricated on 5-µm thick spin-casted polyimide. Photo taken from reference [117]                                                                                                                                                                                                                |

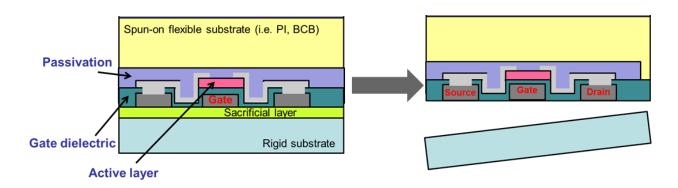

| Figure 72. Cross-sectional schematic of a fabrication process for thin film electronics on a flexible substrate                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 73. (left) Optical micrograph of a ZnO TFT after the flexible substrate was released from the rigid substrate; (right) I <sub>DS</sub> versus V <sub>GS</sub> characteristics of a ZnO TFT fabricated on a rigid substrate and transferred to a flexible substrate                                                                                                                   |

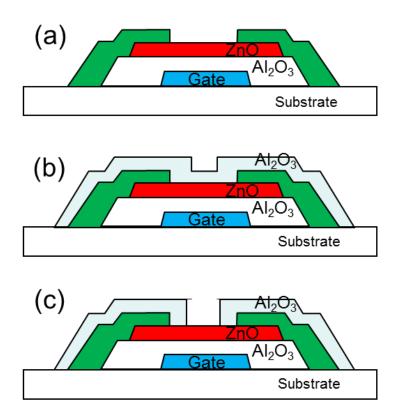

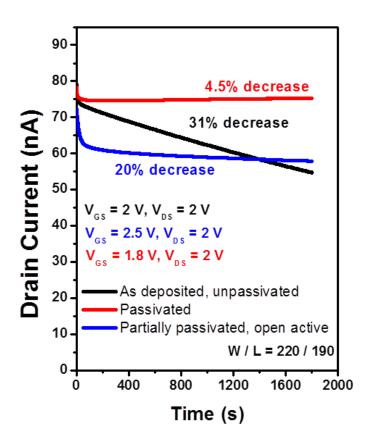

| Figure 74. Cross-sectional schematic of the three different ZnO TFT structures used to investigate the electrical stability in air and the ozone sensitivity. (a) ZnO TFT without a passivation layer (b) ZnO TFT with a passivation layer (c) ZnO TFT partially passivated with the active area exposed to the ambient.                                                                    |

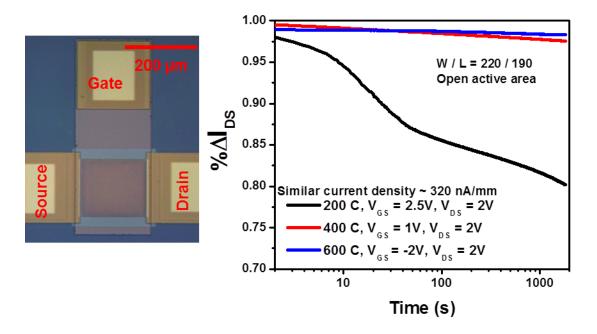

| Figure 75. Drain current as a function of time for ZnO TFTs (black curve) unpassivated (red) passivated (blue) partially passivated. The gate voltage was adjusted in each case to provide similar drain current. A partially passivated ZnO TFTs has a good trade-off between electrical stability and the ability to sense gases.                                                         |

| Figure 76. (left) Optical micrograph of a fabricated ZnO TFT with open active area region to thee ambient (right) Drain current percentage change as function of time for ZnO TFTs annealed at different temperatures. The stability is improved with increasing annealing temperature 113                                                                                                  |

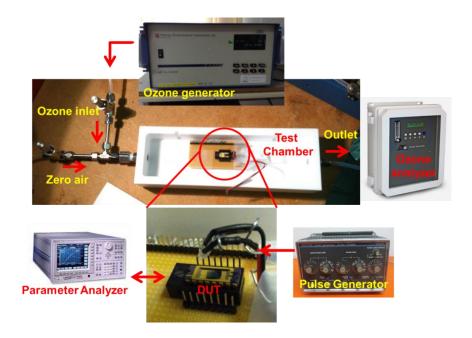

| Figure 77. The gas sensor measurement setup consists of a PTFE chamber with the DUT sample in. A UV LED is pulsed with using a pulse generator. An ozone generator is used to provide ozone to the chamber and an industrial ozone analyzer is connected at the chambers outlet. A parameter analyzer is used to monitor the change in current as a function of time of the ZnO gas sensor. |

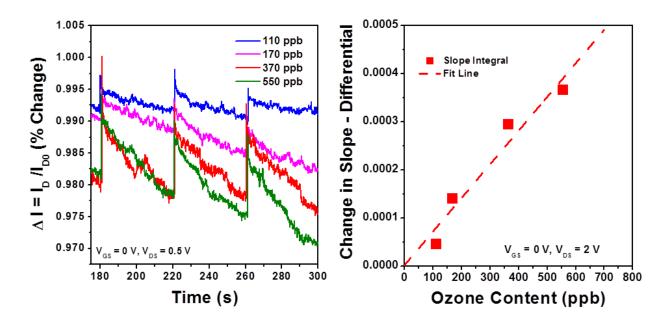

| Figure 78. (left) Percentage of change in current for an optimized ZnO gas sensor with ozone gas detection as low as 110 ppb. The sensing limit was mainly limited by the ozone generator. The periodic increase in current corresponds to when the UV LED is pulsed. (right) The extracted differential slope for each trace correlated the slope with the ozone content                   |

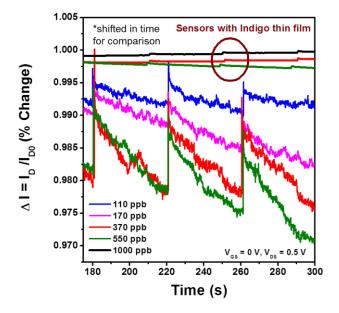

| Figure 79. Percentage of change in current for an optimized ZnO gas sensor without any organic layer (as previously shown in Figure 78) and ZnO gas sensor with ~30-thick indigo film over the gas sensor. The drain current on the ZnO gas sensor with indigo film appears to not change as a function of ozone concentration                                                              |

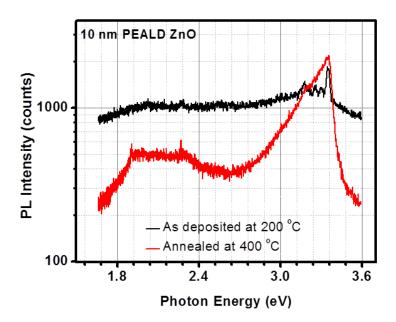

| Figure 80. Photoluminescence spectra obtained at 11 K for PEALD ZnO films as deposited (200 °C) and annealed in air at 400 °C. Understanding of the defect energy levels as function of processing conditions could lead to tune the material for high performance device applications.                                                                                                     |

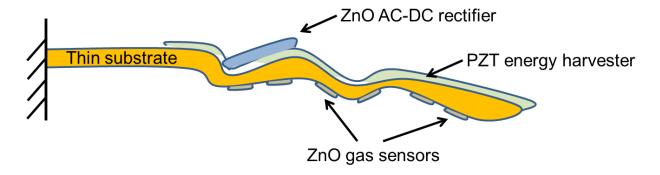

Figure 81. Conceptual art of a self-powered gas sensor node system using PZT as the energy harvesting material and ZnO electronics for AC-to-DC rectification and for gas sensing........ 124

## **Acknowledgements**

This work is a byproduct of the encouragement, discussions, and support I have had by numerous people inside and outside of academia. Over the course of my time at Penn State I have been fortunate to meet many individuals that have positively impacted me academically, professionally, and personally. A person who impacted my growth in each of those areas is my academic advisor, Dr. Tom Jackson. His immense knowledge in this field, patience, and commitment to mentoring was crucial in fostering an environment that generated fruitful discussions that developed into new research directions. Aside from being an excellent mentor, his culinary knowledge was also greatly appreciated outside the lab.

I would also like to thank my committee members: Dr. Suman Datta, Dr. Susan Trolier-McKinstry and Dr. Mark Horn, for their participation and time they devoted to reviewing and guiding this doctoral thesis. In particular, I want to express my appreciation to Dr. Susan Trolier-McKinstry for her patience explaining Materials Science concepts.

The collaborations and camaraderie of past and present members of Jackson's electronic research group (JERG) at Penn State is also gratefully acknowledged. In particular, I thank Dr. Dalong Zhao and Dr. Yuanyuan Li for imparting me their knowledge and for their selfless assistance since day one in the group. The collaboration with Dr. Trolier-McKinstry's group students Hong-Goo Yeo and, particularly, Margeaux Wallace was elemental in expanding my research directions and resources. Many fruitful discussions and collaborations with people outside of Penn State from Air Force Research Labs, Smithsonian Astrophysical Observatory, and North

Carolina State University are also acknowledged. Particularly, the many discussions over the years with Dr. Gregg Jessen from AFRL helped broaden my thinking about the ZnO material system.

Finally I thank my family Jose, Carmen, Liliana, and Abigail for their unconditional love and for tolerating my idiosyncrasies. This achievement was easier with your support.

None of this work would have been possible without the financial assistance of different government and private agencies including: Defense Microelectronics Activity (DMEA), Defense Threat Reduction Agency (DTRA) through the Asian Office of Aerospace Research and Development (AFOSR/AOARD), National Science Foundation (NSF) through Nano-systems Engineering Research Center (NERC) for Advanced Self-Powered System of Integrated Sensors and Technologies (ASSIST), National Aeronautics and Space Administration (NASA), and Corning Incorporated and Alfred P. Sloan Foundation for awarding me fellowships.

# **Chapter 1**

### 1.1 Introduction and Background

Interest in large-area electronics for ubiquitous applications is partly because of the relatively low-cost of the materials used and the simplicity to fabricate such electronics. For example, manufacturing the front-end of a liquid crystal display (LCD) backplane, the exemplary process for large-area electronics, consists of as little as four mask steps. This is in contrast to some technologies such as c-Si CMOS which can afford to use high-cost materials and processes because they have high value per unit area. For large-area electronics fast, inexpensive, and low temperature processes are favored in order to provide a path to have electronics on low-cost substrates. Amorphous silicon (a-Si:H) is an established and successful technology for large-area displays; however, its electrical performance limits useful applications for more than displays and X-ray imagers [1]. In response to the shortcomings of a-Si:H, a variety of inorganic and organic semiconductor materials have been explored as potential candidates to replace a-Si:H, all with different advantages and disadvantages [2-5]. Among some of the requirements for material selection is the ability to deposit the material at low temperatures to be compatible with polymeric substrates and to have good electrical performance and stability to realize useful largearea electronic applications. An emerging class of semiconductors that fulfill these requirements is metal-oxide semiconductors.

Amorphous silicon (a-Si:H) owes its low carrier mobility to the localized electronic states throughout its bandgap [6, 7]. A portion of these states make up the conduction and valence band tails and as it has been shown, the conduction band-tail slope dictates the field-effect mobility in

a-Si:H TFTs [6]. This is as of consequence of the strong directivity of the hybridized  $sp^3$  orbitals causing bond angle fluctuation, thereby altering the electronic levels and causing high density deep tail-states [6]. The disruption in the bond angle and bond length is a consequence of the preferred low temperature deposition process to make the material compatible with low-cost substrates. Oxide semiconductors do not have this issue because of their inherently different ionic bonding. In oxide semiconductor materials like zinc oxide, ZnO, the large difference in electrostatic potential between zinc and oxygen leads to a large ionization energy from lowering the energy levels in the oxygen ions and raising the levels in the zinc ions until the enthalpy of atomization is reached [8]. Thus, a large bandgap is realized (3.37 eV). In ZnO, and other oxide semiconductors with high ionicity, the states near the bottom of the conduction band are formed from isotropic empty s-orbitals of the zinc cation that may have some overlap with adjacent sorbitals [9-11]. This overlap of neighboring s-orbitals is largely unaffected by bond angle and bond length as is the case in materials with  $sp^3$  hybrid bonding (valence band) and anti-bonding (conduction band) like a-Si:H [9, 11, 12]. Therefore, the degenerate band conduction and large electron mobility seen in ZnO is a unique property of ionic bonding in oxide semiconductors and not seen in covalent amorphous semiconductors like a-Si:H.

As mentioned earlier, a number of oxide semiconductors have been explored for large-area electronic applications. These oxide semiconductors, generally n-type, are largely either a binary system like ZnO or derived from it to form ternary or quaternary alloys like indium-zinc-oxide (IZO) and indium-gallium-zinc-oxide (IGZO). In this work, the ZnO semiconductor is used to build electronics for large-area applications. ZnO is a versatile semiconductor with electronic uses in its thin and thick film form for electronic and optoelectronic applications [13-15]. The

wide bandgap ( $E_g = 3.37 \text{ eV}$ ) makes it transparent to IR and visible light. Moreover, because of its large bandgap, the semiconductor can achieve low leakage current, high temperature operation, and high voltage operation [3, 16, 17].

This thesis presents the use of polycrystalline ZnO thin film for electronic applications outside of the backplane technology. A novel plasma-enhanced atomic layer deposition (PEALD) system using a showerhead to dispense the reactants is discussed. This deposition process was key in depositing high performance and reproducible films over large substrates. ZnO films prepared by PEALD used in TFT structures have field-effect mobility of ~40 cm<sup>2</sup>/V-s when deposited at 300 °C and ~25 cm<sup>2</sup>/V-s when deposited at 200 °C. Pulsed-laser deposited ZnO thin films are also reviewed and used as a benchmark for PEALD ZnO thin films because the field-effect mobility of those films is closer to bulk Hall-effect mobility. While the two different deposition techniques produce ZnO films with slightly similar electrical characteristics, there are some subtle microstructural differences. Nevertheless, the similar performance highlights the material's insensitivity to the energy used during deposition. The radiation hardness of ZnO TFTs deposited by both PLD and PEALD further highlights the intrinsic ionic bonding characteristics that make ZnO insensitive to disorder. A simple model is developed to explain the small radiation-induced changes in ZnO TFTs. A general model to reduce radiation-induced changes in staggered bottom-gate thin film transistors is presented. Potential applications for more than displays where large-area electronics would be useful are described. Given the high radiation tolerance of ZnO TFTs, the TFTs are ideal candidates for large-area space applications. Integration of ZnO electronics with lead zirconate titanate (Pb(Zr, Ti)O<sub>3</sub> or PZT) thin films was developed to add functionality to PZT actuators, in particular for adaptive optics in X-ray telescopes. Finally, ultra-low-power ZnO TFT gas sensors for ubiquitous gas sensing applications have been developed.

Chapter 2 provides an overview of the different deposition techniques used to deposit oxide semiconductors. The design and development of a PEALD system that allows deposition over relatively large substrates (20 cm diameter) is presented. The system uses a showerhead to dispense the reaction materials, proving excellent uniformity and with the potential to allow fast deposition rates because of its gas configuration. System optimization was carried to produce high-quality Al<sub>2</sub>O<sub>3</sub> and ZnO thin films used throughout this work in TFT structures. Next, ZnO TFTs with the active layer deposited by PLD are presented. Chapter 2 concludes with a comparison of the electrical and materials characteristics of ZnO thin films deposited by both techniques.

Chapter 3 describes the radiation tolerance of ZnO TFTs with the active layers deposited by both PEALD and PLD. While extensive research has been done on the radiation hardness for silicon and III-V FETs, less is known about radiation-induced effects in oxide-based TFTs. In this work, the intrinsic radiation tolerance of ZnO, and by extension other oxide-based TFTs, is demonstrated. A radiation tolerance up to 100 Mrad(SiO<sub>2</sub>) is shown with no degradation in field-effect mobility and minimal negative threshold voltage (V<sub>T</sub>) shift. Contrary to the enhanced radiation effects in Si CMOS with electrical bias, ZnO TFTs are insensitive to electrical bias. Measurement artifacts in electrically biased ZnO TFTs during irradiation are identified and a framework is proposed to eradicate the artifacts in ZnO and other TFTs with a staggered bottomgate structure. Chapter 3 concludes by investigating the physical locations of charge trapping due

to irradiation in ZnO TFTs is investigated and found that the ZnO surface is the most sensitive to radiation-induced charge trapping.

Chapter 4 builds on the fact that ZnO TFTs are substrate agnostic, due to the low deposition temperature and conformal deposition technique, and applications are explored where TFTs may provide added functionality to other technologies. An example of integrating ZnO passive electronics with barium strontium titanate (Ba<sub>1-x</sub>Sr<sub>x</sub>TiO<sub>3</sub> or BST) thin films for tunable RF filters is described. Furthermore, the integration of ZnO electronics with PZT thin films used for a range of actuators is shown. A robust process was developed to integrated passive and active ZnO-based electronics on different substrates with BST and PZT films without degrading their performance. The radiation-hardness of ZnO TFTs led to explore space-related applications where large-area electronics might be desired such as adaptive x-ray optics using PZT thin films to deform the optics. The ZnO TFTs were used as switches to provide the desired voltage to the PZT thin films and consequently reduce the number of electrical connections needed to address pixels in the adaptive optics. A ZnO-based electrostatic discharge (ESD) circuit was designed and tested to reduce ESD events in the PZT-ZnO array. An array of PZT capacitors were actuated through ZnO TFTs and deformation of the thin flat glass substrate is demonstrated. Chapter 4 concludes by introducing a potentially useful processing technique to build electronics on thin polymeric substrates to avoid problems using conventional microlithography techniques on curved substrates, because the adaptive optical mirrors will ultimately have a conical shape.

Chapter 5 demonstrates ultra-low power ZnO TFTs for ubiquitous gas sensing applications. The ZnO-based gas sensor TFTs were optimized to operate at low temperature with excellent

electrical stability by using a post-deposition anneal and by partially passivating the TFT structure with the active semiconductor area open for gas sensing. The ZnO ozone sensors operate at room temperature with an average power below 1  $\mu$ W. A novel way, using pulsed ultraviolet (UV), to reset and achieve low power consumption of the ozone sensors is described. Different ozone levels were detected by looking at the  $\partial I / \partial t$  after the UV reset pulse. Ozone was detected down to 110 ppb. Chapter 5 concludes by pointing at possible methods and techniques to achieve gas selectivity in ZnO TFTs while keeping the same overall power operation.

Chapter 6 concludes the discussion of exploring the use of ZnO electronics for other applications besides displays and provides suggestion for future work. In order for this technology to be more attractive for broader applications a further understanding of the material properties is needed to be used as guideline to modify the deposition parameter conditions to achieve higher performance films. An iterative and comprehensive study relating different deposition parameters to the energy level transitions by photoluminescence (PL) and connecting it to the device performance is discussed. Also, further application-oriented demonstrations, using the current technology, are proposed. For example, leveraging the radiation-hardness of the ZnO TFTs to develop a backplane integrated with photodiodes for a flexible, low-cost detector is described. Lastly, an application-oriented opportunity is proposed for a system level integration of a self-powered gas sensor node system using PZT as energy harvester, an active ZnO rectifier, and ZnO gas sensors.

# Chapter 2

### 2.1 Thin Film Deposition Processes for Oxide Semiconductors

A wide range of deposition techniques has been used to deposit metal-oxide semiconductors. These deposition techniques vary in the energy used during growth; typical types of energy provided during film deposition are thermal, chemical or electromagnetic. Different techniques such as metal organic vapor deposition (MOCVD), pulsed laser deposition (PLD), sol-gel, and sputtering have been researched to deposit oxides [18-21]. These deposition techniques have advantages and disadvantages and are generally selected depending on the thin-film application. Most of the recent interest and research effort has focused on using sputtering, particularly for thin-film transistors. The interest is partly because sputtering is a scalable technique and the manufacturing infrastructure is already in place in the large-area display industry. This technique has been comprehensively optimized to deposit amorphous oxide thin films such as indium gallium zinc oxide (IGZO) and indium zinc oxide (IZO) [21, 22]. However, for IZO, controlling the defect concentration is often difficult resulting in small current on/off ratios; therefore, the addition of gallium provides better concentration control making it a robust process [22]. The process has matured to the point that some display manufacturers have partially ramped up IGZO-based TFT backplanes to drive active-matrix organic LED (AMOLEDs) [23, 24]. Some of the advantages of oxide semiconductors over the established a-Si:H technology are electricalstress stability, higher field-effect mobility, and lower power consumption.

While the field-effect mobility of IGZO-based TFTs deposited by sputtering can be over 30 cm<sup>2</sup>/V-s, in reality, the average field-effect mobility for TFTs used in backplane manufacturing

can be as low as 4 cm<sup>2</sup>/V-s [25]. This field-effect variation is partly due to ZnO thickness variation which has been reported to be as high as 23.5% variation over ~15 in<sup>2</sup> [25]. Another drawback of sputtering oxide-based thin films is the inherent relatively poor step coverage over substrate defects or complex topography. This is particularly problematic if the use of polymeric substrates, for flexible electronics, is desired. In the following sections, two different techniques to deposit ZnO thin films are presented: pulsed laser deposition (PLD) and plasma-enhanced atomic layer deposition (PEALD). While PLD is hardly scalable to be compatible with large-area electronics, the material grown by PLD was used as a benchmark for TFT electrical performance. On the other hand, an ALD-based deposition technique has a potential pathway to be scalable and compatible with large-area electronics and provides excellent step coverage over inherently complex substrate topology known in polymeric substrates.

The growth and the majority of the fabrication of PLD ZnO TFTs shown hereafter were done at Air Force Research Labs (AFRL) and the device characterization was carried out at Penn State. For the PEALD ZnO TFTs, the growth and fabrication of films was done at Penn State. Films grown by two different techniques allowed comparing and contrasting the materials and electrical characteristics. While different deposition and post-deposition temperatures were investigated throughout this work, the bulk of the effort was focused on depositing films by PEALD at 200 °C to be compatible with polymeric substrates.

#### 2.2 Showerhead Plasma-Enhanced Atomic Layer Deposition

Atomic layer deposition (ALD) is a technique that was developed in the 1960s by V.B. Aleskovskii et al. [26]. ALD is a self-limiting process that takes advantage of the sequential use of a gas phase chemical process. Most ALD reactions use two chemicals, often referred as precursors. Given the half-reaction nature of the process, ALD provides excellent uniformity and conformality; covering aspect ratios of  $L/d \approx 5000$ , where L is film thickness and d initial pore diameter, have been reported [27]. This feature makes the ALD technique an excellent candidate to deposit uniform thin films on a range of substrates, including substrates with high root mean square (RMS) roughness. The technique has been studied to deposit a range of materials such as dielectrics, ferroelectrics, metals, and semiconductors [28-31]. In particular, the ALD technique was very important in the development and introduction of high-k gate dielectric in the 45 nm node in Si CMOS technology [32]. The technique was an attractive option for this application because of its excellent thickness control, even for ultra-thin films, and relatively low deposition temperature. However, its major limitation is its slow deposition rate when thick films are desired. This is not an issue for high-k gate dielectric deposition in state-of-the-art CMOS because the films need to be ultra-thin. However, for applications where relatively thick films are needed the technique becomes less attractive due to its low throughput. A typical deposition rate is 0.5-1 nm per minute. Atmospheric spatial ALD (SALD) is an approach that has been investigated to overcome this drawback [33]. SALD deposition technique uses a head with reactive gases separated by a purge gas to avoid free reaction. The head is then moved over the sample at fast speeds achieving up to 25 nm/min deposition rates [33]. Initial work has been done to assess whether a showerhead system configuration could achieve high throughput.

The ALD process can be slightly modified to use plasma in conjunction with a weak-oxidant to produce the second half of the reaction, acting as an oxidizer. This variation is typically known as plasma-enhanced ALD (PEALD). There have been reports of a variety of oxide thin films such as ZnO, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, and HfO<sub>2</sub> deposited by PEALD [31]. It has been reported that plasma chemistry significantly reduces the incorporation of –OH groups, which are related to conduction in ZnO and defects in oxide-based dielectrics [31, 34]. Using plasma as an energy source for the chemical reaction allows lowering the deposition temperature while still producing high quality thin films [34, 35]. Moreover, the use of plasma has proven to be beneficial in suppressing interface states and Fermi-level unpinning in III-V MOS interfaces [34].

Figure 1. An example of a plasma-enhanced atomic layer deposition (PEALD) cycle to deposit ZnO using diethylzinc (DEZ) as the zinc precursor and a weak oxidant ( $N_2O$  in this example) as both oxidizer (when the plasma is tuned-on) and purge gas.

The majority of PEALD processes use O<sub>2</sub> coupled with plasma as a precursor, creating the oxidizing species in a remote plasma and transporting these species downstream to the substrate [31]. A slightly different approach has been taken in this work similar to the work by Mourey D. et al. [30]. Figure 1 shows a typical PEALD process cycle. The process starts by introducing the metal organic precursor (Zn precursor in the example) in to the chamber to saturate the surfaces with at least a monolayer. Next, the excess metal organic is purged out with a low-reactivity gas, typically CO<sub>2</sub> and N<sub>2</sub>O. Weak-oxidant gases have been chosen over high reactivity gases so the gas can be used as both purge gas and oxidizer when the plasma is turned on. After the excess metal organic is purged out, the plasma is ignited and the oxide layer is formed. The plasma is generated using an Advanced Energy RF power generator RFX-600 (13.56 MHz). The matching network used to ensure close-to 50-ohm impedance at the RF generator was an MFJ-989C 3 kW versa tuner. A high voltage supply (7.5 kV) attached to a thin tungsten wire through a simple vacuum feed through with a sharpen end is used to provide a source of electrons to the plasma when it is first started. This is particularly important to reliably start the plasma at low power densities which is, as will be shown later, important to have high performance thin films. The cycle is completed by purging out the reaction byproducts and the cycle is repeated until the desired thickness is reached. Typically, both, ALD and PEALD use a soak and purge time dictated by the specific chamber volume, inlet and outlet port location in order to achieve film uniformity. During a cycle, there are soaking times (time during the metal organic is introduced and the plasma is turned-on) and purge times. The soak and purge steps during a cycle result in relatively large changes in pressure throughout a cycle. These deposition systems are typically configured with inlet and outlet ports opposite of each other [36, 37]. This configuration helps uniformity and step coverage because the mass transport partially relies on diffusion to deliver the metal organics and oxidizer agents everywhere in the chamber. In this work the possible advantages of modifying the gas handling and delivering in the PEALD process by using a showerhead reactor were studied.

Figure 2. A picture of the showerhead PEALD deposition system with a load-lock chamber. The load-lock chamber was added to the system to minimize moisture in the deposition chamber. A custom-made LabView program was developed to control various deposition parameters.

The deposition system described here uses a modified commercially available showerhead reactor, P5000, manufactured by Applied Materials. The P5000 is a single-wafer chamber often configured in clusters for chemical vapor deposition (CVD), etch and/or photoresist strip applications. The chamber was heavily modified to be used as a single-wafer chamber.

Originally the chamber had a mechanical system for wafer loading compatible with a cluster system design. This was modified by using a loading chamber and a manual valve in between the two chambers, as shown in Figure 2. The load-lock chamber not only provides a convenient way to load a sample but it also helps prevent the process chamber from being exposed to atmosphere, thereby minimizing the moisture intake in it. The original lamp heater was replaced by a simple 15 cm stainless steel heater plate where a 20 cm substrate holder is placed. The showerhead consists of two plenums with spatially asymmetric holes in the innermost showerhead and spatially equidistant holes in the showerhead dispensing the gas to the sample, as show in Figure 4. This geometry provides gas uniformly across a 20 cm Ø substrate. A schematic of the chamber is shown in Figure 3 (left).

Figure 3 (left) Modified Applied Materials P5000 chamber used as a PEALD chamber. The system can handle substrates up to 20 cm; (right) schematic of the pressure and gas flow as a function of time used to operate the showerhead deposition system.

Figure 4. A detailed schematic of the plenums in the showerhead. The showerhead consists of two plenums with spatially asymmetric holes in the innermost showerhead and spatially equidistant holes in the showerhead dispensing the gas to the sample.

As previously mentioned, the gas delivery system designed and built for this chamber is different from convention ALD systems. A detailed schematic of the gas handling is shown in Figure 5. The showerhead PEALD system uses a run/vent gas delivery method; similar to a method often employed in metal-organic chemical vapor deposition (MOCVD) systems, to run at nearly constant chamber pressure. During a typical PEALD deposition the metal organic and one of the weak oxidants gas lines are alternated to keep a constant flow and constant pressure in the process chamber. The gas not dispensed to the chamber is delivered to a secondary pump. This operation mode reduces start-up effects and insures the plasma is contained right above the sample and not inside the showerhead plenums. A schematic of the gas flow and pressure as a function of one cycle is shown in Figure 3 (right). Because the gas is delivered directly above the substrate, in conjunction with the relatively small (~1 L) chamber volume, and the typical flow rates (~1 slpm), a short residence time can be achieved (~100 mseconds). This short residence times, in theory, indicates very short cycles (<0.5 secs) could be achieved. The parameter space in the short cycle regime has been initially explored and deposition rates of ~4 nm/min have been achieved. However, further investigation and optimization is still needed.

Figure 5. A schematic of the showerhead PEALD system including the gas handling. The gas handling operates in a run/vent mode (either gases are introduced to the chamber or taken to the secondary pump).

A system optimization was carried out to understand the trade-offs using an atypical gas delivery method, chamber geometry, constant-flow, and constant-pressure in a PEALD system. Next, films deposited using the showerhead system were characterized in the context of deposition rate, refractive index, and electrical measurements.

## 2.2.1 Showerhead PEALD Thin Film Properties and Devices

The most well studied material deposited by ALD is Al<sub>2</sub>O<sub>3</sub> using trimethylaluminum (TMA) as precursor and water (H<sub>2</sub>O) as oxidizer [38]. Therefore, as a starting point of system optimization

the properties of PEALD Al<sub>2</sub>O<sub>3</sub> were characterized. The deposition rate of Al<sub>2</sub>O<sub>3</sub> is fairly insensitive to deposition parameters partly because of the beta elimination between the TMA and the –OH terminated surfaces which limits the reaction to about one monolayer per cycle [38]. The same chemisorption mechanism also takes places in PEALD-deposited Al<sub>2</sub>O<sub>3</sub> films. The amount of metal organic dispensed (metal organic valve open time × flow rate, at a fixed metal organic temperature and carrier gas pressure); purge time, plasma time, process pressure, and plasma power density were investigated. The minimum metal organic dose needed to saturate all the surfaces (including the substrate) was calculated by estimating the total surface area (cm<sup>2</sup>) of the chamber that the metal organic would need to cover and by estimating the surface density of Al<sub>2</sub>O<sub>3</sub> (atoms/cm<sup>2</sup>). Using these values a dose volume was estimated for a given temperature (typically ~15 °C) and pressure of the bubbler (typically pressurized with argon at ~1500 Torr) containing the metal organic precursor. A diluted dose (argon + metal organic) in the order of ~0.04 Torr-L (~8 cm<sup>3</sup>) was found to be sufficient to form about a monolayer on the substrate and still have good material utilization. The initial optimization of the rest of the parameters was guided by using the refractive index of the deposited films (in general, a higher the index of refraction approaching the bulk material's characteristics, corresponds to high film density). This optimization was followed by electrical characterization as those characteristics were the most relevant to this work. Typical values of parameters for optimized thin films are shown in Figure 6.

| Typical deposition parameters for the showerhead PEALD  |                        |

|---------------------------------------------------------|------------------------|

| Metal organic valve open                                | 2 seconds              |

| Metal organic flow rate                                 | 250 sccm               |

| Purge time                                              | 4 seconds              |

| Weak oxidant flow rate                                  | 250 sccm               |

| 2 <sup>nd</sup> weak oxidant flow rate<br>(always open) | 650 sccm               |

| Plasma time                                             | 2 seconds              |

| Plasma power density                                    | 0.06 W/cm <sup>2</sup> |

| Plasma purge time                                       | 2 seconds              |

| Process pressure                                        | 1 Torr                 |

Figure 6. Typical deposition parameters for optimized thin films deposited using the showerhead PEALD system.

Films thicknesses and refractive index were determined by spectroscopic ellipsometry. Optimized deposition parameters for Al<sub>2</sub>O<sub>3</sub>, deposited at 200 °C yielded a deposition rate of ~1.03 nm/cycle with a refractive index of ~1.64-1.65 at 633 nm. This value is higher than other reported values for films deposited by ALD at 177 °C (1.6 at 633 nm) but, as expected, lower than sapphire (~1.76 at 633 nm) [39, 40]. **Error! Reference source not found.** (left) shows the eposition cycle as a function of thickness for PEALD Al<sub>2</sub>O<sub>3</sub> films. This deposition rate is consistent with ALD and PEALD deposition rates reported in the literature [39, 41].

Figure 7. Deposition rate of PEALD Al<sub>2</sub>O<sub>3</sub> using TMA precursor and CO<sub>2</sub> plasma at 200 °C. The deposition rate was found to be 0.103 nm per cycle.

While a refractive index value similar to the bulk material is indicative of dense thin-film, in this work the electrical properties of the PEALD thin films are of outmost importance to maximize the transistor performance. Figure 8 (left), shows the leakage current as a function of electric field for two 30-nm-thick PEALD Al<sub>2</sub>O<sub>3</sub> films, deposited using two different power densities. The dielectric constant for both films was found to be ~8 by C-V measurements. The deposition rate, refractive index, and breakdown voltage were found to be relatively independent of the deposition details, as shown in Figure 8 (left). The current-voltage characteristics shown in Figure 8 (right) show two clear regions of conduction mechanism. The second region has an exponential increase in current density which can be attributed to the onset of Fowler-Nordheim (FN) tunneling dominance. Subsequent Al<sub>2</sub>O<sub>3</sub> films shown in this chapter were deposited using the optimized conditions as shown in Figure 6.

| Power<br>Density<br>(W/cm²) | Deposition<br>rate<br>(A/cycle) | Refractive<br>Index at<br>633 nm | Soft<br>Breakdown<br>(10 <sup>-7</sup> A/cm²)<br>(MV/cm) | nsity (A / cm <sup>2</sup> | _ <sub>T</sub> |

|-----------------------------|---------------------------------|----------------------------------|----------------------------------------------------------|----------------------------|----------------|

| 0.25                        | 1.03                            | 1.63                             | ~ 6.5                                                    | e l                        |                |

| 0.064                       | 1.03                            | 1.64                             | ~7                                                       | rent D                     |                |

|                             |                                 |                                  |                                                          | O 10°                      |                |

Figure 8. (left) Deposition rate and refractive index for PEALD Al<sub>2</sub>O<sub>3</sub> are fairly insensitive to deposition parameters; (right) leakage current density as a function of applied field for Al<sub>2</sub>O<sub>3</sub> metal-insulator-metal structures deposited at two different power densities.

Unlike Al<sub>2</sub>O<sub>3</sub> deposited by either ALD or PEALD using TMA as precursor, ZnO deposition parameters, using diethyzinc (DEZ) as precursor, can drastically vary the deposition rate, material density, and crystal orientation. The majority of the parameter space investigated was at a fixed temperature of 200 °C. Other deposition temperatures were also investigated, as shown later, but 200 °C was primarily investigated because of its compatibility with low-cost substrates like plastics and glass. ZnO deposition parameters were investigated to maximize field-effect mobility. Choosing field-effect mobility as a parameter to be optimized assumes Ohmic contacts to ZnO; however, experimental and simulation evidence show a 0.1 eV contact barrier [42]. This means that the extracted field-effect mobility may be masked by contact effects. Using a similar approach to the Al<sub>2</sub>O<sub>3</sub> thin-film deposition optimization, various deposition parameters were investigated to optimize ZnO thin films. While the growth rate is dependent on the metal organic (DEZ) pulse time, as shown in Figure 9 (left), the most important parameter, apart from