# The Pennsylvania State University

## The Graduate School

Department of Computer Science and Engineering

# ENABLING INTELLIGENT VISION SYSTEMS IN A CONFIGURABLE MULTI-ALGORITHM PIPELINE

A Dissertation in

Computer Science and Engineering

by

Matthew Joseph Cotter

© 2015 Matthew Joseph Cotter

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

May 2015

The dissertation of Matthew Joseph Cotter was reviewed and approved\* by the following:

Vijaykrishnan Narayanan

Professor in the Department of Computer Science and Engineering at The

Pennsylvania State University

Dissertation Advisor

Chair of Committee

Mary Jane Irwin

Evan Pugh Professor in the Department of Computer Science and Engineering at The Pennsylvania State University

John Sampson

Professor in the Department of Computer Science and Engineering at The Pennsylvania State University

Mary Beth Rosson

Interim Dean of the Department of Information Sciences and Technology at The Pennsylvania State University

John P. Sustersic

Special Member

Research Associate at the Applied Research Laboratory, Intelligent Systems Department, Autonomous Control & Intelligent Systems (ACIS) Division

Steven P. Levitan

Special Member

John A. Jurenko Professor of Computer Engineering in the Department of Electrical and Computer Engineering at The University of Pittsburgh

Lee Coraor

Head of the Graduate Program in the Department of Computer Science and Engineering

<sup>\*</sup>Signatures are on file in the Graduate School

## **ABSTRACT**

The machine vision community has expended tremendous effort in the research and development of algorithms in an effort to develop a system that is capable of seeing the world as humans do. These algorithms often focus on the accomplishment of specific tasks analogous to human vision such as scene awareness, object detection, object recognition, and object tracking. Joining forces with cognitive neuroscientists has steered much of this research towards the development of algorithms that not only accomplish the required tasks, but endeavor to do so in a biologically inspired fashion. Still, development and evaluation of these so-called neuromorphic algorithms is often done in isolation, with little regard given to the rest of the system necessary to make this human-like system a reality.

This dissertation provides a framework for the current and future development of complex and highly integrated multi-algorithm vision systems. This framework not only enables the composition of such systems, but enables seamless development and integration of improved algorithmic modules. In addition to this high-level system composition framework, the Cerebrum tool, targeted at development of hardware-accelerated architectures is detailed in this work. This tool enables the creation of such hardware-based accelerators by researchers and engineers without specific or detailed knowledge of the target hardware platform.

In addition to the framework and tools, this dissertation also details the analysis, development and evaluation of hardware accelerators for HMAX object recognition and AIM saliency detection. Armed with this intelligent framework and algorithmic accelerators, demonstrations of vision systems that leverage multiple algorithms are constructed and evaluated.

Hierarchical object classification, leveraging the benefits of Exemplar SVM and accelerated HMAX is shown to provide performance superior to either algorithm in isolation.

Furthermore, a more complex system, targeting the domain of personal retail assistance is composed and demonstrated for the benefit of visually impaired persons.

With an eye towards future systems, this dissertation also serves to evaluate and explore a number of technologies whose time is coming. New transistors, such as Tunnel FETs, and novel architectures, such as coupled oscillator arrays, are examined to identify benefits and concerns in their use for the development of future visual systems, both at the algorithmic and circuit/component level. This work also explores the potential for inclusion of additional data modalities, such as audio, for a more effective understanding of scene awareness.

The flexibility of the framework described here enables the inclusion of these emerging devices, architectures, and modalities alongside traditional software and hardware-accelerated implementations within a unified system in order to develop, evaluate, and deploy all of the components required for any given visual system.

# TABLE OF CONTENTS

| List of Figures                                                 | vii      |

|-----------------------------------------------------------------|----------|

| List of Tables                                                  | ix       |

| Acknowledgements                                                | x        |

| Chapter 1 Introduction                                          | 1        |

| Contributions of this Dissertation                              | 2        |

| Chapter 2 Vision Algorithms                                     | 5        |

| 2.1 Scene Context & Awareness                                   |          |

| GIST                                                            |          |

| 2.2 Attention & Visual Saliency                                 |          |

| Attention based on Information Maximization                     | 10       |

| 2.3 Object Recognition                                          | 12       |

| HMAX                                                            | 12       |

| Exemplar SVM                                                    | 15       |

| 2.4 Object Tracking                                             |          |

| Consensus-based Matching and Tracking of Keypoints (CMT)        |          |

| Chapter 3 Development of Intelligent Visual Systems             | 21       |

| 3.1 Intelligent Visual Pipeline & Framework                     |          |

| Communication                                                   | 24       |

| Modular Implementation                                          | 25       |

| 3.1 Algorithmic Accelerator Prototyping Tool (Cerebrum)         | 26       |

| Cerebrum Front End.                                             |          |

| Cerebrum Back End                                               |          |

| Chapter 4 Accelerated Architectures                             | 31       |

| 4.1 HMAX Accelerators                                           | 31       |

| Baseline Implementation                                         | 32       |

| S2/C2 Accelerator                                               |          |

| S1 Accelerator                                                  |          |

| System Evaluation                                               |          |

| 4.2 AIM Accelerator                                             |          |

| Chapter 5 Case Study: Hierarchically Refined Object Recognition | 50       |

| HMAX+ESVM Pipeline                                              | 50       |

| Fyaluation                                                      | 50<br>54 |

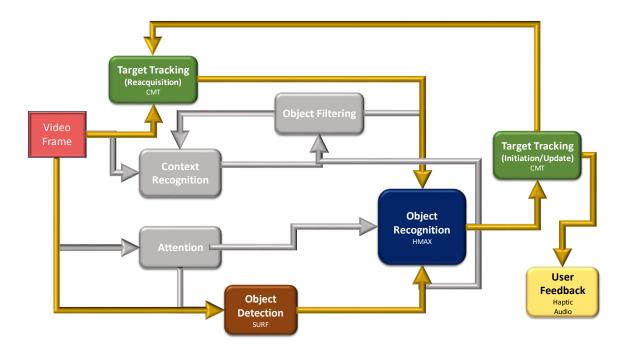

| Chapter 6 Case Study: Object Detection and Tracking for Personal Assistance    | 58 |

|--------------------------------------------------------------------------------|----|

| Detection                                                                      |    |

| Boosted Recognition                                                            | 60 |

| Tracking                                                                       | 61 |

| Feedback                                                                       |    |

| Chapter 7 Future Implications of Emerging Technologies and Non-Visual Features | 63 |

| 7.1 Emerging Technologies                                                      | 63 |

| Tunnel FETs                                                                    |    |

| Non-Boolean Architectures                                                      | 69 |

| 7.2 Multiple Modalities                                                        | 75 |

| Audiovisual Scene Recognition                                                  |    |

| Lexicovisual Scene Recognition                                                 |    |

| Chapter 8 Summary                                                              | 83 |

| References                                                                     | 85 |

# LIST OF FIGURES

| Figure 2-1. Example of AIM attentional algorithm.                                                                                 | 10 |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2. Computational layers and data flow of the HMAX algorithm                                                              | 12 |

| Figure 2-3. Example image pyramid generated in preprocessing of HMAX                                                              | 13 |

| Figure 2-4. Examples of oriented Gabor filters, as used in the S1 layer of HMAX                                                   | 13 |

| Figure 2-5. Illustration of cross scale pooling in C1 layer of HMAX                                                               | 14 |

| Figure 2-6. Illustration of several stages of CMT tracking                                                                        | 19 |

| Figure 3-1. Example of Intelligent Visual Pipeline.                                                                               | 21 |

| Figure 3-2. Example of Cerebrum Core definition                                                                                   | 27 |

| Figure 4-1. Execution time of HMAX as a function of number of threads                                                             | 33 |

| Figure 4-2. Speedup of S2 stage of HMAX as a function of multithreading                                                           | 35 |

| Figure 4-3. Power Consumption of HMAX due to multithreading                                                                       | 36 |

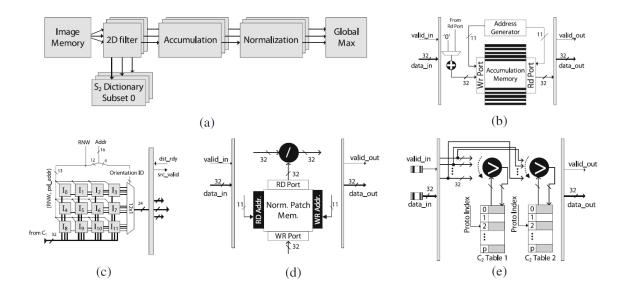

| Figure 4-4. S2/C2 Stage Accelerator for HMAX                                                                                      | 39 |

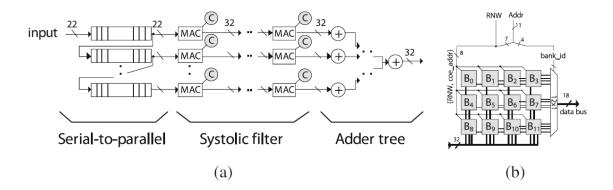

| Figure 4-5. S1 Stage Accelerator for HMAX                                                                                         | 41 |

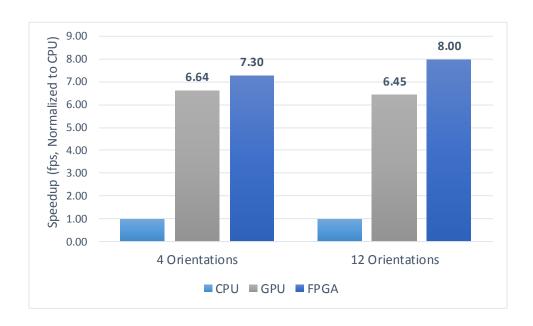

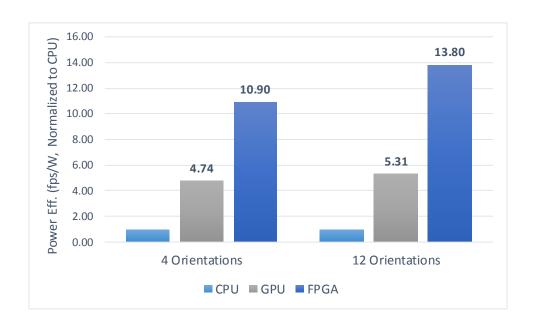

| Figure 4-6. Speedup of GPU- and FPGA-accelerated HMAX                                                                             | 43 |

| Figure 4-7. Power Efficiency of GPU- and FPGA-accelerated HMAX                                                                    | 43 |

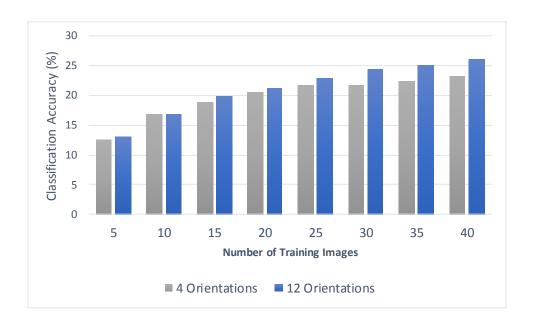

| Figure 4-8. HMAX Classification Accuracy for Caltech256 dataset                                                                   | 44 |

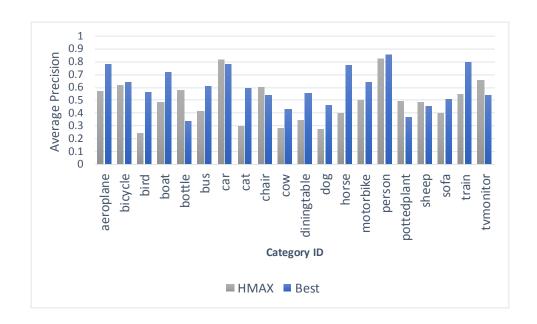

| Figure 4-9. HMAX Classification Accuracy for PASCAL VOC2007 dataset                                                               | 45 |

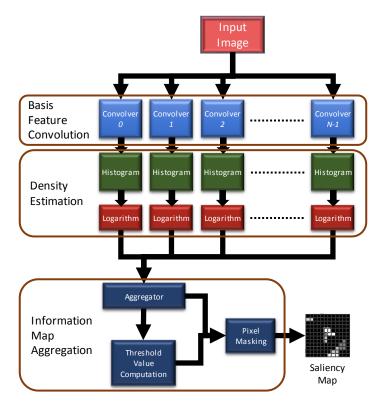

| Figure 4-10. Algorithmic data flow through AIM algorithm, including structural breakdown                                          | 47 |

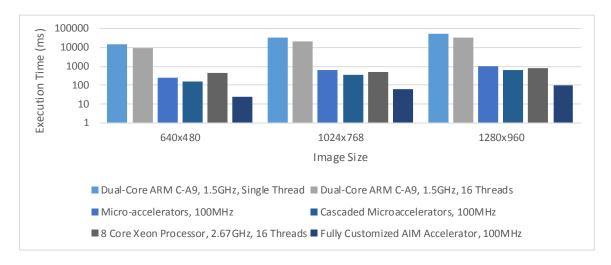

| Figure 4-11. Acceleration of fully custom AIM accelerator vs other platforms                                                      | 48 |

| Figure 4-12. Examples of salient regions identified by AIM                                                                        | 49 |

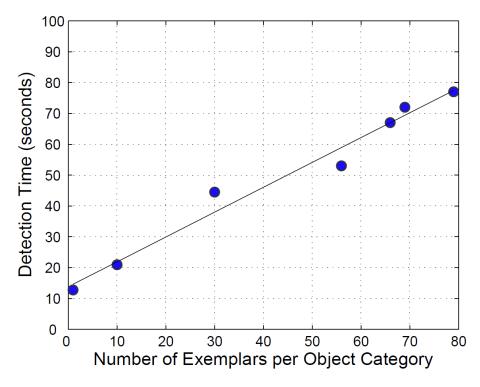

| Figure 5-1. The runtime cost of Exemplar SVM scales with the number of exemplars per class                                        |    |

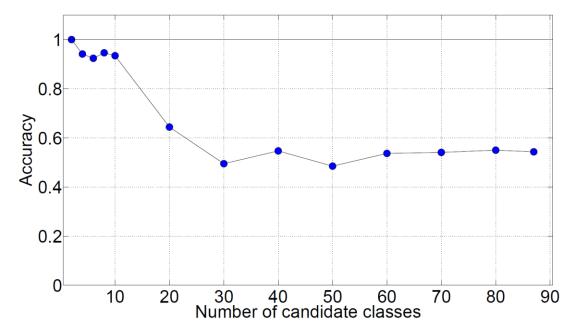

| Figure 5-2. Difficulty of feature-based classification, such as HMAX, increases (to a point) with the number of candidate classes | 51 |

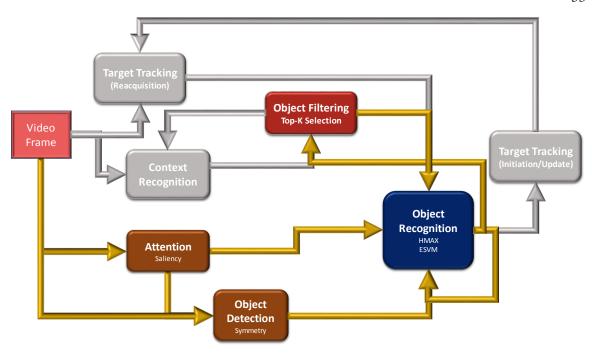

| Figure 5-3. Intelligent visual pipeline configured for HMAX+ESVM classification                                                   | 53 |

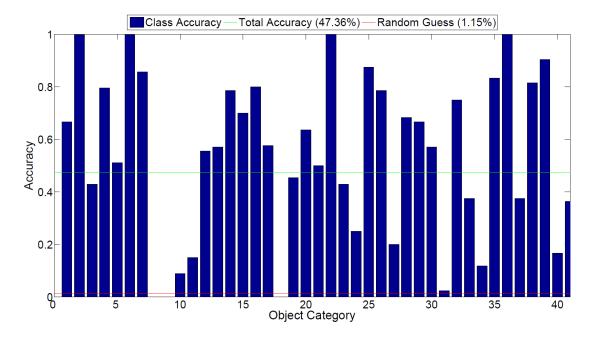

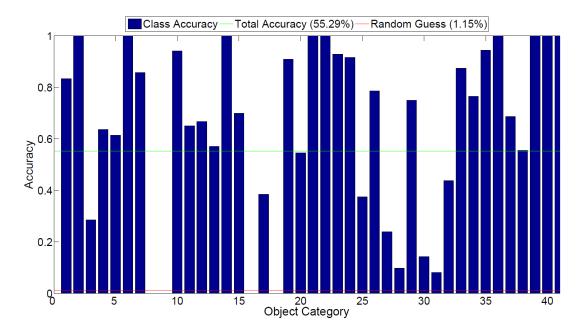

| Figure 5-4. Per-class recognition accuracy for HMAX on grocery dataset                                                                       | 54 |

|----------------------------------------------------------------------------------------------------------------------------------------------|----|

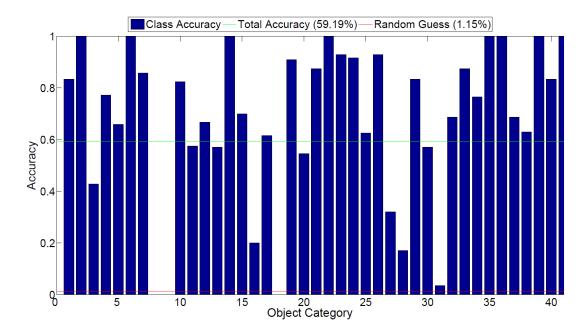

| Figure 5-5. Per-class recognition accuracy for ESVM on grocery dataset                                                                       | 55 |

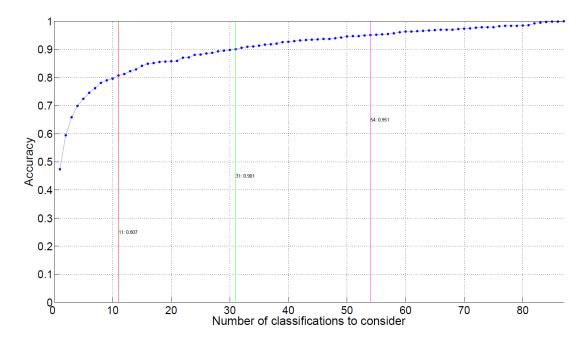

| Figure 5-6. Accuracy of HMAX recognition, as the number of candidate classifications for consideration is increased                          | 56 |

| Figure 5-7. Per-class recognition accuracy for HMAX+ESVM on grocery dataset                                                                  | 57 |

| Figure 6-1. Example of Intelligent Visual Pipeline configured for Personal Assist                                                            | 59 |

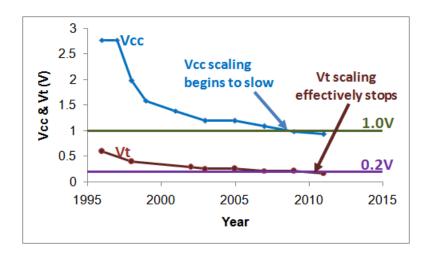

| Figure 7-1. Limitations of Scaling of Vcc and Vt in Silicon MOSFETs                                                                          | 64 |

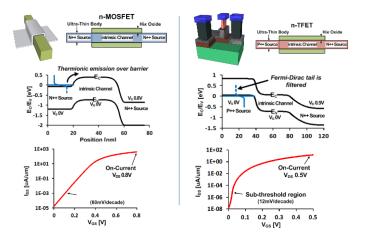

| Figure 7-2. Transport and Drive Characteristics of n-MOSFET vs. n-TFET                                                                       | 65 |

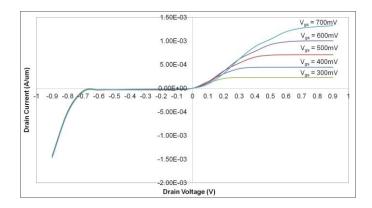

| Figure 7-3. Unidirectional conduction of n-TFET (Id-Vds)                                                                                     | 66 |

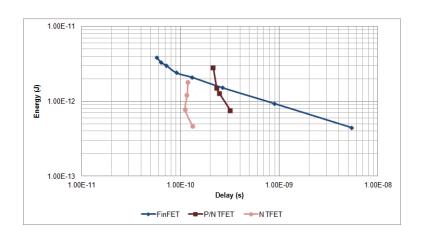

| Figure 7-4. Energy-Delay Plot of TFET-based 32-bit Sparse MCC Adder                                                                          | 67 |

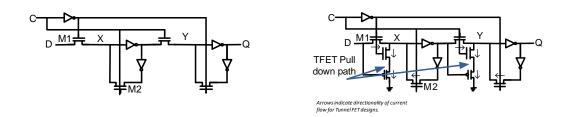

| Figure 7-5. D-Latch Based Flip-Flop Design Using FinFETs (left) and TFETs (right)                                                            | 67 |

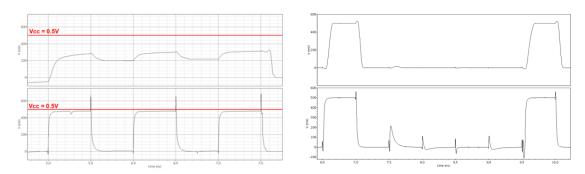

| Figure 7-6. Threshold voltage drop (left) and switching overshoot (right) for FinFETs (top) and Tunnel FETs (bottom)                         | 68 |

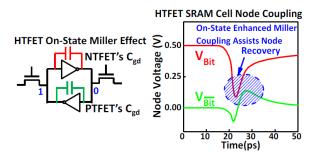

| Figure 7-7. Effect of Enhanced Miller Capacitance on TFET SRAM Soft Errors                                                                   | 69 |

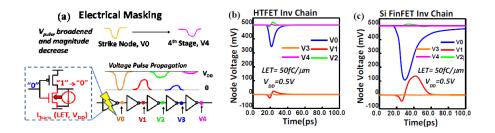

| Figure 7-8. Effect of electrical masking on soft error propagation                                                                           | 69 |

| Figure 7-9. Oscillator Inputs Derived for Edge Detection                                                                                     | 72 |

| Figure 7-10. Edge Detection using Oscillators ( <b>left</b> ) Original Image ( <b>middle</b> ) Canny Edges ( <b>right</b> ) Oscillator Edges | 73 |

| Figure 7-11. Oscillator Inputs Derived for Saliency Approximation                                                                            | 74 |

| Figure 7-12. Results of Visual Saliency From left to right: Original Image, AIM Saliency, Full Oscillator Array, Separated Oscillator Arrays |    |

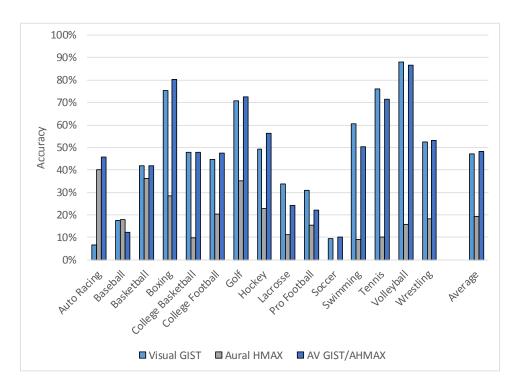

| Figure 7-13. Evaluation of scene recognition using both visual and audio features                                                            | 78 |

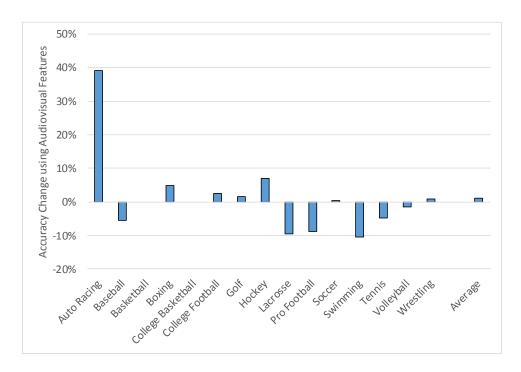

| Figure 7-14. Change in scene recognition accuracy between visual and audiovisual features                                                    | 79 |

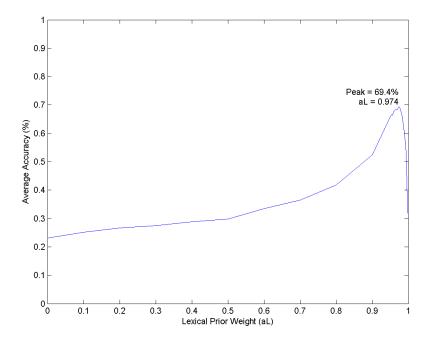

| Figure 7-15. Exploration of impact of lexical prior weight on accuracy                                                                       | 81 |

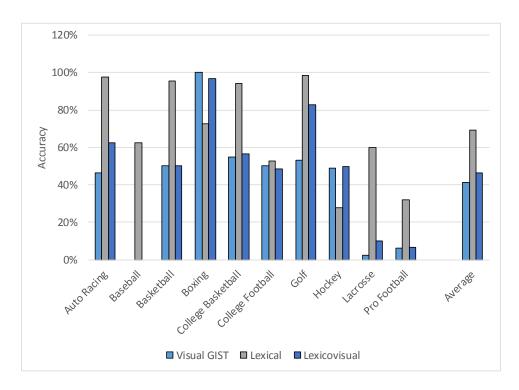

| Figure 7-16. Evaluation of scene recognition using both visual and audio features                                                            | 82 |

# LIST OF TABLES

| Table 3-1. Examples of Intelligent Visual Pipeline Modules                    | 22 |

|-------------------------------------------------------------------------------|----|

| Table 3-2. Examples of Intelligent Visual Pipeline Module Outputs             | 24 |

| Table 4-1. HMAX Algorithm Parameters                                          | 32 |

| Table 4-2. HMAX Stage Execution time, as a percentage of total execution time | 34 |

| Table 4-3. AIM Accelerator Resource Utilization on Virtex6 FPGA               | 47 |

## **ACKNOWLEDGEMENTS**

First and foremost, I would like to acknowledge the tireless guidance and encouragement of my dissertation advisor, Dr. Vijaykrishnan Narayanan. Without his willingness to take me on and guide me, this work, as well as my graduate and post-graduate career would no doubt have been impossible.

I also need to thank the rest of my doctoral committee for their input, guidance, and feedback as I pursued the various aspects of my research and for their confidence both in me and my work as I move forward beyond graduate school.

While all students, faculty, and researchers at the Microsystems Design Laboratory (MDL) at Penn State have been remarkably helpful during my time there, I do need to single out three individuals in particular: Michael Debole, Ahmed Al Maashri, and Kevin Irick. Without the day-to-day help and support from these amazing individuals, I am not sure that I could have made it as far as I have.

Last and certainly not least, I have to acknowledge the patience and sacrifices of my family throughout my academic career. Without their understanding, none of what I have done or will ever do would be possible.

# Chapter 1

#### Introduction

The vision of building a system capable of understanding the world the way humans do has long been a goal of both the machine vision [1,2] and cognitive neuroscience communities [3,4,5]. The ultimate goal of such a system is to enable the system to autonomously answer questions such as: "Where am 1?", "What is going on?", "What is worth looking at?", "What do I see?", "What objects are present?", "Are things moving?", and "Where are they going?" To humans, these questions are often too simple to consciously consider. However, endowing a computing system with these capabilities has proven challenging. For many years, both communities have attempted to tackle these problems separately. Computer scientists have focused on developing image processing algorithms rooted in disciplines such as information theory and machine learning to create systems to accomplish some of these goals. At the other end of the spectrum, cognitive scientists and neuroscientists have examined mammalian behavior and activity in the brain in order to establish an understanding of exactly how humans process information. It is this observation which drives the development of biologically inspired algorithms.

More recently, research has brought both vision communities together in an effort to create a system that is capable of seeing the world how humans see it. Much of this effort has focused on realizing biologically-inspired implementations of key aspects of the human visual process. Development of such neuromorphic algorithms has focused on a few select aspects of the human visual process such as scene and context recognition [4,6], attentional awareness [7,8] and object recognition [3,9,10,11]. Much of the work in developing these state of the art

algorithms has focused on their implementation and evaluation in isolation in order to solve the specific problem they address—answering only one, or possibly two, of these questions at a time.

In order to effectively model human perception, however, multiple algorithms must work in concert in order to quickly, efficiently, and accurately provide as much information as possible. Toward that end, this work discusses a unified multi-algorithm pipeline which is capable of enabling such intelligent visual perception systems. The goal of this pipeline is not to model the entire visual system exactly as in humans—not a fully neuromorphic system—but to provide a framework in which modules may be added, removed, configured and tuned to provide an effective answer to all of the questions necessary. Chapter 2 delves deeper into some of the algorithms that are used to enable an intelligent visual system. While there are a wide variety of algorithms which are capable of addressing machine vision problems such as awareness, attention, recognition and tracking, this chapter serves as an overview of the most prominent and widely used algorithms, many of which are further analyzed and employed throughout the remainder of this dissertation.

## **Contributions of this Dissertation**

The framework for a flexible and configurable pipeline for visual systems is presented in Chapter 3. This framework contributes a foundation for the incremental and iterative development and evaluation of complex multi-algorithm visual systems. This software architecture enables implementation-agnostic support allowing individual modules to be developed and improved independently towards the ultimate realization of the desired system.

In addition to this high-level vision framework, a tool for the graphical development of FPGA-based hardware accelerators has been developed. This tool, Cerebrum [12], has not only been used to develop the hardware accelerator for HMAX, detailed within this dissertation, but

has also been made publicly available and used for the development of other hardware accelerators as well. While similar packages have been developed, such as the iLab Neuromorphic Vision C++ Toolkit [13], these tools focus specifically on the development of purely software based models of primarily neuromorphic vision algorithms. The Cerebrum tool appears to be the first of its kind to enable drag-and-drop synthesis of vision algorithms targeted towards an FPGA-based hardware architecture.

Furthermore, this work provides analysis of multiple vision algorithms, specifically HMAX and AIM, for object recognition and salient target detection, respectively. The analysis and profiling of these algorithms ultimately served as a basis for the exploration and development of hardware accelerators, detailed in Chapter 4, contributing towards the realization of real-time complex visual systems. In addition to the development of these accelerators, this work provides a foundational evaluation of the benefits of such hardware-accelerators in terms of power and performance, relative to other implementations on general purpose CPUs and graphics processing units (GPUs).

The effectiveness and utility of systems making use of these hardware accelerators and multi-algorithm intelligent vision pipelines are demonstrated within this work as well. The flexibility of the pipeline is shown through the use of cascaded object recognition algorithms. This hierarchical object recognition scheme, detailed in Chapter 5, leverages the speed of the hardware-accelerated HMAX algorithm as well higher as accuracies of Exemplar SVM-based classification in order to improve overall recognition accuracy in a reduced time frame.

This work further demonstrates the potential social contributions of such a complex pipeline through the demonstration of a real-world personal assistance system. The personal shopping assistance scenario, targeting visually-impaired, persons is described in Chapter 6. This system incorporates a number of vision-based algorithms to locate, identify, and track desired products within a grocery store environment. In addition to this information gathering, the

system also demonstrates how this information can be leveraged in order to provide feedback allowing a visually-impaired person to locate and pickup products without additional assistance.

Finally, this work provides an exploration of a variety of new and emerging technologies that may be leveraged in intelligent vision systems of the future. The evaluation of Tunnel FETs, as a candidate for the replacement of traditional MOSFET and FinFET devices, provides a foundation for the development and continued evaluation of these devices as they mature. This work contributes to the examination of novel architectures, such as coupled oscillators, by exploring their capability to effectively provide implementations of a variety of operations and algorithms used within the domain of machine vision and image processing. New sources of information may contribute to the understanding of a visual scene as well. This work explores the application of audio signals which may be present, but often ignored, in video systems in order to improve the capability for complex visual systems to achieve better context and scene awareness.

# Chapter 2

# **Vision Algorithms**

Towards the development of an intelligent vision system, many algorithms must work together. This chapter examines some of the questions that need to be answered by such a system, and provides a detailed background on algorithms capable of doing so.

Questions such as "Where am I?" and "What is going on?" are answered through the use of context recognition algorithms [6,14,15], attempting to capture what is commonly referred to as the "gist" of a scene, the name by which they are often called. These GIST-type algorithms employ a feature extraction methodology in order to construct a feature space for future classification using these algorithms. The features generated by these algorithms are typically useful for quickly identifying a generic location or scenario, such as a city street, meadow, or forest. In addition to recognition of such broad environments, these context awareness algorithms can also enable the identification of specific locations, such as a particular room or aisle in a grocery store.

Attentional algorithms such as AIM [1,2,16] and visual saliency [7,8] attempt to answer the simple question: "What is worth looking at?" While the question is simple, the approach is not. AIM attacks this problem from an information theoretic perspective to develop a measure of self-information or "surprise" found at each pixel in an image. These regions of high information indicate regions worth focusing attention on. Visual saliency approaches the problem from the cognitive science perspective, employing features that are demonstrated to produce attentional responses in humans, monkeys and other mammals. Both of these algorithms work to produce a heat map, indicating relative levels of interest which can be found at various locations in the image.

The most intensive research in visual processing algorithms has been focused towards the field of object recognition. These types of algorithms are designed to answer questions such as "What do I see?" and "What objects are present?" Many algorithms have been developed to address the problem of answering these questions. Algorithms such as HMAX [3,9,17,5,18], are modeled after the human ventral stream of visual processing. HMAX extracts features from a particular region of an image by identifying correlations to previously learned features. Others such as Exemplar SVM [19] and SURF [20] use combinations of feature extraction, brute force matching, and machine learning in order to match visible objects to previously seen templates or examples.

Machine vision has long studied tracking algorithms in order to answer the questions "Are things moving?", and "Where are they going?" This research has led to the development of such seminal algorithms as basic mean-shift [21] tracking and Lucas-Kanade optical flow [22,23]. Many current state-of-the-art tracking algorithms, such as OpenTLD [24,25] and CMT [26], are built upon these core algorithms, augmented with the inclusion feature detection, feature extraction, and machine learning algorithms.

All of these algorithms are useful in completing a piece of the puzzle on their own. However, the deep understanding that humans are capable of in their perception does not arise through analysis of all of these pieces in isolation. Upon seeing a scene, humans are capable of quickly—virtually simultaneously—identifying the context of a scene, identifying the locations of key objects in a scene. This is quickly followed by identification of what those objects are and how they (or other objects) may be moving within the scene. As understanding of a scene develops, new inferences will be made and conclusions drawn, modulated or reinforced by the previously observed data. For example, being able to quickly identify a scene as a city street can modulate the attention, focusing it towards the ground level areas, such as sidewalks and roads. Additionally, the knowledge of the current location can influence the likelihood of detecting

certain types of objects—lions are not often found on a city street and cereal boxes don't often appear in the vegetable aisle of a grocery store.

#### 2.1 Scene Context & Awareness

Scene and context recognition algorithms are useful in the identification of a location depicted in an image. The specificity of the location may vary, identifying scenes and contexts ranging from a specific location to a general setting. Regardless, scene and context recognition algorithms enable additional inferences to be made not only about what is going on in the scene, but as to the types of objects that may be identified in the image as well [14,15,27].

# **GIST**

A variety of descriptions can be applied to various scenes, much as humans are capable of describing a scene in multiple ways. Many of these descriptors define various visual aspects of an image, often in degrees. By combining these descriptions, a better understanding of the total content of a scene can be achieved. Oliva and Torralba, in [28], have presented a method for the holistic description of a scene using a spatial envelope encompassing these types of descriptors. This envelope attempts to quantify the degree of several image descriptors such as naturalness, openness, roughness, expansiveness, and ruggedness. These descriptors lead to features which are capable of describing an image in terms of many human-understandable qualities.

Naturalness captures the apparent synthetic nature of a scene, providing an indicator of whether the location appears man-made (urban) or natural (such as a field or forest). Providing a measure of how contained a scene is, openness describes whether the content of a scene is

bounded. For example, while an area such as a forest or grassy meadow has a high degree of openness, an indoor room such as an office appears to have clearly defined boundaries and a corresponding lack of apparent "freedom". Roughness distinguishes the complexity of a scene, differentiating between scenes which contain a degree of regularity and smoothness, such as the exterior of an office building versus those which exhibit a high irregularity and lack of smoothness, such as a forest.

Due to perspective, parallel lines in a scene provide a measure of depth based on their level of convergence in a scene. Expansion quantifies this by determining the degree at which vertical and horizontal edges in a scene converge. Scenes with a high depth, and correspondingly high degree of expansiveness, contain lines that significantly converge towards their respective vanishing points. Ruggedness attempts to measure the contours of the scene of the ground level. Measured with respect to the horizon line of an image, this feature readily provides effective discrimination between man-made environments, typically with relatively smooth ground levels, such as floors and streets, and natural environments with highly uneven terrain, foliage, and rocky formations.

These descriptors can all be formulated as a measure of the spatial information in an image, represented at varying spatial frequencies. The algorithm outlined in [28] details the application of such filters in order to compute these descriptors. Each descriptor is computed by applying the appropriate filters to the input image. The image is first converted into its corresponding representation in the spatial frequency domain. This representation has a two-fold impact on the computation. First, in the frequency domain, any influence of relative location of objects in the scene is obscured. Second, the application of the frequency-domain filters to the frequency domain image results in highly simplified computation. Rather than defining, or transforming, each descriptor filter in the spatial domain, convolution of each filter requires simple point-wise multiplication in the frequency domain.

Once all of the filters have been applied to the image, a summary of the responses must be extracted to use as features for recognition. In order to accomplish this, the response of each filter is transformed back into the spatial domain. A grid of NxM equal-sized subregions is defined across the image and the average response across each of these regions is computed. A finer grid corresponds to a feature vector more representative of the entire image, at the cost of a larger vector for subsequent processing and increased computation time.

# 2.2 Attention & Visual Saliency

The baseline models for visual attention essentially strive towards the ideal goal of identifying what region(s) of an image the eyes would be most drawn to look at first. A variety of attentional models have been developed. Bottom-up models [1,2,16,29] strive to identify regions of interest (ROIs) within a scene based on global image features. These models derive their measure of attention for any particular pixel or region based solely on statistics and information available within the image. While this approach has validity in identifying human fixations [1], there is evidence that human attention is driven by more than what is seen. [30] Recent attentional models have shown that human fixations are often modulated by a task-dependent factor. These task-driven, or top-down, attentional models have become increasingly attractive for systems in which the targets are known ahead of time. Both models have uses in intelligent vision systems, with bottom-up attention later influenced by top-down processing.

#### **Attention based on Information Maximization**

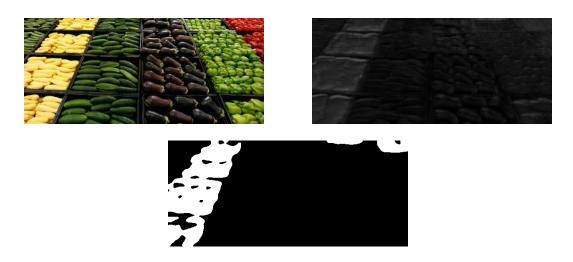

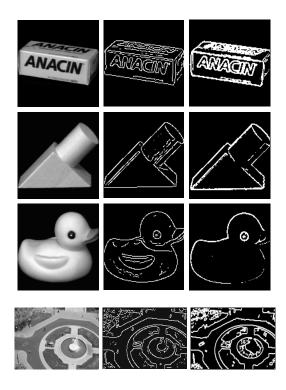

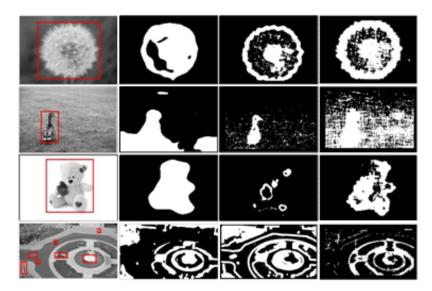

Saliency (Attention) based on Information Maximization [2], dubbed AIM, is a bottom-up attentional model that works to identify regions of interest in an image. These regions are identified using a statistical approach based on information theory. In essence, this algorithm endeavors to assign values to every pixel in an image corresponding to the level of Shannon self-information. These regions found to contain the most information within the image are identified as regions of interest. The kinds of regions identified by this algorithm are found to correspond to those that contain the most surprise, relative to the rest of the image. An example of the results of this algorithm can be seen in Figure 2-1.

Figure 2-1. Example of AIM attentional algorithm. (top-left) Input image, (top-right) Saliency map, (bottom) Thresholded ROI mask

The level of self-information contained throughout the image is extracted through the use of a series of convolutional operations. The kernels used for these convolutions are learned *a priori* and form the foundation of the computation of the algorithm. These kernels are derived through a multi-step process. Initially, a random sampling of image patches is taken from a large

set of images. Each of these patches is then evaluated in terms of its capability to extract information. These patches are then evaluated using Independent Component Analysis (ICA) in order to identify the set of patches which produces the most mutually exclusive information.

These patches then become the basis functions on which the primary algorithm is based.

The runtime operation of the algorithm can be separated into three stages. In the first stage, each of learned basis kernels is convolved with the image. For multi-channel images, each channel is convolved with the basis kernels independently. After convolutions have completed, the response values are binned into histograms in order to compute pixel-response frequency counts. The pixel-responses are used along with these histograms to compute a probability and then a log-likelihood density estimation. This value estimates the probability of a particular pixel response, and therefore the probability of a given pixel. The summation of all of these likelihoods produces an estimate of the self-information at each pixel, resulting in an information map as seen in Figure 2-1 (top-right).

The exact process of identifying salient pixels from this map may vary. One simple approach is to identify a percentile threshold above which a pixel is considered to be salient and below which is considered irrelevant. Using this threshold, the likelihood value(s) which fall on or around this threshold are identified. This value is then used to binarize the information map into salient and non-salient pixels. An example of this binary map is shown in Figure 2-1 (bottom).

# 2.3 Object Recognition

#### **HMAX**

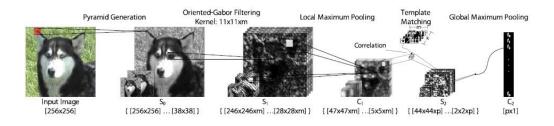

Object recognition in the human brain is processed in the ventral stream, between the V1 visual cortex and the inferior temporal (IT) cortex [3,11,31]. Based on this biological model, HMAX attempts to mirror the behavior and processing performed along the ventral stream in a biologically consistent manner. Working to match the scale-and rotationally-invariant capabilities of human process, this model builds a set of complex features, derived from simple features. This processing happens in a hierarchical, feed-forward fashion. Figure 2-2 [32] shows an example of the computational operations and dataflow of the HMAX algorithm.

Figure 2-2. Computational layers and data flow of the HMAX algorithm

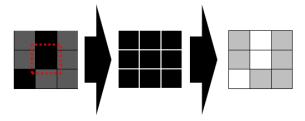

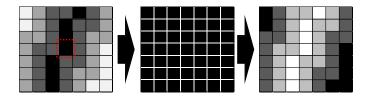

The first processing step performed in HMAX is a pre-processing step. In order to enable scale invariance, the first stage of the HMAX algorithm generates an image pyramid, representing the original input image at a variety of scales and resolutions, as seen in Figure 2-3. After composition of the image pyramid, the remainder of the HMAX algorithm is comprised of alternating layers of convolution operations and pooling operations, corresponding to the (S)imple and (C)omplex cells found within the visual cortex.

Figure 2-3. Example image pyramid generated in preprocessing of HMAX The image of the duck is taken from the COIL-20 dataset [citation]

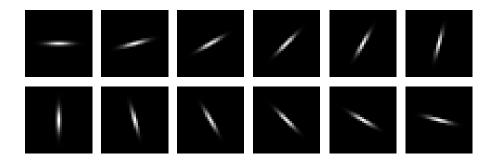

The first of these layers, the S1 layer, enables the rotational invariance of the HMAX algorithm. In the S1 layer, each scale of the image pyramid is convolved with a series of Gabor filters, a widely accepted model of the receptive fields in the visual cortex [31]. As in [33], this series of filters is designed to be 11x11 in size with dominant orientations equally spaced between 0 and  $\pi$  radians. The remaining parameters—wavelength ( $\lambda$ ), effective filter width ( $\sigma$ ), and aspect ratio ( $\gamma$ )—are set as described in [18] to have values of 5.6, 4.6, and 0.3 respectively.

$$G(x,y) = \exp\left(\frac{(X^2 + \gamma^2 Y^2)}{2\sigma^2}\right) \times \cos\left(\frac{2\pi}{\lambda}X\right)$$

Equation 2-1. Gabor filter used in the S1 layer of HMAX processing

Figure 2-4. Examples of oriented Gabor filters, as used in the S1 layer of HMAX Orientation angles spaced equally between 0 and  $\pi$  radians

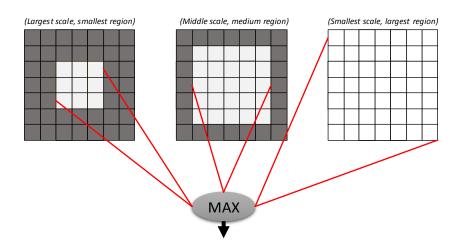

Following the S1 layer, the C1 layer performs localized pooling across S1 output cells. This layer compresses some of the scale invariance introduced in the preprocessing stage by maxpooling values across adjacent scales. In addition to this cross-scale activity, pooling encompasses local regions of these adjacent scales. The resulting output of the C1 layer is a highly condensed set of images, retaining all orientation information generated by the S1 layer.

Figure 2-5. Illustration of cross scale pooling in C1 layer of HMAX

The most complex layer of HMAX processing, the S2 layer is modeled on the V4 (posterior IT) region of the ventral stream. In this layer, a large database of tuned features are matched across each scale of C1 output. This database consists of a number of prototype image patches, of varying sizes (4x4, 8x8, 12x12, and 16x16 as in [10]). Each of these patches consists of the target feature as seen at each orientation as generated by the S1. The matching function of the S2 may be varied, however, the normalized dot product, as shown in Equation 2-2, has been shown to be an effective matching function [32]. The processing of the prototypes through the S2 ensures that each prototype's orientation is matched against the corresponding orientation of C1

output. The output of the S2 layer results in a large amount of data, namely a response image for every dictionary template, correlated at every scale and orientation fed into the S2.

$$R(X, P) = \frac{X.P}{\sqrt{\sum x_i^2 - \frac{(\sum x_i)^2}{n^2 * m}}}$$

Equation 2-2. Equation describing the Normalized Dot-Product used in the S2 layer of HMAX

The final layer of HMAX processing, the C2 layer, enables global invariance by pooling across all responses for each prototype over a range of scales. By grouping large bands of scales together, this pooling effectively eliminates the impact of large variations in scale. Pooling across the entirety of each response image removes the impact of position within the frame. Likewise, pooling across orientations ensures that the best response for each prototype is found regardless of how the object is oriented in the initial input image. This global pooling results in a large and complex feature set that can be used for any number of machine learning systems for object recognition.

## **Exemplar SVM**

The Exemplar SVM (ESVM) [19] model performs object detection based on the relatively simple concept of finding the best match of a particular object within a database of previously learned objects. In support of this, an SVM classifier is trained for each object, exemplar, in the learned database. While the database may contain any number of exemplars for a given class, a unique classifier is trained for each exemplar independently. These exemplars are each represented through the use of a rigid Histogram of Oriented Gradients (HOG) template.

HOG processing is based on gradient computation within the window. Each detected gradient is then employed in a nonlinear weighting operation, allowing each gradient to vote for a particular orientation, based on the magnitude response. These votes are then binned by orientation over small spatial windows within each cell. Contrast normalization is performed across all blocks within the cell, producing a normalized HOG cell response. The complete HOG descriptor is a combined vector of all components of the normalized cell responses from all of the blocks in the detection window [34].

Each specialized exemplar classifier is trained by first windowing the object ground truth in such a way as to produce approximately 100 cell windows. While the exact windowing function is different for each exemplar, the size of all cells for any given exemplar are the same. This results in the number of HOG features being different for each exemplar SVM classifier. The training process for each exemplar begins by this window selection, extracting the HOG features from each window. These features serve as the positive training example of the chosen exemplar,  $X_E$ . A number of negative training examples are then generated by extracting cells, of the same size as the training exemplar from database objects which do not represent the same class as that of the chosen exemplar. For each of the windows extracted from the non-chosen exemplars, HOG features are extracted. These features serve as the negative training examples of the chosen exemplar,  $N_E$ .

Finally, the SVM classifier is trained to learn the feature weights which provide maximal separation of the features represented in  $X_E$  from those found in  $N_E$ . For each positive exemplar, it is not uncommon to use a very large set of negative examples for training. However, the number of training vectors only impacts the training phase of the ESVM algorithm.

Once trained, an unknown object is processed through each of the trained ESVM classifiers. For each classifier, the cell windowing and HOG feature extraction is performed in

such a way as to match the cell topology of the positive example of the class. This ensures that the resulting HOG feature vector will have the same length as the ESVM classifier.

The detection and classification of ESVM has been shown to be highly effective [19]. However, as the classification process must be carried out for each candidate SVM, the runtime performance scales not with the number of classes as many classification schemes, but rather with the number of exemplars. Thus, the ensemble of exemplars can become quite large. The ability to classify a wide number of classes would require processing of the entire ensemble, requiring significant expenditure of time and resources.

# 2.4 Object Tracking

Machine vision has developed a number of algorithms that can be useful for tracking moving objects. The most basic of these algorithms is mean shift tracking. This algorithm suffers from a number of deficits which later algorithms have tried to address. Deformations and rotations in the object easily create confusion and can cause tracking to fail. Algorithms such as Lucas-Kanade optical flow [22] attempt to improve on this by attempting to first identify key components of a tracked object. These components are tracked individually by identifying local regions in subsequent frames which exhibit strong correlation to the component in the previous frame. The net motion of the object can be computed through analysis of the apparent movement of its components. However, this type of tracking may succumb to errors when dealing with objects that are capable of deformation, effectively changing the relative locations between key components while in motion.

More advanced algorithms have attempted to address this issue through several means.

OpenTLD [25] employs an online learning model during tracking. This enables a periodic update allowing the algorithm to adapt to subtle changes in the object over time, effectively

compensating for deformations. However, rapid movements or changes in the object without corresponding updates to the model can cause tracking to fail. Once this happens, it becomes difficult for TLD to re-engage tracking with the target.

Another algorithm, Consensus-Based Matching and Tracking of Keypoints (CMT), sacrifices some of this flexibility in order to enable simplified target reacquisition.

# **Consensus-based Matching and Tracking of Keypoints (CMT)**

The CMT algorithm performs object tracking by combining a persistent object model based on advanced keypoints and optical flow. Tracking is initialized by providing the algorithm with the current frame and the region of that frame which contains the object. The entire input frame is processed using the advanced keypoint detection algorithm, BRISK in the default implementation. The set of active keypoints is constructed by identifying all of the keypoints which fall inside the region defining the target object. These keypoints, and their associated descriptors comprise the defined object model. This model, in addition to the keypoints, contains information relating their relative locations and angles, called springs, with respect to the center of the defined object region. This additional information is used for object center, scale, and rotation estimation during subsequent frames, as seen in Figure 2-6a. All remaining keypoints, and their descriptors, are defined to constitute the background model of the scene.

Figure 2-6. Illustration of several stages of CMT tracking

(a) Keypoints and springs identified during initialization. (b) Optical flow estimation. (c) Scale and Rotation estimation using relationships between keypoints. (d) Center point estimation using transformed springs

Subsequent frames are processed by first performing keypoint based Lucas-Kanade optical flow (Figure 2-6b) of the active model keypoints into the current frame. Both forward and reverse optical flow are computed to define a degree of error in the tracking of each keypoint. Any keypoint which is not able to be tracked within a reasonable error bound is ignored in the tracking as untracked.

The set of keypoints that are successfully tracked are then used to estimate the relative scale and rotation of the object (Figure 2-6c). This is done through analysis of the relative change in distance and locations between keypoints. After estimation of scale and rotation, these keypoints are then used to estimate the center of the object (Figure 2-6). By using the springs for

each of these keypoints, an agglomerative hierarchical clustering algorithm is employed to allow each keypoint to vote for the location it considers the most likely center. The center of the primary cluster is taken as the estimate for the new object center, after any votes which fall too far outside this cluster are discarded.

After tracking, the algorithm attempts to reconstitute any keypoints which were not successfully tracked by performing another round of keypoint detection and matching against the initial model. It is this step that enables CMT to reacquire an object after it has been obscured, left view, or temporarily changed its form or appearance enough to be lost. For each keypoint in the image, it is matched to the model developed in the tracking initialization through the use of a brute force matching algorithm. While the matcher identifies the best match between keypoints, the algorithm enforces a minimum threshold the degree of this match. Additionally, another constraint is imposed, requiring a high degree of relative confidence in the match, by comparing it to the second-best match as well.

With tracking and matching complete, the set of active keypoints is updated and a new bounding box is computed. In its current form, CMT does not adapt the model of the object over time, so one drawback is that it loses tracking of objects that have a significant change in view over time, such as an object with differing front and rear sides that rotates.

# Chapter 3

# **Development of Intelligent Visual Systems**

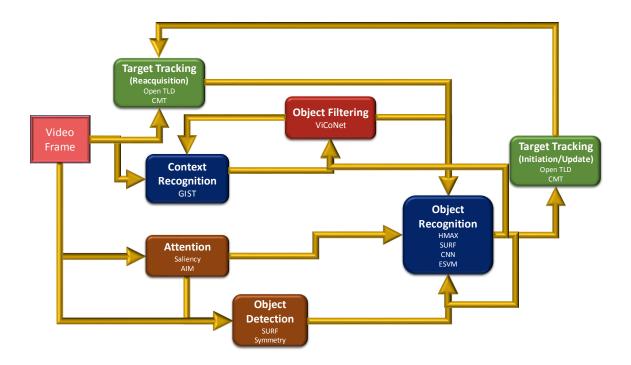

This chapter details the framework for the development of an intelligent visual system based on a software-architected pipeline. This pipeline presents a unified software architecture for the inclusion, development and utilization of a wide variety of detection, recognition, and tracking modules, among others, necessary to construct such an intelligent system. A visualization of a complex intelligent vision pipeline is shown in Figure 3-1. Despite its grounding in a software implementation, the components of the pipeline are entirely self-contained, rendering the internals of their implementations irrelevant.

Figure 3-1. Example of Intelligent Visual Pipeline.

A software tool for the prototyping and development of FPGA-based hardware accelerators is also presented in this chapter. This tool presents a hardware-agnostic interface for

research scientists to develop algorithmic accelerators targeting a variety of FPGA hardware platforms. The interfaces to these accelerators can be easily mapped into the intelligent vision pipeline described here, regardless of the exact nature of their implementation.

# 3.1 Intelligent Visual Pipeline & Framework

The intelligent visual pipeline discussed here is created with several goals in mind. The first of these goals is that the pipeline configuration is highly flexible. The only requirement of components in the system is that they conform to one of several interfaces indicating their general purpose: input, output, detection, feature extraction, classification, filtering, or tracking. Often used together, feature extraction and classification modules may be grouped together into a general class of modules explicitly targeted at self-contained recognition. Examples of the types of components and algorithms that would fall into these categories are listed in Table 3-1. These interfaces are not exhaustive. The dynamic nature of the pipeline facilitates the development and integration of interfaces which have not yet been defined. This enables future support of algorithms and information modules that are not yet known, or known to be necessary.

Table 3-1. Examples of Intelligent Visual Pipeline Modules

| Innut          | Output                | Detection | Recognition Filtonia            |                         | Filtering                                 | Tracking |  |

|----------------|-----------------------|-----------|---------------------------------|-------------------------|-------------------------------------------|----------|--|

| Input          | Output                | Detection | Feature Extraction              | Classification          | rintering                                 | Tracking |  |

| Image Set      | Display<br>Visualizer | Saliency  | SURF                            | Linear (RLS)            | Visual Co-occurrence<br>Network (ViCoNet) | OpenTLD  |  |

| Video File     | Audio<br>Feedback     | AIM       | SIFT                            | Brute Force<br>Matching | Top-K Response                            | CMT      |  |

| GigE<br>Camera | Haptic<br>Feedback    | SURF      | HMAX                            | SVM                     |                                           | OpenTLM  |  |

| USB<br>Webcam  |                       | SIFT      | Histogram Of<br>Gradients (HoG) | ESVM                    |                                           |          |  |

| IP Camera      |                       | Symmetry  |                                 |                         |                                           |          |  |

| Web Stream     |                       |           |                                 |                         |                                           |          |  |

The modular flexibility provided by this framework enables hierarchical solutions to vision-related problems by cascading multiple different algorithms together. Visual GIST-type algorithms, by providing context and awareness, can greatly improve the recognition of objects in a scene. However, the types and configuration of objects found in a scene may be just as telling. For example, if an object recognition module strongly recognizes several objects such as cars, buses, and signs, the system may be able to infer that the location is a city regardless of the result of the context recognition algorithm. In turn, this improved context awareness may enable further refinement of other, less easily recognized objects in the scene.

The cascaded arrangement of modules may also include similar algorithms in order to better solve or reinforce results, such as in the case of object recognition. This is the case explored by the hierarchical recognition pipeline described in Chapter 5. This pipeline employs multiple feature extraction and classification modules alongside a classification filtering module in order to exploit the accuracy and performance characteristics of different recognition algorithms.

With time being a key limiting factor in a real time vision system, it may be often the case where there is insufficient time to sufficiently classify or process all detected objects within a scene. The inclusion of tracking-enabled modules in this intelligent pipeline opens a new means of improving performance by exploiting the temporal dimension. Detected objects can be tracked through frames over time, regardless of whether or not they are given a classification. Over time, as the number of new detections decreases, the slack time may be given to classify these previously unclassified objects. In the event that no objects are found to be unclassified, classification can still provide benefits in the presence of tracking capabilities, however. Objects with weak classifications may be reclassified, possibly with greater effort, in order to improve or reinforce the assigned classification.

The flexibility of this pipeline only requires that those components necessary for the target application be included. The hierarchical recognition described in Chapter 5 presents a simple pipeline, while a more complex pipeline, as described in Chapter 6, utilizes a wider range of components.

#### Communication

Each module must conform to a particular interface, indicative of the type of operation that it performs or purpose it serves. The distinguishing factors of these interfaces, therefore, lies in the type of data that it produces. A summary of the types of outputs each module produces is given in Table 3-2. Input modules produce raw input data such as frames from an IP camera or video file. These output data streams are tagged with the ID and function of the module that generated it in order to facilitate advanced data flows.

Table 3-2. Examples of Intelligent Visual Pipeline Module Outputs

| Inv   | put                      | Output                                       | Detection                        | Recognit           | ion                             | Filtering                       | Tracking                         |  |

|-------|--------------------------|----------------------------------------------|----------------------------------|--------------------|---------------------------------|---------------------------------|----------------------------------|--|

| 111]  | pui                      | Output                                       | Detection                        | Feature Extraction | Classification                  |                                 | Tracking                         |  |

| audio | image,<br>, etc.)<br>ata | Visual,<br>auditory,<br>physical<br>feedback | Regions<br>of Interest<br>(ROIs) | Feature Vectors    | Classification<br>Scores/Labels | Classification<br>Scores/Labels | Regions<br>of Interest<br>(ROIs) |  |

An event/subscription style model is used by the pipeline to propagate data from one module to the next. This allows each module to register for the type of data stream that is requires. The pipeline architecture is then able to connect each available data stream to any modules which have requested it. In addition to specifying the type of data requested, the module may specify additional constraints or restrictions on the source of the data. For example, a

classification module registered to receive feature vectors and trained on HMAX features should not be sent feature vectors generated by a HoG module. So, the classification module may specify that the type of feature vector must come from an HMAX module.

The type of data a module may request isn't strictly limited by its interface. This allows, for example, an object recognition module to request input streams from other object recognition modules. This, naturally, may result in an infinite loop, so the pipeline is crafted so that a module may not receive its own output directly. Such a loop is still possible if routed through additional intermediate modules, so there is some responsibility on the developer of each module to properly ensure that repetitive input data is eventually discarded without producing a response.

#### **Modular Implementation**

The second goal of this intelligent pipeline is to ensure that its operation is wholly agnostic with respect to the underlying implementation of each module. Conceptually, this means that a software implementation of HMAX is no different from a hardware-accelerated implementation of HMAX—they are both feature extractors in the eyes of the pipeline. All classifier modules take in data and produce classification results.

However, it may be of use to know the underlying implementation when constructing a pipeline implementation. Thus, each module may be annotated with additional version or implementation tags that allow intelligent assembly of the pipeline. If a pipeline requires an implementation of the AIM ROI detector, for example, functionally it does not matter whether the module is software-based, or hardware-accelerated. However, the architect may specify that, if available, a hardware-accelerated version be used rather than a software implementation.

Ultimately this allows the description of the pipeline to be boiled down to its essence, which is a

series of modules and the connections between them, allowing the system to assemble the most effective version possible given the available components.

# 3.1 Algorithmic Accelerator Prototyping Tool (Cerebrum)

A number of factors make it difficult for researchers in fields such as neuroscience to quickly and efficiently construct high performance, hardware-accelerated systems to evaluate the algorithms they develop. Firstly, often times researchers in these fields lack the skill set to develop the required hardware accelerators. Additionally, even armed with the necessary accelerators, synthesis of the components into a usable system presents an equally challenging task without additional assistance. Without the tools able to leverage on-chip communication infrastructures, such as networks-on-chip and a lack of standardization across FPGA systems, use of these platforms as a prototyping and development system is seen as far too daunting a task. In an effort to remedy this situation, and bridge the usability gap between computational researchers and engineers, the Cerebrum software tool was developed.

Cerebrum defines and leverages a standardized abstraction across both FPGAs and hardware modules (IP cores) available for them. This enables a clear framework for the creation and modification of an algorithmic dataflow requiring minimal engineering effort. This tool is composed of a front end graphical user interface, exposing the available components and platforms to the user. The back end of the tool automates the processing of several engineering tasks necessary to take the user-defined algorithmic dataflow and map it onto the desired FPGA platform.

### **Cerebrum Front End**

The front end GUI of Cerebrum presents the users with a drag-and-drop style of interface for the development of hardware accelerated algorithms. For the purposes of designing the algorithm, a library of available IP cores are displayed to the user. The visibility and availability of IP cores in the library may be limited by the target hardware platform, thus preventing the user from spending time developing towards a system which ultimately cannot be synthesized due to IP incompatibility. The library of modules is defined by a structured XML-based architecture which enables the hardware developer to expose hardware parameters and control how components and IP cores are connected. The snippet of XML shown in Figure 3-2. Example of Cerebrum Core definition, demonstrates a Cerebrum IP core specification. This example Cerebrum core defines a simple I/O interface core.

```

<Software>

<DesignDisplay>

<Category Name="System Interfaces" />

<Port Type="INITIATOR" Name="rx" Interface="bit:128" />

<Port Type="TARGET" Name="tx" Interface="bit:128" />

</Ports/>

</DesignDisplay>

</Software>

<Hardware>

<Interface Type="SAP" PE="True">sys_iface</>

<PCores>

<PCore Type="sys rx if" Version="1.01.a" ... />

<PCore Type="sys_tx_if" Version="1.01.a" ... />

</PCores>

<Name="100MHz Oscillator"... Frequency="100MHz"... />

</Clocks>

</Hardware>

```

Figure 3-2. Example of Cerebrum Core definition

The <Software> section describes the appearance and interface of the core with respect to the front end GUI. This section defines where the core appears in the library of components, and what visible ports it exposes to the user, among other visual properties. The

types of the ports defined here indicate how the core may be interfaced with other cores in the design. Cerebrum defines four types of ports, applicable to different types of cores. Streaming cores utilize ports designated as either INPUT or OUTPUT. Computational cores expose INITIATOR and TARGET ports. OUTPUT ports may only direct data to INPUT ports (of other streaming cores) or TARGET ports (of computational cores). Likewise, INITIATOR ports may only direct data to an INPUT of streaming cores or a TARGET of computational cores.

The <Hardware> section defines the details of the hardware components which comprise the Cerebrum Core. In addition to defining the type of the Cerebrum Core (SOP: Streaming OPerator) or SAP (Switch-Attached Processor), this section defines the specific IP cores and any required clocks produced by or required by the component. Other aspects of the hardware covered by this section include importing predefined component interconnects, declaring a limited set of supported platforms and architectures, as well as the estimated resource requirements of the components contained in the Cerebrum core. Armed with the cores available in the library, construction of a system becomes a simple matter of dragging and dropping the necessary components into the workspace and creating the dataflow connections between them.

This specification wrapper hides all of the internal details from the algorithm developer.

Once the user has drawn a system on the workspace, the back end of the Cerebrum tool takes over to perform the task of translating the displayed system onto the target platform. In order to achieve this, the tool requires three sets of specifications. The first specification is the design specification, created by the user in the Cerebrum front end. The second specification is that of the target hardware platform. The platform specification defines several low-level details about the reconfigurable platform. This includes the number and types of FPGAs available, how they are connected, both logically and physically, the resources available on each, and any FPGA-specific pin constraints or signals. The final required specification is the Cerebrum project.

This file defines all of the options associated with how and where the EDA tools should be run.

Armed with complete specifications for the project, the design, and the platform, the tool may proceed to back end synthesis, translating the provided information into a hardware definition for the target FPGA platform.

### **Cerebrum Back End**

Using these specifications, the Cerebrum back end performs a series of steps in order to realize the desired system on the target hardware. The first step in this process is the mapping of the necessary components to the available FPGAs in the system. A customized accelerator mapping algorithm was developed in order to optimize multiple constraints including minimization of data flow and inter-FPGA communication while maximizing resource utilization. The mapping algorithm proceeds through several phases in order to work towards an optimal solution.

A feasibility check is first performed. This step is designed to short-circuit the algorithm in the event that the system requires more resources than are available on the entire FPGA platform. If, at least superficially, there are sufficient resources to map the required components, mapping proceeds to the component grouping phase.

Advanced users may annotate the design with requirements that some components be colocated on the same FPGA, without regard to the specific FPGA in the platform. Sets of component groups that are so annotated are coalesced into a Component Group. For the purposes of mapping, this group is treated as a single "black box" component requiring the resources of all contained components as well as data connections to all components with connections to the components internal to the group. Once all component groups have been formed, mapping proceeds to I/O distance computation.

Each component, or component group, is annotated with its distance from the system input and output connections. This distance is calculated by finding the average number of hops, or edges, in the available paths between the component and the specific connection. These distances are used to optimize placement of components with shorter I/O on FPGAs closer to the corresponding system I/O port.

Once again, users with advanced knowledge of the target platform may influence the mapping algorithm. During the design process, if desired, each component may be annotated for placement on a specific FPGA. In the event that a component is assigned to an FPGA and assigned to be grouped with another component, the entire component group is then assigned to the FPGA. If the user attempts to assign groups components to different FPGAs an error is generated, advising the user to correct the discrepancy. With a valid pre-mapping, each such component is assigned to its target FPGA, virtually allocating the required resources.

Finally, the optimization of component placement begins. A greedy algorithm is used to find the best target FPGAs for each component. In order to avoid a lack of resources at later iterations of the algorithm, the components and groups with require the most resources are placed first. Optimal placement is determined by finding the FPGA which has the most resources remaining and also minimizes the data traffic between FPGAs. This traffic is measured by finding the number of inter-FPGA hops required for data to flow through the component, if it were placed on each FPGA. This approach continues until either all components are successfully placed, or a component is encountered for which no available FPGA has sufficient remaining resources.

With all components mapped to a target FPGA, the Cerebrum back end generates the files necessary for the proprietary back end tool flow. A system file is generated for each FPGA based on the components that were assigned to it during by the mapping algorithm. Following this, the entire back end tool flow is automated; proceeding through the steps of synthesis, technology mapping, placement and routing, and finally bit stream generation.

# Chapter 4

## **Accelerated Architectures**

This chapter provides details on the development of novel accelerators for two visual algorithms. The first algorithmic accelerator described here is targeted for the HMAX feature extraction algorithm. This includes a detailed analysis and profiling of the algorithm, both in parts and as a whole, enabling highly effective and targeted optimizations in the overall architecture. This architecture is composed of multiple accelerators which enable high performance with minimal degradation in accuracy. The HMAX accelerator described here not only represents a novel architecture for the algorithm, but was also established as the foundation for ongoing research as part of the DARPA Neovision2 [35] project.

Further extending the family of vision-oriented accelerators, this section also details the development of an attentional model accelerator based on the AIM algorithm. The AIM accelerator described here was developed for incorporation into the visual processing pipeline of the Supervised Autonomous Fires Technology (SAF-T) [36] program under the Office of Naval Research.

#### **4.1 HMAX Accelerators**

The HMAX algorithm, designed for function in an effort to mirror the biological responses in the brain, displays several inefficiencies when executed on a general purpose processor. These inefficiencies are a result of the computational structure of the algorithm and result in less than optimal runtime performance. In order to effectively utilize HMAX as a feature extraction engine for object recognition in a real time intelligent visual system, a detailed study of

the algorithm is necessary. This study, detailed here, identifies many of these inefficiencies within the general purpose CPU implementation of HMAX, thus enabling the development of effective and efficient hardware accelerators enabling dramatically improved performance of the HMAX algorithm.

As detailed in Chapter 2, the implementation of HMAX used in this dissertation is based on the variant HMIN [33]. This implementation defines a number of parameters for this particular implementation of the HMAX algorithm, which are summarized in Table 4-1. In order to establish firm baselines for performance purely in software, the C++ implementation was first augmented to support multiple threads, enabling performance gains through thread-level parallelism.

Table 4-1. HMAX Algorithm Parameters

| Parameter       | Value          |  |  |

|-----------------|----------------|--|--|

|                 | (Range)        |  |  |

| Pyramid Scales  | 8 to 12        |  |  |

| S1 Orientations | 4 or 12        |  |  |

| C2 Pooling      | 1 Scale        |  |  |

| Overlap         |                |  |  |

| S2 Dictionary   | 5120 templates |  |  |

| Templates       | _              |  |  |

| S2 Dictionary   | 4x4, 8x8,      |  |  |

| Template Sizes  | 12x12, 16x16   |  |  |

| C2 Pooling      | 6 Scales       |  |  |

| Range           | [11-6, 6-1]    |  |  |

## **Baseline Implementation**

The evaluation platform for the multi-threaded software implementation of HMAX consisted of an Intel-based system equipped with dual 2.4GHz Quad-Core Xeon-class processors with a total of 12 GB of main system memory. Each of the four cores of the Xeon processor were HyperThreading-capable, providing 2 logical CPUs per core, resulting in a total of 16 processing units. The software was compiled with maximum optimizations and the SSE2 SIMD instruction

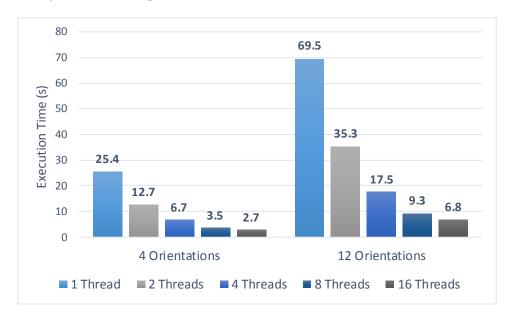

set enabled for further increased performance. Figure 4-1 demonstrates the impact of multithreading on the runtime performance of the software.

Figure 4-1. Execution time of HMAX as a function of number of threads

In addition to the number of available threads, the runtime performance was also found to depend, nearly linearly, on the number of orientations to be processed. Reducing the number of orientations by a factor of 3, from 12 down to 4, the execution time of the algorithm was reduced by a factor of 2.5 to 2.8, depending on the degree of multithreading enabled. The impact of thread-level parallelism is clearly evident in the observed execution times, wherein a 2X increase in the number of threads often results in a nearly 2X increase in performance. However, increasing the number of threads from 8 to 16 produces only a 1.3X improvement in execution time.

This reduced performance benefit is explained by analyzing the impact of multithreading on each stage of the HMAX algorithm. As shown in Table 4-2, the S2 stage of processing thoroughly dominates the runtime of the algorithm. In fact, the S2 computation averages over 96% of the total execution time with virtually no regard to the number of available threads or

orientations being processed. This indicates that the vast majority of the performance gains found due to multithreading can be found within the S2 stage.

Table 4-2. HMAX Stage Execution time, as a percentage of total execution time

| #<br>Threads | #<br>Orientations | S1   | C1   | S2    | C2   |

|--------------|-------------------|------|------|-------|------|

| 1            | 4                 | 1.62 | 0.19 | 97.61 | 0.53 |

|              | 12                | 1.77 | 0.21 | 97.82 | 0.19 |

| 2            | 4                 | 1.69 | 0.22 | 97.45 | 0.56 |

|              | 12                | 1.79 | 0.22 | 97.78 | 0.19 |

| 4            | 4                 | 1.89 | 0.30 | 97.15 | 0.50 |

|              | 12                | 1.90 | 0.26 | 97.60 | 0.17 |

| 8            | 4                 | 3.54 | 0.58 | 94.97 | 0.60 |

|              | 12                | 2.96 | 0.40 | 96.27 | 0.25 |

| 16           | 4                 | 4.71 | 0.87 | 93.26 | 0.76 |

|              | 12                | 3.08 | 0.56 | 95.92 | 0.29 |

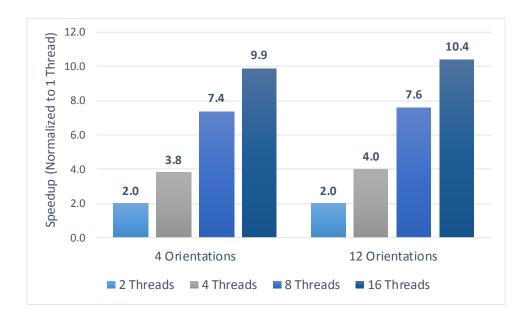

Further profiling of the S2 stage specifically reveals the reason for relatively reduced performance gains when increasing the number of parallel threads from 8 to 16. As the number of threads increases beyond the number of processed orientations, the ability to exploit the available parallelism dramatically decreases. As the critical path of the S2 is comprised of correlation of input images with prototypes in the S2 dictionary, exploitation of parallelism at this level is difficult. The largest performance gains come from the thread-level parallelism at the granularity of processing one orientation/scale being processed per thread. Maximal orientation-level parallelism is achieved at the point in which the number of threads equals the number of orientations, 4 and 12 respectively. Further increases in available threads are able to exploit scale-level parallelism in the processing of the S2, but ultimately the reaches the point of diminishing returns, as seen in Figure 4-2.

Figure 4-2. Speedup of S2 stage of HMAX as a function of multithreading

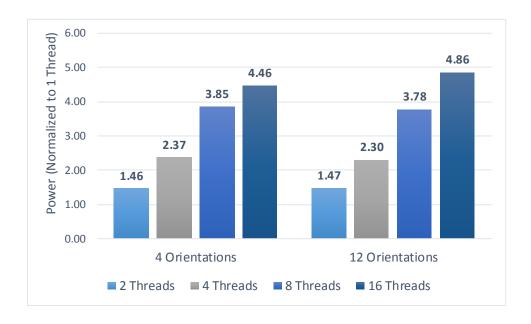

As performance is not the only concern in many systems, such as embedded systems, power consumption must be taken into consideration as well. For each of the algorithmic and multi-threading configurations described here, the runtime power consumption of the system is measured as well and shown in Figure 4-3. For this evaluation, power was measured by using a power meter, which provides both continuous and instantaneous power measurements during runtime.

The results here clearly demonstrate the benefits of such parallelism. However, further performance improvements will require application specific acceleration. Specifically, aspects of the algorithm shown to be least influenced by the enabled parallelism, such as convolution operations, require a targeted approach. Due to its enormous influence on the overall execution time of the algorithm as well as the prevalence of convolution operations within, the S2 represents the stage which can gain the most benefit from targeted acceleration.

Figure 4-3. Power Consumption of HMAX due to multithreading