## The Pennsylvania State University The Graduate School

## DESIGN METHODOLOGIES OF THREE-DIMENSIONAL INTEGRATED CIRCUITS (3D ICS)

A Dissertation in Computer Science and Engineering by Qiaosha Zou

© 2015 Qiaosha Zou

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

The dissertation of Qiaosha Zou was reviewed and approved\* by the following:

Yuan Xie Professor of Computer Science and Engineering Dissertation Co-Advisor, Co-Chair of Committee

Mary Jane Irwin Professor of Computer Science and Engineering Robert E. Noll Professor Evan Pugh Professor Disseration Co-Advisor, Co-Chair of Committee

Vijaykrishnan Narayanan Professor of Computer Science and Engineering

Donghai Wang Associate Professor of Mechanical Engineering

Lee Coraor Associate Professor of Computer Science and Engineering Chair of Department Graduate Program

<sup>\*</sup>Signatures are on file in the Graduate School.

#### **Abstract**

The continuous technology scaling results in the growing delay gap between transistors and interconnects because of the significant increase in parasitics. Moreover, the increased integration density and design complexity exacerbate the interconnect issue from both the rising routing requirements and the prolong wirelength. Recently, the emerging three-dimensional integrated circuits (3D ICs) have been studied intensively as one potential solution towards the future high performance and energy efficient computing systems. Different from previous system-in-package (SiP) designs that stack multiple chips and use wires or bumps for connections, the emerging 3D integration provides finer granularity integration thanks to the vertical interconnects inside chips. In general, 3D ICs provide numerous advantages over traditional 2D IC designs, such as smaller footprint, high bandwidth and short latency interconnects, and the capability of heterogeneous stacking.

Nevertheless, there are several challenges in 3D ICs that need to be solved before this technology is applied in commercial designs with high volume production, such as higher fabrication cost, compromised system reliability, the lack of mature electrical design automation tools, the elevated chip operation temperature, and the insufficient understanding on chip testings. The relatively complicate fabrication process implicates higher cost of 3D ICs compared to 2D counterparts. As the cost is the primary driving force for the new technology adoption, reducing the system cost becomes the one of the primary concerns in 3D designs. On the other hand, the success of this emerging technology should be guaranteed by its functionality correctness. However, a few factors influence the 3D reliability: fabrication limitations, thermal mechanical stresses, interconnect electrical failures, degraded signal integrity, and IR droop in power networks. As a result, these factors should be considered and properly addressed in 3D designs to ensure the chip reliability.

This dissertation proposes novel design methodologies to optimize 3D designs emphasizing the challenges of cost and reliability. In the first part, a cost model is adapted and applied in our analysis framework to evaluate the 3D system cost. Then cost-aware design methods are proposed to reduce the cost from fabrication level to chip design level. The second part of this dissertation handles the chip reliability problems. Three studies are introduced from diverse aspects to manage the interconnect electromigration, thermal mechanical stresses, and the signal integrity issues.

## **Table of Contents**

| List of | Figures                                                         | ix   |

|---------|-----------------------------------------------------------------|------|

| List of | Tables                                                          | xiii |

| Ackno   | wledgments                                                      | xiv  |

| Chapt   | er 1                                                            |      |

| Inti    | roduction                                                       | 1    |

| 1.1     | 3D Integration Technologies                                     | 1    |

| 1.2     | Existing Physical Design Methodologies of 3D ICs                |      |

|         | 1.2.1 3D Partitioning and Floorplanning                         |      |

|         | 1.2.2 3D Placement and Routing                                  |      |

| 1.3     | Existing System Level Design Methodologies                      |      |

| 1.4     | Opportunities and Challenges in 3D ICs                          |      |

| 1.5     | Contribution and Organization                                   |      |

| Chapt   | er 2                                                            |      |

| Cos     | st Analysis Framework with Test Elimination                     | 11   |

| 2.1     | Preliminaries and Motivation                                    | 13   |

| 2.2     | Cost Benefit Analysis Framework                                 | 16   |

| 2.3     | Hierarchical Yield Model                                        | 19   |

| 2.4     | Experiment and Cost Analysis                                    | 21   |

|         | 2.4.1 Impacts of Design Target                                  | 22   |

|         | 2.4.2 Impacts of Cost Parameters and Defect Clustering Degree . | 24   |

|         | 2.4.3 System Cost Analysis on Multicore Design                  | 25   |

| 2.5     | Summary                                                         | 26   |

| Chapte               | er 3    |                                                   |    |

|----------------------|---------|---------------------------------------------------|----|

| Me                   | tal Lay | ver Reduction for Cost Optimization               | 27 |

| 3.1                  | Routa   | ability and Cost Models                           | 28 |

|                      | 3.1.1   | Routability Models                                | 28 |

|                      | 3.1.2   | 3D Cost Model                                     | 30 |

| 3.2                  | Cost I  | Efficient 3D Design Exploration Flow              | 32 |

| 3.3                  | Exper   | iment Results                                     | 35 |

|                      | 3.3.1   | Cost Analysis without Optimization                | 3! |

|                      | 3.3.2   | Cost Analysis with Optimization                   | 3  |

| 3.4                  | Summ    | nary                                              | 39 |

| Chapte               | er 4    |                                                   |    |

| $\operatorname{Ver}$ | tical B | Bandwidth Reconfigurable 3D NoCs Utilizing Redun- |    |

|                      |         | dant TSVs                                         | 40 |

| 4.1                  | Prelin  | ninaries and Related Work                         | 42 |

|                      | 4.1.1   | 3D Multicore Processor Designs                    | 42 |

|                      | 4.1.2   | TSV Redundancy                                    | 43 |

|                      | 4.1.3   | Motivation and Related Work                       | 44 |

| 4.2                  | Recon   | afigurable Vertical Link Design                   | 45 |

|                      | 4.2.1   | Basic Router Architecture                         | 45 |

|                      | 4.2.2   | Proposed Architecture Modification                | 46 |

|                      |         | 4.2.2.1 Switch Allocator Design                   | 4' |

|                      |         | 4.2.2.2 Crossbar Design                           | 47 |

|                      |         | 4.2.2.3 Additional Link Arbitrator                | 4  |

|                      | 4.2.3   | Design Issues                                     | 48 |

|                      |         | 4.2.3.1 Router Placement                          | 49 |

|                      |         | 4.2.3.2 Routing Algorithm and Timing Analysis     | 50 |

|                      |         | 4.2.3.3 Flow Control                              | 50 |

|                      |         | 4.2.3.4 Availability of Spare TSVs                | 5  |

| 4.3                  | Simula  | ation Result Analysis                             | 5  |

|                      | 4.3.1   | Area Evaluation                                   | 5  |

|                      | 4.3.2   | Performance Evaluation                            | 53 |

|                      | 4.3.3   | Layer Sensitivity                                 | 56 |

|                      | 4.3.4   | Failure Mode Sensitivity                          | 57 |

| 4.4                  | Summ    | nary                                              | 59 |

| Chapte               | er 5    |                                                   |    |

| -                    |         | gration Lifetime Analysis in TSV Arrays           | 60 |

| 5.1                  |         | ground and Motivation                             | 6. |

|                      | _       | Motivation                                        | 6  |

|                  | 5.1.2 Related Work                                             | . 63 |

|------------------|----------------------------------------------------------------|------|

| 5.2              | TSV Array Current Density and EM Lifetime Simulation Mechanism |      |

|                  | 5.2.1 Power Grid Model                                         |      |

|                  | 5.2.2 Current Density Calculation                              | . 68 |

|                  | 5.2.3 Array EM Lifetime Calculation                            | . 69 |

| 5.3              | TSV Array EM Lifetime Analysis                                 |      |

|                  | 5.3.1 TSV Array EM Lifetime                                    |      |

|                  | 5.3.2 TSV Filling Material                                     |      |

|                  | 5.3.3 TSV Number and Size in Array                             |      |

| 5.4              | Case Study                                                     | . 76 |

| 5.5              | Summary                                                        | . 7  |

| $\mathbf{Chapt}$ | er 6                                                           |      |

| _                | osstalk Minimization in TSV Arrays                             | 78   |

| 6.1              | Preliminaries                                                  | . 79 |

|                  | 6.1.1 Crosstalk in TSV Array                                   | . 79 |

|                  | 6.1.2 Related Work                                             |      |

| 6.2              | 3D LAT Coding Mechanism                                        | . 82 |

|                  | 6.2.1 Preliminaries in 2D NAT Code                             |      |

|                  | 6.2.2 3D $\omega$ -LAT Code                                    | . 83 |

|                  | 6.2.3 LAT Code Optimization                                    | . 87 |

|                  | 6.2.4 Heuristic LAT CODEC Design                               | . 89 |

| 6.3              | Evaluation                                                     |      |

|                  | 6.3.1 Interconnect Power Analysis                              |      |

|                  | 6.3.2 Crosstalk Delay Analysis                                 | . 93 |

| 6.4              | Summary                                                        | . 94 |

| $\mathbf{Chapt}$ | er 7                                                           |      |

| -                | ermo-Mechanical Stresses Management in 3D ICs                  | 95   |

| 7.1              | Background and Related Work                                    | . 95 |

|                  | 7.1.1 Analysis of TSV Thermal Stress                           |      |

|                  | 7.1.2 TSV Lateral Thermal Blockage Effect                      | . 97 |

|                  | 7.1.3 3D Thermal Cycling Effect                                | . 97 |

| 7.2              | Thermomechanical Stress-Aware 3D Design Methodology            |      |

|                  | 7.2.1 The Heuristic Floorplan Flow                             |      |

|                  | 7.2.2 Thermal Cycling-Aware Run-Time Management                |      |

| 7.3              | Experiment Results and Analysis                                |      |

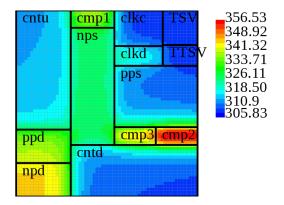

|                  | 7.3.1 Block-Level Thermomechanical Stress-Aware Floorplan      |      |

|                  | 7.3.2 System-Level Thermomechanical Stress-Aware Floorplan .   |      |

|                  | 7.3.3 System-Level Run-time Thermal Management Scheme          | 105  |

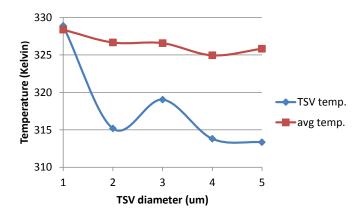

|               | 7.3.4            | Sens | itivit | y St | udy ( | on TS | SVT  | herr | $\operatorname{nal}$ | Cor  | ıduo | ctiv | ity | an | ıd I | Эίε | $\mathbf{m}$ | ete | er I | 106 |

|---------------|------------------|------|--------|------|-------|-------|------|------|----------------------|------|------|------|-----|----|------|-----|--------------|-----|------|-----|

|               | 7.3.5            | Impa | acts c | of T | herm  | al Th | irou | gh-S | ilico                | on V | Vias |      |     |    |      |     |              |     |      | 108 |

| 7.4           | Summa            | ary  |        |      |       |       |      |      |                      |      |      |      |     |    |      |     |              |     |      | 110 |

| Chapte<br>Cor | er 8<br>nclusion | anc  | l Fut  | ure  | · Wo  | ork   |      |      |                      |      |      |      |     |    |      |     |              |     | 1    | .11 |

| Bibliog       | graphy           |      |        |      |       |       |      |      |                      |      |      |      |     |    |      |     |              |     | 1    | 14  |

## **List of Figures**

| 1.1        | Conceptual view of TSV-based 3D integration                                                                                       | 3   |

|------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2        | Conceptual view of interposer-based 3D integration                                                                                | 3   |

| 1.3        | Conceptual view of monolithic 3D integration                                                                                      | 3   |

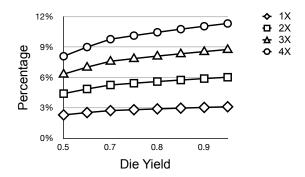

| 2.1        | The test cost percentage in 3D integration with different die yields.                                                             | 14  |

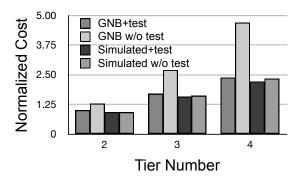

| 2.2<br>2.3 | The normalized system cost of four cost estimation combinations The overview of the proposed framework for cost estimation and    | 15  |

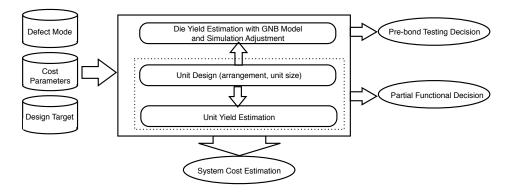

| 2.5        | design option analysis                                                                                                            | 17  |

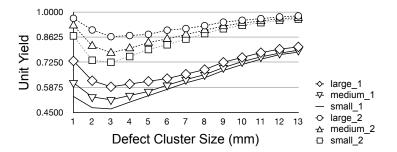

| 2.4        | The variation in partial yield with different defect clustering degrees and two tolerant thresholds                               | 21  |

| 2.5        | Both extremely centralized and extremely scattered defect distribution result in high partial yield. (a). Scattered defects; (b). |     |

|            | Centralized defects                                                                                                               | 21  |

| 2.6        | Cost variations with different die sizes when the unit count is fixed.                                                            | 22  |

| 2.7        | Cost variations with different unit area when the die area is fixed                                                               | 23  |

| 2.8        | Cost variations with different die sizes/unit counts when the unit                                                                | 2.2 |

|            | area is fixed                                                                                                                     | 23  |

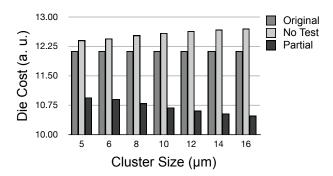

| 2.9        | Cost variations with different defect cluster radius                                                                              | 24  |

| 2.10       | The impact of reducing wafer/bonding costs on integration costs                                                                   | 25  |

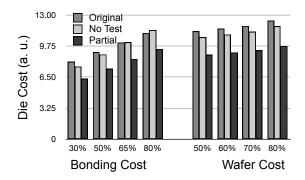

| 3.1        | An example of 3D interposer stacking. (a). Stacking chips are on                                                                  |     |

|            | one side of interposer; (b). Stacking chips are on both sides of                                                                  |     |

|            | interposer                                                                                                                        | 32  |

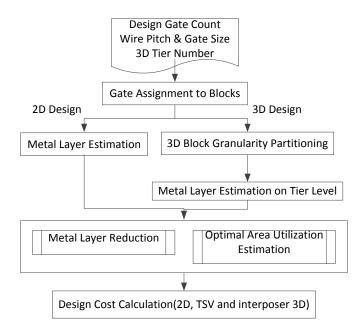

| 3.2        | Cost efficient design exploration flow in 2D, 3D TSV bonding and                                                                  |     |

|            | 3D interposer stacking integrating metal layer reduction technique.                                                               | 33  |

| 3.3        | Cost comparison between design implementation on 2D, 2 layer 3D                                                                   |     |

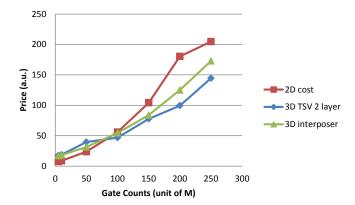

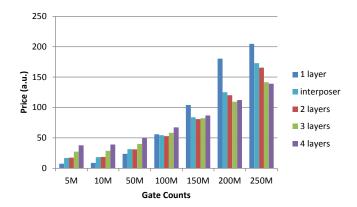

|            | TSV, and 2 layer 3D interposer designs                                                                                            | 36  |

| 3.4        | Product costs of 2, 3, and 4 layers TSV based 3D designs, 2D and                                                                  |     |

|            | interposer based design costs are shown for comparison                                                                            | 37  |

|            |                                                                                                                                   |     |

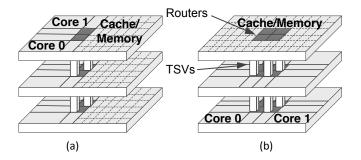

| 4.1  | Overview of core-to-cache/memory 3D stacking. (a). Cores are                |    |

|------|-----------------------------------------------------------------------------|----|

|      | allocated in all layers with part of cache/memory; (b). All cores           |    |

|      | are located in the same layers while cache/memory in others                 | 41 |

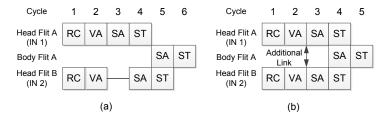

| 4.2  | Timing diagram of the packet latency reduction with additional              |    |

|      | channel width. (a) Original design with fixed channel width; (b)            |    |

|      | Designs with additional output channel width                                | 45 |

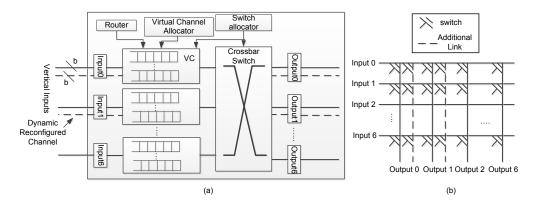

| 4.3  | Virtual-channel based router structure and the corresponding cross-         |    |

|      | bar. (a). Virtual-channel based router architecture; (b). The cross-        |    |

|      | bar design supporting additional vertical links                             | 46 |

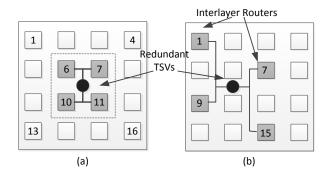

| 4.4  | Router placements on the core layer for a 16-core system. (a). The          |    |

|      | interlayer routers are placed in the middle; (b). The interlayer            |    |

|      | routers are distributed evenly across the core layout                       | 49 |

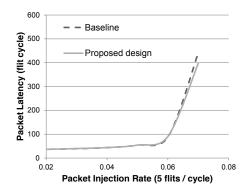

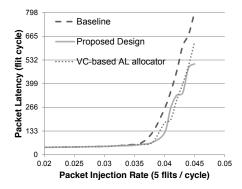

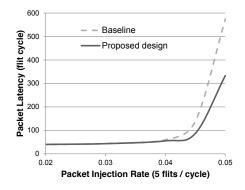

| 4.5  | Packet latency of uniform traffic in a $4\times4$ mesh network              | 52 |

| 4.6  | Packet latency of interlayer traffic in a $4\times4$ mesh network           | 52 |

| 4.7  | Packet latency of weighted interlayer traffic in a $4\times4$ mesh network. | 52 |

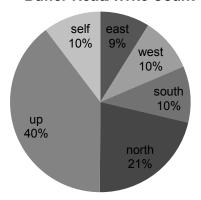

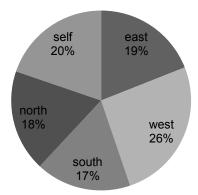

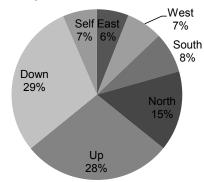

| 4.8  | The input buffers read/write ratio analysis of the interlayer router.       | 55 |

| 4.9  | The input buffers read/write ratio in different directions of the 2D        |    |

|      | router                                                                      | 55 |

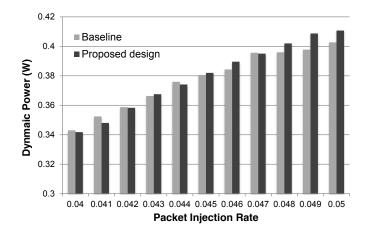

| 4.10 | The dynamic power consumption comparison between baseline and               |    |

|      | proposed design.                                                            | 56 |

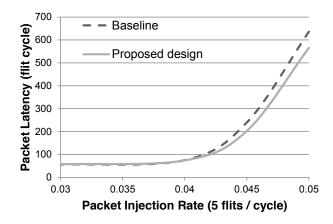

| 4.11 | The average packet latency in 8×8 mesh network with the weighted            |    |

|      | interlayer traffic                                                          | 56 |

| 4.12 | The input buffers read/write ratio of the interlayer router in the          |    |

|      | middle layer.                                                               | 57 |

| 4.13 | The average packet latency with different locations of unavailable          |    |

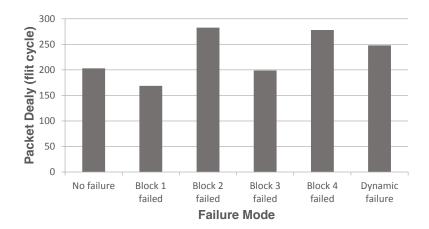

|      | spare TSVs and dynamic failure modeling                                     | 58 |

|      |                                                                             |    |

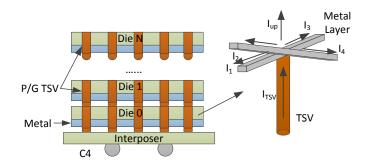

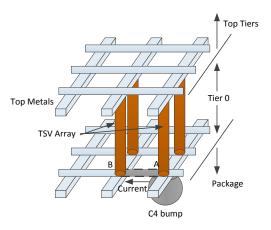

| 5.1  | The overview of stacked dies with 3D P/G network                            | 63 |

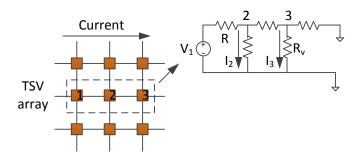

| 5.2  | Top view of TSV array with unevenly distributed current                     | 63 |

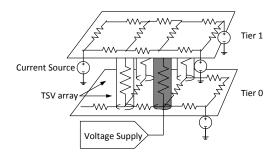

| 5.3  | The EM lifetime analysis framework of TSV arrays consists of cur-           |    |

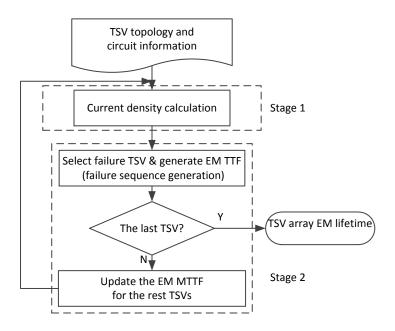

|      | rent distribution calculation and array lifetime estimation                 | 65 |

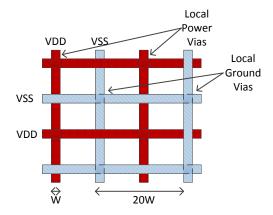

| 5.4  | The 2D planar P/G grid network model on each tier                           | 66 |

| 5.5  | The portion of 3D power supply network with one TSV array (only             |    |

|      | VDD is shown)                                                               | 66 |

| 5.6  | The corresponding resistance path of 3D power supply network                | 67 |

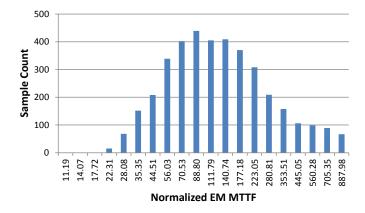

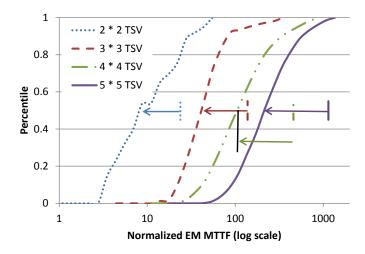

| 5.7  | $4\times4$ TSV array lifetime distribution                                  | 72 |

| 5.8  | EM lifetime distribution with different TSV arrays. The y-axis              |    |

|      | shows the number of samples/percentile, and x-axis shows the nor-           |    |

|      | malized EM lifetime in log scale                                            | 72 |

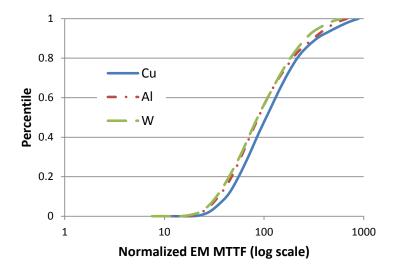

| 5.9        | TSV array EM lifetime distribution with different filling materials: Cu, Al, and W. The y-axis shows the percentile of the TTF distribution, and x-axis shows the normalized lifetime in log scale.                                   | 73  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

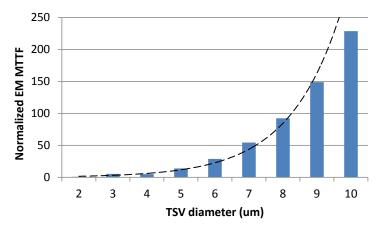

| 5.10       | TSV array EM MTTF with different TSV counts in the array under                                                                                                                                                                        |     |

| 5.11       | three different current stresses                                                                                                                                                                                                      | 75  |

|            | rent load                                                                                                                                                                                                                             | 75  |

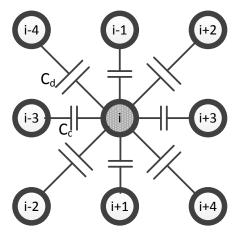

| 6.1        | The capacitance crosstalk model in a $3\times3$ TSV array                                                                                                                                                                             | 80  |

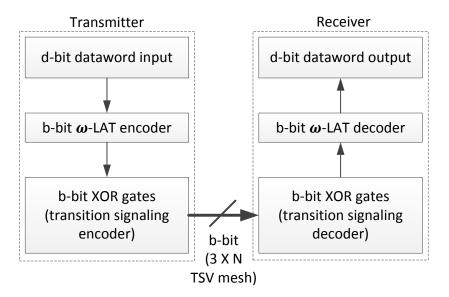

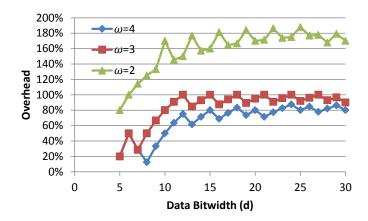

| 6.2<br>6.3 | Framework overview of signal transmission with LAT coding scheme. The overhead caused by redundant TSVs with different $\omega$ . The horizontal axis is the bitwidth of dataword and the vertical axis is                            | 84  |

|            | the overhead percentage.                                                                                                                                                                                                              | 87  |

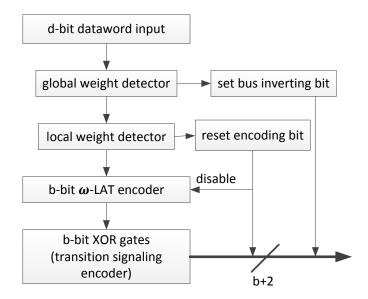

| 6.4        | The overview of signal transmission procedure after overhead opti-                                                                                                                                                                    |     |

| 6 5        | mization                                                                                                                                                                                                                              | 88  |

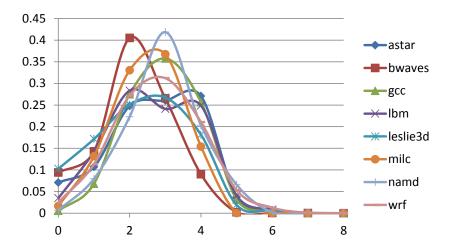

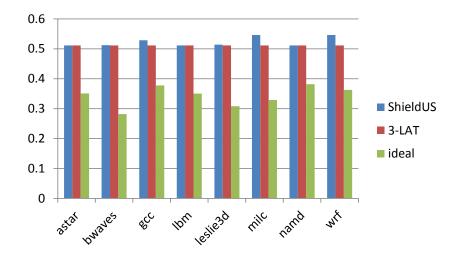

| 6.5<br>6.6 | The benchmark crosstalk characteristic in 3D cases                                                                                                                                                                                    | 93  |

| 0.0        | minimization schemes normalized to uncoded case                                                                                                                                                                                       | 94  |

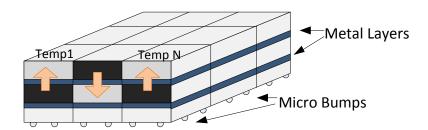

| 7.1        | Stack level thermal cycling effect in 3D structure. Thermal stresses are pointing from hot blocks(dark color) to cool blocks(light color). Alternating direction of stresses (the arrows) easily cause cracking on thinned substrate. | 98  |

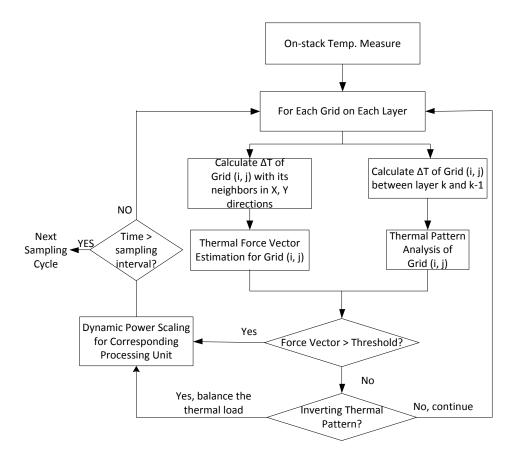

| 7.2        | Run-time thermal cycling-aware thermal management flow for one                                                                                                                                                                        | 30  |

|            | sampling cycle                                                                                                                                                                                                                        | 101 |

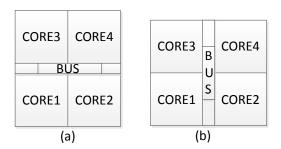

| 7.3        | Floorplan of the core-layer before and after optimization. (a) TSV bus is placed horizontally in the floorplan for wire length and area driven floorplan; (b) TSV bus is placed vertically after thermome-                            |     |

|            | 1                                                                                                                                                                                                                                     | 104 |

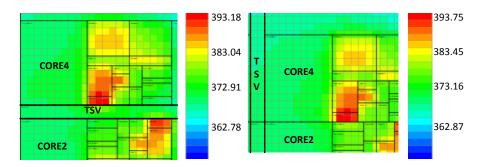

| 7.4        | Zoomed in TSV thermal stress-aware floorplan on core-layer. (a) TSV bus is placed horizontally between execution units of two cores, resulting in higher TSV temperature; (b) TSV bus is placed verti-                                |     |

|            | cally to for reduced thermal load                                                                                                                                                                                                     | 105 |

| 7.5        | Zoomed in memory layer run-time thermal management results.                                                                                                                                                                           |     |

|            | The zoomed region causes inverting thermal cycling pattern be-<br>tween two layer. (a) The thermal map before power scaling; (b)                                                                                                      |     |

|            |                                                                                                                                                                                                                                       | 106 |

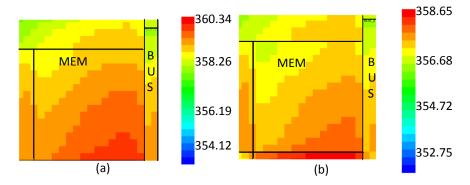

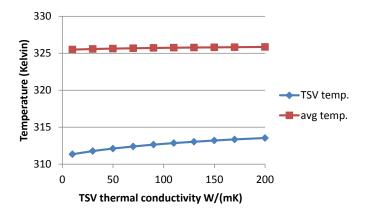

| 7.6        | Temperatures with different TSV thermal conductivity settings                                                                                                                                                                         |     |

| 7.7        | Temperature results with different TSV diameters                                                                                                                                                                                      |     |

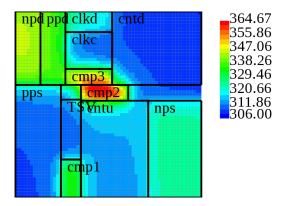

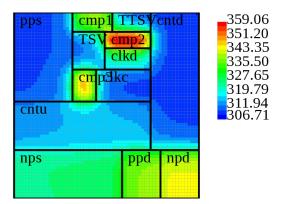

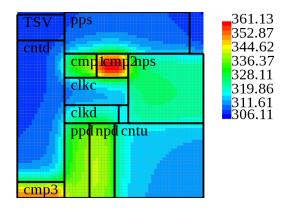

| 7.8        | Thermal maps of benchmark $hp$ without thermal vias                                                                                                                                                                                   | 108 |

| 7.9  | Thermal maps of benchmark $hp$ with thermal vias                | 109 |

|------|-----------------------------------------------------------------|-----|

| 7.10 | Thermal maps of benchmark $hp$ when reducing the weight of wire |     |

|      | length without thermal vias                                     | 109 |

| 7.11 | Thermal maps of benchmark $hp$ when reducing the weight of wire |     |

|      | length with thermal vias                                        | 110 |

### **List of Tables**

| 2.1        | Multi-core processor design system cost comparison                                                                                      | 25       |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1<br>3.2 | Parameters used in the experiments                                                                                                      | 36       |

| 3.3        | for 2D, TSV and interposer based 3D                                                                                                     | 37       |

|            | mal area utilization with default metal layers                                                                                          | 38       |

| 3.4        | Cost Savings of 2D, 3D TSV bonding, and 3D interposer stacking designs with metal layer reduction technique                             | 39       |

| 4.1        | The synthesized area and power of 2D/3D routers, crossbar, and                                                                          | ۲1       |

| 4.2        | AL arbitrator                                                                                                                           | 51<br>57 |

| 5.1        | EM MTTF with fixed area budget                                                                                                          | 76       |

| 6.1<br>6.2 | Coding overhead comparison results of with and without optimization.  The power consumption related parameters comparison between       | 89       |

| 0.2        | uncoded, ShieldUS, 3D 6C CAC, and 3-LAT schemes                                                                                         | 92       |

| 7.1        | Thermal parameters that are used in the experiments; sensitivity study is performed with various TSV lateral thermal conductivity       | 100      |

| 7.0        | and TSV diameter                                                                                                                        | 102      |

| 7.2        | Design time thermomechanical stress-aware floorplan results with<br>average and peak on-chip temperature and thermal stresses reduction | 103      |

| 7.3        | The normalized area/wire length and execution time comparison                                                                           |          |

| 1.0        | The normalized area, whe length and execution time comparison                                                                           | 100      |

### **Acknowledgments**

First of all, I would like to express my sincere gratitude to my advisor Professor Yuan Xie. He introduced me to the world of computer engineering and encouraged me to pursuit my Ph.D. degree when I was confused about my future. His unconditional help and patient guidance throughout all these years make my Ph.D. study more smooth and impel me to conquer the problems in hard times. His positive attitude and passion towards research and working inspire me and become one of the important factors to stimulate my growth in both research and personality.

I would like to thank all my committee members as well, Professor Mary Jane Irwin, Professor Vijaykrishnan Narayannan, and Professor Donghai Wang, for their precious advices and feedback on my research work.

I would also like to thank all my colleagues and friends from MDL group for their kind suggestions and supports on both my life and research: Xiaoxia Wu, Xiangyu Dong, Jin Ouyang, Cong Xu, Jishen Zhao, Matt Poremba, Jia Zhan, Ping Chi, Ivan Stalev, Yang Zheng, Shuangchen Li, and Ziyang Qi. Especially, I owe my thanks to my roommates, Hsiang-Yun Cheng, Jue Wang, Lin Chen, and Zhuo Chen for providing me a such warm and cozy living and study environment. Also, I want to thank my co-authors, Yibo Chen, Dimin Niu, Tao Zhang, and Jing Xie, as they gave me tons of valuable suggestions on my research work. Besides, I want to thank all my Ph.D friends from other departments: Chu Huang, Yiqiang Han, Yan Cao, and Zhe Liu, for their companion. During my intern at Huawei Shannon Lab, I learned a lot and got plenty helps from my collaborators, including but not limited to Rui He, Xing Hu, Shihai Xiao, and Wei Yang.

Finally, I owe my deepest gratitude to my family. I thank them for their understanding and supportive love for my every wilful decision. Especially, I want to express my heartfelt thanks to my husband, Wei Zhou, for backing me up across the ocean for these many years without a single complaint.

#### Introduction

In this chapter, the background of three-dimensional integrated circuits (3D ICs) is first introduced. Then the state-of-art design methodologies of 3D ICs are discussed followed by the challenges that hinder the massive volume production in the industry. The organization and contribution of the remaining chapters are then given.

#### 1.1 3D Integration Technologies

With technology scaling, the continuously decreasing transistor size implicates higher integration density [1]. Inevitably, this integration density translates into ever-growing interconnect length. Moreover, the scaled interconnect parasitics (smaller wire cross sections and smaller wire pitch) makes the interconnect emerge as a dominant source of circuit delay and power consumption [2,3]. The solution of the interconnect crisis is of paramount importance for deep-submicron designs. The 3D integration technology is one of the favorable solutions as it provides the benefits of short vertical interconnects, smaller footprint, and capability of heterogeneous stacking [4–6].

In general, there are three types of 3D designs in terms of the interconnect technologies: system-in-package designs, fine-grain integration, and contactless stacking. The first kind of integration can utilize the traditional 2D designs and connect the signals and I/Os through low density, relatively long vertical connections, such as wires or peripheral solder bumps. The second requires additional process steps

to build the vertical connections insider the device chip, thus it can provide higher density connections with lower latency. The third technology leverages the inductive or capacitive coupling for signal transmissions. The fine-grain 3D integration is attracting a growing number of popularity as it enables high density of vertical connections compared to the SiP and is free of distance restriction as compared to the contactless integration. As a consequence, this dissertation focuses on the design methodologies of this kind of integration.

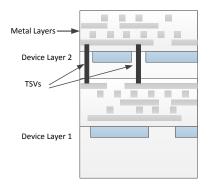

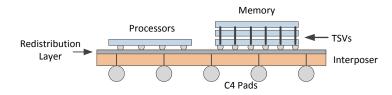

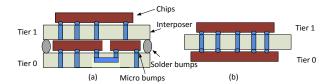

Specifically, the fine-grain integration can be conceptualized either as a parallel or a sequential process. In the parallel process, each individual dies are fabricated in parallel and through-silicon vias (TSVs) are built for signal connection between tiers. The wafer is then thinned to expose the TSVs and bonded to form a stack, as shown in Figure 1.1. Recently, integration circuits with TSV-based interposer (also known as 2.5D ICs, Figure 1.2) are emerging as alternatives of 3D ICs due to the simpler fabrication process and ease of cooperation between companies. In the parallel process, since the bonding is performed after individual fabrications, there are different bonding orientations and stacking methods. In terms of bonding orientation, it can be classified into face-to-back (F2B), back-toback (B2B), and face-to-face (F2F) bonding, in which, the face represents the side with active devices and the back is the bulk silicon. For F2B and B2B stackings, TSVs are required for signal and I/O connections, while in the F2F bonding, the micro-bump is utilized to connect the topmost metal layers of two dies for signal communications, and TSVs are used for I/O connections. The stacking can be realized in three strategies: die-to-wafer (D2W), die-to-die (D2D), and wafer-to-wafer (W2W), which is distinguished by whether the die is sliced before it is stacked. In general, W2W stacking can shorten the time-to-market, however, it has the lowest compound yield as any bad dies in the stack will pollute the final stack. D2W and D2D stacking can prevent the bad dies from polluting good stacks, nevertheless, the requirement for testing of each individual dies increases the system cost and prolongs the time-to-market.

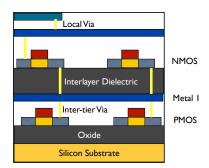

In contrast, the sequential process, also named as monolithic 3D ICs (Figure 1.3), requires the device layers to fabricate sequentially and the Monolithic Inter-die Vias (MIVs) are built with traditional back-end-of-line (BEOL) technology. The small size of MIVs supports higher density integration at finer granularity

Figure 1.1. Conceptual view of TSV-based 3D integration.

Figure 1.2. Conceptual view of interposer-based 3D integration.

3D partitioning, even at the granularity of transistor. The sequential process poses numerous challenges in 3D monolithic design since the high temperature during fabrication compromises the device mobility. As a consequence, before the technology becomes viable and reliable for complete 3D monolithic, the parallel 3D integration is the precursor.

Figure 1.3. Conceptual view of monolithic 3D integration.

## 1.2 Existing Physical Design Methodologies of 3D ICs

Due to the additional third dimension, the circuit design cannot be directly migrated from 2D ICs. Innovated design methodologies are necessary to fully unleash the benefits of 3D ICs. In this section, the existing physical design methodologies targeting 3D ICs are introduced.

#### 1.2.1 3D Partitioning and Floorplanning

Partitioning. The partitioning step is unique in 3D designs and it has great influence on the following floorplanning quality. In this design stage, we need to identify the 3D integration technology, the partitioning granularity, and the design objective. Generally speaking, the partitioning can be done on fine granularity (gate level), or on coarse granularity (block/core level). With smaller vertical connections (e.g. 3D monolithic), finer granularity partitioning can be realized. Different partitioning mechanisms result in various design benefits [7–13]. For example, Loh et at. [14] proposed three cache partitioning schemes and compared the differences in performance improvement and latency/energy reduction.

Floorplanning. To enhance the design flexibility, the layer position is usually determined during floorplanning, which defines the placement in the block granularity. In this stage, the blocks can be moved within one layer or between layers to obtain the optimal result in terms of area or wirelength.

The generalized problem formulation of floorplanning can be described as below. Given a set of modules/blocks with the geometry information of each component, the allowable aspect ratio during rotation, and the total number of layers; based on the design objective, determine the coordinate of each block. According to the design objective, additional information may be needed. For example, when the temperature is more important, the power density of each block should be considered.

Various floorplan representations in 2D ICs can be used in 3D designs, such as sequence pair and B\*-tree. Meanwhile, new floorplan topologies are denoted with novel representations [15, 16]. After the floorplan representation and the

design objective are determined, the floorplan algorithm manipulates the block position until the optimal result is found. Numbers of floorplanning strategies targeting on different design objectives have been proposed [17–22]. Jung et al. [23] studies the impact of block folding and bonding styles on top of traditional 3D floorplanning to improve the power benefits of 3D ICs. Their design offered up to 20.3% power reduction over the 2D counterpart under the same performance. Tsai et al. [18] emphasized the TSV planning on accurate wirelength estimation during the floorplanning. Falkenstern et al. [24] used B\*-Tree for representation and consider the power/ground network synthesis during floorplanning to reduce the potential IR drop. Khan et al. [15] proposed a new topological structure for floorplanning in 3D ICs to minimize the total volume of 3D die.

#### 1.2.2 3D Placement and Routing

Placement Based on the block position decided by floorplanning, the cell/gate position is determined during placement. Different from 2D designs, the 3D placement not only needs to consider the cell spreading on the xy plane, but also in the vertical direction. If temperature is the primary concern, then cell placements on the upper layers should be sparser than the bottom layer which is near heat sink. Temperature and wirelength are two major design objectives during placement.

Various of placement methodologies are presented by previous studies [25–29]. Cong et al. [30] proposed to use transformation for 3D placement with the awareness of temperature. In their proposed framework, a 2D placement is first generated with specific design objective. Then local stacking transformation and a folding-based transformation are used to change the 2D placement into 3D placement. A 3D level refinement is performed to guarantee the design quality. Athikulwongse et al. [31] proposed two thermal-aware global placement algorithms employing the force-directed methodology to exploit the die-to-die thermal coupling in 3D ICs. The first algorithm generates forces for TSV spreading and alignment for better heat dissipation path. The second algorithm builds forces based on thermal conductivity in cells and on power density for TSVs. Their second methods can achieve the best temperature results among state-of-the-art placers. An analytical placer is proposed by Cong et al. [32]. They took the thermal effect of TSVs into

consideration and co-placed cells and TSVs. Experimental results show that their method can reduce the peak temperature by 34% on average.

Routing. In 2D routing, optimization targets usually include wirelength, the interconnect delay, and the routing congestion. When moving to the 3D design, more issues should be considered. First, the interconnect delay is closely related to its temperature, therefore, wires on the critical path should avoid the hot regions, moreover, the interconnect placement should consider help alleviate the on-chip temperature [33,34]. In addition to the temperature, other factors also influence the interconnect, such as thermal stresses, which should be addressed in the routing stage for better and robust performance [35]. The second problem rises from the limited number of TSVs. Due to the large size of vertical interconnects, TSVs are scare resources and should be optimally allocated. Third, the congestion management and blockage avoidance become more complicate, especially when considering the thermal via insertion [36, 37]. The routing on each tier is similar to the traditional 2D routing, only extended to the third dimension with limited vertical routing capacities.

The 3D routing begins from building a minimum spanning tree or steiner tree similar to 2D routing. Then a multi-objective routing algorithm is applied to guide the routing. The associated signal TSV and thermal TSV assignment are commonly accomplished with two approaches: a heuristic multilevel approach and a linear programming (LP) based approach [38–40]. Two stages of TSV positioning are performed to first locate TSVs according to Steiner tree considering the wirelength. Then the stacked-TSV relocation stage assign stacked TSVs near hotspots for temperature reduction [38]. The stacked-TSV assignment exhibits 17% temperature reduction with 4% wirelength overhead and 3% performance degradation. Pathak et al. [39] employed the similar idea as moving TSVs close to hotspots to reduce the cost of dummy TSVs insertion after the initial tree construction. They proposed a relaxed ILP-based formulation to optimize all nets simultaneously. A 9% maximum-temperature reduction is gained with their TSV relocation. At last, the level-by-level routing refinement is performed to alleviate the congestion.

#### 1.3 Existing System Level Design Methodologies

In addition to the physical level design methodologies, plenty of research efforts are devoted into the system level or the high level design methodologies of 3D ICs. Different from physical level designs, the system level designs focus more on the holistic optimization and whole system design tradeoffs in accordance with design requirements. It sometimes involves the architecture-level or system-level design space exploration to find the optimal design point [41–43].

The first possible direction of system level design space exploration is incorporated with high-level synthesis techniques [44–47]. In the high-level synthesis, the system behavior is described in natural language or high level programming language, and various related components are provided as candidates to assemble an optimized system. These components can be either hardware solutions or software solutions, and usually, the same functionality has different implementations. Different from previous 2D designs, the 3D integration synthesis should take the benefits of vertical connections into consideration, and might incorporate with detailed physical level design techniques as demonstrated by Chen et al. [45]. Another methods in system level design is to chain the available EDA tools to form a holistic design tool chain [48].

In addition to the above-mentioned two methodologies, the architecture level 3D integration is examined by various studies focusing on the 3D logic-to-logic stacking in the multicore processor designs or even FPGA designs [49–51], or the more prevalent memory-to-logic stacking to solve the memory bandwidth issues [52–55]. By stacking computing or communication fabrics on top of others brings close proximity, results in advanced performance, lower latency, and energy efficiency. Even though 3D designs can improve system performance without substantial architecture modifications, Loh pointed out that by implementing only a few simple changes to the commodity DRAM organization, a 1.75x speedup can be achieved against baseline 3D DRAM [52].

Besides the homogeneous architecture designs, the heterogeneous system design space is explored to unleash the benefits of 3D ICs [56,57]. The heterogeneous integration can build from four aspects: different on-chip network components, such as electrical and optical connections [58–60]; different memory technologies, such

as traditional SRAM/DRAM with non-volatile memory [61–63], different computing logics, such as general purpose CPU, GPUs, and accelerators [64–66]; different signal handling systems, such as analog circuits and digital circuits [67,68].

#### 1.4 Opportunities and Challenges in 3D ICs

The advantages of 3D ICs attract numerous architecture researchers' attention to solve the prominent Memory and Power Wall problems. Lots of literatures are presented in recent high quality conferences, such as using stacked DRAM as cache [69] or as on-chip memory for high bandwidth computing [53]; or stacking heterogeneous computing/storage fabrics for energy-efficient operations [70].

In addition to academia, the commercial adoptions of 3D memory and 3D FPGA have demonstrated the promising future of 3D integrations. For example, the High Bandwidth Memory standard as proposed by JEDEC [71] can provide as high as 256GB/s bandwidth, targeting on graphic applications. The Hybrid Memory Cube system is proposed to support multiple stacked DRAM through SerDes links and the maximum bandwidth can reach 320GB/s [72]. Moreover, the 2.5D design has been applied to Xilinx Virtex-7 FPGA to enable high-bandwidth connections between multiple dies and provide a  $100 \times$  improvement in inter-die bandwidth per watt [73].

Even these examples from both academia and industry show promising future of 3D ICs, there are still some stoppers before massive production of more sophisticated 3D circuits, such as the thermal management, reliability problem, testing mechanisms, and cost issues.

The thermal problem in 3D ICs exacerbated due to two reasons: the reduced proximity between active devices and the increased distance from the bottom devices to the topmost heat sink. Numerous solutions are proposed to boost the thermal dissipation capability, such as incorporating with more powerful cooling solutions [74–76] and inserting dummy TSVs for building effective vertical dissipation path [38, 77]. The reliability problem stems from either manufacturing limitations or design issues. The manufacturing constraints introduce new circuit failures and fault models, such as TSV open/short defects, thermal mechanical stresses, and device mobility variations [78–82]. Moreover, design level consider-

ations should include signal integrity, power/ground network with less IR droop, and balanced clock network designs [83–88]. The reasons that testings become critical and challenge in 3D ICs can be classified into three categories: new defect modes as in the reliability problem, incomplete functionality on each individual layer, and lack of testing methodologies (pre-bond, intermediate, and post-bond tests) [89–93]. Cost is the primary driving force for industrial adoption of 3D ICs. However, due to the extra wafer thinning and bonding processes, the fabrication cost of 3D ICs is not always lower than that of 2D counterparts. Moreover, in consideration of the re-design and testing efforts, the ever increasing non-recurring cost further worsens the final selling price [94–96].

Currently, most researchers focus on the physical and system level design methodologies to reduce the wirelength and chip area, addressing the power and memory wall problems. However, the prominent challenges in 3D ICs are not properly solved, especially the thermal and reliability problems. Therefore, in this dissertation, reliability and cost are the two primary concerns in the proposed 3D design methodologies and optimizations.

#### 1.5 Contribution and Organization

In this dissertation, the design methodologies and optimizations of 3D ICs are proposed to consider the integration cost and reliability issues. Different from previous studies that ignore the impact of cost in practical designs, the proposed cost-aware design methodologies are easy for industrial adoption. Moreover, the proposed reliability-aware design approaches perform reliability analyses and give circuit/architecture level implications from various reliability aspects (electromigration, thermo-mechanical stresses, etc.)

The following chapters are organized as following. Based on the 3D cost model, Chapter 2 proposes a cost evaluation framework with the assumption of test elimination given the assumption that the fabrication yield is sufficient high. Chapter 3 reviews the routing process and the cost of building metal layers, then describes the aggressive metal layer reduction technique to sacrifice chip area for cost saving from less metal layers. The cost saving technique to reuse the redundant TSVs can be applied on the architecture level for NoC designs, as introduced in Chapter 4.

Three studies are selected towards the reliability problems. Chapter 5 reconsiders the electromigration (EM) problem given that TSV array is usually used for signal transmission instead of a single TSV. The EM lifetime in an array should be different from the analyses of an isolated TSV. Chapter 7 takes the thermo-mechanical stresses into consideration, and proposes a two-stage thermal stress management scheme in both design-time and run-time. The large size and close proximity of TSVs pose challenges in signal integrity due to the capacitance coupling. Chapter 6 analyzes the crosstalk phenomenon in the TSV array and a coding-based crosstalk minimization technique is then proposed. At last, Chapter 8 provides the conclusion and the future work.

# Cost Analysis Framework with Test Elimination

As illustrated in Chapter 1, several shortcomings hinder the commercial adoption of 3D designs. Among these challenges, the 3D integration cost (both recurring and non-recurring cost) is one of the dominant factors [94–96] since the profit margin is the driving force for industrial migration to 3D designs. In this work, we propose to reduce the final system cost by exploring the possibility of test elimination given that the die yield would be sufficient high as fabrication process improved<sup>1</sup>.

In the final system cost breakdown, test cost stands out as one of the major contributors [94,97,98]. In addition, as the CMOS manufacturing process becomes mature, the fabrication cost decreases, which results in a higher percentage of the test cost. Moreover, in 3D designs, testings pose numerous challenges due to the insufficient understanding of 3D testing issues and the lack of efficient testing solutions. There are two major reasons lead to the testing differences between 3D designs and 2D counterparts. The first reason is that any given layer may contain uncompleted modules (e.g., networks for power delivery and clock distribution) due to the function partitioning in 3D ICs. The thinned wafer and the resulted mechanical vulnerability are the second reason. Wafers need to be thinned to expose vertical vias (i.e. TSVs). However, the wafer level probing force, which is about 60-120kg per wafer [99], may damage the thinned wafers.

$<sup>^1{</sup>m This}$  work is published as "A cost benefit analysis: the impact of defect clustering on the necessity of pre-bond tests" on 3DIC 2015.

Pre-bond and intermediate tests are unique in D2W and D2D stackings. Previous studies have shown that cost saving can be obtained through the pre-bond or intermediate testing because it eliminates further process steps on failed stackings [98,100,101]. However, these observations are based on the wafer yield which may be underestimated through the Poisson model or the Generalized Negative Binomial (GNB) model [102]. With the presence of defect clustering [103,104], the die yield should be determined by both the defect count and the defect distribution. If most defects are clustered in a small region, die yield could be significantly higher than the case with random distribution, even though the defect rates are the same. Therefore, under this circumstance, potentially we can eliminate the pre-bond and intermediate testings without elevating the integration cost.

To further reduce the integration cost, we also investigate how the partially functional dies help the system cost. In order to provide advanced and robust performance, multiple disjoint units with the same functionality might be placed on a single die (e.g., homogeneous multicore designs). Partially functional die represents the die that contains some workable units even one or several units are malfunctioned. Rather than simply discarding them, we can sort out the slightly defective dies for lower price according to the design expectation, that is, the expectation of the number of functional units per die. Thus, the traditional concept of bad die is changed to partially functional die for homogeneous multiunit designs. Therefore, partial yield is defined as the ratio of defective dies that can fulfill the design expectation accordingly.

To help manufactures and designers make testing decisions at the early design stage, we build a cost benefit analysis framework. In addition to the testing elimination decision, the framework also provides the estimated system cost using corresponding analytical models. To support the proposed framework, we further provide a hierarchical yield model to estimate both die and partial yields. We reveal the analytical model for partial yield by investigating the relation between partial yield and the density of defect clustering. With this framework, we discuss how different cost parameters influence the system cost. From the analyses, we find that wafer cost is the most significant factor on test elimination and cost saving.

#### 2.1 Preliminaries and Motivation

In this section, the preliminaries of die yield calculation and the motivation example are demonstrated. Previous work on 3D cost analyses and yield enhancement are briefly introduced.

**Preliminaries on yield modeling.** GNB yield model, as shown in Equation 2.1, is prevalently used in previous studies for the depiction of defect clustering, when the defect density  $(D_0)$  and die area (A) are given. By adjusting the parameter  $\alpha$ , different clustering degrees can be expressed. The smaller value of  $\alpha$ , the higher clustering degree.

$$Y(GNB) = \left(1 + \frac{D_0 A}{\alpha}\right)^{-\alpha} \tag{2.1}$$

Even the GNB yield model considers the defect clustering to some extent, it cannot accurately capture the die yield under extreme clustered defects. Moreover, the value of  $\alpha$  is hard to determined even given the defect distribution on a wafer.

Motivation. As manifested from previous studies [96–98], the test cost is one of the major contributors of the 3D system cost. We assume a 4-layer D2W stacking is used, and vary the test cost (increasing the test cost up to 4 times) and die yield to illustrate the ratio of test cost. The cost parameters (value of test cost, wafer cost, etc.) are consistent with the prior study [98]. The cost estimation is based on previous 3D cost model [96] and the results are depicted in Figure 2.1. When the die yield increases, which is likely to happen due to the continuous evolvement of fabrication process, the test cost increases almost linearly. The growing step becomes larger with higher testing costs. For example, when the testing cost is four times of the original value, the percentage increases more than 3%, while in the original case, the percentage increases less than 1%. Moreover, according to the observations in [97], the testing cost percentage increases with more stacking tiers. In this example, the testing circuit overhead is not included, resulting in an underestimated test cost. If the pre-bond/intermediate test is performed for every die and every intermediate stacking in D2W integrations, the circuit overhead for testing makes the test cost unaffordable.

The compound yield of the whole stacking would influence the selection of test flows. Therefore, we want to study when the die yield is high, what would happen

Figure 2.1. The test cost percentage in 3D integration with different die yields.

to the system cost if we eliminate the testing. Assume a wafer has a defect rate of  $0.5 \text{ defects}/cm^2$  and a diameter of 300mm, and the die area is  $50mm^2$ . The calculated yield with GNB model is 81.65%. The compound yields are as low as 66.67%, 54.43%, and 44.45% when the stacking contains 2 tiers, 3 tiers, and 4 tiers, respectively. With our die yield simulation, which generates defect maps with given clustering degree, the statistical die yield can be as high as 97.6%, marked as the simulated yield.

Based on the assumption above, we conduct a study to find out the cost influence when eliminating pre-bond/intermediate testings. The integration system costs of four cases are shown: GNB model with tests (basic case), GNB model without tests, simulated yield with tests, and simulated yield without tests. Figure 2.2 shows the system costs of 3 and 4 layers stackings which are normalized to the cost of 2-layer basic case. We observe that the cost saving from only manufacturing yield improvement is not so obvious when comparing cases 1 and 3 which are with tests. However, when comparing cases 2 and 4, dramatic cost saving is achieved with higher die yield. Moreover, when the die yield is high enough (case 3 and 4), the estimated cost difference between testing and testing elimination scenarios becomes negligible, meaning that the cost saving from testings is marginal. These results reveal the opportunity of eliminating pre-bond/intermediate tests when the yield is high. The test elimination poses negligible cost overhead yet can shorten the time to market.

**Prior Work.** The 3D test cost and system cost have been modeled and analyzed by previous studies [96–98]. Numerous cost-efficient designs and optimization flows are explored [94, 95, 105]. Researchers find that the selection of testing flows

Figure 2.2. The normalized system cost of four cost estimation combinations.

has significant impact on the final integration cost [94,98]. The 3D testing can be categorized into four steps: pre-bond tests to filter good dies; intermediate tests to ensure the functionality after die bonding; pre-package tests for the whole 3D integration before package; and post-package tests for the product integrity. The pre-bond and intermediate tests are unique in the die-level stackings, while pre-package and post-package tests are essential for all 2D and 3D designs. In this work, when we consider eliminating the test, we refer to pre-bond and intermediate tests. The later two tests cannot be eliminated since the final system functionality should be guaranteed before marketing.

In addition to testing, wafer/die matching and redundancies sharing between tiers are two major yield enhancement methods [90,106–109]. Usually, three metrics can be used during the matching process: maximized the matched good dies, maximized the matched bad dies, or minimized the unmatched bad dies. In the wafer matching method, the wafer are carefully selected from wafer repositories to increase the yield. The method of die matchings considers the redundancy resources to guarantee redundancies are enough to share between dies. As such, the final compound yield is increased. The limitations of these studies are that they diminish the product throughput and current algorithms only handle the matching between two layers. However, these mechanisms are orthogonal to our work and can be combined for further cost saving.

#### 2.2 Cost Benefit Analysis Framework

As demonstrated in Figure 2.2, when the die yield is high enough, the pre-bond or intermediate tests can be eliminated for cost saving. Furthermore, the partially functional die can be applied to gain more profit for amortizing the cost. However, various design tradeoffs may affect the cost saving. When the bonding cost or wafer cost decreases, can the design still get benefits from the test elimination? What is the die yield turning point for pre-bond test elimination? How do the size and arrangement of homogeneous units affect the system cost? To answer these questions at an early design stage, we propose and implement a cost benefit analysis framework to select the cost-efficient design.

Our framework can be depicted in Figure 2.3. The inputs contain three parts: the defect mode, cost related parameters, and the design target.

**Defect Mode.** The defect mode is used to generate defect maps for the hierarchical yield model. The information of defect mode includes wafer defect rate, the defect clustering degree, and the yields during bonding and packaging. In our framework, we use the cluster diameter (generated by clustering algorithms from manufactures) to describe the clustering degree. At the early design stage, the detailed cluster size for each wafer cannot be obtained. Therefore, an estimated average value is enough for the cost evaluation. In addition to fabrication processes, defects can occur in the bonding and packaging steps in 3D designs. Wafers need to be thinned to around  $100\mu m$  to expose TSVs, which makes wafers vulnerable to mechanical stresses. Moreover, due to the manufacturing limitation, the TSV yield is beyond expectation. Plenty of work has been done to improve the TSV yield with redundancies [100,110], which significantly improves the bonding yield.

Cost Parameters. For 3D integrations, the system cost can be classified into four categories: wafer cost, bonding cost, testing cost, and package cost [96, 97]. The wafer cost is the major contributor to the system cost. The bonding cost is unique in 3D stacking, which contains the wafer thinning cost, TSV building cost, and bonding cost. The test cost includes all recurring and nonrecurring expenses in pre-bond and intermediate tests. The pre- and post-packaging costs are captured in the package cost category.

**Design Target.** The defect tolerance and unit design options should be given

**Figure 2.3.** The overview of the proposed framework for cost estimation and design option analysis.

in the design target. As illustrated in Section 2.3, the tolerant threshold can significantly influence the partial yield. Instead of giving the determined design, we require design options in our framework due to the impact of unit size and arrangement on the partial yield and die yield. Take the multi-core design as an example, if a total of 8-issue width design is needed, we can use four 2-issue width cores or two 4-issue width cores with different unit and die areas. Even when the die area is fixed, different unit arrangements influence the partial yield. For example, if the design of four 2-issue width cores is selected, placing the cores in  $2\times2$  or  $1\times4$  arrangement results in totally different unit yields. Therefore, holistic design consideration should be made considering both the die yield and partial yield. However, the enormous possible design combinations make the design space exploration infeasible. Fortunately, due to the thermal and power constraints for each design, the design options are limited, and they should be provided as an input in the framework.

The main body of the framework takes these three inputs and generates the cost-efficient testing and design decisions and the corresponding cost estimation. Multiple testing schemes are possible for any 3D stacking [94]. For example, we can choose to test circuit only, interconnect only, or circuit and interconnect during the intermediate test. In this paper, we only consider one testing scheme, which is the pre-bond test for every die and the intermediate test for both device and interconnect whenever a bonding process is established. Although only one test scheme is assumed in this work, other schemes can be easily applied in the framework. The cost saving of partially functional die is determined by the

partial yield which is influenced by the unit size and arrangement. Therefore, by varying the unit design, the die yield and partial yield are updated accordingly until a cost-efficient design is found. Then the die area is fixed, the die yield can be calculated from the combination of GNB model and simulation results or the defect model provided by the manufacture. The decision that whether performing the pre-bond/intermediate test or not can be made given the die yield and cost parameters.

After design decisions are determined, the cost evaluation is performed. According to [95, 96], the cost of a N-layer D2W stacking can be captured with Equation 2.2 combining with the pre- and post-packaging test. In the equation,  $C_{die_i}$  represents the die cost on tier i, which can be calculated using  $C_{wafer}/N_{die_i}$ .  $C_t$ ,  $C_b$ , and  $C_p$  are the test cost, bonding cost, and package cost, respectively.  $Y_p$  is the package yield determined after pre- and post-package testings.

$$C_{D2W} = \left(\frac{\sum_{i=1}^{N} (C_{die_i} + C_t)}{Y_{die_i}} + (N-1)C_b + C_p\right) / Y_p$$

(2.2)

If pre-bond and intermediate tests are eliminated, the expression of system cost is shown in Equation 2.3. Different from Equation 2.2, the bonding cost should be considered for every die (including defective dies). The corresponding compound yield, which is the multiplication of die yield in each tier, is applied. In this sense, the system cost for D2W and W2W stacking are similar. Note that in W2W designs, the die size in each layer should be the same.

$$C_{notest} = \left(\frac{\sum_{i=1}^{N} C_{die_i} + (N-1)C_b}{\prod_{i=1}^{N} Y_{die_i}} + C_p\right) / Y_p$$

(2.3)

When the die yield is not high enough or the bonding cost is relatively large, the test elimination causes significant cost loss. Therefore, we deduct the system cost equation combining the test elimination and partially functional die, which is shown in Equation 2.4.

$$C_{partial} = \left(\frac{\sum_{i=1}^{N} C_{die_i} + (N-1)C_b}{\prod_{i=1}^{N} (Y_{die_i} + Y_{p,th}(1 - Y_{die_i}))} + C_p\right) / Y_p$$

(2.4)

The partially functional die can also be applied even when testings are enabled.

In this case, we only need to add the partial yield to the Equation 2.2. Combining Equation 2.2 and 2.3, the turning point of die yield for test elimination is estimated as follows, assuming the die yield and die cost for each tier are the same:

$$C_t Y_{die}^{N-1} \ge N C_{die} (1 - Y_{die}^{N-1}) + (1 - Y_{die}^{N})(N-1)C_b$$

(2.5)

Induced from the equation, the cost parameters (bonding cost and wafer cost) play an critical role in the turning point. Therefore, when the test cost is relatively high compared to the bonding cost and die cost, it would be cost-efficient to eliminate the pre-bond/intermediate test.

#### 2.3 Hierarchical Yield Model

In this section, we describe our hierarchical yield model that comprises two levels. The first level combines the GNB model and simulation results for die yield estimation with the presence of defect clustering. The second level model estimates the fine-granularity partial yield under the influence of defect clustering.

Defect clustering representations have been studied by several work [103, 104, 111]. These models are suitable for the post-fabrication analysis, but not for cost estimation when the detailed defect information is unknown.

We consider different wafer defect situations given the wafer defect rate and defect clustering degree. The result shows that GNB model underestimates the die yield because of the inaccuracy in capturing the defect clustering. Therefore, apart from GNB model, we built a simulation framework to adjust the die yield estimation according to the defect clustering degree. The simulation framework generates massive wafer samples and the corresponding defect maps to mimic the defect distribution statistically. Combining the simulated yield (Y(sim)) and GNB yield, the die yield estimation is given by  $Y_{die} = \omega_1 Y(GNB) + \omega_2 Y(sim)$ , where  $\omega$  is the weighting parameter to represent the model confidence.

Nevertheless, the first level model is not adequate to determine the system cost when taking partially functional dies into account. Based on the definition, the partial yield is the ratio of the workable defective dies to the total defective dies. The number of reusable defective die depends on the design expectation,

the defect clustering degree, and the unit area. Intuitively, the larger the unit area is, the higher partial yield because fewer units may be affected by defects. Meanwhile, if the defect clustering degree is low, the distribution is more likely to be random, thus more units will be defective. Based on the above reasoning, we assume the partial yield  $Y_{p,th}$  is proportional to the unit area  $A_u$  and inversely proportional to the clustering degree  $C_r$ . The variable th represents the tolerant threshold (design expectation) that is determined by designers to represent how many malfunctioned units can be tolerated. By increasing the threshold, more defective dies can be used, however, the selling price for the severe defective dies may be low, which may degrade final profits.

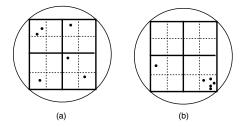

With our simulation framework, the value of  $Y_{p,th}$  is simulated with different defect clustering degrees and tolerant thresholds as shown in Figure 2.4. In the simulation, we assume the aspect ratio of the unit (the ratio of the unit width to the unit height) is fixed. The defect clustering degree is represented as the cluster diameter in the unit of mm. We set three levels of unit size: large, medium, and small, which means there are 4, 6, and 9 units per die (die size is  $50mm^2$ ), respectively. Two tolerant thresholds (1 and 2) are used.

From Figure 2.4, we can see the partial yield decreases significantly as the defect clustering degree increases at the beginning, then it increases gradually until stable. The rationale behind this is that when the defect clustering degree increases first, it has a higher probability that more units inside the die (note that the die area is fixed) are affected by the defects. However, when the clustering degree continuously increases, the defects are more disperse until they are nearly randomly distributed in the whole wafer. Therefore, given one die is defective, the probability that only a certain number of units (represented by th) are affected is high. In this case, the die yield is low whereas the partial yield is high. This phenomenon can be explained through a simple example shown in Figure 2.5. We only demonstrate four dies per wafer and four units per die for simplicity. Even though these two wafers contain the same number of defects, defects in Figure 2.5(a) are more scattered, resulting in a lower die yield. However, inside each die, mostly only one unit is affected and the partial yield can as high as 75%. For the concentrated defects as in Figure 2.5(b), the overall die yield and the partial yield are both high. It can conclude that the partial yield is influenced by the area ratio between units and

**Figure 2.4.** The variation in partial yield with different defect clustering degrees and two tolerant thresholds.

Figure 2.5. Both extremely centralized and extremely scattered defect distribution result in high partial yield. (a). Scattered defects; (b). Centralized defects.

defect clusters, we find the best fitting polynomial curve to analytically represent  $Y_{p,th}$  as the following:

$$Y_{p,th} = -k_1 R^3 + k_2 R^2 - k_3 R + k_4 (2.6)$$

where R represents the ratio of  $A_u/C_r^2$ .  $k_1$  to  $k_4$  denote the empirical coefficients. The values of  $k_1$  to  $k_4$  are 0.0006, 0.0160, 0.08, and th/2, respectively, according to the simulation results in Figure 2.4. This equation can capture the partial yield with the maximum error of 7% with various configurations. The equation is of higher accuracy when the size of the defect cluster is small.

#### 2.4 Experiment and Cost Analysis

In this section, impacts of different design inputs on the system cost are evaluated. These design inputs include the variations of design parameters (the die area, unit area, and unit arrangement), cost parameters<sup>2</sup>, and the clustering degree. For

<sup>&</sup>lt;sup>2</sup>Arbitrary unit (a. u.) is used for cost values due to the non-disclosure agreement with our industry partners.

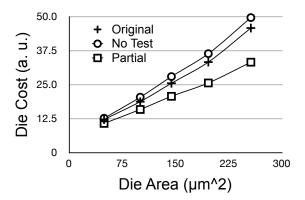

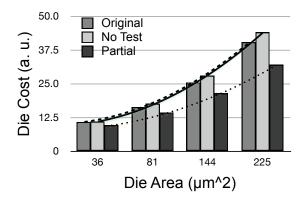

Figure 2.6. Cost variations with different die sizes when the unit count is fixed.

each set of experiments, costs in three scenarios are used for comparison: the basic case, which uses the GNB yield model with the pre-bond and intermediate test; the non-testing scenario, which eliminates the pre-bond/intermediate test and uses the simulation adjusted die yield; and the partially functional case, which includes both non-testing and the hierarchical yield. The tolerant threshold is set to 1 and a two layer face-to-back design is used. The basic configuration is that the defect cluster radius is fixed as 10mm, the wafer defect rate as 0.5 defects/ $cm^2$ ,  $\alpha$  as 0.5 in GNB model, and the die area as  $50mm^2$  with four same size units per die. Then a case study on the multi-core processor design is elaborated and system costs with different design configurations are analyzed.

#### 2.4.1 Impacts of Design Target

In this section, we vary the die area and the unit area to demonstrate the impact of design target on the final system cost. There are three variables in the design target: die area, unit area, and unit count. For each experiment, we fix one variable and change the values of other two. During the first experiment, the die area is changed while the number of units per die is kept constant. The results of the system cost are shown in Figure 2.6. Obviously, the larger the die size, the higher the total die cost. The increasing rates of both basic and non-testing case are the same, however, the case of partially functional dies has slower growing rate due to the increased partial yield when the unit size is large. Therefore, when the die size and unit size are large, using the partially functional die can help bias the cost.

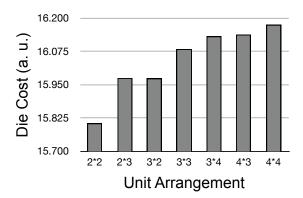

Next, we fix the die area and change the unit area and unit arrangement. The

**Figure 2.7.** Cost variations with different unit area when the die area is fixed.

**Figure 2.8.** Cost variations with different die sizes/unit counts when the unit area is fixed.

costs with partially functional die is shown in Figure 2.7. The basic and non-testing costs are not listed because the die area is not changed in this experiment, leaving the partial yield the only variable. More number of units per die means smaller area per unit. When the number of units per die is fixed, the cost variation between different arrangements is small, as shown in bar  $2\times3$  (representing the unit row and unit column) and  $3\times2$ . However, when the number of units per die increases from  $4\ (2\times2)$  to  $9\ (3\times3)$ , the system cost are significantly increased. When the tolerant threshold and defect cluster degree are set, smaller unit means lower partial yield, because more units may be affected by defects.